Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

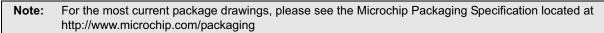

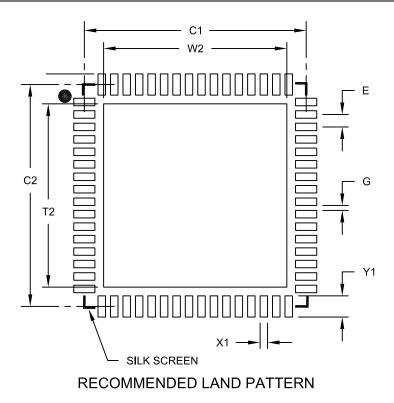

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9×9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc706a-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: PINOUT I/O DESCRIPTIONS                 |                                  |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|----------------------------------------------------|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                           | n Name Pin Buffer Description    |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| AN0-AN31                                           | I                                | Analog                           | Analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| AVdd                                               | Р                                | Р                                | Positive supply for analog modules. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                            |  |  |

| AVss                                               | Р                                | Р                                | Ground reference for analog modules.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| CLKI<br>CLKO                                       | I<br>O                           | ST/CMOS                          | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated<br>with OSC2 pin function.                                                                                                                                                      |  |  |

| CN0-CN23                                           | I                                | ST                               | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                               |  |  |

| C1RX<br>C1TX                                       | I<br>O                           | ST<br>—                          | ECAN1 bus receive pin.<br>ECAN1 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| C2RX                                               | I                                | ST                               | ECAN2 bus receive pin.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| C2TX                                               | 0                                | —                                | ECAN2 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| PGED1<br>PGEC1<br>PGED2<br>PGEC2<br>PGED3<br>PGEC3 | I/O<br>I<br>I/O<br>I<br>I/O<br>I | ST<br>ST<br>ST<br>ST<br>ST<br>ST | Data I/O pin for Programming/Debugging Communication Channel 1.<br>Clock input pin for Programming/Debugging Communication Channel 1.<br>Data I/O pin for Programming/Debugging Communication Channel 2.<br>Clock input pin for Programming/Debugging Communication Channel 2.<br>Data I/O pin for Programming/Debugging Communication Channel 3.<br>Clock input pin for Programming/Debugging Communication Channel 3. |  |  |

| IC1-IC8                                            | 1                                | ST                               | Capture Inputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                                    | -                                |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| INDX<br>QEA                                        |                                  | ST<br>ST                         | Quadrature Encoder Index Pulse input.<br>Quadrature Encoder Phase A input in QEI mode. Auxiliary timer external clock<br>gate input in Timer mode.                                                                                                                                                                                                                                                                      |  |  |

| QEB                                                | I                                | ST                               | Quadrature Encoder Phase A input in QEI mode. Auxiliary timer external clock gate input in Timer mode.                                                                                                                                                                                                                                                                                                                  |  |  |

| UPDN                                               | 0                                | CMOS                             | Position up/down counter direction state.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| INT0                                               | I                                | ST                               | External Interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| INT1                                               |                                  | ST                               | External Interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| INT2                                               |                                  | ST                               | External Interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| INT3<br>INT4                                       |                                  | ST<br>ST                         | External Interrupt 3.<br>External Interrupt 4.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| FLTA                                               |                                  | ST                               | PWM Fault A input.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| FLTB                                               |                                  | ST                               | PWM Fault B input.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PWM1L                                              | Ö                                | _                                | PWM1 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| PWM1H                                              | Ō                                | _                                | PWM1 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PWM2L                                              | 0                                |                                  | PWM2 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| PWM2H                                              | 0                                |                                  | PWM2 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PWM3L                                              | 0                                | _                                | PWM3 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| PWM3H                                              | 0                                | _                                | PWM3 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PWM4L                                              | 0                                | _                                | PWM4 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| PWM4H                                              | 0                                | —                                | PWM4 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| MCLR                                               | I/P                              | ST                               | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                              |  |  |

| OCFA                                               | I                                | ST                               | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                                                                                                                                                                                                                                                             |  |  |

| OCFB                                               | I                                | ST                               | Compare Fault B input (for Compare Channels 5, 6, 7 and 8).                                                                                                                                                                                                                                                                                                                                                             |  |  |

| OC1-OC8                                            | 0                                | _                                | Compare outputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| OSC1                                               | I                                | ST/CMOS                          | Oscillator crystal input. ST buffer when configured in RC mode;<br>CMOS otherwise.                                                                                                                                                                                                                                                                                                                                      |  |  |

| OSC2                                               | I/O                              | -                                | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                                |  |  |

| Legend: CMC                                        | OS = CMO                         | S compatible                     | e input or output Analog = Analog input P = Power                                                                                                                                                                                                                                                                                                                                                                       |  |  |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS compatible input or output Ana ST = Schmitt Trigger input with CMOS levels O =

Analog = Analog input ls O = Output

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow, and thus, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB), and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic, which typically uses both the accumulators.

The device supports three Saturation and Overflow modes:

1. Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- 2. Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

- 3. Bit 39 Catastrophic Overflow:

The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

# 3.6.2.2 Accumulator 'Write Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- 1. W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+ = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

# 3.6.2.3 Round Logic

The round logic is a combinational block which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word is simply discarded.

Conventional rounding zero-extends bit 15 of the accumulator and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.2.4 "Data Space Write Saturation"**). For the MAC class of instructions, the accumulator write-back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

| TABLE 4-5: | INTERRUPT CONTROLLER REGISTER MAP |

|------------|-----------------------------------|

|------------|-----------------------------------|

| IADLL       | т Ј.        |        |        |            | NOLLEN  |         |        |            | -      |          |         |             |         |           |         |            |               |               |

|-------------|-------------|--------|--------|------------|---------|---------|--------|------------|--------|----------|---------|-------------|---------|-----------|---------|------------|---------------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8  | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3     | Bit 2   | Bit 1      | Bit 0         | All<br>Resets |

| INTCON1     | 0080        | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE  | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR   | STKERR  | OSCFAIL    | _             | 0000          |

| INTCON2     | 0082        | ALTIVT | DISI   | _          | _       | _       | _      | _          | _      | _        | _       | _           | INT4EP  | INT3EP    | INT2EP  | INT1EP     | INT0EP        | 0000          |

| IFS0        | 0084        | _      | DMA1IF | AD1IF      | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | T3IF   | T2IF     | OC2IF   | IC2IF       | DMA0IF  | T1IF      | OC1IF   | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS1        | 0086        | U2TXIF | U2RXIF | INT2IF     | T5IF    | T4IF    | OC4IF  | OC3IF      | DMA2IF | IC8IF    | IC7IF   | AD2IF       | INT1IF  | CNIF      | _       | MI2C1IF    | SI2C1IF       | 0000          |

| IFS2        | 0088        | T6IF   | DMA4IF | _          | OC8IF   | OC7IF   | OC6IF  | OC5IF      | IC6IF  | IC5IF    | IC4IF   | IC3IF       | DMA3IF  | C1IF      | C1RXIF  | SPI2IF     | SPI2EIF       | 0000          |

| IFS3        | 008A        | FLTAIF | _      | DMA5IF     | _       | _       | QEIIF  | PWMIF      | C2IF   | C2RXIF   | INT4IF  | INT3IF      | T9IF    | T8IF      | MI2C2IF | SI2C2IF    | T7IF          | 0000          |

| IFS4        | 008C        | _      | _      | _          | _       | _       | _      | _          | _      | C2TXIF   | C1TXIF  | DMA7IF      | DMA6IF  | _         | U2EIF   | U1EIF      | FLTBIF        | 0000          |

| IEC0        | 0094        | _      | DMA1IE | AD1IE      | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | T3IE   | T2IE     | OC2IE   | IC2IE       | DMA0IE  | T1IE      | OC1IE   | IC1IE      | INT0IE        | 0000          |

| IEC1        | 0096        | U2TXIE | U2RXIE | INT2IE     | T5IE    | T4IE    | OC4IE  | OC3IE      | DMA2IE | IC8IE    | IC7IE   | AD2IE       | INT1IE  | CNIE      | _       | MI2C1IE    | SI2C1IE       | 0000          |

| IEC2        | 0098        | T6IE   | DMA4IE | _          | OC8IE   | OC7IE   | OC6IE  | OC5IE      | IC6IE  | IC5IE    | IC4IE   | IC3IE       | DMA3IE  | C1IE      | C1RXIE  | SPI2IE     | SPI2EIE       | 0000          |

| IEC3        | 009A        | FLTAIE | _      | DMA5IE     | _       | _       | QEIIE  | PWMIE      | C2IE   | C2RXIE   | INT4IE  | INT3IE      | T9IE    | T8IE      | MI2C2IE | SI2C2IE    | T7IE          | 0000          |

| IEC4        | 009C        | _      |        |            | —       | _       |        | _          |        | C2TXIE   | C1TXIE  | DMA7IE      | DMA6IE  | _         | U2EIE   | U1EIE      | FLTBIE        | 0000          |

| IPC0        | 00A4        | _      |        | T1IP<2:0>  | >       |         | (      | OC1IP<2:(  | )>     |          |         | IC1IP<2:0>  |         | _         | 11      | NT0IP<2:0> | •             | 4444          |

| IPC1        | 00A6        | _      |        | T2IP<2:0>  | >       | _       | (      | OC2IP<2:(  | )>     |          |         | IC2IP<2:0>  |         | _         | D       | MA0IP<2:0  | >             | 4444          |

| IPC2        | 00A8        | _      | ι      | J1RXIP<2:( | 0>      | _       | \$     | SPI1IP<2:0 | )>     |          | :       | SPI1EIP<2:0 | >       | _         |         | T3IP<2:0>  |               | 4444          |

| IPC3        | 00AA        | _      |        |            | —       |         | D      | MA1IP<2:   | 0>     |          |         | AD1IP<2:0>  | •       | _         | U       | 1TXIP<2:0  | >             | 0444          |

| IPC4        | 00AC        | _      |        | CNIP<2:0>  | >       | _       |        | _          |        |          | I       | MI2C1IP<2:0 | >       | _         | SI      | 2C1IP<2:0  | >             | 4044          |

| IPC5        | 00AE        | _      |        | IC8IP<2:0  | >       |         |        | IC7IP<2:0  | >      |          |         | AD2IP<2:0>  | •       | _         | 11      | NT1IP<2:0> | •             | 4444          |

| IPC6        | 00B0        | _      |        | T4IP<2:0>  | >       |         | (      | OC4IP<2:(  | )>     |          |         | OC3IP<2:0>  | •       | _         | D       | MA2IP<2:0  | >             | 4444          |

| IPC7        | 00B2        | _      | ι      | J2TXIP<2:0 | )>      | _       | U      | J2RXIP<2:  | 0>     | _        |         | INT2IP<2:0> | >       | _         |         | T5IP<2:0>  |               | 4444          |

| IPC8        | 00B4        | _      |        | C1IP<2:0>  | >       |         | C      | C1RXIP<2:  | 0>     |          |         | SPI2IP<2:0> | >       | _         | SI      | PI2EIP<2:0 | >             | 4444          |

| IPC9        | 00B6        | _      |        | IC5IP<2:0> | >       |         |        | IC4IP<2:0  | >      |          |         | IC3IP<2:0>  |         | _         | D       | MA3IP<2:0  | >             | 4444          |

| IPC10       | 00B8        | _      |        | OC7IP<2:0  | )>      |         | (      | OC6IP<2:(  | )>     |          |         | OC5IP<2:0>  | •       | _         | I       | C6IP<2:0>  |               | 4444          |

| IPC11       | 00BA        | _      |        | T6IP<2:0>  | >       |         | D      | MA4IP<2:   | 0>     |          | —       | -           |         | _         | C       | )C8IP<2:0> | •             | 4404          |

| IPC12       | 00BC        | _      |        | T8IP<2:0>  | >       |         | N      | 112C2IP<2  | :0>    |          |         | SI2C2IP<2:0 | >       | _         |         | T7IP<2:0>  |               | 4444          |

| IPC13       | 00BE        | _      | (      | C2RXIP<2:0 | 0>      | _       | I      | NT4IP<2:0  | )>     | -        |         | INT3IP<2:0> | >       | _         |         | T9IP<2:0>  |               | 4444          |

| IPC14       | 00C0        | _      | _      | _          | _       | _       |        | QEIIP<2:0  | >      | -        |         | PWMIP<2:0   | >       | _         |         | C2IP<2:0>  |               | 0444          |

| IPC15       | 00C2        |        | I      | FLTAIP<2:0 | )>      |         |        |            | _      | _        |         | DMA5IP<2:0  | >       | _         |         | —          | —             | 4040          |

| IPC16       | 00C4        | _      |        | —          | —       | _       | I      | U2EIP<2:0  | )>     |          |         | U1EIP<2:0>  |         | _         | F       | LTBIP<2:0> | >             | 0444          |

| IPC17       | 00C6        |        | (      | C2TXIP<2:0 | )>      | _       | C      | C1TXIP<2:  | 0>     | _        |         | DMA7IP<2:0  | >       | _         | D       | MA6IP<2:0  | >             | 4444          |

| INTTREG     | 00E0        | _      | —      | —          | —       |         | ILR<   | 3:0>       |        |          |         |             | VE      | CNUM<6:0> |         |            |               | 0000          |

|             |             |        |        |            |         |         |        |            |        |          |         |             |         |           |         |            |               |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0        | R/W-0                        | U-0                                    | U-0           | U-0                         | U-0               | U-0                                                                                                             | R/W-0                |

|--------------|------------------------------|----------------------------------------|---------------|-----------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|----------------------|

| TRAPR        | IOPUWR                       | —                                      | _             | —                           | —                 | —                                                                                                               | VREGS <sup>(3)</sup> |

| bit 15       |                              |                                        |               | ·                           | •                 |                                                                                                                 | bit                  |

| R/W-0        |                              | R/W-0                                  |               |                             |                   |                                                                                                                 |                      |

| EXTR         | R/W-0<br>SWR                 | SWDTEN <sup>(2)</sup>                  | R/W-0<br>WDTO | R/W-0<br>SLEEP              | R/W-0<br>IDLE     | R/W-1<br>BOR                                                                                                    | R/W-1<br>POR         |

| bit 7        | onne                         | onbien                                 |               | ULL.                        |                   | Bon                                                                                                             | bit                  |

|              |                              |                                        |               |                             |                   |                                                                                                                 |                      |

| Legend:      | L. L.'4                      |                                        | .:.           |                             |                   | (O)                                                                                                             |                      |

| R = Readab   |                              | W = Writable k                         | DIT           | -                           | mented bit, read  |                                                                                                                 |                      |

| -n = Value a | IPOR                         | '1' = Bit is set                       |               | '0' = Bit is cle            | ared              | x = Bit is unk                                                                                                  | nown                 |

| bit 15       | TRAPR: Trap                  | Reset Flag bit                         |               |                             |                   |                                                                                                                 |                      |

|              | 1 = A Trap C                 | onflict Reset has                      |               |                             |                   |                                                                                                                 |                      |

|              | -                            | onflict Reset has                      |               |                             |                   |                                                                                                                 |                      |

| bit 14       |                              | gal Opcode or                          |               |                             | •                 |                                                                                                                 |                      |

|              | 0                            | al opcode detect<br>Pointer caused     | · ·           | gal address m               | ode or uninitia   | lized W regist                                                                                                  | er used as a         |

|              |                              | l opcode or unir                       |               | Reset has not o             | ccurred           |                                                                                                                 |                      |

| bit 13-9     | Unimplemer                   | ted: Read as 'o                        | ,             |                             |                   |                                                                                                                 |                      |

| bit 8        | VREGS: Volt                  | age Regulator S                        | standby Durir | ng Sleep bit <sup>(3)</sup> |                   |                                                                                                                 |                      |

|              |                              | egulator is active<br>egulator goes in |               |                             | ер                |                                                                                                                 |                      |

| bit 7        | EXTR: Extern                 | nal Reset (MCLI                        | R) Pin bit    |                             |                   |                                                                                                                 |                      |

|              |                              | Clear (pin) Res<br>Clear (pin) Res     |               |                             |                   |                                                                                                                 |                      |

| bit 6        | SWR: Softwa                  | are Reset (Instru                      | ction) Flag b | it                          |                   |                                                                                                                 |                      |

|              |                              | instruction has                        |               |                             |                   |                                                                                                                 |                      |

|              |                              | instruction has                        |               |                             |                   |                                                                                                                 |                      |

| bit 5        |                              | oftware Enable/I                       | Jisable of W  |                             |                   |                                                                                                                 |                      |

|              | 1 = WDT is e<br>0 = WDT is d |                                        |               |                             |                   |                                                                                                                 |                      |

| bit 4        |                              | hdog Timer Tim                         | e-out Flag bi | t                           |                   |                                                                                                                 |                      |

|              |                              | e-out has occurr                       |               | -                           |                   |                                                                                                                 |                      |

|              | 0 = WDT time                 | e-out has not oc                       | curred        |                             |                   |                                                                                                                 |                      |

| bit 3        | SLEEP: Wak                   | e-up from Sleep                        | Flag bit      |                             |                   |                                                                                                                 |                      |

|              |                              | as been in Sleep                       |               |                             |                   |                                                                                                                 |                      |

|              |                              | as not been in S                       | •             |                             |                   |                                                                                                                 |                      |

| bit 2        |                              | up from Idle Fla                       | g bit         |                             |                   |                                                                                                                 |                      |

|              |                              | as in Idle mode<br>as not in Idle me   | ode           |                             |                   |                                                                                                                 |                      |

|              | Il of the Reset sta          | •                                      | set or cleare | d in software. S            | Setting one of th | nese bits in soft                                                                                               | ware does no         |

|              | ause a device Re             |                                        | (1) /         |                             |                   | a a la la servició de |                      |

| 2: If        | the FWDTEN Co                | ontiguration bit i                     | s 1 (unprog   | rammed), the V              | VUT IS alwavs (   | enabled, redard                                                                                                 | ness of the          |

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256MCX06A/X08A/X10A devices, this bit is unimplemented and reads back a programmed value.

| R/W-0         | R/W-0           | R/W-0                            | R/W-0          | R/W-0            | R/W-0            | R/W-0          | R/W-0   |

|---------------|-----------------|----------------------------------|----------------|------------------|------------------|----------------|---------|

| U2TXIF        | U2RXIF          | INT2IF                           | T5IF           | T4IF             | OC4IF            | OC3IF          | DMA21IF |

| bit 15        |                 |                                  |                |                  |                  |                | bit 8   |

| R/W-0         | R/W-0           | R/W-0                            | R/W-0          | R/W-0            | U-0              | R/W-0          | R/W-0   |

| IC8IF         | IC7IF           | AD2IF                            | INT1IF         | CNIF             | —                | MI2C1IF        | SI2C1IF |

| bit 7         |                 |                                  |                |                  |                  |                | bit (   |

| Legend:       |                 |                                  |                |                  |                  |                |         |

| R = Readable  | e bit           | W = Writable                     | bit            | U = Unimple      | mented bit, read | d as '0'       |         |

| -n = Value at | POR             | '1' = Bit is se                  | t              | '0' = Bit is cle | eared            | x = Bit is unk | nown    |

|               |                 |                                  |                |                  |                  |                |         |

| bit 15        |                 | RT2 Transmitte                   | -              | g Status bit     |                  |                |         |

|               |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 14        | •               | RT2 Receiver I                   |                | Status bit       |                  |                |         |

|               |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 13        | •               | nal Interrupt 2                  |                | t                |                  |                |         |

|               |                 | request has oc                   |                |                  |                  |                |         |

|               | 0 = Interrupt   | request has no                   | t occurred     |                  |                  |                |         |

| bit 12        |                 | Interrupt Flag                   |                |                  |                  |                |         |

|               |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 11        | -               | Interrupt Flag                   |                |                  |                  |                |         |

|               | 1 = Interrupt   | request has oc<br>request has no | curred         |                  |                  |                |         |

| bit 10        |                 | ut Compare Ch                    |                | upt Flag Status  | s bit            |                |         |

|               | 1 = Interrupt   | request has oc<br>request has no | curred         |                  |                  |                |         |

| bit 9         | •               | ut Compare Ch                    |                | upt Flag Status  | s bit            |                |         |

|               | 1 = Interrupt   | request has oc<br>request has no | curred         |                  |                  |                |         |

| bit 8         |                 |                                  |                | Complete Interi  | rupt Flag Status | bit            |         |

|               | 1 = Interrupt   | request has oc                   | curred         |                  | opti lag etate   |                |         |

|               | •               | request has no                   |                |                  |                  |                |         |

| bit 7         | -               | Capture Chann                    | -              | -lag Status bit  |                  |                |         |

|               |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 6         | -               | Capture Chann                    |                | -lag Status bit  |                  |                |         |

|               |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 5         | AD2IF: ADC2     | 2 Conversion C                   | Complete Inter | rupt Flag Statu  | ıs bit           |                |         |

|               | 1 = Interrupt   | request has oc<br>request has no | curred         | -                |                  |                |         |

| bit 4         | •               | nal Interrupt 1                  |                | t                |                  |                |         |

|               | 1 = Interrupt   | request has oc                   | curred         |                  |                  |                |         |

|               | 0 = Interrupt ( | request has no                   | t occurred     |                  |                  |                |         |

# REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 (CONTINUED)

| bit 1 | SI2C2IE: I2C2 Slave Events Interrupt Enable bit |

|-------|-------------------------------------------------|

|       | 1 = Interrupt request enabled                   |

|       | 0 = Interrupt request not enabled               |

|       |                                                 |

- bit 0 T7IE: Timer7 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0                          | U-0                   | U-0                 | U-0            | R-0               | R-0           | R-0             | R-0   |  |  |

|------------------------------|-----------------------|---------------------|----------------|-------------------|---------------|-----------------|-------|--|--|

|                              | _                     | _                   | _              | ILR<3:0>          |               |                 |       |  |  |

| oit 15                       |                       | 1                   |                |                   |               |                 | bit 8 |  |  |

|                              |                       |                     |                |                   |               |                 |       |  |  |

| U-0                          | R-0                   | R-0                 | R-0            | R-0               | R-0           | R-0             | R-0   |  |  |

| —                            |                       |                     |                | VECNUM<6:0>       | >             |                 |       |  |  |

| oit 7                        |                       |                     |                |                   |               |                 | bit ( |  |  |

|                              |                       |                     |                |                   |               |                 |       |  |  |

| <b>₋egend:</b><br>R = Readab | la hit                | W = Writable        | h:t            |                   | opted bit rea | ad aa (0)       |       |  |  |

|                              |                       |                     |                | U = Unimplem      |               |                 |       |  |  |

| n = Value a                  | IPOR                  | '1' = Bit is set    |                | '0' = Bit is clea | ared          | x = Bit is unkr | IOWN  |  |  |

| oit 15-12                    | Unimpleme             | ented: Read as the  | 0'             |                   |               |                 |       |  |  |

| pit 11-8                     | •                     | New CPU Interru     |                | el bits           |               |                 |       |  |  |

|                              |                       | J interrupt priorit |                |                   |               |                 |       |  |  |

|                              | •                     |                     | ,              |                   |               |                 |       |  |  |

|                              | •                     |                     |                |                   |               |                 |       |  |  |

|                              | •<br>0001 <b>- CP</b> | J interrupt priorit | v lovol is 1   |                   |               |                 |       |  |  |

|                              |                       | J interrupt priorit |                |                   |               |                 |       |  |  |

| oit 7                        | Unimpleme             | ented: Read as '    | 0'             |                   |               |                 |       |  |  |

| oit 6-0                      | VECNUM<               | 6:0>: Vector Nun    | nber of Pendir | ng Interrupt bits |               |                 |       |  |  |

|                              |                       | Interrupt vector    |                | •                 |               |                 |       |  |  |

|                              | •                     |                     | Ū              |                   |               |                 |       |  |  |

|                              | •                     |                     |                |                   |               |                 |       |  |  |

|                              | •                     | Interrupt vector    | nondina in nu  | mbor 0            |               |                 |       |  |  |

|                              | 0000001 =             | Interrupt vector    | penuing is hu  |                   |               |                 |       |  |  |

#### REGISTER 7-33: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

# 18.3 SPI Control Registers

# REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0  | U-0    | R/W-0   | U-0 | U-0 | U-0 | U-0    | U-0    |

|--------|--------|---------|-----|-----|-----|--------|--------|

| SPIEN  | —      | SPISIDL | —   |     | —   |        | —      |

| bit 15 |        |         |     |     |     |        | bit 8  |

|        |        |         |     |     |     |        |        |

| U-0    | R/C-0  | U-0     | U-0 | U-0 | U-0 | R-0    | R-0    |

| —      | SPIROV | —       | —   | _   | —   | SPITBF | SPIRBF |

| bit 7  |        |         |     |     |     |        | bit 0  |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | SPIEN: SPIx Enable bit                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module                                                                                                                                                                               |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 13   | SPISIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                |

|          | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                         |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 6    | SPIROV: Receive Overflow Flag bit                                                                                                                                                                                                                                                             |

|          | <ul> <li>1 = A new byte/word is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.</li> <li>0 = No overflow has occurred</li> </ul>                                                                                                 |

| bit 5-2  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 1    | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                                                  |

|          | 1 = Transmit not yet started; SPIxTXB is full                                                                                                                                                                                                                                                 |

|          | 0 = Transmit started; SPIxTXB is empty<br>Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB. Automatically<br>cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.                                                                       |

| bit 0    | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                                                   |

|          | <ul> <li>1 = Receive complete; SPIxRXB is full</li> <li>0 = Receive is not complete; SPIxRXB is empty</li> <li>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.</li> </ul> |

| U-0                 | U-0           | U-0                                   | R/W-0           | R/W-0              | R/W-0            | R/W-0            | R/W-0              |

|---------------------|---------------|---------------------------------------|-----------------|--------------------|------------------|------------------|--------------------|

|                     | _             | —                                     | DISSCK          | DISSDO             | MODE16           | SMP              | CKE <sup>(1)</sup> |

| bit 15              | l             |                                       |                 |                    |                  | 1                | bit                |

|                     |               |                                       |                 |                    |                  |                  |                    |

| R/W-0               | R/W-0         | R/W-0                                 | R/W-0           | R/W-0              | R/W-0            | R/W-0            | R/W-0              |

| SSEN <sup>(3)</sup> | СКР           | MSTEN                                 |                 | SPRE<2:0>(2        | )                | PPRE-            | <1:0> <b>(2)</b>   |

| bit 7               |               |                                       |                 |                    |                  |                  | bit                |

|                     |               |                                       |                 |                    |                  |                  |                    |

| Legend:             |               |                                       |                 |                    |                  |                  |                    |

| R = Readable        |               | W = Writable                          |                 | -                  | nented bit, read |                  |                    |

| -n = Value at F     | POR           | '1' = Bit is set                      |                 | '0' = Bit is clea  | ared             | x = Bit is unkr  | nown               |

|                     |               |                                       | o.1             |                    |                  |                  |                    |

| bit 15-13           | -             | nted: Read as '                       |                 |                    |                  |                  |                    |

| bit 12              |               | able SCKx Pin                         | ·               | • •                |                  |                  |                    |

|                     |               | SPI clock is disa<br>SPI clock is ena |                 |                    |                  |                  |                    |

| bit 11              | DISSDO: Dis   | sable SDOx Pin                        | bit             |                    |                  |                  |                    |

|                     | 1 = SDOx pir  | n is not used by                      | module; pin f   | functions as I/O   |                  |                  |                    |

|                     | 0 = SDOx pir  | n is controlled b                     | y the module    |                    |                  |                  |                    |

| bit 10              |               | ord/Byte Comm                         |                 |                    |                  |                  |                    |

|                     |               | nication is word-                     | • • •           |                    |                  |                  |                    |

| bit 9               |               | ication is byte-                      |                 |                    |                  |                  |                    |

| DIL 9               | Master mode   | Data Input Samp                       | Die Phase bit   |                    |                  |                  |                    |

|                     | 1 = Input dat | a sampled at e                        |                 |                    |                  |                  |                    |

|                     | -             | a sampled at m                        | iddle of data o | output time        |                  |                  |                    |

|                     | SMP must be   | e cleared when                        | SPIx is used    | in Slave mode      |                  |                  |                    |

| bit 8               |               | lock Edge Sele                        |                 |                    |                  |                  |                    |

|                     |               | •                                     |                 | on from active o   | lock state to Id | le clock state ( | see bit 6)         |

|                     |               |                                       |                 | on from Idle clo   |                  |                  |                    |

| bit 7               |               | e Select Enable                       |                 | de) <sup>(3)</sup> |                  |                  |                    |

|                     |               | used for Slave r                      |                 |                    |                  |                  |                    |

| L:1 0               | -             | -                                     |                 | rolled by port fu  | nction.          |                  |                    |

| bit 6               |               | Polarity Select I                     |                 | ve state is a low  |                  |                  |                    |

|                     |               |                                       | •               | e state is a high  |                  |                  |                    |

| bit 5               |               | ster Mode Enab                        |                 | C                  |                  |                  |                    |

|                     | 1 = Master m  | ode                                   |                 |                    |                  |                  |                    |

|                     |               | loue                                  |                 |                    |                  |                  |                    |

- 2: Do not set both the primary and secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

| U-0           | U-0           | R-0                                                                                      | R-0             | R-0              | R-0              | R-0             | R-0   |  |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|

| _             |               | ТХВО                                                                                     | TXBP            | RXBP             | TXWAR            | RXWAR           | EWARN |  |  |  |

| bit 15        | I             |                                                                                          |                 |                  |                  |                 | bit 8 |  |  |  |

|               |               |                                                                                          |                 |                  |                  |                 |       |  |  |  |

| R/C-0         | R/C-0         | R/C-0                                                                                    | U-0             | R/C-0            | R/C-0            | R/C-0           | R/C-0 |  |  |  |

| IVRIF         | WAKIF         | ERRIF                                                                                    |                 | FIFOIF           | RBOVIF           | RBIF            | TBIF  |  |  |  |

| bit 7         |               |                                                                                          |                 |                  |                  |                 | bit   |  |  |  |

| Legend:       |               |                                                                                          |                 | C = Cle          | earable bit      |                 |       |  |  |  |

| R = Readabl   | le bit        | W = Writable                                                                             | bit             | U = Unimple      | mented bit, read | d as '0'        |       |  |  |  |

| -n = Value at | t POR         | '1' = Bit is set                                                                         | t               | '0' = Bit is cle |                  | x = Bit is unkr | nown  |  |  |  |

| bit 15-14     | Unimplomor    | nted: Read as '                                                                          | 0'              |                  |                  |                 |       |  |  |  |

| bit 13        | -             | mitter in Error                                                                          |                 | bit              |                  |                 |       |  |  |  |

| DIL 15        |               | ter is in Bus Of                                                                         |                 | DI               |                  |                 |       |  |  |  |

|               | 0 = Transmitt | ter is not in Bus                                                                        | off state       |                  |                  |                 |       |  |  |  |

| bit 12        |               | mitter in Error                                                                          |                 | ssive bit        |                  |                 |       |  |  |  |

|               |               | ter is in Bus Pa<br>ter is not in Bus                                                    |                 | ۵                |                  |                 |       |  |  |  |

| bit 11        |               | iver in Error Sta                                                                        |                 | -                |                  |                 |       |  |  |  |

|               |               | is in Bus Pass                                                                           |                 |                  |                  |                 |       |  |  |  |

|               |               | is not in Bus P                                                                          |                 |                  |                  |                 |       |  |  |  |

| bit 10        |               | nsmitter in Erro                                                                         |                 | ng bit           |                  |                 |       |  |  |  |

|               |               | ter is in Error W<br>ter is not in Erro                                                  |                 | ate              |                  |                 |       |  |  |  |

| bit 9         |               | ceiver in Error                                                                          | -               |                  |                  |                 |       |  |  |  |

|               |               | is in Error War                                                                          | -               |                  |                  |                 |       |  |  |  |

|               | 0 = Receiver  | is not in Error                                                                          | Warning state   | •                |                  |                 |       |  |  |  |

| bit 8         |               | nsmitter or Reg                                                                          |                 | •                | ı bit            |                 |       |  |  |  |

|               |               | ter or receiver i<br>ter or receiver i                                                   |                 | •                |                  |                 |       |  |  |  |

| bit 7         |               |                                                                                          |                 | •                |                  |                 |       |  |  |  |

|               |               | IVRIF: Invalid Message Received Interrupt Flag bit<br>1 = Interrupt request has occurred |                 |                  |                  |                 |       |  |  |  |

|               | 0 = Interrupt | request has no                                                                           | t occurred      |                  |                  |                 |       |  |  |  |

| bit 6         | WAKIF: Bus    | Wake-up Activ                                                                            | ity Interrupt F | lag bit          |                  |                 |       |  |  |  |