Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc706a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*. Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the following devices:

- dsPIC33FJ64MC506A

- dsPIC33FJ64MC508A

- dsPIC33FJ64MC510A

- dsPIC33FJ64MC706A

- dsPIC33FJ64MC710A

- dsPIC33FJ128MC506A

- dsPIC33FJ128MC510A

- dsPIC33FJ128MC706A

- dsPIC33FJ128MC708A

- dsPIC33FJ128MC710A

- dsPIC33FJ256MC510A

- dsPIC33FJ256MC710A

The dsPIC33FJXXXMCX06A/X08A/X10A includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes).

These features make this family suitable for a wide variety of high-performance, digital signal control applications. The devices are pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The dsPIC33FJXXXMCX06A/X08A/X10A family of devices employs a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

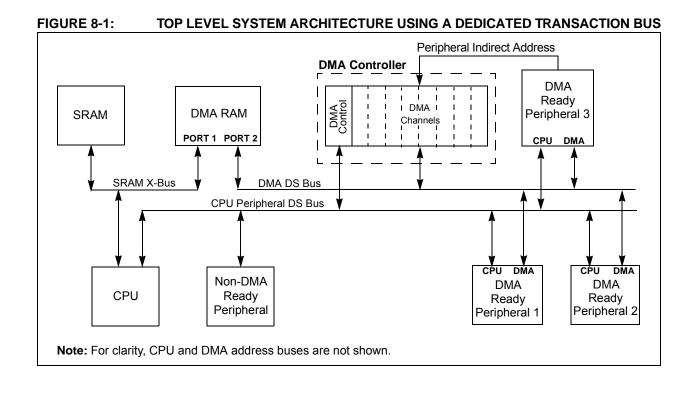

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together, the dsPIC33FJXXXMCX06A/X08A/X10A provide Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the dsPIC33FJXXXMCX06A/X08A/X10A devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXMCX06A/X08A/X10A devices.

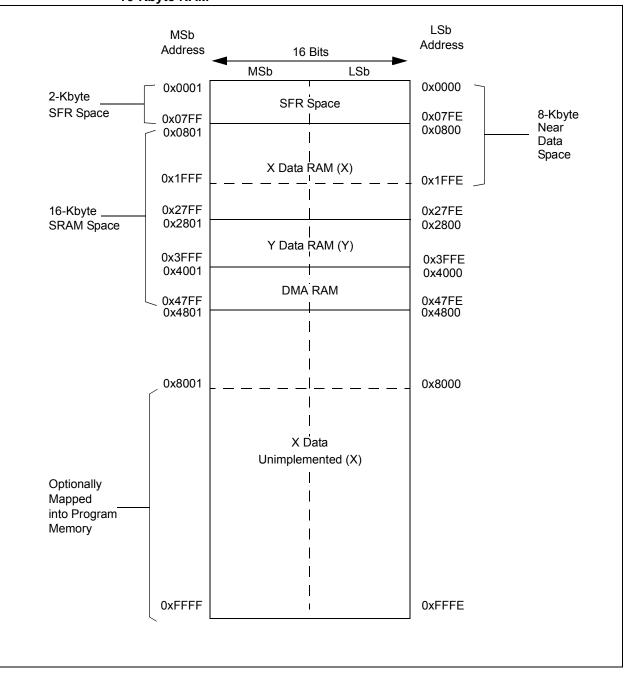

# FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 16-Kbyte RAM

| <b>TABLE 4-22:</b> | ECAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 (CONTINUED) |

|--------------------|---------------------------------------------------------|

|--------------------|---------------------------------------------------------|

| File Name  | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9 | Bit 8    | Bit 7                         | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|-----------|-----------|--------|--------|--------|----------|-------|----------|-------------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11SID | 046C |           |           |        | SID<   | 10:3>  |          |       |          |                               | SID<2:0> |       | —     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C1RXF11EID | 046E |           |           |        | EID<   | 15:8>  |          |       |          | EID<7:0>                      |          |       |       |       |       |       | xxxx  |               |

| C1RXF12SID | 0470 |           |           |        | SID<   | 10:3>  |          |       |          | SID<2:0> — EXIDE — EID<17:16> |          |       |       |       |       |       | 7:16> | xxxx          |

| C1RXF12EID | 0472 | EID<15:8> |           |        |        |        | EID<7:0> |       |          |                               |          |       |       | xxxx  |       |       |       |               |

| C1RXF13SID | 0474 |           | SID<10:3> |        |        |        |          |       | SID<2:0> |                               |          | EXIDE |       | EID<1 | 7:16> | xxxx  |       |               |

| C1RXF13EID | 0476 |           |           |        | EID<   | 15:8>  |          |       |          | EID<7:0>                      |          |       |       |       |       | xxxx  |       |               |

| C1RXF14SID | 0478 |           |           |        | SID<   | 10:3>  |          |       |          |                               | SID<2:0> |       |       | EXIDE |       | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A |           | EID<15:8> |        |        |        |          |       |          |                               |          | EID<  | 7:0>  |       |       |       | xxxx  |               |

| C1RXF15SID | 047C |           |           |        | SID<   | 10:3>  |          |       |          |                               | SID<2:0> |       |       | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF15EID | 047E |           |           |        | EID<   | 15:8>  |          |       |          |                               |          |       | EID<  | 7:0>  | •     | •     |       | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name  | Addr          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10     | Bit 9              | Bit 8        | Bit 7                         | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1              | Bit 0  | All<br>Resets |

|------------|---------------|--------|--------|--------|--------|------------|------------|--------------------|--------------|-------------------------------|----------|--------|-------|-------|--------|--------------------|--------|---------------|

|            | 0500-<br>051E |        | -      |        |        |            |            | Se                 | e definitior | when WIN                      | = x      |        |       |       |        |                    |        |               |

| C2BUFPNT1  | 0520          |        | F3BF   | ><3:0> |        |            | F2BF       | <sup>D</sup> <3:0> |              |                               | F1BF     | P<3:0> |       |       | F0BF   | <sup>2</sup> <3:0> |        | 0000          |

| C2BUFPNT2  | 0522          |        | -      | ><3:0> |        |            | F6BP<3:0>  |                    |              |                               |          | P<3:0> |       |       |        | 2<3:0>             |        | 0000          |

| C2BUFPNT3  | 0524          |        | F11B   | P<3:0> |        |            | F10BP<3:0> |                    |              |                               | F9BF     | ><3:0> |       |       | F8BF   | <3:0>              |        | 0000          |

| C2BUFPNT4  | 0526          |        | F15B   | P<3:0> |        | F14BP<3:0> |            |                    |              |                               | F13BI    | D<3:0> |       |       | F12BI  | ><3:0>             |        | 0000          |

| C2RXM0SID  | 0530          |        |        |        | SID<   | 10:3>      |            |                    |              |                               | SID<2:0> |        | —     | MIDE  | _      | EID<               | 17:16> | xxxx          |

| C2RXM0EID  | 0532          |        |        |        | EID<   | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXM1SID  | 0534          |        |        |        | SID<   | 10:3>      |            |                    |              |                               | SID<2:0> |        | —     | MIDE  | —      | EID<               | 17:16> | xxxx          |

| C2RXM1EID  | 0536          |        |        |        | EID<   | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXM2SID  | 0538          |        |        |        | SID<   | 10:3>      |            |                    |              |                               | SID<2:0> |        | —     | MIDE  | —      | EID<               | 17:16> | xxxx          |

| C2RXM2EID  | 053A          |        |        |        | EID<   | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXF0SID  | 0540          |        |        |        | SID<   | 10:3>      |            |                    |              |                               | SID<2:0> |        | _     | EXIDE | _      | EID<               | 17:16> | xxxx          |

| C2RXF0EID  | 0542          |        |        |        | EID<   | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        | _                  |        | xxxx          |

| C2RXF1SID  | 0544          |        |        |        | SID<   | 10:3>      |            |                    |              |                               | SID<2:0> |        |       | EXIDE |        | EID<               | 17:16> | xxxx          |

| C2RXF1EID  | 0546          |        |        |        | EID<   | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXF2SID  | 0548          |        |        |        | SID<   | 10:3>      |            |                    |              |                               | SID<2:0> |        | —     | EXIDE | —      | EID<               | 17:16> | xxxx          |

| C2RXF2EID  | 054A          |        |        |        | EID<   | 15:8>      |            |                    |              | EID<7:0>                      |          |        |       |       |        | xxxx               |        |               |

| C2RXF3SID  | 054C          |        |        |        | SID<   | 10:3>      |            |                    |              | SID<2:0> — EXIDE — EID<17:16> |          |        |       |       | 17:16> | xxxx               |        |               |

| C2RXF3EID  | 054E          |        |        |        | EID<   | 15:8>      |            |                    |              | EID<7:0>                      |          |        |       |       |        |                    | xxxx   |               |

| C2RXF4SID  | 0550          |        |        |        | SID<   |            |            |                    |              |                               | SID<2:0> |        | —     | EXIDE | —      | EID<               | 17:16> | xxxx          |

| C2RXF4EID  | 0552          |        |        |        | EID<   |            |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXF5SID  | 0554          |        |        |        |        | 10:3>      |            |                    |              |                               | SID<2:0> |        | —     | EXIDE | —      | EID<               | 17:16> | xxxx          |

| C2RXF5EID  | 0556          |        |        |        |        | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXF6SID  | 0558          |        |        |        |        | 10:3>      |            |                    |              |                               | SID<2:0> |        |       | EXIDE | —      | EID<               | 17:16> | xxxx          |

| C2RXF6EID  | 055A          |        |        |        |        | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXF7SID  | 055C          |        |        |        |        | 10:3>      |            |                    |              |                               | SID<2:0> |        | —     | EXIDE | —      | EID<               | 17:16> | xxxx          |

| C2RXF7EID  | 055E          |        |        |        |        | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXF8SID  | 0560          |        |        |        | SID<   |            |            |                    |              |                               | SID<2:0> |        |       | EXIDE | —      | EID<               | 17:16> | xxxx          |

| C2RXF8EID  | 0562          |        |        |        | EID<   |            |            |                    |              |                               | 010.0.5  |        | EID   | <7:0> |        |                    |        | xxxx          |

| C2RXF9SID  | 0564          |        |        |        | SID<   |            |            |                    |              |                               | SID<2:0> |        |       | EXIDE | —      | EID<               | 17:16> | XXXX          |

| C2RXF9EID  | 0566          |        |        |        | EID<   |            |            |                    |              | <b> </b>                      |          |        | EID   | <7:0> |        |                    | 17 10: | XXXX          |

| C2RXF10SID | 0568          |        |        |        | SID<   |            |            |                    |              |                               | SID<2:0> |        |       | EXIDE | —      | EID<               | 17:16> | XXXX          |

| C2RXF10EID | 056A          |        |        |        | EID<   | 15:8>      |            |                    |              |                               |          |        | EID   | <7:0> |        |                    |        | XXXX          |

#### TABLE 4-25: ECAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33FJXXXMC708A/710A DEVICES

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0        | R/W-0                        | U-0                                    | U-0           | U-0                         | U-0               | U-0                                                                                                             | R/W-0                |

|--------------|------------------------------|----------------------------------------|---------------|-----------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|----------------------|

| TRAPR        | IOPUWR                       | —                                      | _             | —                           | —                 | —                                                                                                               | VREGS <sup>(3)</sup> |

| bit 15       |                              |                                        |               | ·                           | •                 |                                                                                                                 | bit                  |

| R/W-0        |                              | R/W-0                                  |               |                             |                   |                                                                                                                 |                      |

| EXTR         | R/W-0<br>SWR                 | SWDTEN <sup>(2)</sup>                  | R/W-0<br>WDTO | R/W-0<br>SLEEP              | R/W-0<br>IDLE     | R/W-1<br>BOR                                                                                                    | R/W-1<br>POR         |

| bit 7        | onne                         | onbien                                 |               | ULL.                        |                   | Bon                                                                                                             | bit                  |

|              |                              |                                        |               |                             |                   |                                                                                                                 |                      |

| Legend:      | L. L.'4                      |                                        | .:.           |                             |                   | (O)                                                                                                             |                      |

| R = Readab   |                              | W = Writable k                         | DIT           | -                           | mented bit, read  |                                                                                                                 |                      |

| -n = Value a | IPOR                         | '1' = Bit is set                       |               | '0' = Bit is cle            | ared              | x = Bit is unk                                                                                                  | nown                 |

| bit 15       | TRAPR: Trap                  | Reset Flag bit                         |               |                             |                   |                                                                                                                 |                      |

|              | 1 = A Trap C                 | onflict Reset has                      |               |                             |                   |                                                                                                                 |                      |

|              | -                            | onflict Reset has                      |               |                             |                   |                                                                                                                 |                      |

| bit 14       |                              | gal Opcode or                          |               |                             | •                 |                                                                                                                 |                      |

|              | 0                            | al opcode detect<br>Pointer caused     | · ·           | gal address m               | ode or uninitia   | lized W regist                                                                                                  | er used as a         |

|              |                              | l opcode or unir                       |               | Reset has not o             | ccurred           |                                                                                                                 |                      |

| bit 13-9     | Unimplemer                   | ted: Read as 'o                        | ,             |                             |                   |                                                                                                                 |                      |

| bit 8        | VREGS: Volt                  | age Regulator S                        | standby Durir | ng Sleep bit <sup>(3)</sup> |                   |                                                                                                                 |                      |

|              |                              | egulator is active<br>egulator goes in |               |                             | ер                |                                                                                                                 |                      |

| bit 7        | EXTR: Extern                 | nal Reset (MCLI                        | R) Pin bit    |                             |                   |                                                                                                                 |                      |

|              |                              | Clear (pin) Res<br>Clear (pin) Res     |               |                             |                   |                                                                                                                 |                      |

| bit 6        | SWR: Softwa                  | are Reset (Instru                      | ction) Flag b | it                          |                   |                                                                                                                 |                      |

|              |                              | instruction has                        |               |                             |                   |                                                                                                                 |                      |

|              |                              | instruction has                        |               |                             |                   |                                                                                                                 |                      |

| bit 5        |                              | oftware Enable/I                       | Jisable of W  |                             |                   |                                                                                                                 |                      |

|              | 1 = WDT is e<br>0 = WDT is d |                                        |               |                             |                   |                                                                                                                 |                      |

| bit 4        |                              | hdog Timer Tim                         | e-out Flag bi | t                           |                   |                                                                                                                 |                      |

|              |                              | e-out has occurr                       |               | -                           |                   |                                                                                                                 |                      |

|              | 0 = WDT time                 | e-out has not oc                       | curred        |                             |                   |                                                                                                                 |                      |

| bit 3        | SLEEP: Wak                   | e-up from Sleep                        | Flag bit      |                             |                   |                                                                                                                 |                      |

|              |                              | as been in Sleep                       |               |                             |                   |                                                                                                                 |                      |

|              |                              | as not been in S                       | •             |                             |                   |                                                                                                                 |                      |

| bit 2        |                              | up from Idle Fla                       | g bit         |                             |                   |                                                                                                                 |                      |

|              |                              | as in Idle mode<br>as not in Idle me   | ode           |                             |                   |                                                                                                                 |                      |

|              | Il of the Reset sta          | •                                      | set or cleare | d in software. S            | Setting one of th | nese bits in soft                                                                                               | ware does no         |

|              | ause a device Re             |                                        | (1) /         |                             |                   | a a la la servició de |                      |

| 2: If        | the FWDTEN Co                | ontiguration bit i                     | s 1 (unprog   | rammed), the V              | VUT IS alwavs (   | enabled, redard                                                                                                 | ness of the          |

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256MCX06A/X08A/X10A devices, this bit is unimplemented and reads back a programmed value.

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| REGISTER 7      | -3: INTCC                      | DN1: INTERR                                                | UPT CONTR                        |                                  | EK 1                 |                 |       |

|-----------------|--------------------------------|------------------------------------------------------------|----------------------------------|----------------------------------|----------------------|-----------------|-------|

| R/W-0           | R/W-0                          | R/W-0                                                      | R/W-0                            | R/W-0                            | R/W-0                | R/W-0           | R/W-0 |

| NSTDIS          | OVAERR                         | OVBERR                                                     | COVAERR                          | COVBERR                          | OVATE                | OVBTE           | COVTE |

| bit 15          |                                |                                                            |                                  |                                  |                      |                 | bit 8 |

| R/W-0           | R/W-0                          | R/W-0                                                      | R/W-0                            | R/W-0                            | R/W-0                | R/W-0           | U-0   |

| SFTACERR        | DIV0ERR                        | DMACERR                                                    | MATHERR                          | ADDRERR                          | STKERR               | OSCFAIL         | _     |

| bit 7           |                                |                                                            | I                                |                                  |                      |                 | bit ( |

| Legend:         |                                |                                                            |                                  |                                  |                      |                 |       |

| R = Readable    | bit                            | W = Writable                                               | bit                              | U = Unimpler                     | nented bit, read     | d as '0'        |       |

| -n = Value at I | POR                            | '1' = Bit is set                                           |                                  | '0' = Bit is cle                 |                      | x = Bit is unkr | nown  |

| bit 15          | 1 = Interrupt                  | errupt Nesting D<br>nesting is disat<br>nesting is enab    | oled                             |                                  |                      |                 |       |

| bit 14          | 1 = Trap was                   | ccumulator A O<br>caused by ove<br>not caused by           | rflow of Accur                   | nulator A                        |                      |                 |       |

| bit 13          | <b>OVBERR:</b> Ac              | ccumulator B O<br>caused by ove<br>not caused by           | verflow Trap F<br>rflow of Accur | lag bit<br>nulator B             |                      |                 |       |

| bit 12          | <b>COVAERR:</b> A 1 = Trap was | Accumulator A<br>caused by cata<br>not caused by           | Catastrophic (<br>astrophic over | Dverflow Trap F<br>flow of Accum | ulator A             |                 |       |

| bit 11          | <b>COVBERR:</b> A 1 = Trap was | Accumulator B<br>caused by cata<br>not caused by           | Catastrophic (<br>astrophic over | Dverflow Trap I<br>flow of Accum | Flag bit<br>ulator B |                 |       |

| bit 10          | OVATE: Accu                    | umulator A Ove                                             | rflow Trap En                    |                                  |                      |                 |       |

| bit 9           |                                | umulator B Ove<br>rflow of Accumu<br>bled                  |                                  | able bit                         |                      |                 |       |

| bit 8           |                                | astrophic Overf<br>catastrophic ove<br>ibled               | •                                |                                  | enabled              |                 |       |

| bit 7           | 1 = Math erro                  | Shift Accumula<br>or trap was caus<br>or trap was not      | sed by an inva                   | lid accumulato                   |                      |                 |       |

| bit 6           | <b>DIV0ERR:</b> Ar             | rithmetic Error S<br>or trap was caus<br>or trap was not   | Status bit<br>sed by a divide    | e by zero                        |                      |                 |       |

| bit 5           | DMACERR: 1<br>1 = DMA con      | DMA Controller<br>troller error trap<br>troller error trap | Error Status I<br>has occurred   | pit<br>I                         |                      |                 |       |

| bit 4           | MATHERR: A                     | Arithmetic Error                                           | Status bit                       |                                  |                      |                 |       |

- $\ensuremath{\mathtt{l}}$  = Math error trap has occurred

- 0 = Math error trap has not occurred

| U-0          | R/W-1              | R/W-0                                  | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |

|--------------|--------------------|----------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| _            |                    | OC7IP<2:0>                             |                 | —                 |                 | OC6IP<2:0>      |       |

| bit 15       |                    |                                        |                 |                   |                 |                 | bit   |

|              |                    |                                        |                 |                   |                 |                 |       |

| U-0          | R/W-1              | R/W-0                                  | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |

|              |                    | OC5IP<2:0>                             |                 |                   |                 | IC6IP<2:0>      |       |

| bit 7        |                    |                                        |                 |                   |                 |                 | bit   |

| Legend:      |                    |                                        |                 |                   |                 |                 |       |

| R = Readab   | le bit             | W = Writable                           | bit             | U = Unimple       | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR              | '1' = Bit is set                       |                 | '0' = Bit is cl   | eared           | x = Bit is unkr | nown  |

| bit 15       | Unimpleme          | nted: Read as '                        | ٦ <b>'</b>      |                   |                 |                 |       |

| bit 14-12    | -                  | : Output Compa                         |                 | ' Interrupt Prio  | ritv bits       |                 |       |

|              |                    | upt is priority 7 (I                   |                 | -                 |                 |                 |       |

|              | •                  |                                        | •               | • • • •           |                 |                 |       |

|              | •                  |                                        |                 |                   |                 |                 |       |

|              | 001 = Interru      | upt is priority 1                      |                 |                   |                 |                 |       |

|              |                    | upt source is dis                      | abled           |                   |                 |                 |       |

| bit 11       | Unimpleme          | nted: Read as 'o                       | כ'              |                   |                 |                 |       |

| bit 10-8     |                    | : Output Compa                         |                 | -                 | rity bits       |                 |       |

|              | 111 = Interru      | upt is priority 7 (I                   | highest priorif | y interrupt)      |                 |                 |       |

|              | •                  |                                        |                 |                   |                 |                 |       |

|              | •                  |                                        |                 |                   |                 |                 |       |

|              |                    | upt is priority 1<br>upt source is dis | ablod           |                   |                 |                 |       |

| bit 7        |                    | nted: Read as '                        |                 |                   |                 |                 |       |

| bit 6-4      | -                  | : Output Compa                         |                 | Interrunt Prio    | rity hits       |                 |       |

|              |                    | upt is priority 7 (I                   |                 | •                 |                 |                 |       |

|              | •                  |                                        | 5               | ,,                |                 |                 |       |

|              | •                  |                                        |                 |                   |                 |                 |       |

|              | •<br>001 = Interri | upt is priority 1                      |                 |                   |                 |                 |       |

|              |                    | upt source is dis                      | abled           |                   |                 |                 |       |

| bit 3        | Unimpleme          | nted: Read as 'o                       | כ'              |                   |                 |                 |       |

| bit 2-0      | IC6IP<2:0>:        | Input Capture C                        | Channel 6 Inte  | errupt Priority I | oits            |                 |       |

|              | 111 = Interru      | upt is priority 7 (I                   | highest priorit | y interrupt)      |                 |                 |       |

|              | •                  |                                        |                 |                   |                 |                 |       |

|              | •                  |                                        |                 |                   |                 |                 |       |

|              | 001 = Interru      | unt in priority 1                      |                 |                   |                 |                 |       |

|              |                    | upt source is dis                      |                 |                   |                 |                 |       |

### REGISTER 7-25: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

#### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PWCOL7 | PWCOL6 | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| XWCOL7 | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3 | XWCOL2 | XWCOL1 | XWCOL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:       |                  |                                                    | C = Clearable bit     |                    |

|---------------|------------------|----------------------------------------------------|-----------------------|--------------------|

| R = Readabl   | e bit            | W = Writable bit                                   | U = Unimplemented bit | , read as '0'      |

| -n = Value at | POR              | '1' = Bit is set                                   | '0' = Bit is cleared  | x = Bit is unknown |

|               |                  |                                                    |                       |                    |

| bit 15        |                  | Channel 7 Peripheral Write                         | e Collision Flag bit  |                    |

|               |                  | collision detected<br>ite collision detected       |                       |                    |

| bit 14        |                  | : Channel 6 Peripheral Write                       | e Collision Flag bit  |                    |

|               |                  | collision detected                                 |                       |                    |

|               | 0 = No wr        | ite collision detected                             |                       |                    |

| bit 13        | PWCOL5           | : Channel 5 Peripheral Write                       | e Collision Flag bit  |                    |

|               |                  | collision detected                                 |                       |                    |

| bit 12        |                  | ite collision detected                             | - Collision Flag hit  |                    |

| DIL 12        |                  | : Channel 4 Peripheral Write<br>collision detected | e Collision Flag bit  |                    |

|               |                  | ite collision detected                             |                       |                    |

| bit 11        | PWCOL3:          | Channel 3 Peripheral Write                         | e Collision Flag bit  |                    |

|               |                  | collision detected                                 |                       |                    |

|               |                  | ite collision detected                             |                       |                    |

| bit 10        |                  | : Channel 2 Peripheral Write                       | e Collision Flag bit  |                    |

|               |                  | collision detected<br>ite collision detected       |                       |                    |

| bit 9         | PWCOL1:          | : Channel 1 Peripheral Write                       | e Collision Flag bit  |                    |

|               | 1 = Write        | collision detected                                 |                       |                    |

|               | 0 <b>= No wr</b> | ite collision detected                             |                       |                    |

| bit 8         |                  | Channel 0 Peripheral Write                         | e Collision Flag bit  |                    |

|               |                  | collision detected<br>ite collision detected       |                       |                    |

| bit 7         |                  | : Channel 7 DMA RAM Writ                           | e Collision Flag bit  |                    |

|               |                  | collision detected                                 |                       |                    |

|               | 0 <b>= No wr</b> | ite collision detected                             |                       |                    |

| bit 6         |                  | : Channel 6 DMA RAM Writ                           | e Collision Flag bit  |                    |

|               |                  | collision detected<br>ite collision detected       |                       |                    |

| bit 5         |                  | : Channel 5 DMA RAM Writ                           | e Collision Flag bit  |                    |

|               |                  | collision detected                                 |                       |                    |

|               |                  | ite collision detected                             |                       |                    |

| bit 4         | XWCOL4           | : Channel 4 DMA RAM Writ                           | e Collision Flag bit  |                    |

|               |                  | collision detected                                 |                       |                    |

|               | 0 = NO Wr        | ite collision detected                             |                       |                    |

### 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJXXXMCX06A/X08A/X10A devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- · Software-controlled Doze mode

- · Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### 10.1 Clock Frequency and Clock Switching

dsPIC33FJXXXMCX06A/X08A/X10A devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

#### 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJXXXMCX06A/X08A/X10A devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode has the following features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports and peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of the following events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | SPI1MD: SPI1 Module Disable bit               |

|-------|-----------------------------------------------|

|       | 1 = SPI1 module is disabled                   |

|       | 0 = SPI1 module is enabled                    |

| bit 2 | C2MD: ECAN2 Module Disable bit                |

|       | 1 = ECAN2 module is disabled                  |

|       | 0 = ECAN2 module is enabled                   |

| bit 1 | C1MD: ECAN1 Module Disable bit                |

|       | 1 = ECAN1 module is disabled                  |

|       | 0 = ECAN1 module is enabled                   |

| bit 0 | AD1MD: ADC1 Module Disable bit <sup>(1)</sup> |

|       | 1 = ADC1 module is disabled                   |

|       | 0 = ADC1 module is enabled                    |

**Note 1:** The PCFGx bits have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

### 11.6 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 26-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and Vss. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 26.0 "Electrical Characteristics" for additional information.

### 11.7 I/O Resources

Many useful resources related to I/O are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en546066

### 11.7.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

111 = PWM mode on OCx, Fault pin enabled 110 = PWM mode on OCx, Fault pin disabled

011 = Compare event toggles OCx pin

000 = Output compare channel is disabled

| U-0          | U-0                    | R/W-0                                | U-0               | U-0               | U-0            | U-0             | U-0   |

|--------------|------------------------|--------------------------------------|-------------------|-------------------|----------------|-----------------|-------|

|              |                        | OCSIDL                               | _                 | _                 | —              | —               | _     |

| bit 15       |                        |                                      |                   |                   |                |                 | bit 8 |

|              |                        |                                      |                   |                   |                |                 |       |

| U-0          | U-0                    | U-0                                  | R-0, HC           | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|              |                        |                                      | OCFLT             | OCTSEL            |                | OCM<2:0>        |       |

| bit 7        |                        |                                      |                   |                   |                |                 | bit 0 |

|              |                        |                                      |                   |                   |                |                 |       |

| Legend:      |                        | HC = Hardware                        | Clearable bit     |                   |                |                 |       |

| R = Readab   | le bit                 | W = Writable bit                     |                   | U = Unimple       | mented bit, re | ad as '0'       |       |

| -n = Value a | t POR                  | '1' = Bit is set                     |                   | '0' = Bit is cle  | eared          | x = Bit is unkr | iown  |

|              |                        |                                      |                   |                   |                |                 |       |

| bit 15-14    | Unimpleme              | nted: Read as '0'                    |                   |                   |                |                 |       |

| bit 13       | OCSIDL: St             | op Output Compa                      | re in Idle Mode   | Control bit       |                |                 |       |

|              |                        | Compare x halts in                   |                   |                   | 1.             |                 |       |

|              | -                      | Compare x continu                    | les to operate ir | n CPU Idle mo     | de             |                 |       |

| bit 12-5     | •                      | nted: Read as '0'                    |                   |                   |                |                 |       |

| bit 4        | OCFLT: PW              | M Fault Condition                    | Status bit        |                   |                |                 |       |

|              |                        | ault condition has                   | <b>`</b>          |                   | <b>,</b>       |                 |       |

|              |                        | /I Fault condition h                 |                   | is bit is only us | sed when OCM   | A<2:0> = 111)   |       |

| bit 3        | OCTSEL: O              | utput Compare Ti                     | mer Select bit    |                   |                |                 |       |

|              |                        | s the clock source                   | •                 |                   |                |                 |       |

|              | $\wedge = 1 m o r^2 i$ |                                      |                   |                   |                |                 |       |

| bit 2-0      |                        | s the clock source<br>Output Compare | •                 |                   |                |                 |       |

101 = Initialize OCx pin low, generate continuous output pulses on OCx pin 100 = Initialize OCx pin low, generate single output pulse on OCx pin

010 = Initialize OCx pin high, compare event forces OCx pin low 001 = Initialize OCx pin low, compare event forces OCx pin high

© 2009-2012 Microchip Technology Inc.

| R/W-0         | R/W-0                                                                                                                                                         | R/W-0              | R/W-0            | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

| FBOV4H        | FBOV4L                                                                                                                                                        | FBOV3H             | FBOV3L           | FBOV2H               | FBOV2L               | FBOV1H               | FBOV1L               |  |  |  |

| bit 15        |                                                                                                                                                               |                    |                  |                      |                      |                      | bit 8                |  |  |  |

|               |                                                                                                                                                               |                    |                  |                      |                      |                      |                      |  |  |  |

| R/W-0         | U-0                                                                                                                                                           | U-0                | U-0              | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| FLTBM         | —                                                                                                                                                             | —                  | —                | FBEN4 <sup>(1)</sup> | FBEN3 <sup>(1)</sup> | FBEN2 <sup>(1)</sup> | FBEN1 <sup>(1)</sup> |  |  |  |

| bit 7         |                                                                                                                                                               |                    |                  |                      |                      |                      | bit (                |  |  |  |

| Legend:       |                                                                                                                                                               |                    |                  |                      |                      |                      |                      |  |  |  |

| R = Readable  | ⊇ hit                                                                                                                                                         | W = Writable       | hit              | II = I Inimplen      | nented bit, read     | las 'O'              |                      |  |  |  |

| -n = Value at |                                                                                                                                                               | '1' = Bit is set   |                  | '0' = Bit is clea    |                      | x = Bit is unkr      | own                  |  |  |  |

|               | TOR                                                                                                                                                           |                    |                  |                      | area                 |                      | lowin                |  |  |  |

| bit 15-8      | FBOVxH<4:1                                                                                                                                                    | I>:FBOVxI <4:      | 1>: Fault Inpu   | t B PWM Over         | ride Value bits      |                      |                      |  |  |  |

|               | <b>FBOVxH&lt;4:1&gt;:FBOVxL&lt;4:1&gt;:</b> Fault Input B PWM Override Value bits<br>1 = The PWM output pin is driven active on an external Fault input event |                    |                  |                      |                      |                      |                      |  |  |  |

|               | 0 = The PWM output pin is driven inactive on an external Fault input event                                                                                    |                    |                  |                      |                      |                      |                      |  |  |  |

| bit 7         | FLTBM: Fault B Mode bit                                                                                                                                       |                    |                  |                      |                      |                      |                      |  |  |  |

|               | 1 = The Fault B input pin functions in the Cycle-by-Cycle mode                                                                                                |                    |                  |                      |                      |                      |                      |  |  |  |

|               |                                                                                                                                                               | t B input pin late |                  | ol pins to the sta   | ates programm        | ed in FLTBCON        | N<15:8>              |  |  |  |

| bit 6-4       | •                                                                                                                                                             | ted: Read as '     |                  |                      |                      |                      |                      |  |  |  |

| bit 3         | FBEN4: Fault Input B Enable bit <sup>(1)</sup>                                                                                                                |                    |                  |                      |                      |                      |                      |  |  |  |

|               | <ul> <li>1 = PWM4H/PWM4L pin pair is controlled by Fault Input B</li> <li>0 = PWM4H/PWM4L pin pair is not controlled by Fault Input B</li> </ul>              |                    |                  |                      |                      |                      |                      |  |  |  |

|               |                                                                                                                                                               |                    |                  | lled by Fault In     | put B                |                      |                      |  |  |  |

| bit 2         | FBEN3: Fault Input B Enable bit <sup>(1)</sup>                                                                                                                |                    |                  |                      |                      |                      |                      |  |  |  |

|               | 1 = PWM3H/PWM3L pin pair is controlled by Fault Input B<br>0 = PWM3H/PWM3L pin pair is not controlled by Fault Input B                                        |                    |                  |                      |                      |                      |                      |  |  |  |

| bit 1         | <b>FBEN2:</b> Fault Input B Enable bit <sup>(1)</sup>                                                                                                         |                    |                  |                      |                      |                      |                      |  |  |  |

| DIL           | 1 = PWM2H/PWM2L pin pair is controlled by Fault Input B                                                                                                       |                    |                  |                      |                      |                      |                      |  |  |  |

|               | 0 = PWM2H/PWM2L pin pair is not controlled by Fault Input B                                                                                                   |                    |                  |                      |                      |                      |                      |  |  |  |

| bit 0         |                                                                                                                                                               | t Input B Enabl    |                  | 2                    |                      |                      |                      |  |  |  |

|               | 1 = PWM1H/PWM1L pin pair is controlled by Fault Input B                                                                                                       |                    |                  |                      |                      |                      |                      |  |  |  |

|               | 1 = PWM1H/                                                                                                                                                    | PWM1L pin pai      | ir is controlled | by Fault Input       | В                    |                      |                      |  |  |  |

#### REGISTER 16-10: PxFLTBCON: PWMx FAULT B CONTROL REGISTER

**Note 1:** Fault A pin has priority over Fault B pin, if enabled.

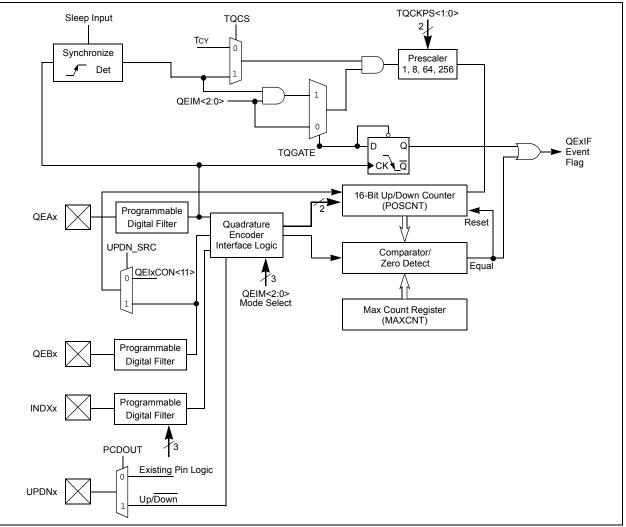

## 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Quadrature Encoder Interface (QEI)" (DS70208) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This section describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI include the following:

- Three input channels for two phase signals and an index pulse

- 16-bit up/down position counter

- · Count direction status

- Position Measurement (x2 and x4) mode

- Programmable digital noise filters on inputs

- Alternate 16-Bit Timer/Counter mode

- · Quadrature Encoder Interface interrupts

The QEI module's operating mode is determined by setting the appropriate bits, QEIM<2:0> (QEIxCON<10:8>). Figure 17-1 depicts the Quadrature Encoder Interface block diagram.

#### REGISTER 21-10: CiCFG2: ECAN™ BAUD RATE CONFIGURATION REGISTER 2

| U-0             | R/W-x                                                                                                 | U-0                | U-0              | U-0              | R/W-x           | R/W-x            | R/W-x |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|-----------------|------------------|-------|--|--|--|

|                 | WAKFIL                                                                                                | _                  | _                |                  |                 | SEG2PH<2:0>      |       |  |  |  |

| bit 15          |                                                                                                       |                    |                  |                  |                 |                  | bit 8 |  |  |  |

|                 |                                                                                                       |                    |                  |                  |                 |                  |       |  |  |  |

| R/W-x           | R/W-x                                                                                                 | R/W-x              | R/W-x            | R/W-x            | R/W-x           | R/W-x            | R/W-x |  |  |  |

| SEG2PHTS        | SAM                                                                                                   |                    | SEG1PH<2:0       | >                |                 | PRSEG<2:0>       |       |  |  |  |

| bit 7           |                                                                                                       |                    |                  |                  |                 |                  | bit ( |  |  |  |

| Legend:         |                                                                                                       |                    |                  |                  |                 |                  |       |  |  |  |

| R = Readable    | hit                                                                                                   | W = Writable       | hit              | LI – Unimplor    | mented bit, rea | d as '0'         |       |  |  |  |

| -n = Value at F |                                                                                                       | '1' = Bit is set   |                  | '0' = Bit is cle |                 | x = Bit is unkr  |       |  |  |  |

|                 | UK                                                                                                    |                    |                  |                  | aleu            |                  |       |  |  |  |

| bit 15          | Unimplemen                                                                                            | ted: Read as '     | 0'               |                  |                 |                  |       |  |  |  |

| bit 14          | WAKFIL: Se                                                                                            | elect CAN bus I    | ine Filter for V | Vake-up bit      |                 |                  |       |  |  |  |

|                 |                                                                                                       | bus line filter f  |                  | •                |                 |                  |       |  |  |  |

|                 | 0 = CAN bus                                                                                           | line filter is not | used for wak     | e-up             |                 |                  |       |  |  |  |

| bit 13-11       | Unimplemen                                                                                            | ted: Read as '     | 0'               |                  |                 |                  |       |  |  |  |

| bit 10-8        | SEG2PH<2:0                                                                                            | )>: Phase Buff     | er Segment 2     | bits             |                 |                  |       |  |  |  |

|                 | 111 = Length is 8 x TQ                                                                                |                    |                  |                  |                 |                  |       |  |  |  |

|                 | 000 = Length                                                                                          | n is 1 x Tq        |                  |                  |                 |                  |       |  |  |  |

| bit 7           | SEG2PHTS: Phase Segment 2 Time Select bit                                                             |                    |                  |                  |                 |                  |       |  |  |  |

|                 | 1 = Freely pro                                                                                        |                    | its or Informat  | ion Processing   | ı Time (IPT), w | hichever is grea | ter   |  |  |  |

| bit 6           |                                                                                                       |                    |                  |                  | ,               |                  |       |  |  |  |

|                 | <b>SAM:</b> Sample of the CAN bus Line bit<br>1 = Bus line is sampled three times at the sample point |                    |                  |                  |                 |                  |       |  |  |  |

|                 |                                                                                                       | s sampled onc      |                  |                  |                 |                  |       |  |  |  |