Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                 |

| Number of I/O              | 53                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 16x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-VFQFN Exposed Pad                                                               |

| Supplier Device Package    | 64-VQFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc706at-i-mr |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXMCX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's *Reference Manual*" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXMCX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXMCX06A/X08A/X10A devices are a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF)

- 2. Signed or unsigned DSP multiply (US)

- 3. Conventional or convergent rounding (RND)

- 4. Automatic saturation on/off for AccA (SATA)

- 5. Automatic saturation on/off for AccB (SATB)

- 6. Automatic saturation on/off for writes to data memory (SATDW)

- 7. Accumulator Saturation mode selection (ACCSAT)

Table 2-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

| SUMMARY     |                         |                   |  |  |  |  |  |  |

|-------------|-------------------------|-------------------|--|--|--|--|--|--|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |  |  |  |  |  |  |

| CLR         | A = 0                   | Yes               |  |  |  |  |  |  |

| ED          | $A = (x - y)^2$         | No                |  |  |  |  |  |  |

| EDAC        | $A = A + (x - y)^2$     | No                |  |  |  |  |  |  |

| MAC         | $A = A + (x \bullet y)$ | Yes               |  |  |  |  |  |  |

| MAC         | $A = A + x^2$           | No                |  |  |  |  |  |  |

| MOVSAC      | No change in A          | Yes               |  |  |  |  |  |  |

| MPY         | $A = x \bullet y$       | No                |  |  |  |  |  |  |

| MPY         | $A = x^2$               | No                |  |  |  |  |  |  |

| MPY.N       | $A = -x \bullet y$      | No                |  |  |  |  |  |  |

| MSC         | $A = A - x \bullet y$   | Yes               |  |  |  |  |  |  |

### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

### 4.2.7 SOFTWARE STACK

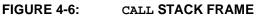

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXMCX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSb |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33FJXXXMCX06A/X08A/X10A devices support data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-36 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the following form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (i.e., the addressing mode can only be Register Direct) which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

| Note: | Not all instructions support all the   |

|-------|----------------------------------------|

|       | addressing modes given above. Individ- |

|       | ual instructions may support different |

|       | subsets of these addressing modes.     |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit                                             |

|-------|--------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit                                                           |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>    |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit                                                          |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>    |

| U-0          | R/W-1                                                      | R/W-0                         | R/W-0          | U-0                | U-0             | U-0             | U-0   |  |  |

|--------------|------------------------------------------------------------|-------------------------------|----------------|--------------------|-----------------|-----------------|-------|--|--|

| _            |                                                            | CNIP<2:0>                     |                | —                  |                 | —               |       |  |  |

| bit 15       |                                                            |                               |                |                    |                 |                 | bit 8 |  |  |

|              |                                                            |                               |                |                    |                 |                 |       |  |  |

| U-0          | R/W-1                                                      | R/W-0<br>MI2C1IP<2:0>         | R/W-0          | U-0                | R/W-1           | R/W-0           | R/W-0 |  |  |

|              |                                                            |                               | SI2C1IP<2:0>   |                    |                 |                 |       |  |  |

| bit 7        |                                                            |                               |                |                    |                 |                 | bit ( |  |  |

| Legend:      |                                                            |                               |                |                    |                 |                 |       |  |  |

| R = Readab   | le bit                                                     | W = Writable                  | bit            | U = Unimplei       | mented bit, rea | d as '0'        |       |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set              |                | '0' = Bit is cle   | eared           | x = Bit is unkr | nown  |  |  |

|              |                                                            |                               |                |                    |                 |                 |       |  |  |

| bit 15       | -                                                          | nented: Read as 'o            |                |                    |                 |                 |       |  |  |

| bit 14-12    |                                                            | >: Change Notifica            | -              | -                  |                 |                 |       |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                               |                |                    |                 |                 |       |  |  |

|              | •                                                          |                               |                |                    |                 |                 |       |  |  |

|              | •                                                          | •                             |                |                    |                 |                 |       |  |  |

|              |                                                            | errupt is priority 1          |                |                    |                 |                 |       |  |  |

|              | 000 = Inte                                                 | errupt source is dis          | abled          |                    |                 |                 |       |  |  |

| bit 11-7     | Unimplem                                                   | nented: Read as 'o            | כ'             |                    |                 |                 |       |  |  |

| bit 6-4      | MI2C1IP<                                                   | 2:0>: I2C1 Master             | Events Inter   | rupt Priority bits | S               |                 |       |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                               |                |                    |                 |                 |       |  |  |

|              | •                                                          |                               |                |                    |                 |                 |       |  |  |

|              | •                                                          |                               |                |                    |                 |                 |       |  |  |

|              | 001 = Inte                                                 | 001 = Interrupt is priority 1 |                |                    |                 |                 |       |  |  |

|              | 000 = Interrupt source is disabled                         |                               |                |                    |                 |                 |       |  |  |

| bit 3        | Unimplem                                                   | nented: Read as 'o            | כ'             |                    |                 |                 |       |  |  |

| bit 2-0      | SI2C1IP<                                                   | 2:0>: I2C1 Slave E            | Events Interru | pt Priority bits   |                 |                 |       |  |  |

|              | 111 = Inte                                                 | errupt is priority 7 (I       | highest priori | ty interrupt)      |                 |                 |       |  |  |

|              | •                                                          |                               |                |                    |                 |                 |       |  |  |

|              | •                                                          |                               |                |                    |                 |                 |       |  |  |

|              | -<br>001 - Inte                                            |                               |                |                    |                 |                 |       |  |  |

|              |                                                            | errupt is priority 1          |                |                    |                 |                 |       |  |  |

### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| REGISTER 7-26: IPC11: INTERRUPT PRIC | ORITY CONTROL REGISTER 11 |

|--------------------------------------|---------------------------|

|--------------------------------------|---------------------------|

| U-0          | R/W-1                                                                 | R/W-0              | R/W-0        | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|--------------|-----------------------------------------------------------------------|--------------------|--------------|------------------|------------------|-----------------|-------|--|--|--|

|              |                                                                       | T6IP<2:0>          |              |                  |                  | DMA4IP<2:0>     |       |  |  |  |

| bit 15       |                                                                       |                    |              |                  |                  |                 | bit 8 |  |  |  |

| U-0          | U-0                                                                   | U-0                | U-0          | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |

| _            |                                                                       | _                  | _            | _                |                  | OC8IP<2:0>      |       |  |  |  |

| bit 7        |                                                                       |                    |              |                  | I                |                 | bit   |  |  |  |

|              |                                                                       |                    |              |                  |                  |                 |       |  |  |  |

| Legend:      |                                                                       |                    |              |                  |                  |                 |       |  |  |  |

| R = Readab   |                                                                       | W = Writable I     | oit          | -                | mented bit, read |                 |       |  |  |  |

| -n = Value a | t POR                                                                 | '1' = Bit is set   |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |

|              |                                                                       |                    |              |                  |                  |                 |       |  |  |  |

| bit 15       | -                                                                     | ented: Read as 'o  |              |                  |                  |                 |       |  |  |  |

| bit 14-12    |                                                                       | Timer6 Interrupt   | -            |                  |                  |                 |       |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)            |                    |              |                  |                  |                 |       |  |  |  |

|              |                                                                       |                    |              |                  |                  |                 |       |  |  |  |

|              |                                                                       |                    |              |                  |                  |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1                                         |                    |              |                  |                  |                 |       |  |  |  |

|              |                                                                       | upt source is disa |              |                  |                  |                 |       |  |  |  |

| bit 11       | -                                                                     | ented: Read as 'o  |              |                  |                  |                 |       |  |  |  |

| bit 10-8     |                                                                       | 0>: DMA Channe     |              | -                | Interrupt Prior  | ity bits        |       |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre> |                    |              |                  |                  |                 |       |  |  |  |

|              | •                                                                     |                    |              |                  |                  |                 |       |  |  |  |

|              | •                                                                     |                    |              |                  |                  |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1                                         |                    |              |                  |                  |                 |       |  |  |  |

|              | 000 = Interr                                                          | upt source is disa | abled        |                  |                  |                 |       |  |  |  |

| bit 7-3      | Unimpleme                                                             | ented: Read as '0  | )'           |                  |                  |                 |       |  |  |  |

| bit 2-0      | OC8IP<2:0                                                             | : Output Compa     | re Channel 8 | Interrupt Prior  | ity bits         |                 |       |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)            |                    |              |                  |                  |                 |       |  |  |  |

|              | •                                                                     |                    |              |                  |                  |                 |       |  |  |  |

|              | •                                                                     |                    |              |                  |                  |                 |       |  |  |  |

|              | •                                                                     |                    |              |                  |                  |                 |       |  |  |  |

|              | •<br>001 = Interr                                                     | upt is priority 1  |              |                  |                  |                 |       |  |  |  |

| U-0                          | U-0                                                                                              | U-0                                                  | U-0           | R-0               | R-0           | R-0             | R-0   |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------|-------------------|---------------|-----------------|-------|--|--|--|

|                              | _                                                                                                | _                                                    | _             |                   | ILF           | <3:0>           |       |  |  |  |

| oit 15                       |                                                                                                  | 1                                                    |               |                   |               |                 | bit 8 |  |  |  |

|                              |                                                                                                  |                                                      |               |                   |               |                 |       |  |  |  |

| U-0                          | R-0                                                                                              | R-0                                                  | R-0           | R-0               | R-0           | R-0             | R-0   |  |  |  |

| —                            |                                                                                                  |                                                      |               | VECNUM<6:0>       | >             |                 |       |  |  |  |

| oit 7                        |                                                                                                  |                                                      |               |                   |               |                 | bit ( |  |  |  |

|                              |                                                                                                  |                                                      |               |                   |               |                 |       |  |  |  |

| <b>₋egend:</b><br>R = Readab | la hit                                                                                           | W = Writable                                         | h:t           |                   | opted bit rec | ad aa (0)       |       |  |  |  |

|                              |                                                                                                  |                                                      |               | U = Unimplem      |               |                 |       |  |  |  |

| n = Value a                  | IPOR                                                                                             | '1' = Bit is set                                     |               | '0' = Bit is clea | ared          | x = Bit is unkr | IOWN  |  |  |  |

| oit 15-12                    | Unimpleme                                                                                        | ented: Read as the                                   | 0'            |                   |               |                 |       |  |  |  |

| pit 11-8                     | •                                                                                                | ILR<3:0>: New CPU Interrupt Priority Level bits      |               |                   |               |                 |       |  |  |  |

|                              | 1111 = CPU interrupt priority level is 15                                                        |                                                      |               |                   |               |                 |       |  |  |  |

|                              | •                                                                                                |                                                      |               |                   |               |                 |       |  |  |  |

|                              | •                                                                                                |                                                      |               |                   |               |                 |       |  |  |  |

|                              | •<br>0001 = CPU interrupt priority level is 1                                                    |                                                      |               |                   |               |                 |       |  |  |  |

|                              |                                                                                                  | J interrupt priorit                                  |               |                   |               |                 |       |  |  |  |

| oit 7                        | Unimpleme                                                                                        | ented: Read as '                                     | 0'            |                   |               |                 |       |  |  |  |

| oit 6-0                      | VECNUM<                                                                                          | VECNUM<6:0>: Vector Number of Pending Interrupt bits |               |                   |               |                 |       |  |  |  |

|                              |                                                                                                  | Interrupt vector                                     |               | •                 |               |                 |       |  |  |  |

|                              | •                                                                                                |                                                      | Ū             |                   |               |                 |       |  |  |  |

|                              | •                                                                                                |                                                      |               |                   |               |                 |       |  |  |  |

|                              | •                                                                                                | Interrupt vector                                     | nondina in nu | mbor 0            |               |                 |       |  |  |  |

|                              | 0000001 = Interrupt vector pending is number 9<br>0000000 = Interrupt vector pending is number 8 |                                                      |               |                   |               |                 |       |  |  |  |

### REGISTER 7-33: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

NOTES:

| REGISTEF     |              | R/W-0                     |                       |                   |                |                | U-0                  |

|--------------|--------------|---------------------------|-----------------------|-------------------|----------------|----------------|----------------------|

|              | R/W-0        |                           | R/W-0                 | U-0               | U-0            | U-0            | 0-0                  |

| T9MD         | T8MD         | T7MD                      | T6MD                  |                   |                | —              |                      |

| bit 15       |              |                           |                       |                   |                |                | bit                  |

|              |              |                           |                       |                   |                |                |                      |

| U-0          | U-0          | U-0                       | U-0                   | U-0               | U-0            | R/W-0          | R/W-0                |

|              | —            | —                         |                       | —                 |                | I2C2MD         | AD2MD <sup>(1)</sup> |

| bit 7        |              |                           |                       |                   |                |                | bit                  |

| Legend:      |              |                           |                       |                   |                |                |                      |

| R = Readal   | ble bit      | W = Writable              | bit                   | U = Unimplem      | ented bit. rea | id as '0'      |                      |

| -n = Value a | at POR       | '1' = Bit is set          |                       | '0' = Bit is clea |                | x = Bit is unk | nown                 |

|              |              |                           |                       |                   |                |                |                      |

| bit 15       | T9MD: Timer  | 9 Module Disal            | ole bit               |                   |                |                |                      |

|              | 1 = Timer9 m | Timer9 module is disabled |                       |                   |                |                |                      |

|              | 0 = Timer9 m | module is enabled         |                       |                   |                |                |                      |

| bit 14       | T8MD: Timer8 | 3 Module Disat            | ole bit               |                   |                |                |                      |

|              | 1 = Timer8 m | odule is disable          | ed                    |                   |                |                |                      |

|              | 0 = Timer8 m | odule is enable           | ed                    |                   |                |                |                      |

| bit 13       | T7MD: Timer7 | 7 Module Disal            | ole bit               |                   |                |                |                      |

|              |              | odule is disable          |                       |                   |                |                |                      |

|              | 0 = Timer7 m | odule is enable           | ed                    |                   |                |                |                      |

| bit 12       | T6MD: Timer6 | 6 Module Disat            | ole bit               |                   |                |                |                      |

|              |              | odule is disable          |                       |                   |                |                |                      |

|              | 0 = Timer6 m | odule is enable           | ed                    |                   |                |                |                      |

| bit 11-2     | Unimplement  | ted: Read as '            | 0'                    |                   |                |                |                      |

| bit 1        | 12C2MD: 12C2 | 2 Module Disat            | ole bit               |                   |                |                |                      |

|              |              | ule is disabled           |                       |                   |                |                |                      |

|              | 0 = I2C2 mod |                           |                       |                   |                |                |                      |

| bit 0        | AD2MD: AD2   | Module Disab              | le bit <sup>(1)</sup> |                   |                |                |                      |

|              | 1 = AD2 modu |                           |                       |                   |                |                |                      |

|              | 0 = AD2 modu | ile is enabled            |                       |                   |                |                |                      |

**Note 1:** The PCFGx bits have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

### REGISTER 17-2: DFLTxCON: DIGITAL FILTER x CONTROL REGISTER

|                | U-0                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                                                                                                     | U-0                                                                                                    | R/W-0                                                                 | R/W-0           | R/W-0 |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------|-------|--|--|--|--|

| —              | —                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                       | —                                                                                                      | IMV<                                                                  | 2:0>            | CEID  |  |  |  |  |

| bit 15         |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                 | bit 8 |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

| R/W-0          |                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                         | U-0                                                                                                    | U-0                                                                   | U-0             | U-0   |  |  |  |  |

| QEOUT          |                                                                                                                                                                                                                                                                                                   | QECK<2:0>                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         | —                                                                                                      | —                                                                     | —               | —     |  |  |  |  |

| bit 7          |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                 | bit   |  |  |  |  |

| Legend:        |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

| R = Readab     | le bit                                                                                                                                                                                                                                                                                            | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                            | oit                                                                                                                                                     | U = Unimple                                                                                            | mented bit, read                                                      | as '0'          |       |  |  |  |  |

| -n = Value a   | It POR                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         | '0' = Bit is cle                                                                                       | eared                                                                 | x = Bit is unkn | nown  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

| bit 15-11      | Unimplemen                                                                                                                                                                                                                                                                                        | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                           | )'                                                                                                                                                      |                                                                                                        |                                                                       |                 |       |  |  |  |  |

| bit 10-9       | IMV<1:0>: Inc                                                                                                                                                                                                                                                                                     | dex Match Valu                                                                                                                                                                                                                                                                                                                                                                                            | e bits                                                                                                                                                  |                                                                                                        |                                                                       |                 |       |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                   | These bits allow the user to specify the state of the QEAx and QEBx input pins during an index pulse                                                                                                                                                                                                                                                                                                      |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                   | when the POSxCNT register is to be reset.                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                   | In 4X Quadrature Count Mode:                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

|                | IMV1 = Required state of Phase B input signal for match on index pulse<br>IMV0 = Required state of Phase A input signal for match on index pulse                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

|                | T = D = D                                                                                                                                                                                                                                                                                         | and state of Db                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                 |       |  |  |  |  |

|                | -                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                           | ase A input s                                                                                                                                           |                                                                                                        |                                                                       |                 |       |  |  |  |  |

|                | In 2X Quadra                                                                                                                                                                                                                                                                                      | ture Count Mod                                                                                                                                                                                                                                                                                                                                                                                            | ase A input s<br><u>le:</u>                                                                                                                             | signal for match                                                                                       | n on index pulse                                                      |                 |       |  |  |  |  |

|                | In 2X Quadra                                                                                                                                                                                                                                                                                      | ture Count Moc<br>ts phase input :                                                                                                                                                                                                                                                                                                                                                                        | ase A input s<br><u>le:</u><br>signal for ind                                                                                                           | signal for match                                                                                       |                                                                       | _ = Phase B)    |       |  |  |  |  |

| bit 8          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ                                                                                                                                                                                                                                                       | ture Count Moc<br>ts phase input :                                                                                                                                                                                                                                                                                                                                                                        | ase A input s<br>l <u>e:</u><br>signal for ind<br>selected Ph                                                                                           | signal for match                                                                                       | n on index pulse<br>(0 = Phase A, 1                                   | _ = Phase B)    |       |  |  |  |  |

| bit 8          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count                                                                                                                                                                                                                                        | ture Count Moc<br>ts phase input s<br>red state of the                                                                                                                                                                                                                                                                                                                                                    | ase A input s<br>l <u>e:</u><br>signal for ind<br>selected Ph<br>Disable bit                                                                            | signal for match<br>lex state match<br>nase input signa                                                | n on index pulse<br>(0 = Phase A, 1                                   | _ = Phase B)    |       |  |  |  |  |

| bit 8          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts                                                                                                                                                                                                                      | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I                                                                                                                                                                                                                                                                                                                               | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa                                                                         | signal for match<br>lex state match<br>nase input signa<br>abled                                       | n on index pulse<br>(0 = Phase A, 1                                   | _ = Phase B)    |       |  |  |  |  |

|                | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts                                                                                                                                                                                                    | ture Count Mod<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e                                                                                                                                                                                                                                                                                                             | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena                                                        | signal for match<br>lex state match<br>nase input signa<br>abled<br>abled                              | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir             | _ = Phase B)    |       |  |  |  |  |

| bit 8<br>bit 7 | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA                                                                                                                                                                                      | ture Count Mod<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e                                                                                                                                                                                                                                                                                           | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F                                       | signal for match<br>lex state match<br>nase input signa<br>abled<br>abled                              | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir             | _ = Phase B)    |       |  |  |  |  |

|                | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte                                                                                                                                                                 | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx                                                                                                                                                                                                                                                                           | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led                                | signal for match<br>lex state match<br>nase input signa<br>abled<br>abled<br>Filter Output En          | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir             | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte                                                                                                                                            | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab                                                                                                                                                                                                                                                        | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte                                                                                                                                            | ture Count Mod<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN                                                                                                                                                                                                                    | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:                                                                                                                              | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide                                                                                                                                                                                                                      | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 c                                                                                                             | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide                                                                                                                                                                                                    | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Seleci<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 c<br>110 = 1:128 c<br>101 = 1:64 cle<br>100 = 1:32 cle                                                       | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>clock divide<br>pock divide                                                                                                                                                                     | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

|                | In 2X Quadra<br>IMV1 = Select<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 ct<br>101 = 1:128 ct<br>101 = 1:32 ct<br>011 = 1:16 ct                                                       | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>clock divide<br>ock divide<br>ock divide                                                                                                                                                        | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Select<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 ct<br>101 = 1:128 ct<br>101 = 1:32 ct<br>011 = 1:16 ct<br>010 = 1:4 cto                                      | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>bock divide<br>bock divide<br>bock divide<br>bock divide<br>bock divide                                                                                                                         | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Select<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 ct<br>101 = 1:128 ct<br>101 = 1:32 ct<br>011 = 1:16 ct<br>010 = 1:4 cto<br>001 = 1:2 cto                     | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>bock divide | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |

| bit 7          | In 2X Quadra<br>IMV1 = Select<br>IMV0 = Requ<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 ct<br>100 = 1:32 ct<br>011 = 1:16 ct<br>010 = 1:4 cto<br>001 = 1:2 cto<br>000 = 1:1 cto | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>bock divide | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>Ded (normal<br>IDXx Digital | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B)    |       |  |  |  |  |