Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc708a-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

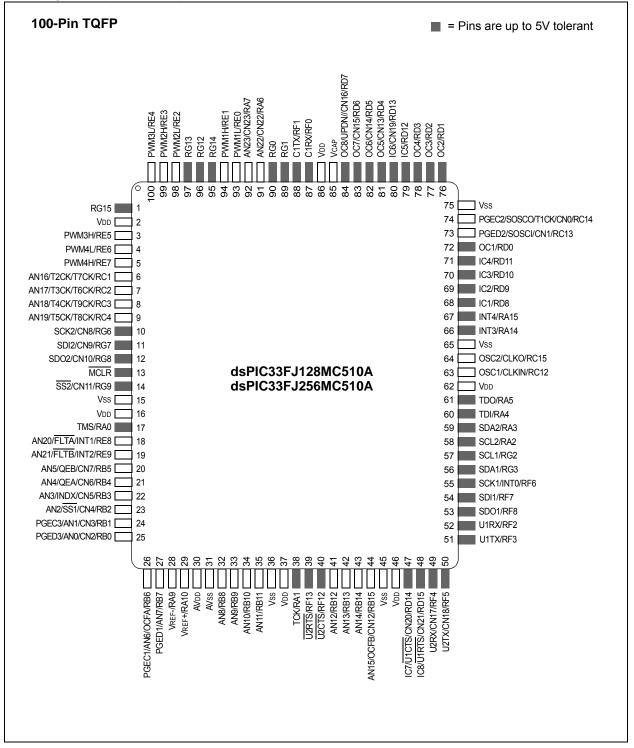

#### **Pin Diagrams (Continued)**

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| TABLE 1-1:                                         | LE 1-1: PINOUT I/O DESCRIPTIONS  |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|----------------------------------------------------|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name                                           | Pin<br>Type                      | Buffer<br>Type                   | Description                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| AN0-AN31                                           | I                                | Analog                           | Analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| AVdd                                               | Р                                | Р                                | Positive supply for analog modules. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| AVss                                               | Р                                | Р                                | Ground reference for analog modules.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| CLKI<br>CLKO                                       | I<br>O                           | ST/CMOS                          | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated<br>with OSC2 pin function.                                                                                                                                                      |  |  |  |  |  |  |

| CN0-CN23                                           | I                                | ST                               | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| C1RX<br>C1TX                                       | I<br>O                           | ST<br>—                          | ECAN1 bus receive pin.<br>ECAN1 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| C2RX                                               | I                                | ST                               | ECAN2 bus receive pin.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| C2TX                                               | 0                                | _                                | ECAN2 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| PGED1<br>PGEC1<br>PGED2<br>PGEC2<br>PGED3<br>PGEC3 | I/O<br>I<br>I/O<br>I<br>I/O<br>I | ST<br>ST<br>ST<br>ST<br>ST<br>ST | Data I/O pin for Programming/Debugging Communication Channel 1.<br>Clock input pin for Programming/Debugging Communication Channel 1.<br>Data I/O pin for Programming/Debugging Communication Channel 2.<br>Clock input pin for Programming/Debugging Communication Channel 2.<br>Data I/O pin for Programming/Debugging Communication Channel 3.<br>Clock input pin for Programming/Debugging Communication Channel 3. |  |  |  |  |  |  |

| IC1-IC8                                            | 1                                | ST                               | Capture Inputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                    | -                                |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| INDX<br>QEA                                        |                                  | ST<br>ST                         | Quadrature Encoder Index Pulse input.<br>Quadrature Encoder Phase A input in QEI mode. Auxiliary timer external clock<br>gate input in Timer mode.                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| QEB                                                | I                                | ST                               | Quadrature Encoder Phase A input in QEI mode. Auxiliary timer external clock gate input in Timer mode.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| UPDN                                               | 0                                | CMOS                             | Position up/down counter direction state.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| INT0                                               | I                                | ST                               | External Interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| INT1                                               |                                  | ST                               | External Interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| INT2                                               |                                  | ST                               | External Interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| INT3<br>INT4                                       |                                  | ST<br>ST                         | External Interrupt 3.<br>External Interrupt 4.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| FLTA                                               |                                  | ST                               | PWM Fault A input.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| FLTB                                               |                                  | ST                               | PWM Fault B input.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| PWM1L                                              | Ö                                | _                                | PWM1 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| PWM1H                                              | Ō                                | _                                | PWM1 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| PWM2L                                              | 0                                |                                  | PWM2 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| PWM2H                                              | 0                                |                                  | PWM2 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| PWM3L                                              | 0                                | _                                | PWM3 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| PWM3H                                              | 0                                | _                                | PWM3 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| PWM4L                                              | 0                                | _                                | PWM4 low output.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| PWM4H                                              | 0                                | —                                | PWM4 high output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| MCLR                                               | I/P                              | ST                               | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| OCFA                                               | I                                | ST                               | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| OCFB                                               | I                                | ST                               | Compare Fault B input (for Compare Channels 5, 6, 7 and 8).                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| OC1-OC8                                            | 0                                | _                                | Compare outputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| OSC1                                               | I                                | ST/CMOS                          | Oscillator crystal input. ST buffer when configured in RC mode;<br>CMOS otherwise.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| OSC2                                               | I/O                              | -                                | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Legend: CMC                                        | OS = CMO                         | S compatible                     | e input or output Analog = Analog input P = Power                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS compatible input or output Ana ST = Schmitt Trigger input with CMOS levels O =

Analog = Analog input ls O = Output

| U-0             | U-0                         | U-0                                    | R/W-0          | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|-----------------------------|----------------------------------------|----------------|---------------------|------------------|------------------|-------|

| _               |                             | —                                      | US             | EDT <sup>(1)</sup>  |                  | DL<2:0>          |       |

| bit 15          |                             |                                        |                |                     |                  |                  | bit   |

| R/W-0           | R/W-0                       | R/W-1                                  | R/W-0          | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                        | SATDW                                  | ACCSAT         | IPL3 <sup>(2)</sup> | PSV              | RND              | IF    |

| bit 7           |                             |                                        |                |                     | I                |                  | bit ( |

| Legend:         |                             | C = Clearabl                           | a hit          |                     |                  |                  |       |

| R = Readabl     | e bit                       | W = Writable                           |                | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle |                             | 'x = Bit is unk                        |                |                     | mented bit, read |                  |       |

|                 |                             |                                        |                |                     | ,                |                  |       |

| bit 15-13       | -                           | ted: Read as                           |                |                     |                  |                  |       |

| bit 12          |                             | tiply Unsigned                         | •              | ol bit              |                  |                  |       |

|                 | U U                         | ne multiplies a<br>ne multiplies a     | 0              |                     |                  |                  |       |

| bit 11          | •                           | C Loop Termina                         | •              | <sub>oit</sub> (1)  |                  |                  |       |

|                 | •                           | •                                      |                | f current loop it   | eration          |                  |       |

|                 | 0 = No effect               | <b>J</b>                               |                |                     |                  |                  |       |

| bit 10-8        | <b>DL&lt;2:0&gt;:</b> DO    | Loop Nesting                           | Level Status b | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b> | ops active                             |                |                     |                  |                  |       |

|                 | •                           |                                        |                |                     |                  |                  |       |

|                 | 001 = 1 DO lo               | op active                              |                |                     |                  |                  |       |

|                 | 000 <b>= 0</b> DO <b>lo</b> | ops active                             |                |                     |                  |                  |       |

| bit 7           |                             | Saturation Ena                         |                |                     |                  |                  |       |

|                 |                             | ator A saturation<br>ator A saturation |                |                     |                  |                  |       |

| bit 6           |                             | Saturation Ena                         |                |                     |                  |                  |       |

|                 |                             | ator B saturatio                       |                |                     |                  |                  |       |

|                 | 0 = Accumula                | ator B saturation                      | on disabled    |                     |                  |                  |       |

| bit 5           | SATDW: Data                 | a Space Write                          | from DSP Eng   | ine Saturation      | Enable bit       |                  |       |

|                 |                             | ce write satura                        |                |                     |                  |                  |       |

| bit 4           |                             | ce write satura<br>cumulator Satu      |                | Soloct bit          |                  |                  |       |

|                 |                             | ration (super s                        |                |                     |                  |                  |       |

|                 |                             | ration (normal                         |                |                     |                  |                  |       |

| bit 3           | IPL3: CPU In                | terrupt Priority                       | Level Status I | oit 3 <b>(2)</b>    |                  |                  |       |

|                 |                             | rupt priority le                       | U U            |                     |                  |                  |       |

| 1.11.0          |                             | rupt priority le                       |                |                     |                  |                  |       |

| bit 2           | -                           | -                                      | •              | ace Enable bit      |                  |                  |       |

|                 | •                           | space visible i<br>space not visit     | •              | се                  |                  |                  |       |

| bit 1           | -                           | ng Mode Sele                           | -              |                     |                  |                  |       |

|                 |                             | onventional) re                        |                | ed                  |                  |                  |       |

|                 |                             | (convergent)                           | -              |                     |                  |                  |       |

| bit 0           | •                           | Fractional Mu                          | •              |                     |                  |                  |       |

|                 |                             | ode enabled for<br>I mode enable       |                |                     |                  |                  |       |

|                 |                             | i noue enable                          | ייסט ווחו      | upiy ops            |                  |                  |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

NOTES:

All

# TABLE 4-23: ECAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 OR 1 FOR dsPIC33FJXXXMC708A/710A DEVICES File Name Addr Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 2 Bit 11

| File Name  | Addr | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11  | Bit 10    | Bit 9    | Bit 8  | Bit 7    | Bit 6                                       | Bit 5     | Bit 4            | Bit 3   | Bit 2             | Bit 1    | Bit 0  | Resets |

|------------|------|---------|-----------|---------|---------|---------|-----------|----------|--------|----------|---------------------------------------------|-----------|------------------|---------|-------------------|----------|--------|--------|

| C2CTRL1    | 0500 | _       | _         | CSIDL   | ABAT    |         | RI        | EQOP<2:0 | >      | OPN      | /IODE<2:0                                   | >         | — CANCAP — — WIN |         |                   | WIN      | 0480   |        |

| C2CTRL2    | 0502 | _       | —         | —       | _       | _       | —         | _        | _      | —        | —                                           | —         |                  | D       | NCNT<4:0          | >        |        | 0000   |

| C2VEC      | 0504 | _       | —         | —       |         | FI      | LHIT<4:0> |          |        | —        |                                             |           | ICODE<6:0>       |         |                   |          | 0000   |        |

| C2FCTRL    | 0506 | C       | DMABS<2:0 | >       | —       | _       | —         | _        | _      | —        | —                                           | —         | – FSA<4:0>       |         |                   | 0000     |        |        |

| C2FIFO     | 0508 | _       | —         |         |         | FBP<    | 5:0>      |          |        | —        | —                                           | FNRB<5:0> |                  |         |                   | 0000     |        |        |

| C2INTF     | 050A | _       | —         | TXBO    | TXBP    | RXBP    | TXWAR     | RXWAR    | EWARN  | IVRIF    | WAKIF                                       | ERRIF     |                  | FIFOIF  | RBOVIF            | RBIF     | TBIF   | 0000   |

| C2INTE     | 050C | —       | —         | —       | _       | _       | —         | _        | _      | IVRIE    | WAKIE                                       | ERRIE     |                  | FIFOIE  | RBOVIE            | RBIE     | TBIE   | 0000   |

| C2EC       | 050E |         |           |         | TERRCN  | T<7:0>  |           |          |        |          |                                             |           | RERRC            | NT<7:0> |                   |          |        | 0000   |

| C2CFG1     | 0510 | —       | —         | —       | _       | _       | —         | _        | _      | SJW<     | 1:0>                                        |           |                  | BRP     | <5:0>             |          |        | 0000   |

| C2CFG2     | 0512 | —       | WAKFIL    | —       | _       | _       | SE        | G2PH<2:0 | )>     | SEG2PHTS | SAM                                         | SE        | EG1PH<2          | :0>     | P                 | RSEG<2:0 | )>     | 0000   |

| C2FEN1     | 0514 | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10   | FLTEN9   | FLTEN8 | FLTEN7   | FLTEN6                                      | FLTEN5    | FLTEN4           | FLTEN3  | FLTEN2            | FLTEN1   | FLTEN0 | FFFF   |

| C2FMSKSEL1 | 0518 | F7MSł   | <<1:0>    | F6MSI   | K<1:0>  | F5MSI   | <<1:0>    | F4MSI    | <<1:0> | F3MSK    | F3MSK<1:0> F2MSK<1:0> F1MSK<1:0> F0MSK<1:0> |           |                  | K<1:0>  | 0000              |          |        |        |

| C2FMSKSEL2 | 051A | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS   | K<1:0>    | F12MS    | K<1:0> | F11MSK   | <1:0>                                       | F10MS     | K<1:0>           | F9MSł   | <b>&lt;</b> <1:0> | F8MS     | K<1:0> | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: ECAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33FJXXXMC708A/710A DEVICES

| File Name | Addr          | Bit 15  | Bit 14      | Bit 13      | Bit 12     | Bit 11     | Bit 10  | Bit 9       | Bit 8       | Bit 7       | Bit 6       | Bit 5       | Bit 4      | Bit 3      | Bit 2   | Bit 1       | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-------------|-------------|------------|------------|---------|-------------|-------------|-------------|-------------|-------------|------------|------------|---------|-------------|---------|---------------|

|           | 0500-<br>051E |         |             |             |            |            |         | See         | edefinition | when WIN    | = x         |             |            |            |         |             |         |               |

| C2RXFUL1  | 0520          | RXFUL15 | RXFUL14     | RXFUL13     | RXFUL12    | RXFUL11    | RXFUL10 | RXFUL9      | RXFUL8      | RXFUL7      | RXFUL6      | RXFUL5      | RXFUL4     | RXFUL3     | RXFUL2  | RXFUL1      | RXFUL0  | 0000          |

| C2RXFUL2  | 0522          | RXFUL31 | RXFUL30     | RXFUL29     | RXFUL28    | RXFUL27    | RXFUL26 | RXFUL25     | RXFUL24     | RXFUL23     | RXFUL22     | RXFUL21     | RXFUL20    | RXFUL19    | RXFUL18 | RXFUL17     | RXFUL16 | 0000          |

| C2RXOVF1  | 0528          | RXOVF15 | RXOVF14     | RXOVF13     | RXOVF12    | RXOVF11    | RXOVF10 | RXOVF09     | RXOVF08     | RXOVF7      | RXOVF6      | RXOVF5      | RXOVF4     | RXOVF3     | RXOVF2  | RXOVF1      | RXOVF0  | 0000          |

| C2RXOVF2  | 052A          | RXOVF31 | RXOVF30     | RXOVF29     | RXOVF28    | RXOVF27    | RXOVF26 | RXOVF25     | RXOVF24     | RXOVF23     | RXOVF22     | RXOVF21     | RXOVF20    | RXOVF19    | RXOVF18 | RXOVF17     | RXOVF16 | 0000          |

| C2TR01CON | 0530          | TXEN1   | TX<br>ABAT1 | TX<br>LARB1 | TX<br>ERR1 | TX<br>REQ1 | RTREN1  | TX1PRI<1:0> |             | TXEN0       | TX<br>ABAT0 | TX<br>LARB0 | TX<br>ERR0 | TX<br>REQ0 | RTREN0  | TX0PRI<1:0> |         | 0000          |

| C2TR23CON | 0532          | TXEN3   | TX<br>ABAT3 | TX<br>LARB3 | TX<br>ERR3 | TX<br>REQ3 | RTREN3  | TX3PF       | RI<1:0>     | TXEN2       | TX<br>ABAT2 | TX<br>LARB2 | TX<br>ERR2 | TX<br>REQ2 | RTREN2  | TX2PF       | RI<1:0> | 0000          |

| C2TR45CON | 0534          | TXEN5   | TX<br>ABAT5 | TX<br>LARB5 | TX<br>ERR5 | TX<br>REQ5 | RTREN5  | TX5PF       | RI<1:0>     | TXEN4       | TX<br>ABAT4 | TX<br>LARB4 | TX<br>ERR4 | TX<br>REQ4 | RTREN4  | TX4PF       | RI<1:0> | 0000          |

| C2TR67CON | 0536          | TXEN7   | TX<br>ABAT7 | TX<br>LARB7 | TX<br>ERR7 | TX<br>REQ7 | RTREN7  | TX7PRI<1:0> |             | TXEN6       | TX<br>ABAT6 | TX<br>LARB6 | TX<br>ERR6 | TX<br>REQ6 | RTREN6  | TX6PRI<1:0> |         | xxxx          |

| C2RXD     | 0540          |         |             |             |            |            |         | EC          | AN2 Reciev  | ved Data W  | ord         |             |            |            |         |             |         | xxxx          |

| C2TXD     | 0542          |         |             |             |            |            |         | EC          | CAN2 Trans  | mit Data Wo | ord         |             |            |            |         |             |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.6 Interfacing Program and Data Memory Spaces

The dsPIC33FJXXXMCX06A/X08A/X10A architecture uses a 24-bit wide program space and a 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJXXXMCX06A/X08A/X10A architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word of the program word.

#### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full, 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-38 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

#### TABLE 4-38: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        | Program Space Address         |           |                                   |                     |     |  |  |  |  |

|--------------------------|---------------|-------------------------------|-----------|-----------------------------------|---------------------|-----|--|--|--|--|

| Access Type              | Space         | <23>                          | <22:16>   | <15>                              | <14:1>              | <0> |  |  |  |  |

| Instruction Access       | User          | 0                             |           | PC<22:1>                          |                     |     |  |  |  |  |

| (Code Execution)         |               | 0xxx xxxx xxxx xxxx xxxx xxx0 |           |                                   |                     |     |  |  |  |  |

| TBLRD/TBLWT              | User          | TB                            | LPAG<7:0> |                                   | Data EA<15:0>       |     |  |  |  |  |

| (Byte/Word Read/Write)   |               | 0                             | xxx xxxx  | xxxx xx                           | xxxx xxxx xxxx xxxx |     |  |  |  |  |

|                          | Configuration | TB                            | LPAG<7:0> |                                   | Data EA<15:0>       |     |  |  |  |  |

|                          |               | 1                             | xxx xxxx  | xxxx xxxx xxxx xxxx               |                     |     |  |  |  |  |

| Program Space Visibility | User          | 0                             | PSVPAG<   | 7:0> Data EA<14:0> <sup>(1)</sup> |                     |     |  |  |  |  |

| (Block Remap/Read)       |               | 0                             | xxxx xxx  | xxx xxxx xxxx xxxx                |                     |     |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

### 5.2 RTSP Operation

The dsPIC33FJXXXMCX06A/X08A/X10A Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory at a time, which consists of eight rows (512 instructions), and to program one row or one word at a time. Table 26-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundaries.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

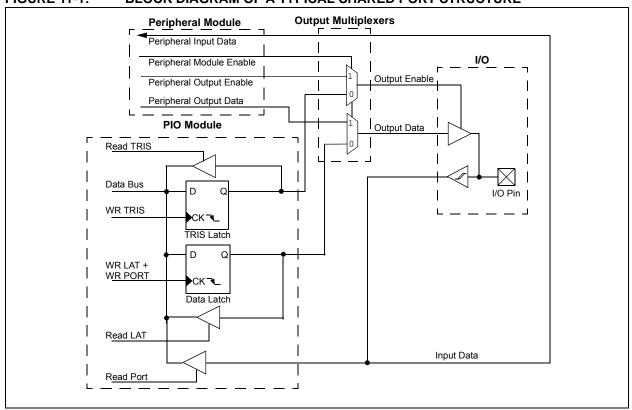

The programming time depends on the FRC accuracy (see Table 26-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the row write time, page erase time and word write cycle time parameters (see Table 26-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `bl11111, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256MCX06A/X08A/X10A devices, this bit is unimplemented and reads back a programmed value.

| R/W-0         | R/W-0          | U-0                              | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |

|---------------|----------------|----------------------------------|------------------|----------------------|------------------|----------------|---------|

| T6IF          | DMA4IF         | _                                | OC8IF            | OC7IF                | OC6IF            | OC5IF          | IC6IF   |

| bit 15        |                |                                  |                  |                      |                  |                | bit 8   |

| R/W-0         | R/W-0          | R/W-0                            | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |

| IC5IF         | IC4IF          | IC3IF                            | DMA3IF           | C1IF                 | C1RXIF           | SPI2IF         | SPI2EIF |

| bit 7         |                |                                  |                  |                      | I                |                | bit (   |

| Legend:       |                |                                  |                  |                      |                  |                |         |

| R = Readable  | e bit          | W = Writable                     | bit              | U = Unimple          | mented bit, read | l as '0'       |         |

| -n = Value at | POR            | '1' = Bit is set                 |                  | '0' = Bit is cle     | eared            | x = Bit is unk | nown    |

| bit 15        | T6IF: Timer6   | Interrupt Flag                   | Status bit       |                      |                  |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 14        |                | •                                |                  | Complete Interi      | rupt Flag Status | bit            |         |

|               |                | request has oc<br>request has no |                  | ·                    |                  |                |         |

| bit 13        |                | ted: Read as '                   |                  |                      |                  |                |         |

| bit 12        | OC8IF: Outpu   | ut Compare Ch                    | annel 8 Interr   | upt Flag Status      | s bit            |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 11        | OC7IF: Outpu   | ut Compare Ch                    | annel 7 Interr   | upt Flag Status      | s bit            |                |         |

|               |                | request has oc                   |                  |                      |                  |                |         |

|               |                | request has no                   |                  |                      |                  |                |         |

| bit 10        | •              | ut Compare Ch                    |                  | upt Flag Status      | s bit            |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 9         | -              | ut Compare Ch                    |                  | upt Flag Status      | s bit            |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 8         |                | Capture Chann                    |                  | -lag Status hit      |                  |                |         |

| bit o         | 1 = Interrupt  | request has oc<br>request has no | curred           | lag Status bit       |                  |                |         |

| bit 7         | •              | Capture Chann                    |                  | -lao Status bit      |                  |                |         |

|               | •              | request has oc                   | •                |                      |                  |                |         |

|               |                | request has no                   |                  |                      |                  |                |         |

| bit 6         | IC4IF: Input C | Capture Chann                    | el 4 Interrupt I | -lag Status bit      |                  |                |         |

|               |                | request has oc                   |                  |                      |                  |                |         |

| bit 5         | -              | request has no<br>Capture Chann  |                  | -<br>Elaa Status hit |                  |                |         |

| bit 5         | 1 = Interrupt  | request has oc<br>request has no | curred           | ay status bit        |                  |                |         |

| bit 4         | •              | •                                |                  | omnlete Inter        | rupt Flag Status | hit            |         |

|               | 1 = Interrupt  | request has oc<br>request has no | curred           |                      | apting Status    | JA             |         |

| bit 3         | -              | l Event Interrup                 |                  | bit                  |                  |                |         |

| Sit U         |                | request has oc                   | -                |                      |                  |                |         |

|               |                | request has no                   |                  |                      |                  |                |         |

#### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| R/W-0         | U-0             | R/W-0                              | U-0             | U-0              | R/W-0            | R/W-0           | R/W-0 |

|---------------|-----------------|------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| FLTAIF        | —               | DMA5IF                             |                 | _                | QEIIF            | PWMIF           | C2IF  |

| bit 15        |                 | •                                  |                 | ÷                |                  |                 | bit 8 |

| R/W-0         | R/W-0           | R/W-0                              | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| C2RXIF        | INT4IF          | INT3IF                             | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |

| bit 7         |                 |                                    |                 |                  |                  | 0.202           | bit C |

| Legend:       |                 |                                    |                 |                  |                  |                 |       |

| R = Readabl   | e bit           | W = Writable                       | bit             | U = Unimplei     | mented bit, read | d as '0'        |       |

| -n = Value at | POR             | '1' = Bit is set                   |                 | '0' = Bit is cle | eared            | x = Bit is unkn | iown  |

|               |                 |                                    |                 |                  |                  |                 |       |

| bit 15        | FLTAIF: PWN     | / Fault A Interr                   | upt Flag Statu  | us bit           |                  |                 |       |

|               |                 | request has oc                     |                 |                  |                  |                 |       |

|               | •               | request has no                     |                 |                  |                  |                 |       |

| bit 14        | -               | ted: Read as '                     |                 |                  |                  |                 |       |

| bit 13        |                 |                                    |                 | Complete Interr  | rupt Flag Status | bit             |       |

|               |                 | request has oco<br>request has not |                 |                  |                  |                 |       |

| bit 12-11     | •               | ted: Read as '                     |                 |                  |                  |                 |       |

| bit 10        | -               | vent Interrupt F                   |                 |                  |                  |                 |       |

|               |                 | request has oc                     | 0               |                  |                  |                 |       |

|               |                 | request has not                    |                 |                  |                  |                 |       |

| bit 9         | PWMIF: PWN      | A Interrupt Flag                   | Status bit      |                  |                  |                 |       |

|               |                 | request has occ<br>request has not |                 |                  |                  |                 |       |

| bit 8         | C2IF: ECAN2     | 2 Event Interrup                   | t Flag Status   | bit              |                  |                 |       |

|               | •               | request has oc                     |                 |                  |                  |                 |       |

|               | 0 = Interrupt r | request has not                    | occurred        |                  |                  |                 |       |

| bit 7         |                 | N2 Receive D                       | •               | errupt Flag Sta  | itus bit         |                 |       |

|               | •               | request has oco<br>request has not |                 |                  |                  |                 |       |

| bit 6         | =               | nal Interrupt 4                    |                 | it               |                  |                 |       |

|               |                 | request has oc                     | -               | it.              |                  |                 |       |

|               |                 | request has not                    |                 |                  |                  |                 |       |

| bit 5         | INT3IF: Exter   | mal Interrupt 3                    | Flag Status b   | it               |                  |                 |       |

|               |                 | request has oc                     |                 |                  |                  |                 |       |

|               | -               | request has not                    |                 |                  |                  |                 |       |

| bit 4         |                 | Interrupt Flag                     |                 |                  |                  |                 |       |

|               | •               | request has oco<br>request has not |                 |                  |                  |                 |       |

| bit 3         | -               | Interrupt Flag                     |                 |                  |                  |                 |       |

|               |                 | request has oc                     |                 |                  |                  |                 |       |

|               | •               | request has not                    |                 |                  |                  |                 |       |

| bit 2         | MI2C2IF: I2C    | 2 Master Even                      | ts Interrupt FI | ag Status bit    |                  |                 |       |

|               |                 | request has oc                     |                 |                  |                  |                 |       |

|               | 0 = Interrupt r | request has not                    | occurred        |                  |                  |                 |       |

#### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

NOTES:

### 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, dsPIC33FJXXXMCX06A/X08A/X10A devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 23.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires the following basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

### 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

<sup>© 2009-2012</sup> Microchip Technology Inc.

### 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 11.1 Parallel I/O (PIO) Ports

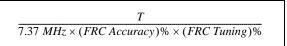

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the

output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

### 16.0 MOTOR CONTROL PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Motor Control PWM" (DS70187) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This module simplifies the task of generating multiple, synchronized Pulse-Width Modulated (PWM) outputs. In particular, the following power and motion control applications are supported by the PWM module:

- · 3-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

The PWM module has the following features:

- Eight PWM I/O pins with four duty cycle generators

- · Up to 16-bit resolution

- 'On-the-fly' PWM frequency changes

- Edge and Center-Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation

- Special Event' comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

- Duty cycle updates are configurable to be immediate or synchronized to the PWM time base

This module contains four duty cycle generators, numbered 1 through 4. The module has eight PWM output pins, numbered PWM1H/PWM1L through PWM4H/PWM4L. The eight I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

The PWM module allows several modes of operation which are beneficial for specific power control applications.

### 21.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

#### 21.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set, and the TXREQ bit is cleared.

### 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

#### 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

#### 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = 111. In this mode, the data which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

#### 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

| U-0          | U-0                                                                                 | U-0                                                                                 | U-0           | U-0              | R/W-0           | R/W-0            | R/W-0   |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------|------------------|-----------------|------------------|---------|--|--|--|--|--|

| _            |                                                                                     |                                                                                     | —             |                  | CH123           | VB<1:0>          | CH123SB |  |  |  |  |  |

| bit 15       |                                                                                     |                                                                                     |               |                  |                 |                  | bit 8   |  |  |  |  |  |

|              |                                                                                     |                                                                                     |               |                  |                 |                  |         |  |  |  |  |  |

| U-0          | U-0                                                                                 | U-0                                                                                 | U-0           | U-0              | R/W-0           | R/W-0            | R/W-0   |  |  |  |  |  |