Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | · ·                                                                               |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc708a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXMCX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's *Reference Manual*" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXMCX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXMCX06A/X08A/X10A devices are a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF)

- 2. Signed or unsigned DSP multiply (US)

- 3. Conventional or convergent rounding (RND)

- 4. Automatic saturation on/off for AccA (SATA)

- 5. Automatic saturation on/off for AccB (SATB)

- 6. Automatic saturation on/off for writes to data memory (SATDW)

- 7. Accumulator Saturation mode selection (ACCSAT)

Table 2-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

#### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

NOTES:

All

# TABLE 4-23: ECAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 OR 1 FOR dsPIC33FJXXXMC708A/710A DEVICES File Name Addr Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 2 Bit 11

| File Name  | Addr | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11  | Bit 10    | Bit 9    | Bit 8  | Bit 7    | Bit 6     | Bit 5  | Bit 4                         | Bit 3     | Bit 2             | Bit 1  | Bit 0  | Resets |

|------------|------|---------|-----------|---------|---------|---------|-----------|----------|--------|----------|-----------|--------|-------------------------------|-----------|-------------------|--------|--------|--------|

| C2CTRL1    | 0500 | _       | _         | CSIDL   | ABAT    |         | RI        | EQOP<2:0 | >      | OPN      | /IODE<2:0 | >      |                               | CANCAP    |                   | _      | WIN    | 0480   |

| C2CTRL2    | 0502 | _       | —         | —       | _       | _       | —         | _        | _      | —        | —         | —      |                               | D         | NCNT<4:0          | >      |        | 0000   |

| C2VEC      | 0504 | _       | —         | —       |         | FI      | LHIT<4:0> |          |        | —        |           |        |                               | ICODE<6:0 | )>                |        |        | 0000   |

| C2FCTRL    | 0506 | C       | DMABS<2:0 | >       | —       | _       | —         | _        | _      | —        | —         | —      |                               |           | FSA<4:0>          |        |        | 0000   |

| C2FIFO     | 0508 | _       | —         |         |         | FBP<    | 5:0>      |          |        | —        | —         |        | FNRB<5:0>                     |           |                   |        | 0000   |        |

| C2INTF     | 050A | _       | —         | TXBO    | TXBP    | RXBP    | TXWAR     | RXWAR    | EWARN  | IVRIF    | WAKIF     | ERRIF  |                               | FIFOIF    | RBOVIF            | RBIF   | TBIF   | 0000   |

| C2INTE     | 050C | —       | —         | —       | _       | _       | —         | _        | _      | IVRIE    | WAKIE     | ERRIE  |                               | FIFOIE    | RBOVIE            | RBIE   | TBIE   | 0000   |

| C2EC       | 050E |         |           |         | TERRCN  | T<7:0>  |           |          |        |          |           |        | RERRC                         | NT<7:0>   |                   |        |        | 0000   |

| C2CFG1     | 0510 | _       | —         | —       | _       | _       | —         | _        | _      | SJW<     | 1:0>      |        |                               | BRP       | <5:0>             |        |        | 0000   |

| C2CFG2     | 0512 | _       | WAKFIL    | —       | _       | _       | SE        | G2PH<2:0 | )>     | SEG2PHTS | SAM       | SE     | SEG1PH<2:0> PRSE              |           | RSEG<2:0          | )>     | 0000   |        |

| C2FEN1     | 0514 | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10   | FLTEN9   | FLTEN8 | FLTEN7   | FLTEN6    | FLTEN5 | FLTEN4                        | FLTEN3    | FLTEN2            | FLTEN1 | FLTEN0 | FFFF   |

| C2FMSKSEL1 | 0518 | F7MSł   | <<1:0>    | F6MSI   | K<1:0>  | F5MSI   | <<1:0>    | F4MSI    | <<1:0> | F3MSK    | <1:0>     | F2MSH  | SK<1:0> F1MSK<1:0> F0MSK<1:0> |           |                   | 0000   |        |        |

| C2FMSKSEL2 | 051A | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS   | K<1:0>    | F12MS    | K<1:0> | F11MSK   | <1:0>     | F10MS  | K<1:0>                        | F9MSł     | <b>&lt;</b> <1:0> | F8MS   | K<1:0> | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-24: ECAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33FJXXXMC708A/710A DEVICES

| File Name | Addr          | Bit 15  | Bit 14                      | Bit 13      | Bit 12     | Bit 11     | Bit 10  | Bit 9   | Bit 8      | Bit 7       | Bit 6       | Bit 5       | Bit 4      | Bit 3      | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-----------------------------|-------------|------------|------------|---------|---------|------------|-------------|-------------|-------------|------------|------------|---------|---------|---------|---------------|

|           | 0500-<br>051E |         | See definition when WIN = x |             |            |            |         |         |            |             |             |             |            |            |         |         |         |               |

| C2RXFUL1  | 0520          | RXFUL15 | RXFUL14                     | RXFUL13     | RXFUL12    | RXFUL11    | RXFUL10 | RXFUL9  | RXFUL8     | RXFUL7      | RXFUL6      | RXFUL5      | RXFUL4     | RXFUL3     | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C2RXFUL2  | 0522          | RXFUL31 | RXFUL30                     | RXFUL29     | RXFUL28    | RXFUL27    | RXFUL26 | RXFUL25 | RXFUL24    | RXFUL23     | RXFUL22     | RXFUL21     | RXFUL20    | RXFUL19    | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C2RXOVF1  | 0528          | RXOVF15 | RXOVF14                     | RXOVF13     | RXOVF12    | RXOVF11    | RXOVF10 | RXOVF09 | RXOVF08    | RXOVF7      | RXOVF6      | RXOVF5      | RXOVF4     | RXOVF3     | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C2RXOVF2  | 052A          | RXOVF31 | RXOVF30                     | RXOVF29     | RXOVF28    | RXOVF27    | RXOVF26 | RXOVF25 | RXOVF24    | RXOVF23     | RXOVF22     | RXOVF21     | RXOVF20    | RXOVF19    | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C2TR01CON | 0530          | TXEN1   | TX<br>ABAT1                 | TX<br>LARB1 | TX<br>ERR1 | TX<br>REQ1 | RTREN1  | TX1PF   | RI<1:0>    | TXEN0       | TX<br>ABAT0 | TX<br>LARB0 | TX<br>ERR0 | TX<br>REQ0 | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C2TR23CON | 0532          | TXEN3   | TX<br>ABAT3                 | TX<br>LARB3 | TX<br>ERR3 | TX<br>REQ3 | RTREN3  | TX3PF   | RI<1:0>    | TXEN2       | TX<br>ABAT2 | TX<br>LARB2 | TX<br>ERR2 | TX<br>REQ2 | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C2TR45CON | 0534          | TXEN5   | TX<br>ABAT5                 | TX<br>LARB5 | TX<br>ERR5 | TX<br>REQ5 | RTREN5  | TX5PF   | RI<1:0>    | TXEN4       | TX<br>ABAT4 | TX<br>LARB4 | TX<br>ERR4 | TX<br>REQ4 | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C2TR67CON | 0536          | TXEN7   | TX<br>ABAT7                 | TX<br>LARB7 | TX<br>ERR7 | TX<br>REQ7 | RTREN7  | TX7PF   | RI<1:0>    | TXEN6       | TX<br>ABAT6 | TX<br>LARB6 | TX<br>ERR6 | TX<br>REQ6 | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C2RXD     | 0540          |         |                             |             |            |            |         | EC      | AN2 Reciev | ved Data W  | ord         |             |            |            |         |         |         | xxxx          |

| C2TXD     | 0542          |         |                             |             |            |            |         | EC      | CAN2 Trans | mit Data Wo | ord         |             |            |            |         |         |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (e.g., [W7+W2]) is used, Modulo Address correction is performed but the contents of the register remain unchanged.

# 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order; thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when the following conditions exist:

- The BWM bits (W register selection) in the MODCON register are any value other than 15 (the stack cannot be accessed using Bit-Reversed Addressing).

- 2. The BREN bit is set in the XBREV register.

- 3. The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is only executed for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data; normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed Addressing should not be enabled |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | together. In the event that the user                                |  |  |  |  |  |  |  |  |  |

|       | attempts to do so, Bit-Reversed Address-                            |  |  |  |  |  |  |  |  |  |

|       | ing will assume priority for the X WAGU,                            |  |  |  |  |  |  |  |  |  |

|       | and X WAGU Modulo Addressing will be                                |  |  |  |  |  |  |  |  |  |

|       | disabled. However, Modulo Addressing will                           |  |  |  |  |  |  |  |  |  |

|       | continue to function in the X RAGU.                                 |  |  |  |  |  |  |  |  |  |

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

# REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 (CONTINUED)

| bit 2 | <b>C1RXIE:</b> ECAN1 Receive Data Ready Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>SPI2IE:</b> SPI2 Event Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled               |

| bit 0 | <b>SPI2EIE:</b> SPI2 Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled              |

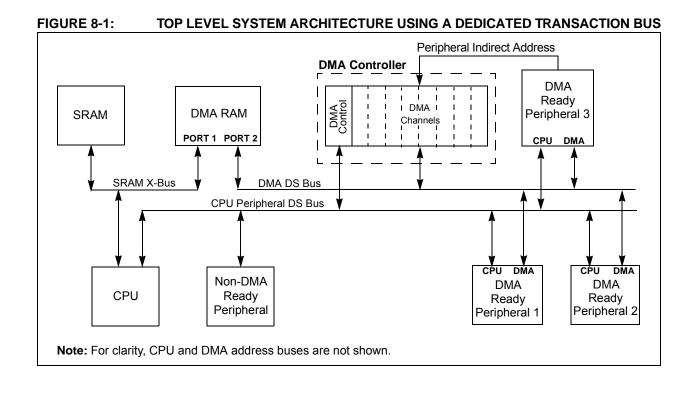

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 22. "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., the UART Receive register and Input Capture 1 buffer) and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers, and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJXXXMCX06A/X08A/X10A peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

### TABLE 8-1: PERIPHERALS WITH DMA SUPPORT

| Peripheral         | IRQ Number |

|--------------------|------------|

| INTO               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels. Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data, either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- · Word or byte-sized data transfers.

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral.

- Indirect Addressing of DMA RAM locations with or without automatic post-increment.

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral.

- One-Shot Block Transfers Terminating DMA transfer after one block transfer.

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete.

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately.

- · Automatic or manual initiation of block transfers.

- Each channel can select from 20 possible sources of data sources or destinations.

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

NOTES:

# 20.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 20.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546066                                        |

#### 20.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 21.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

# 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

# 21.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set, and the TXREQ bit is cleared.

# 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

# 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

# 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = 111. In this mode, the data which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

# 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

| REGISTER     | ZI-J. CIVLO                                                                                                          |                                                                                                                                                                            |                                                                      | CODE REGIS       |                |                 |      |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------|----------------|-----------------|------|--|--|--|--|

| U-0          | U-0                                                                                                                  | U-0                                                                                                                                                                        | R-0                                                                  | R-0              | R-0            | R-0             | R-0  |  |  |  |  |

| —            | —                                                                                                                    | —                                                                                                                                                                          |                                                                      |                  | FILHIT<4:(     | )>              |      |  |  |  |  |

| bit 15       |                                                                                                                      |                                                                                                                                                                            |                                                                      |                  |                |                 | bit  |  |  |  |  |

| U-0          | R-1                                                                                                                  | R-0                                                                                                                                                                        | R-0                                                                  | R-0              | R-0            | R-0             | R-0  |  |  |  |  |

| _            |                                                                                                                      |                                                                                                                                                                            |                                                                      | ICODE<6:0>       | >              |                 |      |  |  |  |  |

| bit 7        |                                                                                                                      |                                                                                                                                                                            |                                                                      |                  |                |                 | bit  |  |  |  |  |

| Legend:      |                                                                                                                      |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

| R = Readab   | le bit                                                                                                               | W = Writable                                                                                                                                                               | bit                                                                  | U = Unimple      | mented bit, re | ad as '0'       |      |  |  |  |  |

| -n = Value a | t POR                                                                                                                | '1' = Bit is set                                                                                                                                                           |                                                                      | '0' = Bit is cle | eared          | x = Bit is unkr | nown |  |  |  |  |

| bit 15-13    | Unimplemen                                                                                                           | ted: Read as '                                                                                                                                                             | )'                                                                   |                  |                |                 |      |  |  |  |  |

| bit 12-8     | -                                                                                                                    | Filter Hit Num                                                                                                                                                             |                                                                      |                  |                |                 |      |  |  |  |  |

|              | 10000-1111<br>01111 <b>= Filte</b>                                                                                   | 1 = Reserved<br>r 15                                                                                                                                                       |                                                                      |                  |                |                 |      |  |  |  |  |

|              | •                                                                                                                    |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

|              | •                                                                                                                    |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

|              | •<br>00001 = Filter 1                                                                                                |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

|              | 00001 = Filte<br>00000 = Filte                                                                                       |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

| bit 7        | Unimplemented: Read as '0'                                                                                           |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

| bit 6-0      | ICODE<6:0>: Interrupt Flag Code bits                                                                                 |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

|              | 1000100 = F<br>1000011 = R                                                                                           |                                                                                                                                                                            | interrupt<br>w interrupt                                             |                  |                |                 |      |  |  |  |  |

|              |                                                                                                                      | 11111 = Rese<br>B15 buffer Inte                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

|              | •                                                                                                                    |                                                                                                                                                                            |                                                                      |                  |                |                 |      |  |  |  |  |

|              | 0001000 = R<br>0000111 = T<br>0000110 = T<br>0000101 = T<br>0000100 = T<br>0000011 = T<br>0000010 = T<br>0000010 = T | B9 buffer intern<br>B8 buffer intern<br>RB7 buffer inter<br>RB6 buffer inte<br>RB5 buffer inte<br>RB4 buffer inte<br>RB3 buffer inte<br>RB2 buffer inte<br>RB1 buffer inte | rrupt<br>rrupt<br>rrupt<br>rrupt<br>rrupt<br>rrupt<br>rrupt<br>rrupt |                  |                |                 |      |  |  |  |  |

# REGISTER 21-3: CiVEC: ECAN™ INTERRUPT CODE REGISTER

### REGISTER 21-22: CiRXFUL1: ECAN™ RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  | •      |        |        | •      |        |        | bit 0  |

| Legend:           |                  | C= Clearable bit      |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

RXFUL15:RXFUL0: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

#### REGISTER 21-23: CIRXFUL2: ECAN™ RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  | C= Clearable bit      |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXFUL31:RXFUL16:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are singleword instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| { }             | Optional field or operation                                                          |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .W              | Word mode selection (default)                                                        |

| Acc             | One of two accumulators {A, B}                                                       |

| AWB             | Accumulator Write-Back Destination Address register ∈ {W13, [W13]+ = 2}              |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0x00000x1FFF}                                               |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4            | 4-bit unsigned literal ∈ {015}                                                       |

| lit5            | 5-bit unsigned literal ∈ {031}                                                       |

| lit8            | 8-bit unsigned literal $\in \{0255\}$                                                |

| lit10           | 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode           |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16           | 16-bit unsigned literal $\in \{065535\}$                                             |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None            | Field does not require an entry, may be blank                                        |

| OA, OB, SA, SB  | DSP Status bits: AccA Overflow, AccB Overflow, AccA Saturate, AccB Saturate          |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register $\in$ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                          |

#### TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

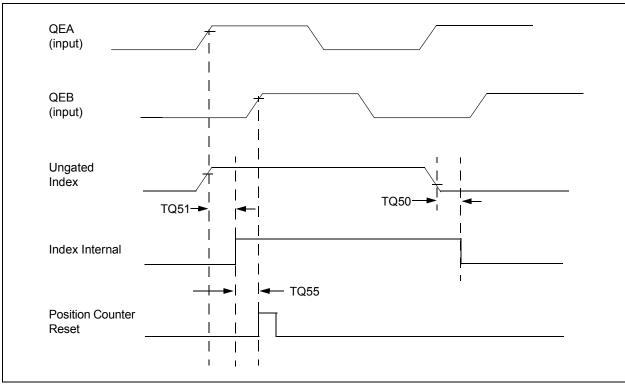

### FIGURE 26-12: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS

#### TABLE 26-30: QEI INDEX PULSE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |  |             |     |       |                                                         |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|-----|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           |  | Min         | Max | Units | Conditions                                              |

| TQ50               | TqiL   | Filter Time to Recognize Low with Digital Filter                                                                                                                                                                                                                                        |  | 3 * N * Tcy | _   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |

| TQ51               | TqiH   | Filter Time to Recognize High with Digital Filter                                                                                                                                                                                                                                       |  | 3 * N * Tcy | —   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |

| TQ55               | Tqidxr | Index Pulse Recognized<br>Counter Reset (ungated i                                                                                                                                                                                                                                      |  | 3 TCY       | _   | ns    | _                                                       |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on falling edge.

| CHARA        | AC<br>CTERISTICS      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     | ,     |            |

|--------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               |     | _   | 35  | ns    | _          |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 25  | —   | —   | ns    | _          |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 25  | —   | —   | ns    | —          |

| HSP51        | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                  | 15  | —   | 55  | ns    | See Note 2 |

#### TABLE 27-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Assumes 50 pF load on all SPIx pins.

#### TABLE 27-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| -            | AC<br>TERISTICS       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |     |       | -          |

|--------------|-----------------------|------------------------------------------------------|-----|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                        | Min | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge            |     |     | 35  | ns    | —          |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input<br>to SCKx Edge        | 25  | _   | _   | ns    | _          |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge         | 25  |     |     | ns    | _          |

| HSP51        | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance               | 15  | _   | 55  | ns    | See Note 2 |

| HSP60        | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge             | _   |     | 55  | ns    | —          |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Assumes 50 pF load on all SPIx pins.

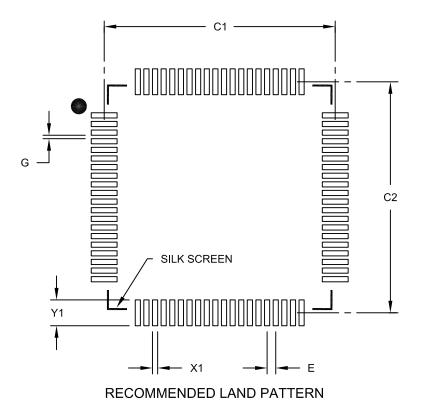

# 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           | MILLIMETERS |      |

|--------------------------|------------------|-----------|-------------|------|

|                          | Dimension Limits | MIN       | NOM         | MAX  |

| Number of Leads          | N                |           | 80          |      |

| Lead Pitch               | е                |           | 0.50 BSC    |      |

| Overall Height           | А                | -         | _           | 1.20 |

| Molded Package Thickness | A2               | 0.95      | 1.00        | 1.05 |

| Standoff                 | A1               | 0.05      | -           | 0.15 |

| Foot Length              | L                | 0.45      | 0.60        | 0.75 |

| Footprint                | L1               |           | 1.00 REF    |      |

| Foot Angle               | ф                | 0°        | 3.5°        | 7°   |

| Overall Width            | E                | 14.00 BSC |             |      |

| Overall Length           | D                | 14.00 BSC |             |      |

| Molded Package Width     | E1               |           | 12.00 BSC   |      |

| Molded Package Length    | D1               | 12.00 BSC |             |      |

| Lead Thickness           | С                | 0.09      | -           | 0.20 |

| Lead Width               | b                | 0.17      | 0.22        | 0.27 |

| Mold Draft Angle Top     | α                | 11°       | 12°         | 13°  |

| Mold Draft Angle Bottom  | β                | 11°       | 12°         | 13°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B

80-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Ν  | <b>/ILLIMETER</b> | S        |      |

|--------------------------|----|-------------------|----------|------|

| Dimension Limits         |    | MIN               | NOM      | MAX  |

| Contact Pitch            | Е  |                   | 0.50 BSC |      |

| Contact Pad Spacing      | C1 |                   | 13.40    |      |

| Contact Pad Spacing      | C2 |                   | 13.40    |      |

| Contact Pad Width (X80)  | X1 |                   |          | 0.30 |

| Contact Pad Length (X80) | Y1 |                   |          | 1.50 |

| Distance Between Pads    | G  | 0.20              |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2092B

# APPENDIX A: MIGRATING FROM dsPIC33FJXXXMCX06/ X08/X10 DEVICES TO dsPIC33FJXXXMCX06A/ X08A/X10A DEVICES

The dsPIC33FJXXXMCX06A/X08A/X10A devices were designed to enhance the dsPIC33FJXXXMCX06/ X08/X10 families of devices.

In general, the dsPIC33FJXXXMCX06A/X08A/X10A devices are backward-compatible with dsPIC33FJXXXMCX06/X08/X10 devices; however, manufacturing differences may cause dsPIC33FJXXXMCX06A/X08A/X10A devices to behave differently from dsPIC33FJXXXMCX06/X08/X10 devices. Therefore, complete system test and characterization is recommended if dsPIC33FJXXXMCX06A/X08A/X10A devices are used to replace dsPIC33FJXXXMCX06/X08/X10 devices.

The following enhancements were introduced:

- Extended temperature support of up to +125°C

- Enhanced Flash module with higher endurance and retention

- New PLL Lock Enable Configuration bit

- Added Timer5 trigger for ADC1 and Timer3 trigger for ADC2

# **Revision C (March 2011)**

This revision includes typographical and formatting changes throughout the data sheet text. In addition, all instances of VDDCORE have been removed.

All other major changes are referenced by their respective section in the following table.

| TABLE D-2. WAJON SECTION OF DATES | TABLE B-2: | MAJOR SECTION UPDATES |

|-----------------------------------|------------|-----------------------|

|-----------------------------------|------------|-----------------------|

| Section Name                                                                        | Update Description                                                                                                                       |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Updated the title of Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)".                                                         |

|                                                                                     | The frequency limitation for device PLL start-up conditions was updated in Section 2.7 "Oscillator Value Conditions on Device Start-up". |

|                                                                                     | The second paragraph in Section 2.9 "Unused I/Os" was updated.                                                                           |

| Section 4.0 "Memory Organization"                                                   | The All Resets values for the following SFRs in the Timer Register<br>Map were changed (see Table 4-6):                                  |

|                                                                                     | • TMR1<br>• TMR2                                                                                                                         |

|                                                                                     | • TMR3                                                                                                                                   |

|                                                                                     | • TMR4                                                                                                                                   |

|                                                                                     | • TMR5                                                                                                                                   |

|                                                                                     | • TMR6                                                                                                                                   |

|                                                                                     | • TMR7                                                                                                                                   |

|                                                                                     | • TMR8                                                                                                                                   |

|                                                                                     | • TMR9                                                                                                                                   |

| Section 9.0 "Oscillator Configuration"                                              | Added Note 3 to the OSCCON: Oscillator Control Register (see Register 9-1).                                                              |

|                                                                                     | Added Note 2 to the CLKDIV: Clock Divisor Register (see Register 9-2).                                                                   |

|                                                                                     | Added Note 1 to the PLLFBD: PLL Feedback Divisor Register (see Register 9-3).                                                            |

|                                                                                     | Added Note 2 to the OSCTUN: FRC Oscillator Tuning Register (see Register 9-4).                                                           |

| Section 22.0 "10-bit/12-bit Analog-to-Digital Converter (ADC)"                      | Updated the VREFL references in the ADC1 module block diagram (see Figure 22-1).                                                         |

| Section 23.0 "Special Features"                                                     | Added a new paragraph and removed the third paragraph in <b>Section 23.1 "Configuration Bits"</b> .                                      |

|                                                                                     | Added the column "RTSP Effects" to the Configuration Bits Descriptions (see Table 23-2).                                                 |

| Timing Specifications                             |     |

|---------------------------------------------------|-----|

| 10-Bit A/D Conversion Requirements                | 328 |

| 12-Bit A/D Conversion Requirements                | 325 |

| CAN I/O Requirements                              | 320 |

| I2Cx Bus Data Requirements (Master Mode)          | 317 |

| I2Cx Bus Data Requirements (Slave Mode)           | 319 |

| Motor Control PWM Requirements                    | 300 |

| Output Compare Requirements 2                     | 298 |

| PLL Clock                                         | 333 |

| QEI External Clock Requirements                   | 303 |

| QEI Index Pulse Requirements                      | 302 |

| Quadrature Decoder Requirements                   | 301 |

| Reset, Watchdog Timer, Oscillator Start-up Timer, |     |

| Power-up Timer and Brown-out                      |     |

| Reset Requirements2                               | 295 |

| Simple OC/PWM Mode Requirements 2                 | 299 |

| Timer1 External Clock Requirements2               | 296 |

| Timer2, Timer4, Timer6 and Timer8 External        |     |

| Clock Requirements2                               | 297 |

| Timer3, Timer5, Timer7 and Timer9                 |     |

| External Clock Requirements2                      | 297 |

|                                                   |     |

#### U

| UART Module<br>UART1 Register Map51<br>UART2 Register Map51 |

|-------------------------------------------------------------|

| V                                                           |

| Voltage Regulator (On-Chip) 264                             |

| W                                                           |

| Watchdog Timer (WDT) 259, 265                               |

| Programming Considerations                                  |

| WWW Address                                                 |

| WWW, On-Line Support 11                                     |