Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| 2000                       |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc710a-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

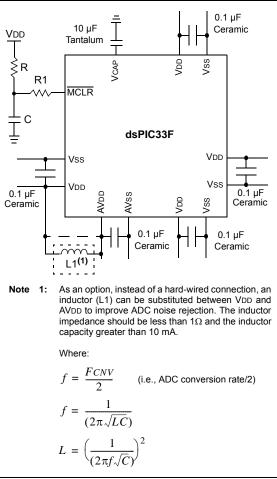

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

# 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 26.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 23.2 "On-Chip Voltage Regulator"** for details.

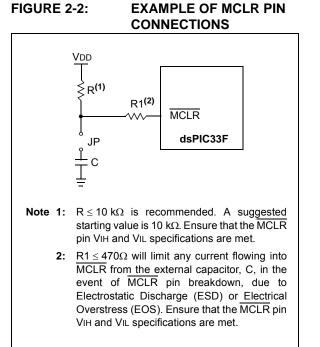

# 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

| U-0             | U-0                              | U-0                                    | R/W-0          | R/W-0               | R-0              | R-0              | R-0   |  |  |  |  |

|-----------------|----------------------------------|----------------------------------------|----------------|---------------------|------------------|------------------|-------|--|--|--|--|

| _               |                                  | —                                      | US             | EDT <sup>(1)</sup>  |                  | DL<2:0>          |       |  |  |  |  |

| bit 15          |                                  |                                        |                |                     |                  |                  | bit   |  |  |  |  |

| R/W-0           | R/W-0                            | R/W-1                                  | R/W-0          | R/C-0               | R/W-0            | R/W-0            | R/W-0 |  |  |  |  |

| SATA            | SATB                             | SATDW                                  | ACCSAT         | IPL3 <sup>(2)</sup> | PSV              | RND              | IF    |  |  |  |  |

| bit 7           |                                  |                                        |                |                     | I                |                  | bit ( |  |  |  |  |

| Legend:         |                                  | C = Clearabl                           | a hit          |                     |                  |                  |       |  |  |  |  |

| R = Readabl     | e bit                            | W = Writable                           |                | -n = Value at       | POR              | '1' = Bit is set |       |  |  |  |  |

| 0' = Bit is cle |                                  | 'x = Bit is unk                        |                |                     | mented bit, read |                  |       |  |  |  |  |

|                 |                                  |                                        |                |                     | ,                |                  |       |  |  |  |  |

| bit 15-13       | -                                | ted: Read as                           |                |                     |                  |                  |       |  |  |  |  |

| bit 12          |                                  | tiply Unsigned                         | •              | ol bit              |                  |                  |       |  |  |  |  |

|                 | U U                              | ne multiplies a<br>ne multiplies a     | 0              |                     |                  |                  |       |  |  |  |  |

| bit 11          | •                                | C Loop Termina                         | •              | <sub>oit</sub> (1)  |                  |                  |       |  |  |  |  |

|                 | •                                | •                                      |                | f current loop it   | eration          |                  |       |  |  |  |  |

|                 | 0 = No effect                    | <b>J</b>                               |                |                     |                  |                  |       |  |  |  |  |

| bit 10-8        | <b>DL&lt;2:0&gt;:</b> DO         | Loop Nesting                           | Level Status b | its                 |                  |                  |       |  |  |  |  |

|                 | 111 <b>= 7</b> DO <b>lo</b>      | ops active                             |                |                     |                  |                  |       |  |  |  |  |

|                 | •                                |                                        |                |                     |                  |                  |       |  |  |  |  |

|                 | 001 = 1 DO lo                    | op active                              |                |                     |                  |                  |       |  |  |  |  |

|                 | 000 <b>= 0</b> DO <b>lo</b>      | ops active                             |                |                     |                  |                  |       |  |  |  |  |

| bit 7           | SATA: AccA Saturation Enable bit |                                        |                |                     |                  |                  |       |  |  |  |  |

|                 |                                  | ator A saturation<br>ator A saturation |                |                     |                  |                  |       |  |  |  |  |

| bit 6           |                                  | Saturation Ena                         |                |                     |                  |                  |       |  |  |  |  |

|                 |                                  | ator B saturatio                       |                |                     |                  |                  |       |  |  |  |  |

|                 | 0 = Accumula                     | ator B saturation                      | on disabled    |                     |                  |                  |       |  |  |  |  |

| bit 5           | SATDW: Data                      | a Space Write                          | from DSP Eng   | ine Saturation      | Enable bit       |                  |       |  |  |  |  |

|                 |                                  | ce write satura                        |                |                     |                  |                  |       |  |  |  |  |

| bit 4           |                                  | ce write satura<br>cumulator Satu      |                | Soloct bit          |                  |                  |       |  |  |  |  |

|                 |                                  | ration (super s                        |                |                     |                  |                  |       |  |  |  |  |

|                 |                                  | ration (normal                         |                |                     |                  |                  |       |  |  |  |  |

| bit 3           | IPL3: CPU In                     | terrupt Priority                       | Level Status I | oit 3 <b>(2)</b>    |                  |                  |       |  |  |  |  |

|                 |                                  | rupt priority le                       | U U            |                     |                  |                  |       |  |  |  |  |

| 1.11.0          |                                  | rupt priority le                       |                |                     |                  |                  |       |  |  |  |  |

| bit 2           | -                                | -                                      | •              | ace Enable bit      |                  |                  |       |  |  |  |  |

|                 | •                                | space visible i<br>space not visit     | •              | се                  |                  |                  |       |  |  |  |  |

| bit 1           | -                                | ng Mode Sele                           | -              |                     |                  |                  |       |  |  |  |  |

|                 |                                  | onventional) re                        |                | ed                  |                  |                  |       |  |  |  |  |

|                 |                                  | (convergent)                           | -              |                     |                  |                  |       |  |  |  |  |

| bit 0           | •                                | Fractional Mu                          | •              |                     |                  |                  |       |  |  |  |  |

|                 |                                  | ode enabled for<br>I mode enable       |                |                     |                  |                  |       |  |  |  |  |

|                 |                                  | i noue enable                          | יווח אפת וחו   | upiy ops            |                  |                  |       |  |  |  |  |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

### TABLE 4-17: ADC1 REGISTER MAP

| File Name               | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11    | Bit 10    | Bit 9   | Bit 8    | Bit 7      | Bit 6     | Bit 5        | Bit 4  | Bit 3  | Bit 2  | Bit 1     | Bit 0   | All<br>Resets |

|-------------------------|------|--------|----------|--------|---------|-----------|-----------|---------|----------|------------|-----------|--------------|--------|--------|--------|-----------|---------|---------------|

| ADC1BUF0                | 0300 |        |          |        |         |           |           |         | ADC1 Dat | a Buffer 0 |           |              |        |        |        |           |         | xxxx          |

| AD1CON1                 | 0320 | ADON   | —        | ADSIDL | ADDMABM | _         | AD12B     | FOR     | M<1:0>   | :          | SSRC<2:0> |              | _      | SIMSAM | ASAM   | SAMP      | DONE    | 0000          |

| AD1CON2                 | 0322 | ,      | VCFG<2:0 | >      | _       | _         | CSCNA     | CHP     | S<1:0>   | BUFS       | _         |              | SMPI   | <3:0>  |        | BUFM      | ALTS    | 0000          |

| AD1CON3                 | 0324 | ADRC   | _        | _      |         | SAMC<4:0> |           |         |          | ADCS<7:0>  |           |              |        |        | 0000   |           |         |               |

| AD1CHS123               | 0326 | _      | _        | _      | _       | _         | CH123N    | VB<1:0> | CH123SB  | _          | _         | _            | _      | _      | CH123I | NA<1:0>   | CH123SA | 0000          |

| AD1CHS0                 | 0328 | CH0NB  | _        | _      |         | С         | H0SB<4:0> | >       |          | CH0NA      | _         | — CH0SA<4:0> |        |        |        | 0000      |         |               |

| AD1PCFGH <sup>(1)</sup> | 032A | PCFG31 | PCFG30   | PCFG29 | PCFG28  | PCFG27    | PCFG26    | PCFG25  | PCFG24   | PCFG23     | PCFG22    | PCFG21       | PCFG20 | PCFG19 | PCFG18 | PCFG17    | PCFG16  | 0000          |

| AD1PCFGL                | 032C | PCFG15 | PCFG14   | PCFG13 | PCFG12  | PCFG11    | PCFG10    | PCFG9   | PCFG8    | PCFG7      | PCFG6     | PCFG5        | PCFG4  | PCFG3  | PCFG2  | PCFG1     | PCFG0   | 0000          |

| AD1CSSH(1)              | 032E | CSS31  | CSS30    | CSS29  | CSS28   | CSS27     | CSS26     | CSS25   | CSS24    | CSS23      | CSS22     | CSS21        | CSS20  | CSS19  | CSS18  | CSS17     | CSS16   | 0000          |

| AD1CSSL                 | 0330 | CSS15  | CSS14    | CSS13  | CSS12   | CSS11     | CSS10     | CSS9    | CSS8     | CSS7       | CSS6      | CSS5         | CSS4   | CSS3   | CSS2   | CSS1      | CSS0    | 0000          |

| AD1CON4                 | 0332 | _      | _        | _      | _       | _         | -         | _       | _        | _          | _         | _            | _      | —      |        | DMABL<2:( | 0>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Not all ANx inputs are available on all devices. Refer to the device pin diagrams for available ANx inputs.

# TABLE 4-18: ADC2 REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11    | Bit 10 | Bit 9   | Bit 8     | Bit 7    | Bit 6     | Bit 5     | Bit 4        | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------|--------|---------|-----------|--------|---------|-----------|----------|-----------|-----------|--------------|--------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340 |        |           |        |         |           |        |         | ADC2 Data | Buffer 0 |           |           |              |        |        |          |         | xxxx          |

| AD2CON1   | 0360 | ADON   | —         | ADSIDL | ADDMABM | _         | AD12B  | FOR     | VI<1:0>   | ;        | SSRC<2:0> | >         | _            | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362 |        | VCFG<2:0> | >      | _       | _         | CSCNA  | CHP     | S<1:0>    | BUFS     | _         |           | SMPI         | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364 | ADRC   | _         | _      |         | SAMC<4:0> |        |         |           |          |           | ADCS<7:0> |              |        |        |          | 0000    |               |

| AD2CHS123 | 0366 | _      | _         | _      | _       | _         | CH123N | IB<1:0> | CH123SB   | _        | _         | _         | _            | _      | CH123N | NA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368 | CH0NB  | _         | _      | _       |           | CH0S   | B<3:0>  |           | CH0NA    | _         | _         | — CH0SA<3:0> |        |        |          | 0000    |               |

| Reserved  | 036A |        | _         |        | —       |           | —      |         |           |          |           | —         | —            | _      |        | —        | —       | 0000          |

| AD2PCFGL  | 036C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11    | PCFG10 | PCFG9   | PCFG8     | PCFG7    | PCFG6     | PCFG5     | PCFG4        | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E |        | _         |        | —       |           | —      |         |           |          |           | —         | —            | _      |        | —        | —       | 0000          |

| AD2CSSL   | 0370 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11     | CSS10  | CSS9    | CSS8      | CSS7     | CSS6      | CSS5      | CSS4         | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372 | _      | _         | _      | _       | _         | _      | _       | _         | _        | _         | _         | _            | _      |        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

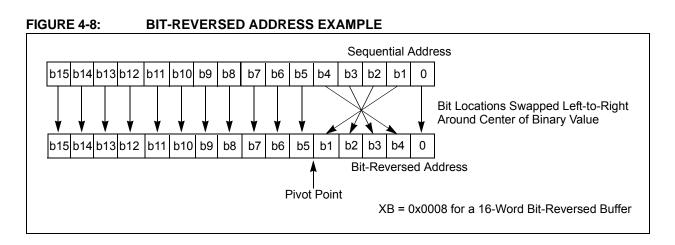

# TABLE 4-37: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXMCX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and

three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data by blocks (or 'rows') of 64 instructions (192 bytes) at a time or by single program memory word; the user can erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

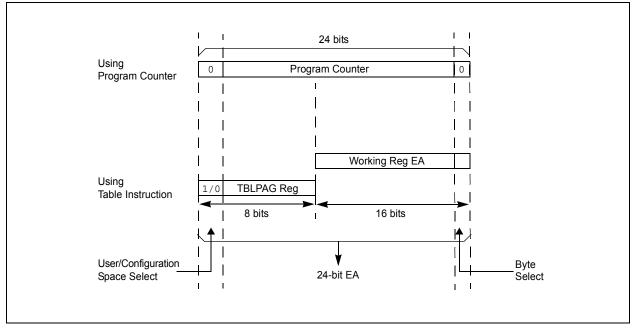

# 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

# FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| U-0           | R/W-0                                                                                         | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------|-----------------|-----------------|--------|--|--|--|--|

| —             | DMA1IF                                                                                        | AD1IF                            | U1TXIF           | U1RXIF            | SPI1IF          | SPI1EIF         | T3IF   |  |  |  |  |

| bit 15        |                                                                                               |                                  |                  |                   |                 |                 | bit 8  |  |  |  |  |

| R/W-0         | R/W-0                                                                                         | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

| T2IF          | OC2IF                                                                                         | IC2IF                            | DMA01IF          | T1IF              | OC1IF           | IC1IF           | INT0IF |  |  |  |  |

| bit 7         | L.                                                                                            |                                  |                  |                   |                 |                 | bit (  |  |  |  |  |

| Legend:       |                                                                                               |                                  |                  |                   |                 |                 |        |  |  |  |  |

| R = Readable  | e bit                                                                                         | W = Writable                     | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |  |  |  |  |

| -n = Value at | POR                                                                                           | '1' = Bit is se                  | t                | '0' = Bit is clea | ared            | x = Bit is unkn | iown   |  |  |  |  |

| bit 15        | Unimplemen                                                                                    | ted: Read as                     | ʻ0'              |                   |                 |                 |        |  |  |  |  |

| bit 14        | -                                                                                             |                                  | ata Transfer C   | omplete Interro   | upt Flag Status | s bit           |        |  |  |  |  |

|               |                                                                                               | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | •                                                                                             | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 13        |                                                                                               |                                  | Complete Interr  | upt Flag Status   | s bit           |                 |        |  |  |  |  |

|               |                                                                                               | request has oc<br>request has no |                  |                   |                 |                 |        |  |  |  |  |

| bit 12        | •                                                                                             |                                  | r Interrupt Flag | g Status bit      |                 |                 |        |  |  |  |  |

|               |                                                                                               | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | -                                                                                             | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 11        | <b>U1RXIF:</b> UART1 Receiver Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               |                                                                                               | request has oc<br>request has no |                  |                   |                 |                 |        |  |  |  |  |

| bit 10        | •                                                                                             | •                                | ot Flag Status b | oit               |                 |                 |        |  |  |  |  |

|               |                                                                                               | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | -                                                                                             | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 9         | <b>SPI1EIF:</b> SPI1 Fault Interrupt Flag Status bit<br>1 = Interrupt request has occurred    |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               |                                                                                               | request has oc<br>request has no |                  |                   |                 |                 |        |  |  |  |  |

| bit 8         | •                                                                                             | Interrupt Flag                   |                  |                   |                 |                 |        |  |  |  |  |

|               |                                                                                               | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | •                                                                                             | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 7         |                                                                                               | Interrupt Flag                   |                  |                   |                 |                 |        |  |  |  |  |

|               |                                                                                               | request has oc<br>request has no |                  |                   |                 |                 |        |  |  |  |  |

| bit 6         | -                                                                                             | -                                | nannel 2 Interru | upt Flag Status   | bit             |                 |        |  |  |  |  |

|               |                                                                                               | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | •                                                                                             | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 5         |                                                                                               | -                                | el 2 Interrupt F | lag Status bit    |                 |                 |        |  |  |  |  |

|               |                                                                                               | request has oc<br>request has no |                  |                   |                 |                 |        |  |  |  |  |

| bit 4         | -                                                                                             | -                                | ata Transfer C   | omplete Interri   | upt Flag Status | s bit           |        |  |  |  |  |

|               |                                                                                               | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | -                                                                                             | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 3         |                                                                                               | Interrupt Flag<br>request has or |                  |                   |                 |                 |        |  |  |  |  |

|               |                                                                                               |                                  |                  |                   |                 |                 |        |  |  |  |  |

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0          | R/W-1                                                                                                                               | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| _            |                                                                                                                                     | T8IP<2:0>                                |                |                   |                 | MI2C2IP<2:0>    |       |  |  |  |  |

| bit 15       | ·                                                                                                                                   |                                          |                |                   | •               |                 | bit   |  |  |  |  |

|              |                                                                                                                                     |                                          |                |                   |                 |                 |       |  |  |  |  |

| U-0          | R/W-1                                                                                                                               | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                                                                                                                     | SI2C2IP<2:0>                             |                | —                 |                 | T7IP<2:0>       | 1.11  |  |  |  |  |

| bit 7        |                                                                                                                                     |                                          |                |                   |                 |                 | bit   |  |  |  |  |

| Legend:      |                                                                                                                                     |                                          |                |                   |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                                                                              | W = Writable b                           | oit            | U = Unimple       | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                                                                                                               | '1' = Bit is set                         |                | '0' = Bit is cle  | eared           | x = Bit is unkr | iown  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                           | ented: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |

| bit 14-12    | -                                                                                                                                   | Timer8 Interrupt                         |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                                     | rupt is priority 7 (h                    | -              | ty interrupt)     |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Inter                                                                                                                         | rupt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |

|              | 000 = Inter                                                                                                                         | rupt source is disa                      | abled          |                   |                 |                 |       |  |  |  |  |

| bit 11       | Unimpleme                                                                                                                           | ented: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |

| bit 10-8     | <b>MI2C2IP&lt;2:0&gt;:</b> I2C2 Master Events Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                          |                |                   |                 |                 |       |  |  |  |  |

|              | 111 = Inter                                                                                                                         | rupt is priority 7 (h                    | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                                     | rupt is priority 1                       | ablad          |                   |                 |                 |       |  |  |  |  |

| bit 7        |                                                                                                                                     | rupt source is disa<br>ented: Read as '0 |                |                   |                 |                 |       |  |  |  |  |

| bit 6-4      | -                                                                                                                                   | :0>: I2C2 Slave E                        |                | unt Priority hite |                 |                 |       |  |  |  |  |

| DIL 0-4      |                                                                                                                                     | rupt is priority 7 (h                    |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          | ignoot phon    | ty monapty        |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |

|              | •<br>001 = Inter                                                                                                                    | rupt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                                     | rupt source is disa                      | abled          |                   |                 |                 |       |  |  |  |  |

| bit 3        | Unimpleme                                                                                                                           | ented: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |

| bit 2-0      | T7IP<2:0>:                                                                                                                          | Timer7 Interrupt                         | Priority bits  |                   |                 |                 |       |  |  |  |  |

|              | 111 = Inter                                                                                                                         | rupt is priority 7 (h                    | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Inter                                                                                                                         | rupt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                                     | rupt source is disa                      |                |                   |                 |                 |       |  |  |  |  |

# REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

# 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "**Pin Diagrams**" section for the available pins and their functionality.

# 11.3 Configuring Analog Port Pins

The ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the ADC port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: |                                             |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

# 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

# 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJXXXMCX06A/X08A/X10A devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN Interrupt Enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the Weak Pull-up Enable bits (CNxPUE) for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFF00, WO | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

|      |            |                                   |

| R/W-0              | U-0                                                         | R/W-0                             | U-0              | U-0                            | U-0           | U-0                  | U-0            |  |  |  |  |

|--------------------|-------------------------------------------------------------|-----------------------------------|------------------|--------------------------------|---------------|----------------------|----------------|--|--|--|--|

| TON <sup>(1)</sup> | _                                                           | TSIDL <sup>(2)</sup>              |                  | _                              | _             | _                    | _              |  |  |  |  |

| bit 15             |                                                             |                                   |                  | •                              |               |                      | bit 8          |  |  |  |  |

|                    |                                                             |                                   |                  |                                |               |                      |                |  |  |  |  |

| U-0                | R/W-0                                                       | R/W-0                             | R/W-0            | U-0                            | U-0           | R/W-0                | U-0            |  |  |  |  |

|                    | TGATE <sup>(1)</sup>                                        | TCKPS                             | <1:0> <b>(1)</b> | —                              |               | TCS <sup>(1,3)</sup> |                |  |  |  |  |

| bit 7              |                                                             |                                   |                  |                                |               |                      | bit (          |  |  |  |  |

|                    |                                                             |                                   |                  |                                |               |                      |                |  |  |  |  |

| Legend:            | . 1. 11                                                     |                                   |                  |                                |               |                      |                |  |  |  |  |

| R = Readable       |                                                             | W = Writable                      | DIt              | U = Unimplen                   |               |                      |                |  |  |  |  |

| -n = Value at      | POR                                                         | '1' = Bit is set                  |                  | '0' = Bit is clea              | ared          | x = Bit is unkno     | own            |  |  |  |  |

| bit 15             | TON: Timery                                                 | On bit <sup>(1)</sup>             |                  |                                |               |                      |                |  |  |  |  |

|                    | 1 = Starts 16-                                              |                                   |                  |                                |               |                      |                |  |  |  |  |

|                    | 0 = Stops 16-                                               |                                   |                  |                                |               |                      |                |  |  |  |  |

| bit 14             | Unimplemen                                                  | ted: Read as '                    | )'               |                                |               |                      |                |  |  |  |  |

| bit 13             | TSIDL: Stop i                                               | in Idle Mode bit                  | (2)              |                                |               |                      |                |  |  |  |  |

|                    |                                                             |                                   |                  | device enters Id               | le mode       |                      |                |  |  |  |  |

|                    | 0 = Continue                                                | module operati                    | on in Idle mo    | ode                            |               |                      |                |  |  |  |  |

| bit 12-7           | -                                                           | ted: Read as '                    |                  |                                |               |                      |                |  |  |  |  |

| bit 6              | TGATE: Time                                                 | ery Gated Time                    | Accumulatio      | n Enable bit <sup>(1)</sup>    |               |                      |                |  |  |  |  |

|                    | When TCS =                                                  |                                   |                  |                                |               |                      |                |  |  |  |  |

|                    | This bit is ignored.                                        |                                   |                  |                                |               |                      |                |  |  |  |  |

|                    | <u>When TCS = 0:</u><br>1 = Gated time accumulation enabled |                                   |                  |                                |               |                      |                |  |  |  |  |

|                    |                                                             | ne accumulation                   |                  |                                |               |                      |                |  |  |  |  |

| bit 5-4            | TCKPS<1:0>                                                  | : Timer3 Input                    | Clock Presca     | ale Select bits <sup>(1)</sup> |               |                      |                |  |  |  |  |

|                    | 11 <b>= 1:256</b>                                           | ·                                 |                  |                                |               |                      |                |  |  |  |  |

|                    | 10 <b>= 1:64</b>                                            |                                   |                  |                                |               |                      |                |  |  |  |  |

|                    | 01 = 1:8                                                    |                                   |                  |                                |               |                      |                |  |  |  |  |

| <b>h</b> :+ 0 0    | 00 = 1:1                                                    | tod. Dood oo '                    | <b>、</b>         |                                |               |                      |                |  |  |  |  |

| bit 3-2            | •                                                           | ted: Read as '0<br>Clock Source S |                  |                                |               |                      |                |  |  |  |  |

| bit 1              | ,                                                           |                                   |                  |                                |               |                      |                |  |  |  |  |

|                    | 1 = External c<br>0 = Internal c                            | clock from TyCł<br>lock (Ecy)     | C pin (on the    | nsing edge)                    |               |                      |                |  |  |  |  |

| bit 0              |                                                             | ited: Read as '                   | )'               |                                |               |                      |                |  |  |  |  |

|                    | P                                                           |                                   | -                |                                |               |                      |                |  |  |  |  |

|                    |                                                             |                                   |                  | = 1), these bits               | have no effec | t on Timery operat   | tion; all time |  |  |  |  |

| fur                | nctions are set th                                          | hrough T2CON                      |                  |                                |               |                      |                |  |  |  |  |

REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

# 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

# 20.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

## 20.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546066                                        |

### 20.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# REGISTER 20-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                      |

- Note 1: Refer to Section 17. "UART" (DS70188) in the "dsPIC33F/PIC24H Family Reference Manual" for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on the UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on the UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters</li> </ul> |

| bit 5   | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                                   |

|         | <ul><li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect.</li><li>0 = Address Detect mode disabled</li></ul>                                                                                                                                                                                                                                                              |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                               |

|         | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                        |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                      |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                                                                                                                                                                                                                    |

|         | 1 = Receive buffer has overflowed                                                                                                                                                                                                                                                                                                                                                                                  |

|         | $0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 \rightarrow 0 transition) will resetthe receiver buffer and the UxRSR to the empty state.$                                                                                                                                                                                                                                           |

| bit 0   | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                                      |

Note 1: Refer to Section 17. "UART" (DS70188) in the "dsPIC33F/PIC24H Family Reference Manual" for information on enabling the UART module for transmit operation.

| Note: T      | he buffers, SID, I                                                 | EID, DLC, Data                      | Field and R | eceive Status re | gisters, are lo | cated in DMA R     | AM.   |

|--------------|--------------------------------------------------------------------|-------------------------------------|-------------|------------------|-----------------|--------------------|-------|

| REGISTER     | 21-27: CiTRB                                                       | BnSID: ECAN                         | ™ BUFFER    | n STANDAR        | D IDENTIFIE     | ER (n = 0, 1,      | , 31) |

| U-0          | U-0                                                                | U-0                                 | R/W-x       | R/W-x            | R/W-x           | R/W-x              | R/W-x |

|              |                                                                    |                                     |             |                  | SID<10:6>       |                    |       |

| bit 15       |                                                                    |                                     |             |                  |                 |                    | bit 8 |

|              |                                                                    |                                     |             |                  |                 |                    |       |

| R/W-x        | R/W-x                                                              | R/W-x                               | R/W-x       | R/W-x            | R/W-x           | R/W-x              | R/W-x |

|              |                                                                    | SID<                                | 5:0>        |                  |                 | SRR                | IDE   |

| bit 7        |                                                                    |                                     |             |                  |                 |                    | bit 0 |

|              |                                                                    |                                     |             |                  |                 |                    |       |

| Legend:      |                                                                    |                                     |             |                  |                 |                    |       |

| R = Readab   | le bit                                                             | W = Writable                        | bit         | U = Unimpler     | nented bit, rea | id as '0'          |       |

| -n = Value a | t POR                                                              | '1' = Bit is set                    |             | '0' = Bit is cle | ared            | x = Bit is unknown |       |

|              |                                                                    |                                     |             |                  |                 |                    |       |

| bit 15-13    | Unimplemen                                                         | ted: Read as '                      | o'          |                  |                 |                    |       |

| bit 12-2     | SID<10:0>: 3                                                       | SID<10:0>: Standard Identifier bits |             |                  |                 |                    |       |

| bit 1        | SRR: Substit                                                       | ute Remote Re                       | quest bit   |                  |                 |                    |       |

|              | 1 = Message will request remote transmission<br>0 = Normal message |                                     |             |                  |                 |                    |       |

bit 0 **IDE:** Extended Identifier bit

1 = Message will transmit extended identifier

0 = Message will transmit standard identifier

'1' = Bit is set

# REGISTER 21-28: CiTRBnEID: ECAN™ BUFFER n EXTENDED IDENTIFIER (n = 0, 1, ..., 31)

| U-0             | U-0   | U-0             | U-0   | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|-----------------|-------|-----------------|-------|--------------|------------------|----------|-------|

| —               | _     | —               | _     |              | EID<'            | 17:14>   |       |

| bit 15          |       |                 |       | ·            |                  |          | bit 8 |

|                 |       |                 |       |              |                  |          |       |

| R/W-x           | R/W-x | R/W-x           | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|                 |       |                 | EID   | <13:6>       |                  |          |       |

| bit 7           |       |                 |       |              |                  |          | bit 0 |

|                 |       |                 |       |              |                  |          |       |

| Legend:         |       |                 |       |              |                  |          |       |

| R = Readable bi | it    | W = Writable bi | t     | U = Unimpler | nented bit, read | l as '0' |       |

'0' = Bit is cleared

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

-n = Value at POR

x = Bit is unknown

# 25.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 25.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 25.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 25.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express