Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 20 MIPS                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc710a-h-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/ X10A family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJXXXMCX06A/X08A/X10A family of 16-bit Digital Signal Controllers (DSC) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The AVDD  |         | and         | and AVss |    | mu  | st be |

|-------|-----------|---------|-------------|----------|----|-----|-------|

|       | connected |         | independent |          | of | the | ADC   |

|       | volta     | ge refe | rence       | source.  |    |     |       |

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

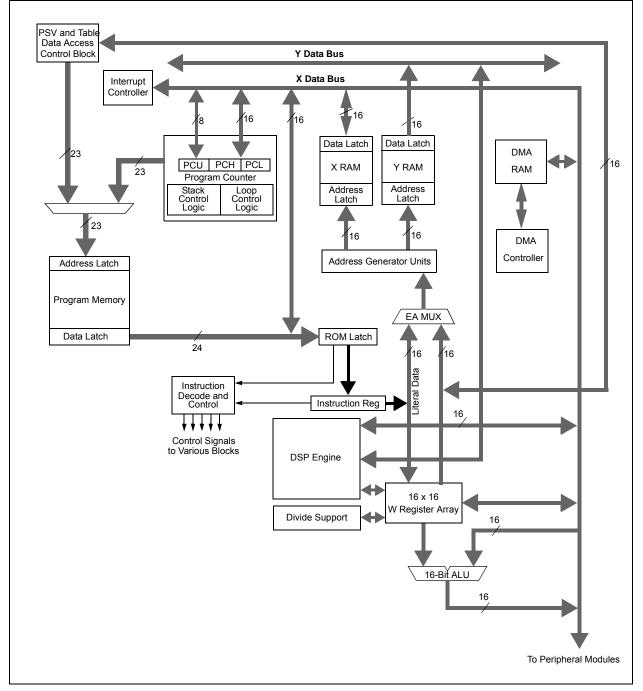

## 3.3 Special MCU Features

The dsPIC33FJXXXMCX06A/X08A/X10A devices feature a 17-bit by 17-bit, single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJXXXMCX06A/X08A/X10A devices support 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without a loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

### FIGURE 3-1: dsPIC33FJXXXMCX06A/X08A/X10A CPU CORE BLOCK DIAGRAM

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|----------------------------|--------|--------|--------|--------|-------|------------|-------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        |        |                            |        |        |        |        |       | Input 1 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | _      | _                          | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        |        | Input 2 Capture Register x |        |        |        |        |       |            |             |       | xxxx  |       |       |       |          |       |               |

| IC2CON   | 0146        | -      | _                          | ICSIDL | _      | _      | _      |       | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |        | Input 3 Capture Register x |        |        |        |        |       |            |             |       |       | xxxx  |       |       |          |       |               |

| IC3CON   | 014A        | _      | —                          | ICSIDL | _      | _      |        | _     | —          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |        | Input 4 Capture Register   |        |        |        |        |       |            |             |       | xxxx  |       |       |       |          |       |               |

| IC4CON   | 014E        | _      | _                          | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |        |                            |        |        |        |        |       | Input 5 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        | _      | _                          | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |        |                            |        |        |        |        |       | Input 6 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        | _      | _                          | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |        |                            |        |        |        |        |       | Input 7 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        | _      |                            | ICSIDL | —      |        | _      | _     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |        |                            |        |        |        |        |       | Input 8 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | _      |                            | ICSIDL | _      | _      |        | _     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

#### TABLE 4-7: INPUT CAPTURE REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

## TABLE 4-36: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing     |

|-------|----------------------------------------------|

|       | mode specified in the instruction can differ |

|       | for the source and destination EA.           |

|       | However, the 4-bit Wb (register offset)      |

|       | field is shared between both source and      |

|       | destination (but typically only used by      |

|       | one).                                        |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the Data Pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 will always be directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9, and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.3.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

## 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (e.g., [W7+W2]) is used, Modulo Address correction is performed but the contents of the register remain unchanged.

## 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order; thus, the only operand requiring reversal is the modifier.

## 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when the following conditions exist:

- The BWM bits (W register selection) in the MODCON register are any value other than 15 (the stack cannot be accessed using Bit-Reversed Addressing).

- 2. The BREN bit is set in the XBREV register.

- 3. The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is only executed for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data; normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed Addressing should not be enabled |

|-------|---------------------------------------------------------------------|

|       | together. In the event that the user                                |

|       | attempts to do so, Bit-Reversed Address-                            |

|       | ing will assume priority for the X WAGU,                            |

|       | and X WAGU Modulo Addressing will be                                |

|       | disabled. However, Modulo Addressing will                           |

|       | continue to function in the X RAGU.                                 |

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

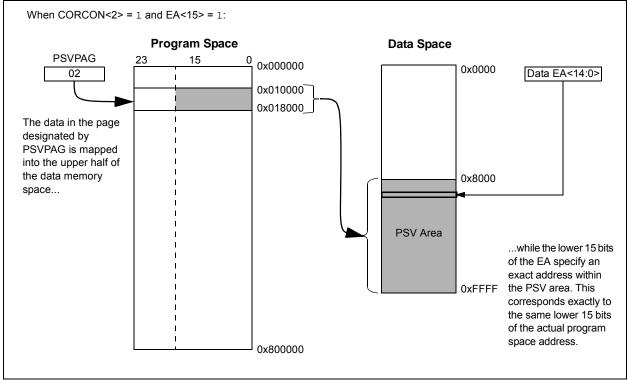

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

## Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV and are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data using PSV to execute in a single cycle.

## FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

© 2009-2012 Microchip Technology Inc.

| R/W-0         | R-0           | U-0                                  | U-0           | U-0              | U-0              | U-0             | U-0   |

|---------------|---------------|--------------------------------------|---------------|------------------|------------------|-----------------|-------|

| ALTIVT        | DISI          | —                                    | _             | —                | —                |                 | —     |

| bit 15        |               |                                      |               |                  |                  |                 | bit 8 |

|               |               |                                      |               |                  |                  |                 |       |

| U-0           | U-0           | U-0                                  | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —             | —             | INT1EP                               | INT0EP        |                  |                  |                 |       |

| bit 7         |               |                                      |               |                  |                  |                 | bit 0 |

|               |               |                                      |               |                  |                  |                 |       |

| Legend:       |               |                                      |               |                  |                  |                 |       |

| R = Readable  |               | W = Writable                         |               | -                | nented bit, read |                 |       |

| -n = Value at | POR           | '1' = Bit is set                     |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               |               |                                      |               |                  |                  |                 |       |

| bit 15        |               | ole Alternate In                     | •             | lable bit        |                  |                 |       |

|               |               | nate Interrupt \<br>lard (default) v |               |                  |                  |                 |       |

| bit 14        |               | struction Statu                      |               |                  |                  |                 |       |

|               |               | ruction is activ                     |               |                  |                  |                 |       |

|               | 0 = DISI inst | ruction is not a                     | ictive        |                  |                  |                 |       |

| bit 13-5      | Unimplemen    | ted: Read as '                       | 0'            |                  |                  |                 |       |

| bit 4         | INT4EP: Exte  | ernal Interrupt 4                    | Edge Detect   | Polarity Select  | bit              |                 |       |

|               |               | on negative ed                       |               |                  |                  |                 |       |

|               | -             | on positive edg                      |               |                  |                  |                 |       |

| bit 3         |               | •                                    | •             | Polarity Select  | bit              |                 |       |

|               |               | on negative ed<br>on positive edg    |               |                  |                  |                 |       |

| bit 2         | -             |                                      |               | Polarity Select  | bit              |                 |       |

| SIT Z         |               | on negative ed                       | •             |                  | . Dit            |                 |       |

|               |               | on positive edg                      |               |                  |                  |                 |       |

| bit 1         | INT1EP: Exte  | ernal Interrupt                      | I Edge Detect | Polarity Select  | bit              |                 |       |

|               |               | on negative ed                       | 0             |                  |                  |                 |       |

|               | •             | on positive edg                      |               |                  |                  |                 |       |

| bit 0         |               |                                      |               | Polarity Select  | bit              |                 |       |

|               |               | on negative ed                       |               |                  |                  |                 |       |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 (CONTINUED)

| bit 2 | <b>C1RXIE:</b> ECAN1 Receive Data Ready Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>SPI2IE:</b> SPI2 Event Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled               |

| bit 0 | <b>SPI2EIE:</b> SPI2 Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled              |

# dsPIC33FJXXXMCX06A/X08A/X10A

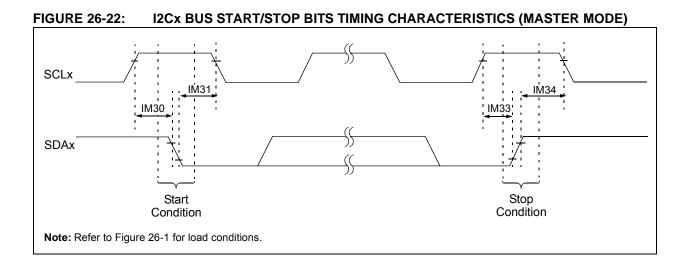

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0 = Send ACK during Acknowledge                                                                                                                                                                                                             |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                 |

|       | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul>                             |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                 |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte</li> <li>0 = Receive sequence not in progress</li> </ul>                                                              |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                           |

|       | <ul> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence</li> <li>0 = Stop condition not in progress</li> </ul>                                                                            |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                |

|       | 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence                                                                                                                        |

|       | 0 = Repeated Start condition not in progress                                                                                                                                                                                                |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                 |

|       | <ul> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li> <li>0 = Start condition not in progress</li> </ul>                                                                         |

# dsPIC33FJXXXMCX06A/X08A/X10A

## REGISTER 21-2: CiCTRL2: ECAN™ CONTROL REGISTER 2

| U-0             | U-0                | U-0                                | U-0             | U-0                                | U-0        | U-0                | U-0   |  |  |

|-----------------|--------------------|------------------------------------|-----------------|------------------------------------|------------|--------------------|-------|--|--|

| —               | —                  | —                                  | —               | —                                  | —          | —                  | —     |  |  |

| bit 15          |                    |                                    |                 |                                    |            |                    | bit 8 |  |  |

|                 |                    |                                    |                 |                                    |            |                    |       |  |  |

| U-0             | U-0                | U-0                                | R-0             | R-0                                | R-0        | R-0                | R-0   |  |  |

| _               | —                  | —                                  |                 |                                    | DNCNT<4:0> |                    |       |  |  |

| bit 7           |                    |                                    |                 |                                    |            |                    | bit 0 |  |  |

|                 |                    |                                    |                 |                                    |            |                    |       |  |  |

| Legend:         |                    |                                    |                 |                                    |            |                    |       |  |  |

| R = Readable    | bit                | W = Writable                       | bit             | U = Unimplemented bit, read as '0' |            |                    |       |  |  |

| -n = Value at F | POR                | '1' = Bit is set                   |                 | '0' = Bit is cle                   | ared       | x = Bit is unknown |       |  |  |

|                 |                    |                                    |                 |                                    |            |                    |       |  |  |

| bit 15-5        | Unimplemen         | ted: Read as '                     | כ'              |                                    |            |                    |       |  |  |

| bit 4-0         | DNCNT<4:0>         | •: DeviceNet™                      | Filter Bit Num  | ber bits                           |            |                    |       |  |  |

|                 |                    | 1 = Invalid sele                   |                 |                                    |            |                    |       |  |  |

|                 | 10001 <b>= Com</b> | npare up to data                   | a byte 3, bit 6 | with EID<17>                       |            |                    |       |  |  |

| •               |                    |                                    |                 |                                    |            |                    |       |  |  |

|                 | •                  |                                    |                 |                                    |            |                    |       |  |  |

|                 | •                  |                                    |                 |                                    |            |                    |       |  |  |

|                 |                    | npare up to data<br>not compare da | -               | with EID<0>                        |            |                    |       |  |  |

| bit 7<br>Legend:                                        | — —<br>W-0 R/W-0                                           | R/W-0<br>ADCS•          | R/W-0<br><7:0>(2) | SAMC<4:0> <sup>(1)</sup><br>R/W-0 | )<br>R/W-0      | bit   |  |  |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------|-------------------------|-------------------|-----------------------------------|-----------------|-------|--|--|--|--|--|

| R/W-0 R/<br>bit 7<br><b>Legend:</b><br>R = Readable bit | N-0 R/W-0                                                  |                         | _                 | R/W-0                             | R/W-0           | bit   |  |  |  |  |  |

| bit 7<br><b>Legend:</b><br>R = Readable bit             | W-0 R/W-0                                                  |                         | _                 | R/W-0                             | R/W-0           |       |  |  |  |  |  |

| bit 7<br><b>Legend:</b><br>R = Readable bit             |                                                            |                         | _                 |                                   |                 | R/W-0 |  |  |  |  |  |

| Legend:<br>R = Readable bit                             |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| R = Readable bit                                        |                                                            |                         |                   |                                   |                 | bit   |  |  |  |  |  |

| R = Readable bit                                        |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| R = Readable bit<br>-n = Value at POR                   |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| -n = Value at POR                                       | W = Writable b                                             | bit                     | U = Unimplen      | nented bit, read                  | d as '0'        |       |  |  |  |  |  |

|                                                         | '1' = Bit is set                                           |                         | '0' = Bit is clea | ared                              | x = Bit is unkr | Iown  |  |  |  |  |  |

|                                                         |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | : ADC Conversion Cloo                                      | ck Source bit           |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | DC internal RC clock                                       |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | ock derived from syster                                    |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | Unimplemented: Read as '0'                                 |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | <4:0>: Auto-Sample Ti                                      | ime bits <sup>(1)</sup> |                   |                                   |                 |       |  |  |  |  |  |

| 11111                                                   | L = 31 TAD                                                 |                         |                   |                                   |                 |       |  |  |  |  |  |

| •                                                       |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| •                                                       | . = 1 TAD                                                  |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | = 0 TAD                                                    |                         |                   |                                   |                 |       |  |  |  |  |  |

| bit 7-0 ADCS                                            | ADCS<7:0>: ADC Conversion Clock Select bits <sup>(2)</sup> |                         |                   |                                   |                 |       |  |  |  |  |  |

| 11111                                                   | 111 = Reserved                                             |                         |                   |                                   |                 |       |  |  |  |  |  |

| •                                                       |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| •                                                       |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| •                                                       |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | 0000 = Reserved                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| 00111                                                   | 1111 = TCY · (ADCS<7                                       | :0> + 1) = 64           | • TCY = TAD       |                                   |                 |       |  |  |  |  |  |

| •                                                       |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| •                                                       |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

| •                                                       |                                                            |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | $010 = \text{Tcy} \cdot (\text{ADCS} < 7)$                 |                         |                   |                                   |                 |       |  |  |  |  |  |

|                                                         | 0001 = Tcy · (ADCS<7<br>0000 = Tcy · (ADCS<7               |                         |                   |                                   |                 |       |  |  |  |  |  |

- - 2: This bit is not used if ADxCON3<15> (ADRC) = 1.

REGISTER 22-3: ADxCON3: ADCx CONTROL REGISTER 3

# dsPIC33FJXXXMCX06A/X08A/X10A

| R/W-0                 | U-0                        | U-0                                                                                                                 | R/W-0                                                          | R/W-0            | R/W-0                   | R/W-0           | R/W-0 |

|-----------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------|-------------------------|-----------------|-------|

| CHONB                 | _                          |                                                                                                                     |                                                                |                  | CH0SB<4:03              | >               |       |

| bit 15                |                            |                                                                                                                     |                                                                |                  |                         |                 | bit 8 |

| R/W-0                 | U-0                        | U-0                                                                                                                 | R/W-0                                                          | R/W-0            | R/W-0                   | R/W-0           | R/W-0 |

| CH0NA                 |                            | _                                                                                                                   |                                                                |                  | CH0SA<4:0>              | (1)             |       |

| bit 7                 |                            |                                                                                                                     |                                                                |                  |                         |                 | bit 0 |

| Legend:               |                            |                                                                                                                     |                                                                |                  |                         |                 |       |

| R = Readabl           | le bit                     | W = Writable t                                                                                                      | oit                                                            | U = Unimpler     | mented bit, rea         | ad as '0'       |       |

| -n = Value at         | t POR                      | '1' = Bit is set                                                                                                    |                                                                | '0' = Bit is cle | ared                    | x = Bit is unkr | nown  |

| bit 14-13<br>bit 12-8 | CH0SB<4:0:<br>Same definit | nted: Read as 'o<br>>: Channel 0 Po<br>ion as bit<4:0>.                                                             | sitive Input Se                                                |                  |                         |                 |       |

| bit 7                 | 1 = Channel                | annel 0 Negative<br>0 negative input<br>0 negative input                                                            | is AN1                                                         | for Sample A b   | it                      |                 |       |

| bit 6-5               | Unimpleme                  | nted: Read as 'o                                                                                                    | )'                                                             |                  |                         |                 |       |

| bit 4-0               | 11111 = Cha<br>11110 = Cha | >: Channel 0 Po<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive | input is AN31<br>input is AN30<br>input is AN2<br>input is AN1 | elect for Sample | e A bits <sup>(1)</sup> |                 |       |

#### REGISTER 22-6: ADxCHS0: ADCx INPUT CHANNEL 0 SELECT REGISTER

Note 1: ADC2 can only select AN0-AN15 as positive inputs.

| REGISTER 22-9: ADxF | CFGH: ADCx PORT CONFIGURATION REGISTER HIGH <sup>(1,2,3,4)</sup> |

|---------------------|------------------------------------------------------------------|

|---------------------|------------------------------------------------------------------|

| R/W-0       | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------------|--------|--------|--------|--------|--------|--------|--------|

| PCFG31      | PCFG30 | PCFG29 | PCFG28 | PCFG27 | PCFG26 | PCFG25 | PCFG24 |

| bit 15      |        | •      |        |        |        | -<br>- | bit 8  |

|             |        |        |        |        |        |        |        |

| R/W-0       | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| PCFG23      | PCFG22 | PCFG21 | PCFG20 | PCFG19 | PCFG18 | PCFG17 | PCFG16 |

| bit 7       | ·      | •      | •      |        |        |        | bit 0  |

|             |        |        |        |        |        |        |        |

| I a manual. |        |        |        |        |        |        |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

PCFG<31:16>: ADC Port Configuration Control bits

1 = Port pin in Digital mode; port read input enabled; ADC input multiplexer connected to AVss

0 = Port pin in Analog mode; port read input disabled; ADC samples pin voltage

- **Note 1:** On devices without 32 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on the device.

- 2: ADC2 only supports analog inputs, AN0-AN15; therefore, no ADC2 port Configuration register exists.

- **3:** PCFGx = ANx, where x = 16 through 31.

- **4:** The PCFGx bits have no effect if the ADC module is disabled by setting the ADxMD bit in the PMDx register. In this case, all port pins multiplexed with ANx will be in Digital mode.

## **REGISTER 22-10:** ADxPCFGL: ADCx PORT CONFIGURATION REGISTER LOW<sup>(1,2,3,4)</sup>

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| PCFG15 | PCFG14 | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 15 |        |        |        |        |        |       | bit 8 |

|        |        |        |        |        |        |       |       |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| PCFG7  | PCFG6  | PCFG5  | PCFG4  | PCFG3  | PCFG2  | PCFG1 | PCFG0 |

| bit 7  |        |        | •      |        |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 PCFG<15:0>: ADC Port Configuration Control bits

1 = Port pin in Digital mode; port read input enabled; ADC input multiplexer connected to AVss

0 = Port pin in Analog mode; port read input disabled; ADC samples pin voltage

- **Note 1:** On devices without 16 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on the device.

- **2:** On devices with two analog-to-digital modules, both AD1PCFGL and AD2PCFGL will affect the configuration of port pins multiplexed with AN0-AN15.

- **3:** PCFGx = ANx, where x = 0 through 15.

- 4: The PCFGx bits have no effect if the ADC module is disabled by setting the ADxMD bit in the PMDx register. In this case, all port pins multiplexed with ANx will be in Digital mode.

## 25.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 25.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 25.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 25.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 25.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

## TABLE 26-23: TIMER2, TIMER4, TIMER6 AND TIMER8 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                |                                          |                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                                      |     |                     |          |                                                                              |

|--------------------|----------------|------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|---------------------|----------|------------------------------------------------------------------------------|

| Param<br>No.       | Symbol         | Charact                                  | eristic         |                                                                                                                                                                                                                                                                                     | Min                                  | Тур | Max                 | Units    | Conditions                                                                   |

| TB10               | TtxH           | TxCK High Time                           | Synchro<br>mode | onous                                                                                                                                                                                                                                                                               | Greater of<br>20 or (Tcy +<br>20)/N  |     |                     | ns<br>ns | Must also meet<br>parameter TB15<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB11               | TtxL           | TxCK Low Time                            | Synchro<br>mode | onous                                                                                                                                                                                                                                                                               | Greater of<br>20 or (Tcy +<br>20)/N  |     |                     | ns<br>ns | Must also meet<br>parameter TB15<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB15               | TtxP           | TxCK Input<br>Period                     | Synchro<br>mode | onous                                                                                                                                                                                                                                                                               | Greater of<br>40 or (2Tcy<br>+ 40)/N | _   | _                   | ns       | N = prescale<br>value<br>(1, 8, 64, 256)                                     |

| TB20               | TCKEXT-<br>MRL | Delay from Externa<br>Edge to Timer Incr |                 | Clock                                                                                                                                                                                                                                                                               | 0.75 Tcy +<br>40                     | _   | 1.75<br>Tcy +<br>40 | ns       | —                                                                            |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

## TABLE 26-24:TIMER3, TIMER5, TIMER7 AND TIMER9 EXTERNAL CLOCK TIMING<br/>REQUIREMENTS

|              |           |                                                           |                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                  |     |                  |       | or Industrial                            |

|--------------|-----------|-----------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|-------|------------------------------------------|

| Param<br>No. | Symbol    | Characte                                                  | Characteristic             |                                                                                                                                                                                                                                                                                         |                  | Тур | Мах              | Units | Conditions                               |

| TC10         | TtxH      | TxCK High Time                                            | Synchronous                |                                                                                                                                                                                                                                                                                         | Тсү + 20         | —   | _                | ns    | Must also meet parameter TC15            |

| TC11         | TtxL      | TxCK Low Time                                             | Synchro                    | nous                                                                                                                                                                                                                                                                                    | Tcy + 20         | —   | —                | ns    | Must also meet parameter TC15            |

| TC15         | TtxP      | TxCK Input Period                                         | Synchronous with prescaler |                                                                                                                                                                                                                                                                                         | 2 Tcy + 40       | -   | _                | ns    | N = prescale<br>value<br>(1, 8, 64, 256) |

| TC20         | TCKEXTMRL | Delay from External TxCK Clock<br>Edge to Timer Increment |                            |                                                                                                                                                                                                                                                                                         | 0.75 Tcy +<br>40 | —   | 1.75 Tcy<br>+ 40 |       | —                                        |

Note 1: These parameters are characterized, but are not tested in manufacturing.

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                         |  |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                | Min                                                                                                                                                                                                                                                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                              |  |

| SP10               | TscP                  | Maximum SCK Frequency                        | —                                                                                                                                                                                                                                                                                     | _                  | 15  | MHz   | See Note 3                              |  |

| SP20               | TscF                  | SCKx Output Fall Time                        | —                                                                                                                                                                                                                                                                                     | —                  |     | ns    | See parameter DO32 and <b>Note 4</b>    |  |

| SP21               | TscR                  | SCKx Output Rise Time                        | —                                                                                                                                                                                                                                                                                     | —                  |     | ns    | See parameter DO31<br>and <b>Note 4</b> |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                     | —                  | _   | ns    | See parameter DO32 and <b>Note 4</b>    |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                     | —                  | _   | ns    | See parameter DO31 and <b>Note 4</b>    |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                                                                                                                                                                                                                                                     | 6                  | 20  | ns    | _                                       |  |

| SP36               | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                    |                    |     | ns    |                                         |  |

#### TABLE 26-33: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

## TABLE 26-38:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       | ARACTERIS             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |              |                    |     |       |                                      |

|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min          | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70         | TscP                  | Maximum SCK Input Frequency                                                                                                                                                                                                                                                             | _            | _                  | 15  | MHz   | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                                                                                                                                                                                                                                                    | —            | —                  |     | ns    | See parameter DO32 and <b>Note 4</b> |

| SP73         | TscR                  | SCKx Input Rise Time                                                                                                                                                                                                                                                                    | —            | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                                                                                                                                                                                                                                              | —            | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                                                                                                                                                                                                                                              | _            | _                  | -   | ns    | See parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                                                                                                                               | _            | 6                  | 20  | ns    | —                                    |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                                                                                                                                                            | 30           | _                  |     | ns    | —                                    |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                              | 30           | _                  | _   | ns    | —                                    |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                               | 30           | _                  | _   | ns    | —                                    |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input                                                                                                                                                                                                                            | 120          | _                  | _   | ns    | _                                    |

| SP51         | TssH2doZ              | SSx                                                                                                                                                                                                                                                                                     | 10           | —                  | 50  | ns    | —                                    |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                                                                                                                                                                                                                                     | 1.5 Tcy + 40 | —                  |     | ns    | See Note 4                           |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCK clock generated by the Master must not violate this specificiation.

**4:** Assumes 50 pF load on all SPIx pins.

# dsPIC33FJXXXMCX06A/X08A/X10A