Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 20 MIPS                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

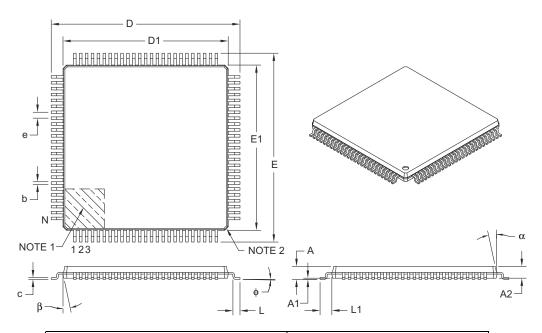

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc710a-h-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

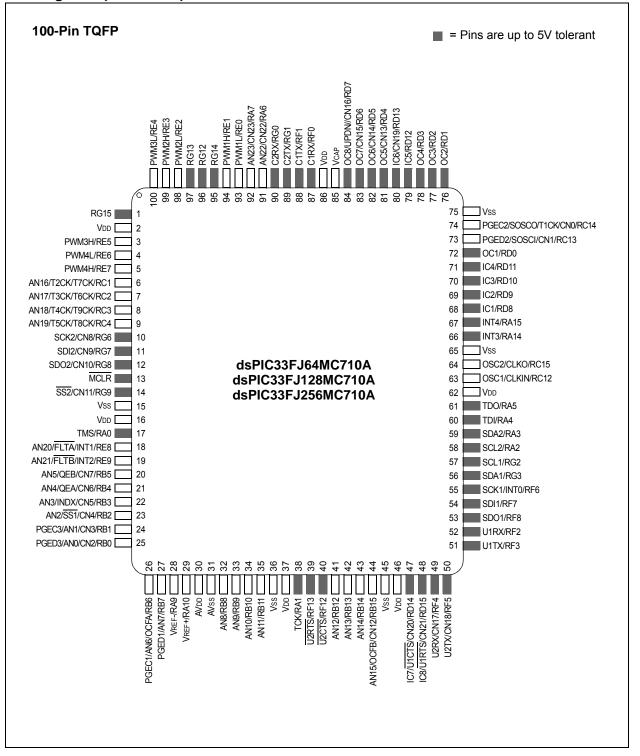

### **Pin Diagrams (Continued)**

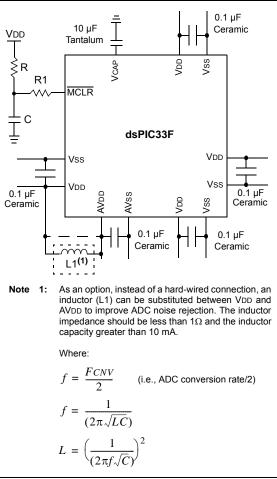

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

# 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 26.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 23.2 "On-Chip Voltage Regulator"** for details.

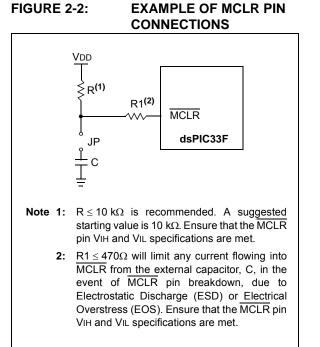

# 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJXXXMCX06A/X08A/X10A devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJXXXMCX06A/X08A/X10A instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum 'C' compiler efficiency. For most instructions, the dsPIC33FJXXXMCX06A/X08A/X10A devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1 and the programmer's model for the dsPIC33FJXXXMCX06A/X08A/X10A is shown in Figure 3-2.

## 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes, and is split into two blocks referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page register (PSVPAG). The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers but may be used as general purpose RAM.

# 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers, and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM memory data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

## 4.0 MEMORY ORGANIZATION

Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to Section 3. "Data Memory" (DS70202) and Section 4. "Program Memory" (DS70203) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06A/X08A/X10A architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the data space during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33FJXXXMCX06A/X08A/X10A devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in **Section 4.6** "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space. Memory usage for the dsPIC33FJXXXMCX06A/X08A/X10A family of devices is shown in Figure 4-1.

|                            | dsPIC33FJ64MCXXXA                                  | dsPIC33FJ128MCXXXA                                 | dsPIC33FJ256MCXXXA     |                                  |

|----------------------------|----------------------------------------------------|----------------------------------------------------|------------------------|----------------------------------|

| Ā                          | GOTO Instruction                                   | GOTO Instruction                                   | GOTO Instruction       | 0x000000<br>0x000002             |

|                            | Reset Address                                      | Reset Address                                      | Reset Address          | 0x000002<br>0x000004             |

|                            | Interrupt Vector Table                             | Interrupt Vector Table                             | Interrupt Vector Table | 0x0000FE                         |

|                            | Reserved                                           | Reserved                                           | Reserved               | 0x000100<br>0x000104             |

|                            | Alternate Vector Table                             | Alternate Vector Table                             | Alternate Vector Table | 0x0001FE                         |

| User Memory Space          | User Program<br>Flash Memory<br>(22K instructions) | User Program<br>Flash Memory<br>(44K instructions) | User Program           | 0x000200<br>0x00ABFE<br>0x00AC00 |

| Jory                       |                                                    |                                                    | (88K instructions)     |                                  |

| len                        |                                                    |                                                    |                        | 0x0157FE                         |

| er N                       | Linimplemented                                     |                                                    |                        | 0x015800                         |

| Ns                         | Unimplemented<br>(Read '0's)                       |                                                    |                        | <b>-</b> -                       |

|                            | (Read 0.5)                                         | Unimplemented                                      |                        | 0x02ABFE<br>0x02AC00             |

|                            |                                                    | (Read '0's)                                        | Unimplemented          |                                  |

|                            |                                                    |                                                    | (Read '0's)            |                                  |

| •                          |                                                    |                                                    | (Read 0.3)             | 0x7FFFFE                         |

| <b>Å</b>                   |                                                    |                                                    |                        | 0x800000                         |

|                            | Reserved                                           | Reserved                                           | Reserved               |                                  |

| ace                        | Device Configuration                               | Device Configuration                               | Device Configuration   | 0xF7FFFE<br>0xF80000             |

| g<br>S                     | Registers                                          | Device Configuration<br>Registers                  | Registers              | 0xF80017                         |

| Configuration Memory Space | Reserved                                           | Reserved                                           | Reserved               | 0xF80010                         |

| Confi                      | DEVID (2)                                          | <br>DEVID (2)                                      | DEVID (2)              | 0xFEFFFE<br>0xFF0000             |

| <u> </u>                   | ==::=(=)                                           |                                                    | ==::= (=)              | 0xFFFFFE                         |

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES

### TABLE 4-17: ADC1 REGISTER MAP

| File Name               | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8    | Bit 7      | Bit 6     | Bit 5  | Bit 4        | Bit 3  | Bit 2  | Bit 1     | Bit 0   | All<br>Resets |

|-------------------------|------|--------|----------|--------|---------|--------|-----------|---------|----------|------------|-----------|--------|--------------|--------|--------|-----------|---------|---------------|

| ADC1BUF0                | 0300 |        |          |        |         |        |           |         | ADC1 Dat | a Buffer 0 |           |        |              |        |        |           |         | xxxx          |

| AD1CON1                 | 0320 | ADON   | —        | ADSIDL | ADDMABM | _      | AD12B     | FOR     | M<1:0>   | :          | SSRC<2:0> |        | _            | SIMSAM | ASAM   | SAMP      | DONE    | 0000          |

| AD1CON2                 | 0322 | ,      | VCFG<2:0 | >      | _       | _      | CSCNA     | CHP     | S<1:0>   | BUFS       | _         |        | SMPI         | <3:0>  |        | BUFM      | ALTS    | 0000          |

| AD1CON3                 | 0324 | ADRC   | _        | _      |         | S      | AMC<4:0>  |         |          |            |           |        | ADCS         | <7:0>  |        |           |         | 0000          |

| AD1CHS123               | 0326 | _      | _        | _      | _       | _      | CH123N    | VB<1:0> | CH123SB  | _          | _         | _      | _            | _      | CH123I | NA<1:0>   | CH123SA | 0000          |

| AD1CHS0                 | 0328 | CH0NB  | _        | _      |         | С      | H0SB<4:0> | >       |          | CH0NA      | _         | _      | - CH0SA<4:0> |        |        |           | 0000    |               |

| AD1PCFGH <sup>(1)</sup> | 032A | PCFG31 | PCFG30   | PCFG29 | PCFG28  | PCFG27 | PCFG26    | PCFG25  | PCFG24   | PCFG23     | PCFG22    | PCFG21 | PCFG20       | PCFG19 | PCFG18 | PCFG17    | PCFG16  | 0000          |

| AD1PCFGL                | 032C | PCFG15 | PCFG14   | PCFG13 | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8    | PCFG7      | PCFG6     | PCFG5  | PCFG4        | PCFG3  | PCFG2  | PCFG1     | PCFG0   | 0000          |

| AD1CSSH(1)              | 032E | CSS31  | CSS30    | CSS29  | CSS28   | CSS27  | CSS26     | CSS25   | CSS24    | CSS23      | CSS22     | CSS21  | CSS20        | CSS19  | CSS18  | CSS17     | CSS16   | 0000          |

| AD1CSSL                 | 0330 | CSS15  | CSS14    | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8     | CSS7       | CSS6      | CSS5   | CSS4         | CSS3   | CSS2   | CSS1      | CSS0    | 0000          |

| AD1CON4                 | 0332 | _      | _        | _      | _       | _      | -         | _       | _        | _          | _         | _      | _            | —      |        | DMABL<2:( | 0>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Not all ANx inputs are available on all devices. Refer to the device pin diagrams for available ANx inputs.

## TABLE 4-18: ADC2 REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8     | Bit 7    | Bit 6     | Bit 5 | Bit 4        | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------|--------|---------|--------|-----------|---------|-----------|----------|-----------|-------|--------------|--------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340 |        |           |        |         |        |           |         | ADC2 Data | Buffer 0 |           |       |              |        |        |          |         | xxxx          |

| AD2CON1   | 0360 | ADON   | —         | ADSIDL | ADDMABM | _      | AD12B     | FOR     | VI<1:0>   | ;        | SSRC<2:0> | >     | _            | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362 |        | VCFG<2:0> | >      | _       | _      | CSCNA     | CHP     | S<1:0>    | BUFS     | _         |       | SMPI         | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364 | ADRC   | _         | _      |         | S      | SAMC<4:0> |         |           |          | ADCS<7:0> |       |              |        |        |          | 0000    |               |

| AD2CHS123 | 0366 | _      | _         | _      | _       | _      | CH123N    | IB<1:0> | CH123SB   | _        | _         | _     | _            | _      | CH123N | NA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368 | CH0NB  | _         | _      | _       |        | CH0S      | B<3:0>  |           | CH0NA    | _         | _     | — CH0SA<3:0> |        |        |          | 0000    |               |

| Reserved  | 036A |        | _         |        | —       |        | —         |         |           |          |           | —     | —            | _      |        | —        | —       | 0000          |

| AD2PCFGL  | 036C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8     | PCFG7    | PCFG6     | PCFG5 | PCFG4        | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E |        | _         |        | —       |        | —         |         |           |          |           | —     | —            | _      |        | —        | —       | 0000          |

| AD2CSSL   | 0370 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8      | CSS7     | CSS6      | CSS5  | CSS4         | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372 | _      | _         | _      | _       | _      | _         | _       | _         | _        | _         | _     | _            | _      |        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name  | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                         | Bit 8        | Bit 7                         | Bit 6    | Bit 5  | Bit 4 | Bit 3  | Bit 2              | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|-----------|--------|--------|--------|--------|-------------------------------|--------------|-------------------------------|----------|--------|-------|--------|--------------------|--------|--------|---------------|

|            | 0500-<br>051E |        | -         |        |        |        |        | Se                            | e definitior | when WIN                      | = x      |        |       |        |                    |        |        |               |

| C2BUFPNT1  | 0520          |        | F3BF      | ><3:0> |        |        | F2BF   | <sup>D</sup> <3:0>            |              | F1BP<3:0> F0BP<3:0>           |          |        |       |        |                    | 0000   |        |               |

| C2BUFPNT2  | 0522          |        | -         | ><3:0> |        |        |        | P<3:0>                        |              |                               |          | P<3:0> |       |        |                    | 2<3:0> |        | 0000          |

| C2BUFPNT3  | 0524          |        | F11B      | P<3:0> |        |        | F10B   | P<3:0>                        |              |                               | F9BF     | ><3:0> |       |        | F8BF               | <3:0>  |        | 0000          |

| C2BUFPNT4  | 0526          |        | F15B      | P<3:0> |        |        | F14B   | P<3:0>                        |              |                               | F13BI    | D<3:0> |       |        | F12BI              | ><3:0> |        | 0000          |

| C2RXM0SID  | 0530          |        | SID<10:3> |        |        |        |        |                               | SID<2:0>     |                               | —        | MIDE   | _     | EID<   | 17:16>             | xxxx   |        |               |

| C2RXM0EID  | 0532          |        | EID<15:8> |        |        |        |        |                               |              |                               |          | EID    | <7:0> |        |                    |        | xxxx   |               |

| C2RXM1SID  | 0534          |        | SID<10:3> |        |        |        |        |                               | SID<2:0>     |                               | —        | MIDE   | —     | EID<   | 17:16>             | xxxx   |        |               |

| C2RXM1EID  | 0536          |        | EID<15:8> |        |        |        |        |                               |              |                               |          |        | EID   | <7:0>  |                    |        |        | xxxx          |

| C2RXM2SID  | 0538          |        |           |        | SID<   | 10:3>  |        |                               |              |                               | SID<2:0> |        | —     | MIDE   | —                  | EID<   | 17:16> | xxxx          |

| C2RXM2EID  | 053A          |        | EID<15:8> |        |        |        |        |                               |              |                               |          | EID    | <7:0> |        |                    |        | xxxx   |               |

| C2RXF0SID  | 0540          |        | SID<10:3> |        |        |        |        | SID<2:0> — EXIDE — EID<17:16> |              |                               |          |        |       |        | xxxx               |        |        |               |

| C2RXF0EID  | 0542          |        | EID<15:8> |        |        |        |        |                               |              |                               | EID      | <7:0>  |       | _      |                    | xxxx   |        |               |

| C2RXF1SID  | 0544          |        | SID<10:3> |        |        |        |        |                               | SID<2:0>     |                               |          | EXIDE  |       | EID<   | 17:16>             | xxxx   |        |               |

| C2RXF1EID  | 0546          |        |           |        | EID<   | 15:8>  |        |                               |              |                               |          |        | EID   | <7:0>  |                    |        |        | xxxx          |

| C2RXF2SID  | 0548          |        |           |        | SID<   | 10:3>  |        |                               |              |                               | SID<2:0> |        | —     | EXIDE  | —                  | EID<   | 17:16> | xxxx          |

| C2RXF2EID  | 054A          |        |           |        | EID<   | 15:8>  |        |                               |              | EID<7:0>                      |          |        |       |        |                    |        | xxxx   |               |

| C2RXF3SID  | 054C          |        |           |        | SID<   | 10:3>  |        |                               |              |                               |          |        |       |        | EXIDE — EID<17:16> |        |        | xxxx          |

| C2RXF3EID  | 054E          |        |           |        | EID<   | 15:8>  |        |                               |              | EID<7:0>                      |          |        |       |        |                    | xxxx   |        |               |

| C2RXF4SID  | 0550          |        |           |        | SID<   |        |        |                               |              | SID<2:0> — EXIDE — EID<17:16> |          |        |       |        |                    | 17:16> | xxxx   |               |

| C2RXF4EID  | 0552          |        |           |        | EID<   |        |        |                               |              | EID<7:0>                      |          |        |       |        |                    |        | xxxx   |               |

| C2RXF5SID  | 0554          |        |           |        |        | 10:3>  |        |                               |              | SID<2:0> — EXIDE — EID<17:16> |          |        |       |        |                    | 17:16> | xxxx   |               |

| C2RXF5EID  | 0556          |        |           |        |        | 15:8>  |        |                               |              |                               |          |        | EID   | <7:0>  |                    |        |        | XXXX          |

| C2RXF6SID  | 0558          |        |           |        |        | 10:3>  |        |                               |              |                               | SID<2:0> |        |       | EXIDE  | —                  | EID<   | 17:16> | xxxx          |

| C2RXF6EID  | 055A          |        |           |        |        | 15:8>  |        |                               |              |                               |          |        | EID   | <7:0>  |                    |        |        | xxxx          |

| C2RXF7SID  | 055C          |        |           |        |        | 10:3>  |        |                               |              |                               | SID<2:0> |        | —     | EXIDE  | —                  | EID<   | 17:16> | xxxx          |

| C2RXF7EID  | 055E          |        |           |        |        | 15:8>  |        |                               |              | EID<7:0>                      |          |        |       |        |                    |        | xxxx   |               |

| C2RXF8SID  | 0560          |        | SID<10:3> |        |        |        |        |                               | SID<2:0>     |                               |          | EXIDE  | —     | EID<   | 17:16>             | xxxx   |        |               |

| C2RXF8EID  | 0562          |        | EID<15:8> |        |        |        |        |                               | 010.0.5      |                               | EID      | <7:0>  |       |        |                    | xxxx   |        |               |

| C2RXF9SID  | 0564          |        | SID<10:3> |        |        |        |        | SID<2:0> — EXIDE — EID<17:16> |              |                               |          |        |       | 17:16> | XXXX               |        |        |               |

| C2RXF9EID  | 0566          |        | EID<15:8> |        |        |        |        |                               | EID<7:0>     |                               |          |        |       | 17 10: | XXXX               |        |        |               |

| C2RXF10SID | 0568          |        |           |        | SID<   |        |        |                               |              |                               | SID<2:0> |        |       | EXIDE  | —                  | EID<   | 17:16> | XXXX          |

| C2RXF10EID | 056A          |        | EID<15:8> |        |        |        |        |                               | EID<7:0>     |                               |          |        |       |        | XXXX               |        |        |               |

#### TABLE 4-25: ECAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33FJXXXMC708A/710A DEVICES

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IE:</b> Input Capture Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled  |

| bit 0 | INTOIE: External Interrupt 0 Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                     |

| R/W-0         | R/W-0                          | R/W-1                                                                                                                                               | R/W-1         | R/W-0                                 | R/W-0           | R/W-0              | R/W-0          |  |  |  |  |  |

|---------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------|-----------------|--------------------|----------------|--|--|--|--|--|

| ROI           |                                | DOZE<2:0>                                                                                                                                           |               | DOZEN <sup>(1)</sup>                  |                 | FRCDIV<2:0>        |                |  |  |  |  |  |

| bit 15        |                                |                                                                                                                                                     |               |                                       |                 |                    | bit 8          |  |  |  |  |  |

|               | <b>D A A A</b>                 |                                                                                                                                                     | DANO          | DAMA                                  | <b>D</b> /// 0  | DAMA               | <b>D</b> 444 0 |  |  |  |  |  |

| R/W-0         | R/W-1                          | U-0                                                                                                                                                 | R/W-0         | R/W-0                                 | R/W-0           | R/W-0              | R/W-0          |  |  |  |  |  |

|               | OST<1:0>                       |                                                                                                                                                     |               |                                       | PLLPRE<4:0      | >                  |                |  |  |  |  |  |

| bit 7         |                                |                                                                                                                                                     |               |                                       |                 |                    | bit 0          |  |  |  |  |  |

| Legend:       |                                | y = Value set                                                                                                                                       | from Configu  | ration bits on P                      | OR              |                    |                |  |  |  |  |  |

| R = Readabl   | e bit                          | W = Writable                                                                                                                                        | •             |                                       | nented bit, rea | d as '0'           |                |  |  |  |  |  |

| -n = Value at | POR                            | '1' = Bit is set                                                                                                                                    |               | '0' = Bit is clea                     |                 | x = Bit is unkr    | iown           |  |  |  |  |  |

|               |                                |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

| bit 15        | ROI: Recove                    | r on Interrupt bi                                                                                                                                   | t             |                                       |                 |                    |                |  |  |  |  |  |

|               | 1 = Interrupt                  | s will clear the [                                                                                                                                  | OZEN bit ar   | nd the processo                       | r clock/periphe | ral clock ratio is | set to 1:1     |  |  |  |  |  |

|               | 0 = Interrupt                  | s have no effect                                                                                                                                    | t on the DOZ  | EN bit                                |                 |                    |                |  |  |  |  |  |

| bit 14-12     | DOZE<2:0>:                     | Processor Cloc                                                                                                                                      | k Reduction   | Select bits                           |                 |                    |                |  |  |  |  |  |

|               | 000 = Fcy/1                    |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 001 = Fcy/2                    |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 010 = FCY/4<br>011 = FCY/8     | (default)                                                                                                                                           |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 100 = Fcy/16                   |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 101 = FCY/32                   |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 110 = Fcy/64                   | ŧ                                                                                                                                                   |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 111 = Fcy/12                   |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

| bit 11        | DOZEN: DOZ                     | <b>DOZEN:</b> DOZE Mode Enable bit <sup>(1)</sup><br>1 = DOZE<2:0> field specifies the ratio between the peripheral clocks and the processor clocks |               |                                       |                 |                    |                |  |  |  |  |  |

|               |                                |                                                                                                                                                     |               |                                       | ipheral clocks  | and the process    | or clocks      |  |  |  |  |  |

| h:+ 10 0      |                                | or clock/periphe                                                                                                                                    |               |                                       | _               |                    |                |  |  |  |  |  |

| bit 10-8      |                                |                                                                                                                                                     |               | or Postscaler bit                     | 5               |                    |                |  |  |  |  |  |

|               | 000 = FRC d<br>001 = FRC d     | ivide by 1 (defa                                                                                                                                    | uit)          |                                       |                 |                    |                |  |  |  |  |  |

|               | 010 = FRC d                    | •                                                                                                                                                   |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 011 = FRC d                    | •                                                                                                                                                   |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 100 <b>= FRC d</b>             |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 101 <b>= FRC d</b>             | •                                                                                                                                                   |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 110 = FRC d                    | •                                                                                                                                                   |               |                                       |                 |                    |                |  |  |  |  |  |

| L:1 7 0       | 111 = FRC d                    | ,                                                                                                                                                   |               |                                       |                 |                    | ( )            |  |  |  |  |  |

| bit 7-6       |                                |                                                                                                                                                     | Jutput Divide | er Select bits (al                    | so denoted as   | 'NZ', PLL posts    | caler)         |  |  |  |  |  |

|               | 00 = Output/2<br>01 = Output/4 |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 10 = Reserve                   |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 11 = Output/8                  |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

| bit 5         | -                              | ted: Read as '                                                                                                                                      | )'            |                                       |                 |                    |                |  |  |  |  |  |

| bit 4-0       | -                              |                                                                                                                                                     |               | ıt Divider bits (a                    | lso denoted as  | 'N1', PLL preso    | caler)         |  |  |  |  |  |

|               | 00000 <b>= Inp</b> u           | ut/2 (default)                                                                                                                                      |               | , , , , , , , , , , , , , , , , , , , |                 | , ,                | ,              |  |  |  |  |  |

|               | 00001 <b>= Inp</b>             | ut/3                                                                                                                                                |               |                                       |                 |                    |                |  |  |  |  |  |

|               | •                              |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | •                              |                                                                                                                                                     |               |                                       |                 |                    |                |  |  |  |  |  |

|               | •                              | 1/00                                                                                                                                                |               |                                       |                 |                    |                |  |  |  |  |  |

|               | 11111 = Inpu                   | 17/33                                                                                                                                               |               |                                       |                 |                    |                |  |  |  |  |  |

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

**2:** This register is reset only on a Power-on Reset (POR).

## REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | R/W-0  | R/W-0 |

|--------------|-------|--------------|-------|--------------|------------------|--------|-------|

| —            | —     | —            | —     |              | —                | AMSK9  | AMSK8 |

| bit 15       |       |              |       |              |                  |        | bit 8 |

|              |       |              |       |              |                  |        |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

| AMSK7        | AMSK6 | AMSK5        | AMSK4 | AMSK3        | AMSK2            | AMSK1  | AMSK0 |

| bit 7        |       |              |       |              |                  | •      | bit 0 |

|              |       |              |       |              |                  |        |       |

| Legend:      |       |              |       |              |                  |        |       |

| R = Readable | bit   | W = Writable | bit   | U = Unimpler | mented bit, read | as '0' |       |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSKx: Mask for Address bit x Select bits

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

## REGISTER 21-22: CiRXFUL1: ECAN™ RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  | C= Clearable bit      |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

RXFUL15:RXFUL0: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

### REGISTER 21-23: CIRXFUL2: ECAN™ RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend: C= Clearable bit |                  |                                                     |                    |  |  |  |  |

|--------------------------|------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit         | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR        | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 15-0 **RXFUL31:RXFUL16:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax        | Description                                                 | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|------------------------|-------------------------------------------------------------|---------------|----------------|--------------------------|

| 11                 | BTSS                 | BTSS    | f,#bit4                | Bit Test f, Skip if Set                                     | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS    | Ws,#bit4               | Bit Test Ws, Skip if Set                                    | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST    | f,#bit4                | Bit Test f                                                  | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,#bit4               | Bit Test Ws to C                                            | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,#bit4               | Bit Test Ws to Z                                            | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,Wb                  | Bit Test Ws <wb> to C</wb>                                  | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,Wb                  | Bit Test Ws <wb> to Z</wb>                                  | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4                | Bit Test then Set f                                         | 1             | 1              | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4               | Bit Test Ws to C, then Set                                  | 1             | 1              | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4               | Bit Test Ws to Z, then Set                                  | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL    | lit23                  | Call Subroutine                                             | 2             | 2              | None                     |

|                    |                      | CALL    | Wn                     | Call Indirect Subroutine                                    | 1             | 2              | None                     |

| 15                 | CLR                  | CLR     | f                      | f = 0x0000                                                  | 1             | 1              | None                     |

|                    |                      | CLR     | WREG                   | WREG = 0x0000                                               | 1             | 1              | None                     |

|                    |                      | CLR     | Ws                     | Ws = 0x0000                                                 | 1             | 1              | None                     |

|                    |                      | CLR     | Acc,Wx,Wxd,Wy,Wyd,AWB  | Clear Accumulator                                           | 1             | 1              | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT  |                        | Clear Watchdog Timer                                        | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | COM     | f                      | f = f                                                       | 1             | 1              | N,Z                      |

|                    |                      | COM     | f,WREG                 | WREG = f                                                    | 1             | 1              | N,Z                      |

|                    |                      | COM     | Ws,Wd                  | $Wd = \overline{Ws}$                                        | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP      | f                      | Compare f with WREG                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit5               | Compare Wb with lit5                                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                  | Compare Wb with Ws (Wb – Ws)                                | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CPO                  | CP0     | f                      | Compare f with 0x0000                                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP0     | Ws                     | Compare Ws with 0x0000                                      | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                      | Compare f with WREG, with Borrow                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit5               | Compare Wb with lit5, with Borrow                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                  | Compare Wb with Ws, with Borrow (Wb – Ws – $\overline{C}$ ) | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb, Wn                 | Compare Wb with Wn, Skip if =                               | 1             | 1<br>(2 or 3)  | None                     |

| 22                 | CPSGT                | CPSGT   | Wb, Wn                 | Compare Wb with Wn, Skip if >                               | 1             | 1<br>(2 or 3)  | None                     |

| 23                 | CPSLT                | CPSLT   | Wb, Wn                 | Compare Wb with Wn, Skip if <                               | 1             | 1<br>(2 or 3)  | None                     |

| 24                 | CPSNE                | CPSNE   | Wb, Wn                 | Compare Wb with Wn, Skip if ≠                               | 1             | 1<br>(2 or 3)  | None                     |

| 25                 | DAW                  | DAW     | Wn                     | Wn = Decimal Adjust Wn                                      | 1             | 1              | С                        |

| 26                 | DEC                  | DEC     | f                      | f = f - 1                                                   | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | f,WREG                 | WREG = f – 1                                                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | Ws,Wd                  | Wd = Ws – 1                                                 | 1             | 1              | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2    | f                      | f = f - 2                                                   | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | f,WREG                 | WREG = f – 2                                                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | Ws,Wd                  | Wd = Ws - 2                                                 | 1             | 1              | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI    | #lit14                 | Disable Interrupts for k Instruction Cycles                 | 1             | 1              | None                     |

| 29                 | DIV                  | DIV.S   | Wm,Wn                  | Signed 16/16-bit Integer Divide                             | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.SD  | Wm,Wn                  | Signed 32/16-bit Integer Divide                             | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.U   | Wm,Wn                  | Unsigned 16/16-bit Integer Divide                           | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.UD  | Wm,Wn                  | Unsigned 32/16-bit Integer Divide                           | 1             | 18             | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF    | Wm,Wn                  | Signed 16/16-bit Fractional Divide                          | 1             | 18             | N,Z,C,OV                 |

| 31                 | DO                   | DO      | <pre>#lit14,Expr</pre> | Do Code to PC + Expr, lit14 + 1 Times                       | 2             | 2              | None                     |

|                    |                      | DO      | Wn,Expr                | Do Code to PC + Expr, (Wn) + 1 Times                        | 2             | 2              | None                     |

| 32                 | ED                   | ED      | Wm*Wm,Acc,Wx,Wy,Wxd    | Euclidean Distance (no accumulate)                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC    | Wm*Wm,Acc,Wx,Wy,Wxd    | Euclidean Distance                                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

## TABLE 24-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| DC CHARACT                      | ERISTICS               |             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |         |  |  |  |

|---------------------------------|------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|---------|--|--|--|

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup> | Max         | Units                                                                                                                                                                                                                                                                                   | Conditions |        |         |  |  |  |

| Idle Current (I                 | DLE): Core Of          | f, Clock On | Base Current                                                                                                                                                                                                                                                                            | (1)        |        |         |  |  |  |

| DC40d                           | 3                      | 25          | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |         |  |  |  |

| DC40a                           | 3                      | 25          | mA                                                                                                                                                                                                                                                                                      | +25°C      |        |         |  |  |  |

| DC40b                           | 3                      | 25          | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V   | 10 MIPS |  |  |  |

| DC40c                           | 3                      | 25          | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |  |

| DC41d                           | 4                      | 25          | mA                                                                                                                                                                                                                                                                                      | -40°C      |        | 16 MIPS |  |  |  |

| DC41a                           | 5                      | 25          | mA                                                                                                                                                                                                                                                                                      | +25°C      | 2.21/  |         |  |  |  |

| DC41b                           | 6                      | 25          | mA                                                                                                                                                                                                                                                                                      | +85°C      | - 3.3V | 10 MIPS |  |  |  |

| DC41c                           | 6                      | 25          | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |  |

| DC42d                           | 8                      | 25          | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |         |  |  |  |

| DC42a                           | 9                      | 25          | mA                                                                                                                                                                                                                                                                                      | +25°C      | - 3.3V |         |  |  |  |

| DC42b                           | 10                     | 25          | mA                                                                                                                                                                                                                                                                                      | +85°C      | - 3.3V | 20 MIPS |  |  |  |

| DC42c                           | 10                     | 25          | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |  |

| DC43a                           | 15                     | 25          | mA                                                                                                                                                                                                                                                                                      | +25°C      |        |         |  |  |  |

| DC43d                           | 15                     | 25          | mA                                                                                                                                                                                                                                                                                      | -40°C      | 2.21/  | 20 МІЛЯ |  |  |  |

| DC43b                           | 15                     | 25          | mA                                                                                                                                                                                                                                                                                      | +85°C      | - 3.3V | 30 MIPS |  |  |  |

| DC43c                           | 15                     | 25          | mA                                                                                                                                                                                                                                                                                      | +125°C     | 1      |         |  |  |  |

| DC44d                           | 16                     | 25          | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |         |  |  |  |

| DC44a                           | 16                     | 25          | mA                                                                                                                                                                                                                                                                                      | +25°C      | 2.21/  |         |  |  |  |

| DC44b                           | 16                     | 25          | mA                                                                                                                                                                                                                                                                                      | +85°C      | - 3.3V | 40 MIPS |  |  |  |

| DC44c                           | 16                     | 25          | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |         |  |  |  |

### TABLE 26-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: Base IIDLE current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

• No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- · JTAG is disabled

- **2:** These parameters are characterized but not tested in manufacturing.

- **3:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

| DC CHARACTERISTICS (unless otherw       |                        |      |       |            | perating Conditions: 3.0V to 3.6V<br>erwise stated)<br>mperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                              |  |  |  |  |

|-----------------------------------------|------------------------|------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

| Parameter<br>No. <sup>(3)</sup>         | Typical <sup>(2)</sup> | Мах  | Units | Conditions |                                                                                                                                                                                |                                              |  |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup> |                        |      |       |            |                                                                                                                                                                                |                                              |  |  |  |  |

| DC60d                                   | 50                     | 200  | μA    | -40°C      |                                                                                                                                                                                |                                              |  |  |  |  |

| DC60a                                   | 50                     | 200  | μA    | +25°C      | 3.3V                                                                                                                                                                           | Base Power-Down Current <sup>(3)</sup>       |  |  |  |  |

| DC60b                                   | 200                    | 500  | μA    | +85°C      | 3.3V                                                                                                                                                                           | base Fower-Down Currenter                    |  |  |  |  |

| DC60c                                   | 600                    | 1000 | μA    | +125°C     |                                                                                                                                                                                |                                              |  |  |  |  |

| DC61d                                   | 8                      | 13   | μΑ    | -40°C      |                                                                                                                                                                                |                                              |  |  |  |  |

| DC61a                                   | 10                     | 15   | μA    | +25°C      | 2 2)/                                                                                                                                                                          | Watchdog Timer Current: ∆IwDT <sup>(3)</sup> |  |  |  |  |

| DC61b                                   | 12                     | 20   | μA    | +85°C      | 3.3V                                                                                                                                                                           | Watchdog Timer Current: AlwD107              |  |  |  |  |

| DC61c                                   | 13                     | 25   | μA    | +125°C     |                                                                                                                                                                                |                                              |  |  |  |  |

### TABLE 26-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** IPD (Sleep) current is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

· CLKO is configured as an I/O input pin in the Configuration word

All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD, WDT and FSCM are disabled, all peripheral modules except the ADC are disabled (PMDx bits are all '1's). The following ADC settings are enabled for each ADC module (ADCx) prior to executing the PWRSAV instruction: ADON = 1, VCFG = 1, AD12B = 1 and ADxMD = 0.

• VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- RTCC is disabled.

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The Watchdog Timer Current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but are not tested in manufacturing.