Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

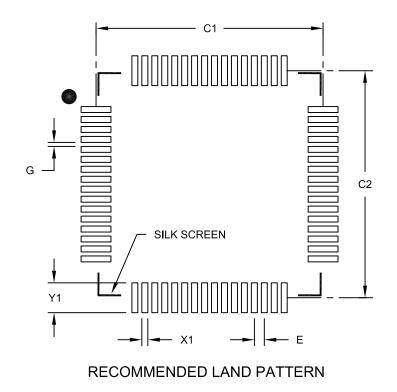

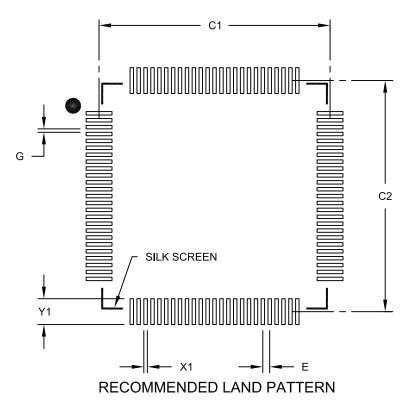

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc710a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

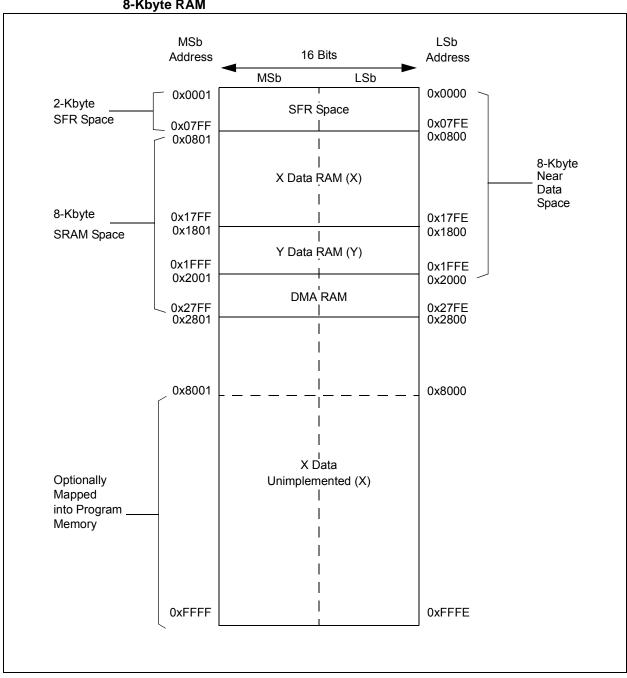

# FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 8-Kbyte RAM

| TADLE 4-19. DIVIA REGISTER IVIAR | TABLE 4-19: | DMA REGISTER MAP |

|----------------------------------|-------------|------------------|

|----------------------------------|-------------|------------------|

| IABLE 4   | <del>1</del> -19: | DIVIA             | REGIS     |        |             |        |        |       |       | 1         |       |       |        |           |       |       |       |               |

|-----------|-------------------|-------------------|-----------|--------|-------------|--------|--------|-------|-------|-----------|-------|-------|--------|-----------|-------|-------|-------|---------------|

| File Name | Addr              | Bit 15            | Bit 14    | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| DMA0CON   | 0380              | CHEN              | SIZE      | DIR    | HALF        | NULLW  | _      | —     | —     | _         |       | AMOD  | E<1:0> | —         | _     | MODE  | <1:0> | 0000          |

| DMA0REQ   | 0382              | FORCE             | _         | _      | _           | _      | _      | _     | _     | _         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA0STA   | 0384              |                   |           |        |             |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0STB   | 0386              |                   |           |        |             |        |        |       | S     | STB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0PAD   | 0388              |                   |           |        |             |        |        |       | F     | AD<15:0>  |       |       |        |           |       |       |       | 0000          |

| DMA0CNT   | 038A              | —                 | —         | _      | _           | —      | _      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA1CON   | 038C              | CHEN              | SIZE      | DIR    | HALF        | NULLW  | _      | _     | _     | _         | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000          |

| DMA1REQ   | 038E              | FORCE             | —         | _      | IRQSEL<6:0> |        |        |       |       |           |       |       | 0000   |           |       |       |       |               |

| DMA1STA   | 0390              |                   |           |        |             |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1STB   | 0392              |                   | STB<15:0> |        |             |        |        |       |       |           |       | 0000  |        |           |       |       |       |               |

| DMA1PAD   | 0394              |                   | PAD<15:0> |        |             |        |        |       |       |           |       | 0000  |        |           |       |       |       |               |

| DMA1CNT   | 0396              | CNT<9:0>          |           |        |             |        |        |       |       | 0000      |       |       |        |           |       |       |       |               |

| DMA2CON   | 0398              | CHEN              | SIZE      | DIR    | HALF        | NULLW  |        | _     | _     | _         | _     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000          |

| DMA2REQ   | 039A              | FORCE IRQSEL<6:0> |           |        |             |        |        |       |       | 0000      |       |       |        |           |       |       |       |               |

| DMA2STA   | 039C              |                   | STA<15:0> |        |             |        |        |       |       |           |       | 0000  |        |           |       |       |       |               |

| DMA2STB   | 039E              |                   | STB<15:0> |        |             |        |        |       |       |           | 0000  |       |        |           |       |       |       |               |

| DMA2PAD   | 03A0              |                   |           |        |             |        |        |       | F     | PAD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2CNT   | 03A2              | —                 | —         | —      |             | _      | —      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA3CON   | 03A4              | CHEN              | SIZE      | DIR    | HALF        | NULLW  |        | _     |       |           |       | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000          |

| DMA3REQ   | 03A6              | FORCE             | _         | _      | _           | _      | _      | _     | _     | _         |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA3STA   | 03A8              |                   |           |        |             |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3STB   | 03AA              |                   |           |        |             |        |        |       | S     | STB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3PAD   | 03AC              |                   |           |        |             |        |        |       | F     | PAD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3CNT   | 03AE              | —                 | —         | —      |             | _      | —      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA4CON   | 03B0              | CHEN              | SIZE      | DIR    | HALF        | NULLW  | _      | _     |       | —         | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000          |

| DMA4REQ   | 03B2              | FORCE             | _         | _      | _           | _      | _      | _     | _     | _         |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA4STA   | 03B4              |                   |           |        |             |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4STB   | 03B6              |                   |           |        |             |        |        |       | S     | STB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4PAD   | 03B8              |                   |           |        |             |        |        |       | F     | PAD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4CNT   | 03BA              | —                 | —         | —      | _           | _      | —      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA5CON   | 03BC              | CHEN              | SIZE      | DIR    | HALF        | NULLW  | _      | —     | —     | _         | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000          |

| DMA5REQ   | 03BE              | FORCE             | _         | _      | _           | _      | _      | _     | _     | —         |       |       |        | RQSEL<6:0 | >     |       |       | 0000          |

| DMA5STA   | 03C0              |                   |           |        |             |        |        |       |       | STA<15:0> | •     |       |        |           |       |       |       | 0000          |

| DMA5STB   | 03C2              |                   |           |        |             |        |        |       | S     | STB<15:0> |       |       |        |           |       |       |       | 0000          |

| L         |                   |                   |           |        |             |        |        |       |       |           |       |       |        |           |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

| U-0           | R/W-0      | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|---------------|------------|----------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| —             | DMA1IF     | AD1IF                            | U1TXIF           | U1RXIF            | SPI1IF          | SPI1EIF         | T3IF   |

| bit 15        |            |                                  |                  |                   |                 |                 | bit 8  |

| R/W-0         | R/W-0      | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| T2IF          | OC2IF      | IC2IF                            | DMA01IF          | T1IF              | OC1IF           | IC1IF           | INT0IF |

| bit 7         | L.         |                                  | 1                |                   |                 |                 | bit (  |

| Legend:       |            |                                  |                  |                   |                 |                 |        |

| R = Readable  | e bit      | W = Writable                     | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |

| -n = Value at | POR        | '1' = Bit is se                  | t                | '0' = Bit is clea | ared            | x = Bit is unkn | iown   |

| bit 15        | Unimplemen | ted: Read as                     | ʻ0'              |                   |                 |                 |        |

| bit 14        | -          |                                  | ata Transfer C   | omplete Interro   | upt Flag Status | s bit           |        |

|               |            | request has oc                   |                  |                   |                 |                 |        |

|               | •          | request has no                   |                  |                   |                 |                 |        |

| bit 13        |            |                                  | Complete Interr  | upt Flag Status   | s bit           |                 |        |

|               |            | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 12        | •          |                                  | r Interrupt Flag | g Status bit      |                 |                 |        |

|               |            | request has oc                   |                  |                   |                 |                 |        |

|               | -          | request has no                   |                  |                   |                 |                 |        |

| bit 11        |            |                                  | nterrupt Flag S  | Status bit        |                 |                 |        |

|               |            | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 10        | •          | •                                | ot Flag Status b | oit               |                 |                 |        |

|               |            | request has oc                   |                  |                   |                 |                 |        |

|               | -          | request has no                   |                  |                   |                 |                 |        |

| bit 9         |            |                                  | pt Flag Status I | bit               |                 |                 |        |

|               |            | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 8         | •          | Interrupt Flag                   |                  |                   |                 |                 |        |

|               |            | request has oc                   |                  |                   |                 |                 |        |

|               | •          | request has no                   |                  |                   |                 |                 |        |

| bit 7         |            | Interrupt Flag                   |                  |                   |                 |                 |        |

|               |            | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 6         | -          | -                                | nannel 2 Interru | upt Flag Status   | bit             |                 |        |

|               |            | request has oc                   |                  |                   |                 |                 |        |

|               | •          | request has no                   |                  |                   |                 |                 |        |

| bit 5         | •          | -                                | el 2 Interrupt F | lag Status bit    |                 |                 |        |

|               |            | request has oc<br>request has no |                  |                   |                 |                 |        |

| bit 4         | -          | -                                | ata Transfer C   | omplete Interri   | upt Flag Status | s bit           |        |

|               |            | request has oc                   |                  |                   |                 |                 |        |

|               | -          | request has no                   |                  |                   |                 |                 |        |

| bit 3         |            | Interrupt Flag<br>request has or |                  |                   |                 |                 |        |

|               |            |                                  |                  |                   |                 |                 |        |

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0         | U-0             | R/W-0                                                                    | U-0             | U-0              | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| FLTAIF        | —               | DMA5IF                                                                   |                 | _                | QEIIF            | PWMIF           | C2IF  |  |  |  |  |

| bit 15        |                 | •                                                                        |                 | ÷                |                  |                 | bit 8 |  |  |  |  |

| R/W-0         | R/W-0           | R/W-0                                                                    | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| C2RXIF        | INT4IF          | INT3IF                                                                   | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |  |  |  |  |

| bit 7         |                 |                                                                          |                 |                  |                  | 0.202           | bit C |  |  |  |  |

| Legend:       |                 |                                                                          |                 |                  |                  |                 |       |  |  |  |  |

| R = Readabl   | e bit           | W = Writable                                                             | bit             | U = Unimplei     | mented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at | POR             | '1' = Bit is set                                                         |                 | '0' = Bit is cle | eared            | x = Bit is unkn | iown  |  |  |  |  |

|               |                 |                                                                          |                 |                  |                  |                 |       |  |  |  |  |

| bit 15        | FLTAIF: PWN     | / Fault A Interr                                                         | upt Flag Statu  | us bit           |                  |                 |       |  |  |  |  |

|               |                 | request has oc                                                           |                 |                  |                  |                 |       |  |  |  |  |

|               | •               | request has no                                                           |                 |                  |                  |                 |       |  |  |  |  |

| bit 14        | -               | ted: Read as '                                                           |                 |                  |                  |                 |       |  |  |  |  |

| bit 13        |                 |                                                                          |                 | Complete Interr  | rupt Flag Status | bit             |       |  |  |  |  |

|               |                 | request has occ<br>request has not                                       |                 |                  |                  |                 |       |  |  |  |  |

| bit 12-11     | •               | •                                                                        |                 |                  |                  |                 |       |  |  |  |  |

| bit 10        | -               | Unimplemented: Read as '0'<br>QEIIF: QEI Event Interrupt Flag Status bit |                 |                  |                  |                 |       |  |  |  |  |

|               |                 | request has oc                                                           | 0               |                  |                  |                 |       |  |  |  |  |

|               |                 | request has not                                                          |                 |                  |                  |                 |       |  |  |  |  |

| bit 9         | PWMIF: PWN      | A Interrupt Flag                                                         | Status bit      |                  |                  |                 |       |  |  |  |  |

|               |                 | request has occ<br>request has not                                       |                 |                  |                  |                 |       |  |  |  |  |

| bit 8         | C2IF: ECAN2     | 2 Event Interrup                                                         | t Flag Status   | bit              |                  |                 |       |  |  |  |  |

|               | •               | request has oc                                                           |                 |                  |                  |                 |       |  |  |  |  |

|               | 0 = Interrupt r | request has not                                                          | occurred        |                  |                  |                 |       |  |  |  |  |

| bit 7         |                 | N2 Receive D                                                             | •               | errupt Flag Sta  | itus bit         |                 |       |  |  |  |  |

|               | •               | request has oco<br>request has not                                       |                 |                  |                  |                 |       |  |  |  |  |

| bit 6         | =               | nal Interrupt 4                                                          |                 | it               |                  |                 |       |  |  |  |  |

|               |                 | request has oc                                                           | -               | it.              |                  |                 |       |  |  |  |  |

|               |                 | request has not                                                          |                 |                  |                  |                 |       |  |  |  |  |

| bit 5         | INT3IF: Exter   | INT3IF: External Interrupt 3 Flag Status bit                             |                 |                  |                  |                 |       |  |  |  |  |

|               |                 | request has oc                                                           |                 |                  |                  |                 |       |  |  |  |  |

|               | -               | request has not                                                          |                 |                  |                  |                 |       |  |  |  |  |

| bit 4         |                 | Interrupt Flag                                                           |                 |                  |                  |                 |       |  |  |  |  |

|               | •               | request has oco<br>request has not                                       |                 |                  |                  |                 |       |  |  |  |  |

| bit 3         | -               | Interrupt Flag                                                           |                 |                  |                  |                 |       |  |  |  |  |

|               |                 | request has oc                                                           |                 |                  |                  |                 |       |  |  |  |  |

|               | •               | request has not                                                          |                 |                  |                  |                 |       |  |  |  |  |

| bit 2         | MI2C2IF: I2C    | 2 Master Even                                                            | ts Interrupt FI | ag Status bit    |                  |                 |       |  |  |  |  |

|               |                 | request has oc                                                           |                 |                  |                  |                 |       |  |  |  |  |

|               | 0 = Interrupt r | request has not                                                          | occurred        |                  |                  |                 |       |  |  |  |  |

# REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| REGISTER 7-12: | IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| R/W-0         | R/W-0                                                                                        | U-0                                                 | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |

|---------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|

| T6IE          | DMA4IE                                                                                       |                                                     | OC8IE            | OC7IE            | OC6IE            | OC5IE           | IC6IE   |  |

| bit 15        |                                                                                              | ·                                                   |                  |                  |                  |                 | bit 8   |  |

| R/W-0         | R/W-0                                                                                        | R/W-0                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |

| IC5IE         | IC4IE                                                                                        | IC3IE                                               | DMA3IE           | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |  |

| bit 7         | ł                                                                                            |                                                     |                  |                  |                  |                 | bit 0   |  |

| Legend:       |                                                                                              |                                                     |                  |                  |                  |                 |         |  |

| R = Readable  | e bit                                                                                        | W = Writable                                        | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |  |

| -n = Value at | POR                                                                                          | '1' = Bit is set                                    |                  | '0' = Bit is cle | eared            | x = Bit is unki | nown    |  |

| bit 15        | T6IF: Timer6                                                                                 | Interrupt Enabl                                     | e bit            |                  |                  |                 |         |  |

|               |                                                                                              | request enabled                                     |                  |                  |                  |                 |         |  |

|               |                                                                                              | request not ena                                     |                  |                  |                  |                 |         |  |

| bit 14        |                                                                                              | A Channel 4 D                                       |                  | Complete Interi  | rupt Enable bit  |                 |         |  |

|               |                                                                                              | request enableo<br>request not ena                  |                  |                  |                  |                 |         |  |

| bit 13        |                                                                                              | ted: Read as '                                      |                  |                  |                  |                 |         |  |

| bit 12        | -                                                                                            | ut Compare Ch                                       |                  | unt Enable bit   |                  |                 |         |  |

| 51(12         | •                                                                                            | request enabled                                     |                  |                  |                  |                 |         |  |

|               |                                                                                              | equest not ena                                      |                  |                  |                  |                 |         |  |

| bit 11        | •                                                                                            | ut Compare Ch                                       |                  | upt Enable bit   |                  |                 |         |  |

|               | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                                                     |                  |                  |                  |                 |         |  |

| bit 10        | •                                                                                            | ut Compare Ch                                       |                  | upt Enable bit   |                  |                 |         |  |

|               | 1 = Interrupt r                                                                              | request enabled                                     | b                |                  |                  |                 |         |  |

|               | •                                                                                            | request not ena                                     |                  |                  |                  |                 |         |  |

| bit 9         | 1 = Interrupt r                                                                              | ut Compare Ch<br>request enableo<br>request not ena | b                | upt Enable bit   |                  |                 |         |  |

| bit 8         |                                                                                              | Capture Channe                                      |                  | Enable bit       |                  |                 |         |  |

|               | 1 = Interrupt r                                                                              | request enable<br>request not ena                   | d                |                  |                  |                 |         |  |

| bit 7         | IC5IE: Input C                                                                               | Capture Channe                                      | el 5 Interrupt I | Enable bit       |                  |                 |         |  |

|               |                                                                                              | request enable<br>request not ena                   |                  |                  |                  |                 |         |  |

| bit 6         | IC4IE: Input C                                                                               | Capture Channe                                      | el 4 Interrupt I | Enable bit       |                  |                 |         |  |

|               |                                                                                              | request enableo<br>request not ena                  |                  |                  |                  |                 |         |  |

| bit 5         | •                                                                                            | Capture Channe                                      |                  | Enable bit       |                  |                 |         |  |

|               | 1 = Interrupt r                                                                              | request enabled<br>request not ena                  | d                |                  |                  |                 |         |  |

| bit 4         | DMA3IE: DM                                                                                   | A Channel 3 D                                       | ata Transfer C   | Complete Interi  | rupt Enable bit  |                 |         |  |

|               |                                                                                              | request enabled<br>request not ena                  |                  |                  |                  |                 |         |  |

| bit 3         | -                                                                                            | Event Interrup                                      |                  |                  |                  |                 |         |  |

|               |                                                                                              | equest enable                                       |                  |                  |                  |                 |         |  |

### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 (CONTINUED)

| bit 1 | SI2C2IE: I2C2 Slave Events Interrupt Enable bit |

|-------|-------------------------------------------------|

|       | 1 = Interrupt request enabled                   |

|       | 0 = Interrupt request not enabled               |

|       |                                                 |

- bit 0 T7IE: Timer7 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0          | R/W-1                                                                                                                              | R/W-0                 | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| _            |                                                                                                                                    | T8IP<2:0>             |                |                   |                 | MI2C2IP<2:0>    |       |  |  |  |  |

| bit 15       | ·                                                                                                                                  |                       |                |                   | •               |                 | bit   |  |  |  |  |

|              |                                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

| U-0          | R/W-1                                                                                                                              | R/W-0                 | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                                                                                                                    | SI2C2IP<2:0>          |                | —                 |                 | T7IP<2:0>       | 1.11  |  |  |  |  |

| bit 7        |                                                                                                                                    |                       |                |                   |                 |                 | bit   |  |  |  |  |

| Legend:      |                                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                                                                             | W = Writable b        | oit            | U = Unimple       | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                                                                                                              | '1' = Bit is set      |                | '0' = Bit is cle  | eared           | x = Bit is unkr | iown  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                          | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |

| bit 14-12    | -                                                                                                                                  | Timer8 Interrupt      |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                                    | rupt is priority 7 (h | -              | ty interrupt)     |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Inter                                                                                                                        | rupt is priority 1    |                |                   |                 |                 |       |  |  |  |  |

|              | 000 = Inter                                                                                                                        | rupt source is disa   | abled          |                   |                 |                 |       |  |  |  |  |

| bit 11       | Unimpleme                                                                                                                          | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |

| bit 10-8     | MI2C2IP<2:0>: I2C2 Master Events Interrupt Priority bits                                                                           |                       |                |                   |                 |                 |       |  |  |  |  |

|              | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> </ul>                                          |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                |                       |                |                   |                 |                 |       |  |  |  |  |

| bit 7        |                                                                                                                                    | ented: Read as '0     |                |                   |                 |                 |       |  |  |  |  |

| bit 6-4      | -                                                                                                                                  |                       |                | unt Priority hite |                 |                 |       |  |  |  |  |

| DIL 0-4      | <b>SI2C2IP&lt;2:0&gt;:</b> I2C2 Slave Events Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       | ignoot phon    | ty monapty        |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                                 |                       |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                                    | rupt source is disa   | abled          |                   |                 |                 |       |  |  |  |  |

| bit 3        | Unimpleme                                                                                                                          | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |

| bit 2-0      | T7IP<2:0>:                                                                                                                         | Timer7 Interrupt      | Priority bits  |                   |                 |                 |       |  |  |  |  |

|              | 111 = Inter                                                                                                                        | rupt is priority 7 (h | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Inter                                                                                                                        | rupt is priority 1    |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                                    | rupt source is disa   |                |                   |                 |                 |       |  |  |  |  |

# REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | ST/   | 4<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | id as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

## REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|------------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                  |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15           |       |                  |       |                  |                 |                 | bit 8 |

|                  |       |                  |       |                  |                 |                 |       |

| R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                  |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7            |       |                  |       |                  |                 |                 | bit 0 |

|                  |       |                  |       |                  |                 |                 |       |

| Legend:          |       |                  |       |                  |                 |                 |       |

| R = Readable b   | oit   | W = Writable b   | pit   | U = Unimplen     | nented bit, rea | id as '0'       |       |

| -n = Value at Po | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

**EQUATION 9-3:**

**XT WITH PLL MODE**

= 40 MIPS

**EXAMPLE**

$FCY = \frac{FOSC}{2} = \frac{1}{2} \left( \frac{10000000 \cdot 32}{2 \cdot 2} \right)$

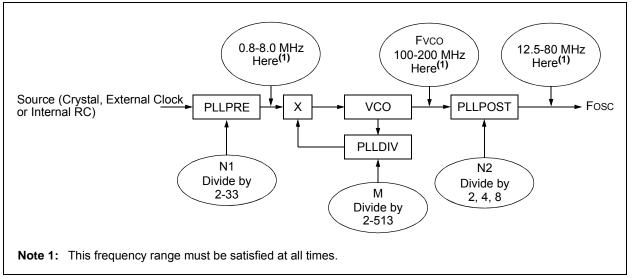

For example, suppose a 10 MHz crystal is being used with "XT with PLL" as the selected oscillator mode. If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz. If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 \* 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

#### FIGURE 9-2: dsPIC33FJXXXMCX06A/X08A/X10A PLL BLOCK DIAGRAM

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Note |

|--------------------------------------------------|-------------------|-------------|------------|----------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | xx          | 111        | 1, 2     |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | xx          | 110        | 1        |

| Low-Power RC Oscillator (LPRC)                   | Internal          | XX          | 101        | 1        |

| Secondary (Timer1) Oscillator (Sosc)             | Secondary         | xx          | 100        | 1        |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | -        |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -        |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1        |

| Primary Oscillator (HS)                          | Primary           | 10          | 010        | _        |

| Primary Oscillator (XT)                          | Primary           | 01          | 010        | —        |

| Primary Oscillator (EC)                          | Primary           | 00          | 010        | 1        |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal          | XX          | 001        | 1        |

| Fast RC Oscillator (FRC)                         | Internal          | xx          | 000        | 1        |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### REGISTER 21-10: CiCFG2: ECAN™ BAUD RATE CONFIGURATION REGISTER 2

| U-0             | R/W-x                         | U-0               | U-0               | U-0             | R/W-x           | R/W-x             | R/W-x |

|-----------------|-------------------------------|-------------------|-------------------|-----------------|-----------------|-------------------|-------|

|                 | WAKFIL                        | —                 | _                 |                 |                 | SEG2PH<2:0>       |       |

| bit 15          |                               | I                 | ł                 |                 | l               |                   | bit 8 |

|                 |                               |                   |                   |                 |                 |                   |       |

| R/W-x           | R/W-x                         | R/W-x             | R/W-x             | R/W-x           | R/W-x           | R/W-x             | R/W-x |

| SEG2PHTS        | SAM                           |                   | SEG1PH<2:0        | >               |                 | PRSEG<2:0>        |       |

| bit 7           |                               |                   |                   |                 |                 |                   | bit ( |

| Legend:         |                               |                   |                   |                 |                 |                   |       |

| R = Readable    | h:t                           |                   | , bit             |                 | monted bit rea  | ad aa '0'         |       |

| -n = Value at F |                               | W = Writable      |                   | 0 = Onimpler    | mented bit, rea | x = Bit is unkn   | 0.110 |

|                 | UR                            |                   | :L                |                 | areu            |                   | IOWI  |

| bit 15          | Unimplemen                    | ted: Read as      | <b>'</b> 0'       |                 |                 |                   |       |

| bit 14          | -                             |                   | Line Filter for \ | Nake-up bit     |                 |                   |       |

|                 |                               | bus line filter   |                   | ·               |                 |                   |       |

|                 | 0 = CAN bus                   | line filter is no | t used for wak    | e-up            |                 |                   |       |

| bit 13-11       | Unimplemen                    | ted: Read as      | ʻ0'               |                 |                 |                   |       |

| bit 10-8        | SEG2PH<2:0                    | )>: Phase Bu      | ffer Segment 2    | bits            |                 |                   |       |

|                 | 111 = Length                  |                   |                   |                 |                 |                   |       |

|                 | 000 = Length                  |                   |                   |                 |                 |                   |       |

| bit 7           |                               | 0                 | ent 2 Time Sel    | ect bit         |                 |                   |       |

|                 | 1 = Freely pro<br>0 = Maximum |                   | oits or Informat  | tion Processing | ı Time (IPT), v | /hichever is grea | ter   |

| bit 6           |                               | le of the CAN     |                   |                 |                 | 0                 |       |

|                 | •                             |                   | ee times at the   | sample point    |                 |                   |       |

|                 | 0 = Bus line is               | s sampled one     | ce at the samp    | le point        |                 |                   |       |

| bit 5-3         | SEG1PH<2:0                    | )>: Phase But     | ffer Segment 1    | bits            |                 |                   |       |

|                 | 111 = Length                  |                   |                   |                 |                 |                   |       |

|                 | 000 = Length                  |                   |                   |                 |                 |                   |       |

| bit 2-0         |                               |                   | n Time Segme      | nt bits         |                 |                   |       |

|                 | 111 = Length<br>000 = Length  |                   |                   |                 |                 |                   |       |

|                 | ooo – Lengin                  | JI A I GI         |                   |                 |                 |                   |       |

## REGISTER 21-18: CiFMSKSEL1: ECAN™ FILTER 7-0 MASK SELECTION REGISTER

| R/W-0         | R/W-0        | R/W-0                                               | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  | )     |

|---------------|--------------|-----------------------------------------------------|-------------------|-------------------|------------------|-----------------|--------|-------|

| F7MS          | SK<1:0>      | F6MSł                                               | <<1:0>            | F5MS              | K<1:0>           | F4MSh           | <<1:0> |       |

| bit 15        |              |                                                     |                   |                   |                  |                 | k      | bit 8 |

|               |              |                                                     |                   |                   |                  |                 |        |       |

| R/W-0         | R/W-0        | R/W-0                                               | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  | )     |

|               | SK<1:0>      | F2MSł                                               | <<1:0>            | F1MS              | K<1:0>           | FOMSH           | -      |       |

| bit 7         |              |                                                     |                   |                   |                  |                 | k      | bit 0 |

| Legend:       |              |                                                     |                   |                   |                  |                 |        |       |

| R = Readabl   | e bit        | W = Writable                                        | bit               | U = Unimplen      | nented bit, read | d as '0'        |        |       |

| -n = Value at | POR          | '1' = Bit is set                                    |                   | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |       |

|               |              |                                                     |                   |                   |                  |                 |        |       |

| bit 15-14     |              | : Mask Source                                       | e for Filter 7 bi | t                 |                  |                 |        |       |

|               |              | ed; do not use                                      | riotoro contain   | maak              |                  |                 |        |       |

|               | •            | ince Mask 2 reg<br>ince Mask 1 reg                  | •                 |                   |                  |                 |        |       |

|               |              | ince Mask 0 reg                                     |                   |                   |                  |                 |        |       |

| bit 13-12     | •            | ·: Mask Source                                      |                   |                   |                  |                 |        |       |

|               |              | ed; do not use                                      |                   |                   |                  |                 |        |       |

|               |              | nce Mask 2 reg                                      |                   |                   |                  |                 |        |       |

|               |              | ince Mask 1 reg<br>ince Mask 0 reg                  |                   |                   |                  |                 |        |       |

| bit 11-10     | -            | : Mask Source                                       | -                 |                   |                  |                 |        |       |

|               |              | ed; do not use                                      |                   |                   |                  |                 |        |       |

|               |              | nce Mask 2 reg                                      |                   |                   |                  |                 |        |       |

|               |              | ince Mask 1 reg                                     |                   |                   |                  |                 |        |       |

| bit 9-8       | -            | ince Mask 0 reg                                     | -                 |                   |                  |                 |        |       |

| DIL 9-0       |              | ed; do not use                                      |                   | L                 |                  |                 |        |       |

|               |              | ince Mask 2 reg                                     | gisters contain   | mask              |                  |                 |        |       |

|               | •            | ince Mask 1 reg                                     | •                 |                   |                  |                 |        |       |

|               | -            | ince Mask 0 reg                                     | -                 |                   |                  |                 |        |       |

| bit 7-6       |              | <ul> <li>Mask Source</li> <li>do not use</li> </ul> | e for Filter 3 bi | t                 |                  |                 |        |       |

|               |              | ince Mask 2 reg                                     | pisters contain   | mask              |                  |                 |        |       |

|               |              | ince Mask 1 reg                                     |                   |                   |                  |                 |        |       |

|               | 00 = Accepta | ince Mask 0 reg                                     | gisters contain   | mask              |                  |                 |        |       |

| bit 5-4       |              | : Mask Source                                       | e for Filter 2 bi | t                 |                  |                 |        |       |

|               |              | ed; do not use<br>ince Mask 2 reg                   | nistore contain   | mask              |                  |                 |        |       |

|               |              | ince Mask 2 reg                                     |                   |                   |                  |                 |        |       |

|               |              | nce Mask 0 reg                                      |                   |                   |                  |                 |        |       |

| bit 3-2       | F1MSK<1:0>   | : Mask Source                                       | e for Filter 1 bi | t                 |                  |                 |        |       |

|               |              | ed; do not use                                      |                   |                   |                  |                 |        |       |

|               |              | ince Mask 2 reg<br>ince Mask 1 reg                  | -                 |                   |                  |                 |        |       |

|               |              | ince Mask 0 reg                                     |                   |                   |                  |                 |        |       |

| bit 1-0       | -            | : Mask Source                                       | -                 |                   |                  |                 |        |       |

|               | 11 = Reserve | ed; do not use                                      | -                 |                   |                  |                 |        |       |

|               | 10 = Accepta | nce Mask 2 reg                                      |                   |                   |                  |                 |        |       |

|               |              | ince Mask 1 reg                                     |                   |                   |                  |                 |        |       |

|               | 00 = Accepta | nce Mask 0 reg                                      | gisters contain   | mask              |                  |                 |        |       |

| Bit Field         | Register | RTSP<br>Effect                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GWRP              | FGS      | Immediate                                                                                                       | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                   |

| IESO              | FOSCSEL  | Immediate                                                                                                       | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start-up device with user-selected oscillator source</li> </ul>                                                                                                                                                   |

| FNOSC<2:0>        | FOSCSEL  | If clock<br>switch is<br>enabled,<br>RTSP<br>effect is<br>on any<br>device<br>Reset;<br>otherwise,<br>Immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Internal Fast RC (FRC) oscillator with divide-by-16<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |

| FCKSM<1:0>        | FOSC     | Immediate                                                                                                       | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                   |

| OSCIOFNC          | FOSC     | Immediate                                                                                                       | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                                        |

| POSCMD<1:0>       | FOSC     | Immediate                                                                                                       | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                      |

| FWDTEN            | FWDT     | Immediate                                                                                                       | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled.<br/>Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register.)</li> </ul>                                                          |

| WINDIS            | FWDT     | Immediate                                                                                                       | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                      |

| PLLKEN            | FWDT     | Immediate                                                                                                       | PLL Lock Enable bit<br>1 = Clock switch to PLL source will wait until the PLL lock signal is valid<br>0 = Clock switch will not wait for the PLL lock signal                                                                                                                                                                                                                                        |

| WDTPRE            | FWDT     | Immediate                                                                                                       | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                                                                                                               |

| WDT-<br>POST<3:0> | FWDT     | Immediate                                                                                                       | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                               |

#### TABLE 23-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

### TABLE 26-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| AC CHARACTERISTICS |        |                                                                  | (unless of | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                |  |  |  |

|--------------------|--------|------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------|--|--|--|

| Param<br>No.       | Symbol | Characteris                                                      | stic       | Min                                                                                                                                                                                                                                                                                     | Typ <sup>(1)</sup> | Max | Units | Conditions                     |  |  |  |

| OS50               | Fplli  | PLL Voltage Controll<br>Oscillator (VCO) Inpl<br>Frequency Range |            | 0.8                                                                                                                                                                                                                                                                                     |                    | 8.0 | MHz   | ECPLL, HSPLL, XTPLL<br>modes   |  |  |  |

| OS51               | Fsys   | On-Chip VCO Syster<br>Frequency                                  | m          | 100                                                                                                                                                                                                                                                                                     | —                  | 200 | MHz   | —                              |  |  |  |

| OS52               | TLOCK  | PLL Start-up Time (L                                             | ock Time)  | 0.9                                                                                                                                                                                                                                                                                     | 1.5                | 3.1 | ms    | _                              |  |  |  |

| OS53               | DCLK   | CLKO Stability (Jitter                                           | -)         | -3.0                                                                                                                                                                                                                                                                                    | 0.5                | 3.0 | %     | Measured over 100 ms<br>period |  |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: These parameters are characterized by similarity but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time base or communication clocks used by peripherals use the formula:

Peripheral Clock Jitter = DCLK /  $\sqrt{(Fosc/Peripheral bit rate clock)}$

Example Only: Fosc = 80 MHz, DCLK = 3%, SPI bit rate clock, (i.e. SCK), is 5 MHz

SPI SCK Jitter = [ DCLK / \sqrt{(80 MHz/5 MHz)]} = [3%/\sqrt{16}] = [3% / 4] = 0.75%

### TABLE 26-18: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

| AC CHA       | RACTERISTICS            |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |          |                    |                                                                     |  |  |  |  |

|--------------|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|---------------------------------------------------------------------|--|--|--|--|