Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| 2 0 0 0 0 0                |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                 |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10/12b                                                                      |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc710at-i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

|          |             |        |            |        |        |        | <u> </u> |       |       |              |             |          |       |       |        |        |        |               |

|----------|-------------|--------|------------|--------|--------|--------|----------|-------|-------|--------------|-------------|----------|-------|-------|--------|--------|--------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9 | Bit 8 | Bit 7        | Bit 6       | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| YMODSRT  | 004C        |        | YS<15:1> 0 |        |        |        |          |       |       |              | xxxx        |          |       |       |        |        |        |               |

| YMODEND  | 004E        |        | YE<15:1> 1 |        |        |        |          | 1     | xxxx  |              |             |          |       |       |        |        |        |               |

| XBREV    | 0050        | BREN   |            |        |        |        |          |       |       | XB<14:0>     |             |          |       |       |        |        |        | xxxx          |

| DISICNT  | 0052        | _      | _          |        |        |        |          |       | Disab | e Interrupts | s Counter F | Register |       |       |        |        |        | xxxx          |

| BSRAM    | 0750        | _      | _          | _      | _      | _      | _        | _     | _     | _            | _           | _        | _     | _     | IW_BSR | IR_BSR | RL_BSR | 0000          |

| SSRAM    | 0752        | -      | _          | _      | _      | _      | _        | _     | _     | _            | _           | _        | _     | _     | IW_SSR | IR_SSR | RL_SSR | 0000          |

|          |             |        | - ·        |        |        |        |          |       |       |              |             |          |       |       |        |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.2 RTSP Operation

The dsPIC33FJXXXMCX06A/X08A/X10A Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory at a time, which consists of eight rows (512 instructions), and to program one row or one word at a time. Table 26-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundaries.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

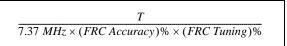

The programming time depends on the FRC accuracy (see Table 26-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the row write time, page erase time and word write cycle time parameters (see Table 26-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `bl11111, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

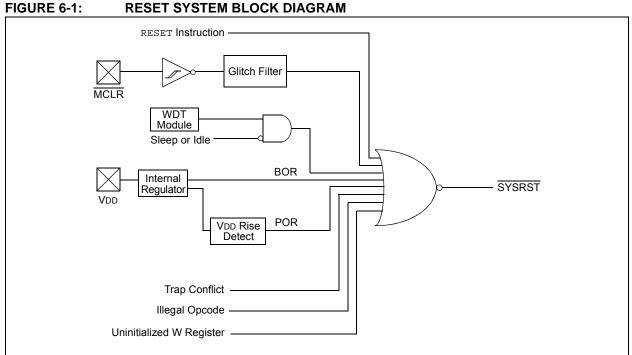

#### 6.0 RESET

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode and Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Refer to the specific peripheral or CPU Note: section of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits except for the POR bit (RCON<0>), which is set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

The status bits in the RCON register Note: should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

| R/W-0        | R/W-0                        | U-0                                    | U-0           | U-0                         | U-0               | U-0                                                                                                             | R/W-0                |

|--------------|------------------------------|----------------------------------------|---------------|-----------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|----------------------|

| TRAPR        | IOPUWR                       | —                                      | _             | —                           | —                 | —                                                                                                               | VREGS <sup>(3)</sup> |

| bit 15       |                              |                                        |               | ·                           | •                 |                                                                                                                 | bit                  |

| R/W-0        |                              | R/W-0                                  |               |                             |                   |                                                                                                                 |                      |

| EXTR         | R/W-0<br>SWR                 | SWDTEN <sup>(2)</sup>                  | R/W-0<br>WDTO | R/W-0<br>SLEEP              | R/W-0<br>IDLE     | R/W-1<br>BOR                                                                                                    | R/W-1<br>POR         |

| bit 7        | onne                         | onbien                                 |               | ULL.                        |                   | Bon                                                                                                             | bit                  |

|              |                              |                                        |               |                             |                   |                                                                                                                 |                      |

| Legend:      | L. L.'4                      |                                        | .:.           |                             |                   | (O)                                                                                                             |                      |

| R = Readab   |                              | W = Writable k                         | DIT           | -                           | mented bit, read  |                                                                                                                 |                      |

| -n = Value a | IPOR                         | '1' = Bit is set                       |               | '0' = Bit is cle            | ared              | x = Bit is unk                                                                                                  | nown                 |

| bit 15       | TRAPR: Trap                  | Reset Flag bit                         |               |                             |                   |                                                                                                                 |                      |

|              | 1 = A Trap C                 | onflict Reset has                      |               |                             |                   |                                                                                                                 |                      |

|              | -                            | onflict Reset has                      |               |                             |                   |                                                                                                                 |                      |

| bit 14       |                              | gal Opcode or                          |               |                             | •                 |                                                                                                                 |                      |

|              | 0                            | al opcode detect<br>Pointer caused     | · ·           | gal address m               | ode or uninitia   | lized W regist                                                                                                  | er used as a         |

|              |                              | l opcode or unir                       |               | Reset has not o             | ccurred           |                                                                                                                 |                      |

| bit 13-9     | Unimplemer                   | ted: Read as 'o                        | ,             |                             |                   |                                                                                                                 |                      |

| bit 8        | VREGS: Volt                  | age Regulator S                        | standby Durir | ng Sleep bit <sup>(3)</sup> |                   |                                                                                                                 |                      |

|              |                              | egulator is active<br>egulator goes in |               |                             | ер                |                                                                                                                 |                      |

| bit 7        | EXTR: Extern                 | nal Reset (MCLI                        | R) Pin bit    |                             |                   |                                                                                                                 |                      |

|              |                              | Clear (pin) Res<br>Clear (pin) Res     |               |                             |                   |                                                                                                                 |                      |

| bit 6        | SWR: Softwa                  | are Reset (Instru                      | ction) Flag b | it                          |                   |                                                                                                                 |                      |

|              |                              | instruction has                        |               |                             |                   |                                                                                                                 |                      |

|              |                              | instruction has                        |               |                             |                   |                                                                                                                 |                      |

| bit 5        |                              | oftware Enable/I                       | Jisable of W  |                             |                   |                                                                                                                 |                      |

|              | 1 = WDT is e<br>0 = WDT is d |                                        |               |                             |                   |                                                                                                                 |                      |

| bit 4        |                              | hdog Timer Tim                         | e-out Flag bi | t                           |                   |                                                                                                                 |                      |

|              |                              | e-out has occurr                       |               | -                           |                   |                                                                                                                 |                      |

|              | 0 = WDT time                 | e-out has not oc                       | curred        |                             |                   |                                                                                                                 |                      |

| bit 3        | SLEEP: Wak                   | e-up from Sleep                        | Flag bit      |                             |                   |                                                                                                                 |                      |

|              |                              | as been in Sleep                       |               |                             |                   |                                                                                                                 |                      |

|              |                              | as not been in S                       | •             |                             |                   |                                                                                                                 |                      |

| bit 2        |                              | up from Idle Fla                       | g bit         |                             |                   |                                                                                                                 |                      |

|              |                              | as in Idle mode<br>as not in Idle me   | ode           |                             |                   |                                                                                                                 |                      |

|              | ll of the Reset sta          | •                                      | set or cleare | d in software. S            | Setting one of th | nese bits in soft                                                                                               | ware does no         |

|              | ause a device Re             |                                        | (1) /         |                             |                   | a a la la servición de la composición d |                      |

| 2: If        | the FWDTEN Co                | ontiguration bit i                     | s 1 (unprog   | rammed), the V              | VUT IS alwavs (   | enabled, redard                                                                                                 | ness of the          |

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256MCX06A/X08A/X10A devices, this bit is unimplemented and reads back a programmed value.

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256MCX06A/X08A/X10A devices, this bit is unimplemented and reads back a programmed value.

| U-0          | U-0        | U-0                                  | U-0                        | U-0               | U-0              | U-0             | U-0   |

|--------------|------------|--------------------------------------|----------------------------|-------------------|------------------|-----------------|-------|

| —            | _          | —                                    | _                          | —                 | —                | —               | —     |

| bit 15       |            |                                      |                            |                   |                  |                 | bit 8 |

|              |            |                                      |                            |                   |                  |                 |       |

| U-0          | U-0        | R/W-0                                | R/W-0                      | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| —            |            |                                      |                            | TUN<              | <5:0> <b>(1)</b> |                 |       |

| bit 7        |            |                                      |                            |                   |                  |                 | bit ( |

|              |            |                                      |                            |                   |                  |                 |       |

| Legend:      |            |                                      |                            |                   |                  |                 |       |

| R = Readab   | le bit     | W = Writable                         | bit                        | •                 | nented bit, rea  | d as '0'        |       |

| -n = Value a | t POR      | '1' = Bit is set                     | :                          | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |            |                                      |                            |                   |                  |                 |       |

| bit 15-6     | -          | ented: Read as '                     |                            |                   |                  |                 |       |

| bit 5-0      | TUN<5:0>:  | FRC Oscillator                       | Funing bits <sup>(1)</sup> |                   |                  |                 |       |

|              |            | Center frequency                     |                            |                   |                  |                 |       |

|              | 011110 = 0 | Center frequency                     | + 11.25% (8.2              | 20 MHz)           |                  |                 |       |

|              | •          |                                      |                            |                   |                  |                 |       |

|              | •          |                                      |                            |                   |                  |                 |       |

|              | •          |                                      |                            |                   |                  |                 |       |

|              |            | Center frequency                     |                            |                   |                  |                 |       |

|              |            | Center frequency<br>Center frequency |                            |                   |                  |                 |       |

|              | •          |                                      | 0.07070 (7.                | 5 10 Wil 12)      |                  |                 |       |

|              | •          |                                      |                            |                   |                  |                 |       |

|              | •          |                                      |                            |                   |                  |                 |       |

|              | 100001 = 0 | Center frequency                     | – 11.625% (6               | .52 MHz)          |                  |                 |       |

|              |            | Center frequency                     |                            | · ·····-,         |                  |                 |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(2)</sup>

- **Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

- 2: This register is reset only on a Power-on Reset (POR).

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit                                                        |

|-------|----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Output Compare 4 module is disabled</li><li>0 = Output Compare 4 module is enabled</li></ul> |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul> |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul> |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                        |

|       | 1 = Output Compare 1 module is disabled                                                                  |

|       | 0 = Output Compare 1 module is enabled                                                                   |

|       |                                                                                                          |

#### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "**Pin Diagrams**" section for the available pins and their functionality.

#### 11.3 Configuring Analog Port Pins

The ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the ADC port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: |                                             |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

#### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJXXXMCX06A/X08A/X10A devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN Interrupt Enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the Weak Pull-up Enable bits (CNxPUE) for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFF00, WO | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

|      |            |                                   |

| U-0          | U-0                          | U-0                                                                                | U-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |

|--------------|------------------------------|------------------------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|

| _            | —                            | —                                                                                  | —             |                  | SEVO            | PS<3:0>         |       |  |

| bit 15       |                              |                                                                                    |               |                  |                 |                 | bit 8 |  |

|              |                              |                                                                                    |               |                  |                 |                 |       |  |

| U-0          | U-0                          | U-0                                                                                | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0 |  |

|              | <u> </u>                     | —                                                                                  | _             |                  | IUE             | OSYNC           | UDIS  |  |

| bit 7        |                              |                                                                                    |               |                  |                 |                 | bit 0 |  |

|              |                              |                                                                                    |               |                  |                 |                 |       |  |

| Legend:      |                              |                                                                                    |               |                  |                 |                 |       |  |

| R = Readab   | le bit                       | W = Writable                                                                       | bit           | U = Unimpler     | nented bit, rea | d as '0'        |       |  |

| -n = Value a | t POR                        | '1' = Bit is set                                                                   |               | '0' = Bit is cle | ared            | x = Bit is unkn | own   |  |

|              |                              |                                                                                    |               |                  |                 |                 |       |  |

| bit 15-12    | •                            | nted: Read as '                                                                    |               |                  |                 |                 |       |  |

| bit 11-8     |                              | <b>0&gt;:</b> PWM Speci                                                            | al Event Trig | ger Output Post  | scale Select b  | its             |       |  |

|              | 1111 = 1:16                  | postscale                                                                          |               |                  |                 |                 |       |  |

|              | •                            |                                                                                    |               |                  |                 |                 |       |  |

|              | •                            | antanala                                                                           |               |                  |                 |                 |       |  |

|              | 0001 = 1:2 p<br>0000 = 1:1 p |                                                                                    |               |                  |                 |                 |       |  |

| bit 7-3      | •                            | nted: Read as '                                                                    | 0'            |                  |                 |                 |       |  |

| bit 2        | -                            | ate Update Ena                                                                     |               |                  |                 |                 |       |  |

|              |                              | to the active PE                                                                   |               | are immediate    |                 |                 |       |  |

|              | 0 = Updates                  | to the active PD                                                                   | C registers a | are synchronize  | d to the PWM    | time base       |       |  |

| bit 1        | OSYNC: Ou                    | OSYNC: Output Override Synchronization bit                                         |               |                  |                 |                 |       |  |

|              |                              | 1 = Output overrides via the OVDCON register are synchronized to the PWM time base |               |                  |                 |                 |       |  |

| 1.1.0        |                              | 0 = Output overrides via the OVDCON register occur on next Tcy boundary            |               |                  |                 |                 |       |  |

| bit 0        |                              | Update Disable                                                                     |               |                  | ana diaabl'     |                 |       |  |

|              |                              | from Duty Cycle<br>from Duty Cycle                                                 |               |                  |                 |                 |       |  |

|              | o opudico                    |                                                                                    |               | Earlor regiotoro |                 |                 |       |  |

#### REGISTER 16-6: PWMxCON2: PWMx CONTROL REGISTER 2

#### 21.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

#### 21.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set, and the TXREQ bit is cleared.

#### 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

#### 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

#### 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = 111. In this mode, the data which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

#### 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

| U-0           | U-0           | R-0                                     | R-0             | R-0              | R-0              | R-0             | R-0   |

|---------------|---------------|-----------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| _             |               | ТХВО                                    | TXBP            | RXBP             | TXWAR            | RXWAR           | EWARN |

| bit 15        | I             |                                         |                 |                  |                  |                 | bit 8 |

|               |               |                                         |                 |                  |                  |                 |       |

| R/C-0         | R/C-0         | R/C-0                                   | U-0             | R/C-0            | R/C-0            | R/C-0           | R/C-0 |

| IVRIF         | WAKIF         | ERRIF                                   |                 | FIFOIF           | RBOVIF           | RBIF            | TBIF  |

| bit 7         |               |                                         |                 |                  |                  |                 | bit   |

| Legend:       |               |                                         |                 | C = Cle          | earable bit      |                 |       |

| R = Readabl   | le bit        | W = Writable                            | bit             | U = Unimple      | mented bit, read | d as '0'        |       |

| -n = Value at | t POR         | '1' = Bit is set                        | t               | '0' = Bit is cle |                  | x = Bit is unkr | nown  |

| bit 15-14     | Unimplomor    | nted: Read as '                         | 0'              |                  |                  |                 |       |

| bit 13        | -             | mitter in Error                         |                 | bit              |                  |                 |       |

| DIL 15        |               | ter is in Bus Of                        |                 | DI               |                  |                 |       |

|               | 0 = Transmitt | ter is not in Bus                       | off state       |                  |                  |                 |       |

| bit 12        |               | mitter in Error                         |                 | ssive bit        |                  |                 |       |

|               |               | ter is in Bus Pa<br>ter is not in Bus   |                 | ۵                |                  |                 |       |

| bit 11        |               | iver in Error Sta                       |                 | -                |                  |                 |       |

|               |               | is in Bus Pass                          |                 |                  |                  |                 |       |

|               |               | is not in Bus P                         |                 |                  |                  |                 |       |

| bit 10        |               | nsmitter in Erro                        |                 | ng bit           |                  |                 |       |

|               |               | ter is in Error W<br>ter is not in Erro |                 | ate              |                  |                 |       |

| bit 9         |               | ceiver in Error                         | -               |                  |                  |                 |       |

|               |               | is in Error War                         | -               |                  |                  |                 |       |

|               | 0 = Receiver  | is not in Error                         | Warning state   | •                |                  |                 |       |

| bit 8         |               | nsmitter or Reg                         |                 | •                | ı bit            |                 |       |

|               |               | ter or receiver i<br>ter or receiver i  |                 | •                |                  |                 |       |

| bit 7         |               | d Message Rec                           |                 | •                |                  |                 |       |

|               |               | request has oc                          |                 | or lug bit       |                  |                 |       |

|               | 0 = Interrupt | request has no                          | t occurred      |                  |                  |                 |       |

| bit 6         | WAKIF: Bus    | Wake-up Activ                           | ity Interrupt F | lag bit          |                  |                 |       |

|               |               | request has oc<br>request has no        |                 |                  |                  |                 |       |

| bit 5         |               |                                         |                 | ources in CilN   | TF<13:8> regist  | or)             |       |

| bit 5         |               | request has oc                          |                 |                  |                  |                 |       |

|               |               | request has no                          |                 |                  |                  |                 |       |

| bit 4         | Unimplemer    | ted: Read as                            | 0'              |                  |                  |                 |       |

| bit 3         | FIFOIF: FIFO  | Almost Full In                          | terrupt Flag b  | oit              |                  |                 |       |

|               |               | request has oc                          |                 |                  |                  |                 |       |

|               | -             | request has no                          |                 |                  |                  |                 |       |

| bit 2         |               | Buffer Overflo<br>request has oc        |                 | ag bit           |                  |                 |       |

|               |               | request has no                          |                 |                  |                  |                 |       |

| bit 1         | -             | ffer Interrupt F                        |                 |                  |                  |                 |       |

|               | 1 = Interrupt | request has oc                          | curred          |                  |                  |                 |       |

|               | -             | request has no                          |                 |                  |                  |                 |       |

| bit 0         |               | ffer Interrupt Fla                      |                 |                  |                  |                 |       |

|               |               | request has oc<br>request has no        |                 |                  |                  |                 |       |

|               | 0 – menupi    | icquesi nas no                          |                 |                  |                  |                 |       |

|               |               |                                         |                 |                  |                  |                 |       |

© 2009-2012 Microchip Technology Inc.

| R/W-0         | R/W-0        | R/W-0                             | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0             | )     |

|---------------|--------------|-----------------------------------|-----------------|-------------------|-----------------|-----------------|-------------------|-------|

| F15N          | ISK<1:0>     | F14MS                             | K<1:0>          | F13MS             | SK<1:0>         | F12MS           | K<1:0>            |       |

| bit 15        |              |                                   |                 |                   |                 |                 | b                 | oit 8 |

|               |              |                                   |                 |                   |                 |                 |                   |       |

| R/W-0         | R/W-0        | R/W-0                             | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0             | )     |

| F11M          | ISK<1:0>     | F10MS                             | K<1:0>          | F9MS              | K<1:0>          | F8MSI           | <b>&lt;</b> <1:0> |       |

| bit 7         |              |                                   |                 |                   |                 |                 | b                 | oit C |

|               |              |                                   |                 |                   |                 |                 |                   |       |

| Legend:       | - h:t        |                                   | L:1             |                   | a antod bit was | d aa '0'        |                   |       |

| R = Readabl   |              | W = Writable                      |                 | -                 | nented bit, rea |                 |                   |       |

| -n = Value at | PUR          | '1' = Bit is set                  |                 | '0' = Bit is clea | ared            | x = Bit is unkr | IOWN              |       |

| bit 15-14     | F15MSK<1.    | )>: Mask Sourc                    | e for Filter 15 | bit               |                 |                 |                   |       |

|               |              | ed: do not use                    |                 | Sit               |                 |                 |                   |       |

|               |              | ance Mask 2 re                    | gisters contair | n mask            |                 |                 |                   |       |

|               |              | ance Mask 1 re                    |                 |                   |                 |                 |                   |       |

|               | 00 = Accepta | ance Mask 0 re                    | gisters contair | n mask            |                 |                 |                   |       |

| bit 13-12     |              | D>: Mask Source                   | e for Filter 14 | bit               |                 |                 |                   |       |

|               |              | ed; do not use                    | niatoro contoir |                   |                 |                 |                   |       |

|               |              | ance Mask 2 re<br>ance Mask 1 re  |                 |                   |                 |                 |                   |       |

|               | •            | ance Mask 0 re                    | •               |                   |                 |                 |                   |       |

| bit 11-10     |              | D>: Mask Sourc                    | -               |                   |                 |                 |                   |       |

|               |              | ed; do not use                    |                 |                   |                 |                 |                   |       |

|               |              | ance Mask 2 re                    |                 |                   |                 |                 |                   |       |

|               |              | ance Mask 1 re                    | -               |                   |                 |                 |                   |       |

| h:+ 0 0       | -            | ance Mask 0 re                    | -               |                   |                 |                 |                   |       |

| bit 9-8       |              | D>: Mask Source<br>ed; do not use |                 | bit               |                 |                 |                   |       |

|               |              | ance Mask 2 re                    | gisters contair | n mask            |                 |                 |                   |       |

|               |              | ance Mask 1 re                    |                 |                   |                 |                 |                   |       |

|               | 00 = Accepta | ance Mask 0 re                    | gisters contair | n mask            |                 |                 |                   |       |

| bit 7-6       |              | >: Mask Sourc                     | e for Filter 11 | bit               |                 |                 |                   |       |

|               |              | ed; do not use                    | niatoro contair | maak              |                 |                 |                   |       |

|               |              | ance Mask 2 re<br>ance Mask 1 re  |                 |                   |                 |                 |                   |       |

|               |              | ance Mask 0 re                    |                 |                   |                 |                 |                   |       |

| bit 5-4       |              | D>: Mask Sourc                    |                 |                   |                 |                 |                   |       |

|               | 11 = Reserve | ed; do not use                    |                 |                   |                 |                 |                   |       |

|               |              | ance Mask 2 re                    | -               |                   |                 |                 |                   |       |

|               | •            | ance Mask 1 re                    | •               |                   |                 |                 |                   |       |

| hit 2 2       | -            | ance Mask 0 re                    | -               |                   |                 |                 |                   |       |

| bit 3-2       |              | Hask Source<br>ed; do not use     | for Filter 9 bi | L                 |                 |                 |                   |       |

|               |              | ance Mask 2 re                    | aisters contair | n mask            |                 |                 |                   |       |

|               |              | ance Mask 1 re                    |                 |                   |                 |                 |                   |       |

|               | 00 = Accepta | ance Mask 0 re                    | gisters contair | n mask            |                 |                 |                   |       |

| bit 1-0       | F8MSK<1:0>   | : Mask Source                     | for Filter 8 bi | t                 |                 |                 |                   |       |

|               |              | ed; do not use                    |                 |                   |                 |                 |                   |       |

|               |              | ance Mask 2 re                    | -               |                   |                 |                 |                   |       |

|               |              | ance Mask 1 re                    | -               |                   |                 |                 |                   |       |

|               |              | ance Mask 0 re                    | yisters contair | 1111051           |                 |                 |                   |       |

#### REGISTER 21-19: CiFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

#### 22.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

#### 22.5 ADC Resources

Many useful resources related to ADC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en546066                                                                                                                          |

#### 22.5.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

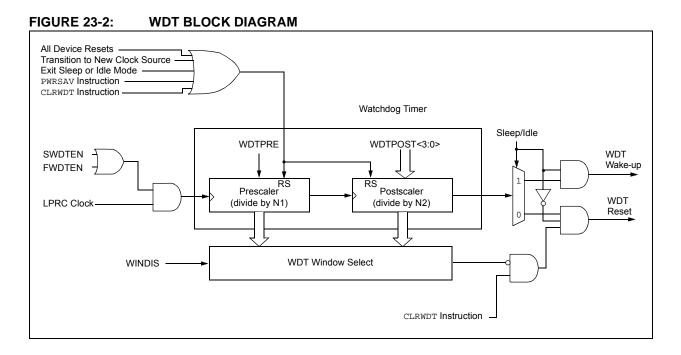

#### 23.4 Watchdog Timer (WDT)

For dsPIC33FJXXXMCX06A/X08A/X10A devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler than can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) will need to be cleared in software after the device wakes up.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

| Note: | The                                       | CLRWDT    | and | PWRSAV | instructions |  |  |  |

|-------|-------------------------------------------|-----------|-----|--------|--------------|--|--|--|

|       | clear the prescaler and postscaler counts |           |     |        |              |  |  |  |

|       | wher                                      | n execute | d.  |        |              |  |  |  |

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

#### TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm                                                                                                                                                                                                                                           | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                            |

| Wm*Wn                                                                                                                                                                                                                                           | Multiplicand and Multiplier working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                           |

| Wn                                                                                                                                                                                                                                              | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wnd                                                                                                                                                                                                                                             | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                        |

| Wns                                                                                                                                                                                                                                             | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                             |

| WREG                                                                                                                                                                                                                                            | W0 (working register used in file register instructions)                                                                                                                                                                                                 |

| Ws                                                                                                                                                                                                                                              | Source W register ∈ {Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws]}                                                                                                                                                                                               |

| Wso                                                                                                                                                                                                                                             | Source W register ∈<br>{Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb]}                                                                                                                                                                            |

| Wx         X Data Space Prefetch Address register for DSP instructions           ∈ {[W8]+ = 6, [W8]+ = 4, [W8]+ = 2, [W8], [W8]- = 6, [W8]- = 4, [W8]- = 2, [W9]+ = 6, [W9]+ = 6, [W9]+ = 2, [W9]- = 6, [W9]- = 4, [W9]- = 2, [W9 + W12], none} |                                                                                                                                                                                                                                                          |

| Wxd                                                                                                                                                                                                                                             | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

| Wy                                                                                                                                                                                                                                              | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10]+ = 6, [W10]+ = 4, [W10]+ = 2, [W10], [W10]- = 6, [W10]- = 4, [W10]- = 2,<br>[W11]+ = 6, [W11]+ = 4, [W11]+ = 2, [W11], [W11]- = 6, [W11]- = 4, [W11]- = 2,<br>[W11 + W12], none} |

| Wyd                                                                                                                                                                                                                                             | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

| Base<br>Instr<br># | tr Assembly Assembly Syntax Description |        | Description    | # of<br>Words                                     | # of<br>Cycles | Status Flags<br>Affected |                         |

|--------------------|-----------------------------------------|--------|----------------|---------------------------------------------------|----------------|--------------------------|-------------------------|

| 51 MUL             |                                         | MUL.SS | Wb,Ws,Wnd      | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1              | 1                        | None                    |

|                    |                                         | MUL.SU | Wb,Ws,Wnd      | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1              | 1                        | None                    |

|                    |                                         | MUL.US | Wb,Ws,Wnd      | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1              | 1                        | None                    |

|                    |                                         | MUL.UU | Wb,Ws,Wnd      | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1              | 1                        | None                    |

|                    |                                         | MUL.SU | Wb,#lit5,Wnd   | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)      | 1              | 1                        | None                    |

|                    |                                         | MUL.UU | Wb,#lit5,Wnd   | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1              | 1                        | None                    |

|                    |                                         | MUL    | f              | W3:W2 = f * WREG                                  | 1              | 1                        | None                    |

| 52                 | NEG                                     | NEG    | Acc            | Negate Accumulator                                | 1              | 1                        | OA,OB,OAB,<br>SA,SB,SAB |

|                    |                                         | NEG    | f              | $f = \overline{f} + 1$                            | 1              | 1                        | C,DC,N,OV,Z             |

|                    |                                         | NEG    | f,WREG         | WREG = $\overline{f}$ + 1                         | 1              | 1                        | C,DC,N,OV,Z             |

|                    |                                         | NEG    | Ws,Wd          | Wd = Ws + 1                                       | 1              | 1                        | C,DC,N,OV,Z             |

| 53                 | NOP                                     | NOP    |                | No Operation                                      | 1              | 1                        | None                    |

|                    |                                         | NOPR   |                | No Operation                                      | 1              | 1                        | None                    |

| 54                 | POP                                     | POP    | f              | Pop f from Top-of-Stack (TOS)                     | 1              | 1                        | None                    |

|                    |                                         | POP    | Wdo            | Pop from Top-of-Stack (TOS) to Wdo                | 1              | 1                        | None                    |

|                    |                                         | POP.D  | Wnd            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1              | 2                        | None                    |

|                    |                                         | POP.S  |                | Pop Shadow Registers                              | 1              | 1                        | All                     |

| 55                 | PUSH                                    | PUSH   | f              | Push f to Top-of-Stack (TOS)                      | 1              | 1                        | None                    |

|                    |                                         | PUSH   | Wso            | Push Wso to Top-of-Stack (TOS)                    | 1              | 1                        | None                    |

|                    |                                         | PUSH.D | Wns            | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)        | 1              | 2                        | None                    |

|                    |                                         | PUSH.S |                | Push Shadow Registers                             | 1              | 1                        | None                    |