Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc510a-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

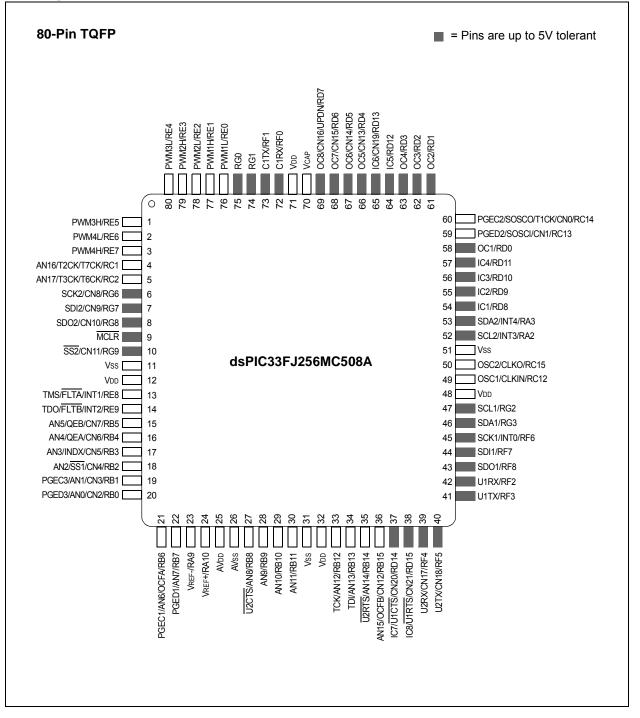

#### **Pin Diagrams (Continued)**

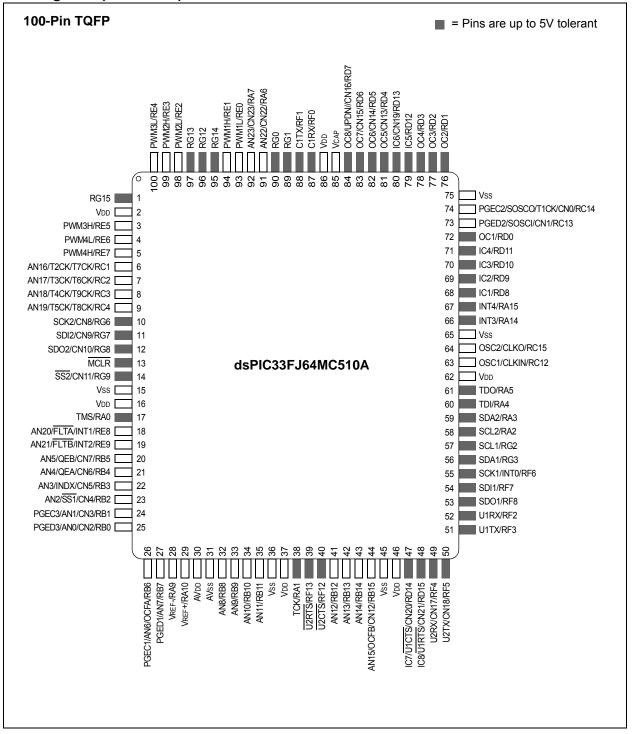

#### **Pin Diagrams (Continued)**

NOTES:

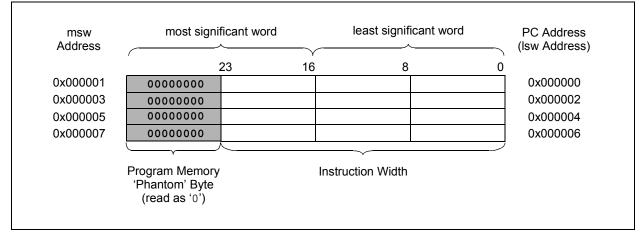

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXMCX06A/X08A/X10A devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXMCX06A/X08A/X10A devices also have two interrupt vector tables located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

## TABLE 4-10: QEI REGISTER MAP

| SFR<br>Name    | Addr | Bit 15 | Bit 14                 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8    | Bit 7    | Bit 6  | Bit 5     | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0    |      | Reset State | e      |

|----------------|------|--------|------------------------|---------|--------|--------|--------|---------|----------|----------|--------|-----------|-------|--------|--------|-------|----------|------|-------------|--------|

| <b>QEI1CON</b> | 01E0 | CNTERR | —                      | QEISIDL | INDX   | UPDN   | Q      | EIM<2:0 | )>       | SWPAB    | PCDOUT | TQGATE    | TQCKP | S<1:0> | POSRES | TQCS  | UPDN_SRC | 0000 | 0000 000    | 0 0000 |

| DFLT1CON       | 01E2 | _      | —                      | _       | _      | _      | IMV<   | :1:0>   | CEID     | QEOUT    |        | QECK<2:0> |       |        | _      |       | _        | 0000 | 0000 000    | 0 0000 |

| POS1CNT        | 01E4 |        | Position Counter<15:0> |         |        |        |        | 0000    | 0000 000 | 0 0000   |        |           |       |        |        |       |          |      |             |        |

| MAX1CNT        | 01E6 |        | Maximum Count<15:0>    |         |        |        |        |         | 1111     | 1111 111 | 1 1111 |           |       |        |        |       |          |      |             |        |

Legend: u = uninitialized bit, - = unimplemented, read as '0'

#### TABLE 4-11: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                        | Bit 7 | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|------------------------------|-------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       |        | _       |        |        | _      |        | I2C1 Receive Register        |       |       |            |             | 0000         |       |       |       |               |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | _                            |       |       |            | I2C1 Trans  | mit Register |       |       |       | OOFF          |

| I2C1BRG  | 0204        | —       | _      | _       | -      |        | —      | —      | Baud Rate Generator Register |       |       |            | 0000        |              |       |       |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                         | GCEN  | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                        | IWCOL | I2COV | D_A        | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |                              |       |       | I2C1 Addre | ss Register |              |       |       |       | 0000          |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      | —      |        |                              |       | 120   | 1 Address  | Mask Regis  | ster         |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                        | Bit 7                   | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|------------------------------|-------------------------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        | —       | -      | —       | —      | —      | —      | —      | —                            | - I2C2 Receive Register |       |            |             |              | 0000  |       |       |               |

| I2C2TRN  | 0212        | _       | _      | _       | _      | _      | _      | _      | _                            |                         |       |            | I2C2 Transı | nit Register |       |       |       | OOFF          |

| I2C2BRG  | 0214        | _       | _      | _       | _      | _      | _      | _      | Baud Rate Generator Register |                         |       |            | 0000        |              |       |       |       |               |

| I2C2CON  | 0216        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                         | GCEN                    | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                        | IWCOL                   | I2COV | D_A        | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        | _       | _      | _       | _      | _      | _      |        |                              |                         |       | I2C2 Addre | ss Register |              |       |       |       | 0000          |

| I2C2MSK  | 021C        | —       |        |         | —      | -      |        |        |                              |                         | 120   | 2 Address  | Mask Regis  | ter          |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

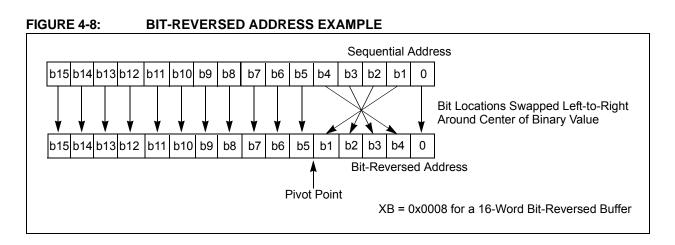

## TABLE 4-37: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

## REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IE:</b> Input Capture Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled  |

| bit 0 | INTOIE: External Interrupt 0 Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                     |

#### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 (CONTINUED)

| bit 1 | SI2C2IE: I2C2 Slave Events Interrupt Enable bit |

|-------|-------------------------------------------------|

|       | 1 = Interrupt request enabled                   |

|       | 0 = Interrupt request not enabled               |

|       |                                                 |

- bit 0 T7IE: Timer7 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0           | R/W-1                                                                   | R/W-0                                   | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------|-----------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| _             |                                                                         | C1IP<2:0>                               |                |                  |                 | C1RXIP<2:0>     |       |  |  |  |  |  |  |

| bit 15        |                                                                         |                                         |                |                  |                 |                 | bit   |  |  |  |  |  |  |

| U-0           | R/W-1                                                                   | R/W-0                                   | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _             |                                                                         | SPI2IP<2:0>                             |                | _                |                 | SPI2EIP<2:0>    |       |  |  |  |  |  |  |

| bit 7         |                                                                         |                                         |                |                  |                 |                 | bit   |  |  |  |  |  |  |

| Legend:       |                                                                         |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

| R = Readabl   | le bit                                                                  | W = Writable k                          | bit            | U = Unimplei     | mented bit, rea | id as '0'       |       |  |  |  |  |  |  |

| -n = Value at | t POR                                                                   | '1' = Bit is set                        |                | '0' = Bit is cle | ared            | x = Bit is unkn | own   |  |  |  |  |  |  |

| bit 15        | Unimpleme                                                               | ented: Read as '0                       | ,              |                  |                 |                 |       |  |  |  |  |  |  |

| bit 14-12     | C1IP<2:0>:                                                              | ECAN1 Event In                          | terrupt Priori | ity bits         |                 |                 |       |  |  |  |  |  |  |

|               | <pre>111 = Interrupt is priority 7 (highest priority interrupt) .</pre> |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                         | upt is priority 1<br>upt source is disa | abled          |                  |                 |                 |       |  |  |  |  |  |  |

| bit 11        |                                                                         | ented: Read as '0                       |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 10-8      | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits           |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)              |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled     |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 7         |                                                                         | ented: Read as '0                       |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 6-4       | -                                                                       | >: SPI2 Event Int                       |                | y bits           |                 |                 |       |  |  |  |  |  |  |

|               | 111 = Interr                                                            | upt is priority 7 (h                    | ighest priori  | ty interrupt)    |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 001 = Interr                                                            | upt is priority 1                       |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                         | upt source is disa                      |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 3         | -                                                                       | ented: Read as '0                       |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 2-0       |                                                                         | 0>: SPI2 Error In                       | -              | -                |                 |                 |       |  |  |  |  |  |  |

|               | 111 = Interr                                                            | upt is priority 7 (h                    | lighest priori | ty interrupt)    |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                       |                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                         | upt is priority 1<br>upt source is disa | abled          |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                         |                                         | 11151          |                  |                 |                 |       |  |  |  |  |  |  |

### REGISTER 7-23: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

### 8.1 DMAC Registers

Each DMAC Channel x (x = 0, 1, 2, 3, 4, 5, 6 or 7) contains the following registers:

- A 16-Bit DMA Channel Control register (DMAxCON)

- A 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- A 16-Bit DMA RAM Primary Start Address Offset register (DMAxSTA)

- A 16-Bit DMA RAM Secondary Start Address Offset register (DMAxSTB)

- A 16-Bit DMA Peripheral Address register (DMAxPAD)

- A 10-Bit DMA Transfer Count register (DMAxCNT)

An additional pair of status registers, DMACS0 and DMACS1, are common to all DMAC channels.

#### REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-------|-----|-----|-------|

| CHEN   | SIZE  | DIR   | HALF  | NULLW | —   | —   | —     |

| bit 15 |       |       |       |       |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0  |

|-------|-----|-------|--------|-----|-----|-------|--------|

| —     | —   | AMOD  | E<1:0> | —   | —   | MODE  | =<1:0> |

| bit 7 |     |       |        |     |     |       | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | CHEN: Channel Enable bit                                                                                                                                      |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Channel enabled                                                                                                                                           |

|          | 0 = Channel disabled                                                                                                                                          |

| bit 14   | SIZE: Data Transfer Size bit                                                                                                                                  |

|          | 1 = Byte                                                                                                                                                      |

|          | 0 = Word                                                                                                                                                      |

| bit 13   | <b>DIR:</b> Transfer Direction bit (source/destination bus select)                                                                                            |

|          | 1 = Read from DMA RAM address; write to peripheral address                                                                                                    |

|          | 0 = Read from peripheral address; write to DMA RAM address                                                                                                    |

| bit 12   | HALF: Early Block Transfer Complete Interrupt Select bit                                                                                                      |

|          | 1 = Initiate block transfer complete interrupt when half of the data has been moved                                                                           |

|          | 0 = Initiate block transfer complete interrupt when all of the data has been moved                                                                            |

| bit 11   | NULLW: Null Data Peripheral Write Mode Select bit                                                                                                             |

|          | 1 = Null data write to peripheral in addition to DMA RAM write (DIR bit must also be clear)                                                                   |

|          | 0 = Normal operation                                                                                                                                          |

| bit 10-6 | Unimplemented: Read as '0'                                                                                                                                    |

| bit 5-4  | AMODE<1:0>: DMA Channel Operating Mode Select bits                                                                                                            |

|          | 11 = Reserved                                                                                                                                                 |

|          | 10 = Peripheral Indirect Addressing mode                                                                                                                      |

|          | 01 = Register Indirect without Post-Increment mode<br>00 = Register Indirect with Post-Increment mode                                                         |

| bit 3-2  |                                                                                                                                                               |

|          | Unimplemented: Read as '0'                                                                                                                                    |

| bit 1-0  | MODE<1:0>: DMA Channel Operating Mode Select bits                                                                                                             |

|          | <ul> <li>11 = One-Shot, Ping-Pong modes enabled (one block transfer from/to each DMA RAM buffer)</li> <li>10 = Continuous, Ping-Pong modes enabled</li> </ul> |

|          | 01 = One-Shot, Ping-Pong modes disabled                                                                                                                       |

|          | 00 = Continuous, Ping-Pong modes disabled                                                                                                                     |

|          |                                                                                                                                                               |

## 16.0 MOTOR CONTROL PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Motor Control PWM" (DS70187) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This module simplifies the task of generating multiple, synchronized Pulse-Width Modulated (PWM) outputs. In particular, the following power and motion control applications are supported by the PWM module:

- · 3-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

The PWM module has the following features:

- Eight PWM I/O pins with four duty cycle generators

- · Up to 16-bit resolution

- 'On-the-fly' PWM frequency changes

- Edge and Center-Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation

- Special Event' comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

- Duty cycle updates are configurable to be immediate or synchronized to the PWM time base

This module contains four duty cycle generators, numbered 1 through 4. The module has eight PWM output pins, numbered PWM1H/PWM1L through PWM4H/PWM4L. The eight I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

The PWM module allows several modes of operation which are beneficial for specific power control applications.

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                               | R/W-0                                             | R/W-0           | R/W-0                | R/W-0            | R/W-0              | R/W-0  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|----------------------|------------------|--------------------|--------|--|

| FAOV4H        | FAOV4L                                                                                                                                                                                                                                                                                                              | FAOV3H                                            | FAOV3L          | FAOV2H               | FAOV2L           | FAOV1H             | FAOV1L |  |

| bit 15        | ·                                                                                                                                                                                                                                                                                                                   |                                                   | •               |                      |                  | •                  | bit 8  |  |

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                 | U-0                                               | U-0             | R/W-0                | R/W-0            | R/W-0              | R/W-0  |  |

| FLTAM         | _                                                                                                                                                                                                                                                                                                                   | _                                                 | _               | FAEN4                | FAEN3            | FAEN2              | FAEN1  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                     |                                                   |                 |                      |                  |                    | bit (  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                     |                                                   |                 |                      |                  |                    |        |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                               | W = Writable                                      | bit             | U = Unimplen         | nented bit, read | d as '0'           |        |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                                  |                 | '0' = Bit is cleared |                  | x = Bit is unknown |        |  |

| bit 7         | <ul> <li>0 = The PWM output pin is driven inactive on an external Fault input event</li> <li>FLTAM: Fault A Mode bit</li> <li>1 = The Fault A input pin functions in the Cycle-by-Cycle mode</li> <li>0 = The Fault A input pin latches all control pins to the states programmed in FLTACON&lt;15:8&gt;</li> </ul> |                                                   |                 |                      |                  |                    |        |  |

| bit 6-4       | -                                                                                                                                                                                                                                                                                                                   | ited: Read as '                                   |                 |                      |                  |                    |        |  |

| bit 3         | FAEN4: Fault Input A Enable bit<br>1 = PWM4H/PWM4L pin pair is controlled by Fault Input A<br>0 = PWM4H/PWM4L pin pair is not controlled by Fault Input A                                                                                                                                                           |                                                   |                 |                      |                  |                    |        |  |

| bit 2         | FAEN3: Fault Input A Enable bit<br>1 = PWM3H/PWM3L pin pair is controlled by Fault Input A<br>0 = PWM3H/PWM3L pin pair is not controlled by Fault Input A                                                                                                                                                           |                                                   |                 |                      |                  |                    |        |  |

| bit 1         | <b>FAEN2:</b> Fault Input A Enable bit<br>1 = PWM2H/PWM2L pin pair is controlled by Fault Input A<br>0 = PWM2H/PWM2L pin pair is not controlled by Fault Input A                                                                                                                                                    |                                                   |                 |                      |                  |                    |        |  |

| bit 0         | 1 = PWM1H/                                                                                                                                                                                                                                                                                                          | t Input A Enabl<br>PWM1L pin pai<br>PWM1L pin pai | r is controlled |                      |                  |                    |        |  |

#### REGISTER 16-9: PxFLTACON: PWMx FAULT A CONTROL REGISTER

#### REGISTER 17-2: DFLTxCON: DIGITAL FILTER x CONTROL REGISTER

|                | U-0                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                                                                                                     | U-0                                                                                                    | R/W-0                                                                 | R/W-0        | R/W-0 |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-------|--|--|--|

| —              | —                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                       | —                                                                                                      | IMV<                                                                  | 2:0>         | CEID  |  |  |  |

| bit 15         | ·                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              | bit 8 |  |  |  |

|                |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

| R/W-0          |                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                         | U-0                                                                                                    | U-0                                                                   | U-0          | U-0   |  |  |  |

| QEOUT          |                                                                                                                                                                                                                                                                                                     | QECK<2:0>                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         | _                                                                                                      | —                                                                     | _            |       |  |  |  |

| bit 7          |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              | bit   |  |  |  |

| Legend:        |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

| R = Readab     | le bit                                                                                                                                                                                                                                                                                              | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                            | oit                                                                                                                                                     | U = Unimple                                                                                            | mented bit, read                                                      | as '0'       |       |  |  |  |

| -n = Value a   | t POR                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         | '0' = Bit is cle                                                                                       | eared x = Bit is unkn                                                 |              | iown  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

| bit 15-11      | -                                                                                                                                                                                                                                                                                                   | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

| bit 10-9       | IMV<1:0>: Inc                                                                                                                                                                                                                                                                                       | IMV<1:0>: Index Match Value bits                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

|                |                                                                                                                                                                                                                                                                                                     | These bits allow the user to specify the state of the QEAx and QEBx input pins during an index puls                                                                                                                                                                                                                                                                                                       |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

|                | when the POSxCNT register is to be reset.                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

|                | In 4X Quadrature Count Mode:                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

|                | IMV1 = Required state of Phase B input signal for match on index pulse<br>IMV0 = Required state of Phase A input signal for match on index pulse                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

|                | T M T O = D O M H                                                                                                                                                                                                                                                                                   | rad atata of Dh                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |              |       |  |  |  |

|                | -                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           | ase A input s                                                                                                                                           |                                                                                                        |                                                                       |              |       |  |  |  |

|                | In 2X Quadra                                                                                                                                                                                                                                                                                        | ture Count Mod                                                                                                                                                                                                                                                                                                                                                                                            | ase A input s<br><u>le:</u>                                                                                                                             | signal for match                                                                                       | n on index pulse                                                      |              |       |  |  |  |

|                | In 2X Quadra<br>IMV1 = Selec                                                                                                                                                                                                                                                                        | ture Count Moc<br>ts phase input :                                                                                                                                                                                                                                                                                                                                                                        | ase A input s<br><u>le:</u><br>signal for ind                                                                                                           | signal for match                                                                                       |                                                                       | _ = Phase B) |       |  |  |  |

| bit 8          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requi                                                                                                                                                                                                                                                        | ture Count Moc<br>ts phase input :                                                                                                                                                                                                                                                                                                                                                                        | ase A input s<br>l <u>e:</u><br>signal for ind<br>selected Ph                                                                                           | signal for match                                                                                       | n on index pulse<br>(0 = Phase A, 1                                   | _ = Phase B) |       |  |  |  |

| bit 8          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requi<br>CEID: Count                                                                                                                                                                                                                                         | ture Count Moc<br>ts phase input s<br>red state of the                                                                                                                                                                                                                                                                                                                                                    | ase A input s<br>l <u>e:</u><br>signal for ind<br>selected Ph<br>Disable bit                                                                            | signal for match<br>lex state match<br>nase input signa                                                | n on index pulse<br>(0 = Phase A, 1                                   | _ = Phase B) |       |  |  |  |

| bit 8          | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts                                                                                                                                                                                                                       | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I                                                                                                                                                                                                                                                                                                                               | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa                                                                         | signal for match<br>lex state match<br>nase input signa<br>abled                                       | n on index pulse<br>(0 = Phase A, 1                                   | _ = Phase B) |       |  |  |  |

| bit 8<br>bit 7 | In 2X Quadra<br>IMV1 = Selec<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts                                                                                                                                                                                                     | ture Count Mod<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e                                                                                                                                                                                                                                                                                                             | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena                                                        | signal for match<br>lex state match<br>nase input signa<br>abled<br>abled                              | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir             | _ = Phase B) |       |  |  |  |

|                | In 2X Quadrat<br>IMV1 = Selec<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA                                                                                                                                                                                      | ture Count Mod<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e                                                                                                                                                                                                                                                                                           | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F                                       | signal for match<br>lex state match<br>nase input signa<br>abled<br>abled                              | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir             | _ = Phase B) |       |  |  |  |

|                | In 2X Quadrat<br>IMV1 = Selec<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte                                                                                                                                                                 | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx                                                                                                                                                                                                                                                                           | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led                                | signal for match<br>lex state match<br>nase input signa<br>abled<br>abled<br>Filter Output En          | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir             | _ = Phase B) |       |  |  |  |

|                | In 2X Quadrat<br>IMV1 = Selec<br>IMV0 = Requi<br><b>CEID:</b> Count<br>1 = Interrupts<br>0 = Interrupts<br><b>QEOUT:</b> QEA<br>1 = Digital filte<br>0 = Digital filte                                                                                                                              | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab                                                                                                                                                                                                                                                        | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Selec<br>IMV0 = Requi<br><b>CEID:</b> Count<br>1 = Interrupts<br>0 = Interrupts<br><b>QEOUT:</b> QEA<br>1 = Digital filte<br>0 = Digital filte                                                                                                                              | ture Count Mod<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN                                                                                                                                                                                                                    | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Selec<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:                                                                                                                              | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide                                                                                                                                                                                                                      | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Select<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 c                                                                                                            | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide                                                                                                                                                                                                    | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Select<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 c<br>101 = 1:128 c<br>101 = 1:32 ch                                                                          | ture Count Moc<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>clock divide<br>pock divide                                                                                                                                                                     | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Select<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 c<br>101 = 1:128 c<br>101 = 1:32 cl<br>011 = 1:16 cl                                                         | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>clock divide<br>ock divide<br>ock divide                                                                                                                                                        | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Select<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 c<br>110 = 1:128 c<br>101 = 1:64 cle<br>011 = 1:16 cle<br>010 = 1:4 clo                                      | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>bock divide<br>bock divide<br>bock divide<br>bock divide<br>bock divide                                                                                                                         | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Select<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 c<br>101 = 1:128 c<br>101 = 1:32 clo<br>011 = 1:16 clo<br>010 = 1:4 clo<br>001 = 1:2 clo                     | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>bock divide | ase A input s<br>signal for ind<br>selected Pr<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>oled (normal                | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

| bit 7          | In 2X Quadrat<br>IMV1 = Select<br>IMV0 = Requi<br>CEID: Count<br>1 = Interrupts<br>0 = Interrupts<br>QEOUT: QEA<br>1 = Digital filte<br>0 = Digital filte<br>0 = Digital filte<br>QECK<2:0>:<br>111 = 1:256 ct<br>100 = 1:32 ct<br>011 = 1:16 ct<br>010 = 1:4 cto<br>001 = 1:2 cto<br>000 = 1:1 cto | ture Count Moo<br>ts phase input s<br>red state of the<br>Error Interrupt I<br>due to count e<br>due to count e<br>x/QEBx/INDXx<br>er outputs enab<br>er outputs disat<br>QEAx/QEBx/IN<br>clock divide<br>bock divide | ase A input s<br>signal for ind<br>selected Ph<br>Disable bit<br>rrors are disa<br>rrors are ena<br>Pin Digital F<br>led<br>Ded (normal<br>IDXx Digital | signal for match<br>lex state match<br>hase input signa<br>abled<br>Filter Output En<br>pin operation) | n on index pulse<br>(0 = Phase A, 1<br>al for match on ir<br>able bit | _ = Phase B) |       |  |  |  |

## 20.3 UART Control Registers

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0                                                                                                                                         | R/W-0                                                                                                    | R/W-0               | R/W-0                | U-0                                   | R/W-0            | R/W-0               |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------|----------------------|---------------------------------------|------------------|---------------------|--|--|