Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                 |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 256KB (256K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10/12b                                                                      |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc510at-i-pf |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.6.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated – but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly. For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

### 3.6.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts and between bit positions 0 to 16 for left shifts.

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|-------|------------|-------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        |        |        |        |        |        |        |       | Input 1 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | _      | _      | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        |        |        |        |        |        |        |       | Input 2 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC2CON   | 0146        | -      | _      | ICSIDL | _      | _      | _      |       | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |        | •      |        |        |        |        | •     | Input 3 Ca | pture Regis | er    |       | •     |       |       |          |       | xxxx          |

| IC3CON   | 014A        | _      | —      | ICSIDL | _      | _      |        | _     | —          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |        |        |        |        |        |        |       | Input 4 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC4CON   | 014E        | _      | _      | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |        |        |        |        |        |        |       | Input 5 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        | _      | _      | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |        |        |        |        |        |        |       | Input 6 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        | _      | _      | ICSIDL | _      | _      |        | —     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |        |        |        |        |        |        |       | Input 7 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        | _      |        | ICSIDL | —      |        | _      | _     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |        |        |        |        |        |        |       | Input 8 Ca | pture Regis | er    |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | _      |        | ICSIDL | _      | _      |        | _     | _          | ICTMR       | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

### TABLE 4-7: INPUT CAPTURE REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

### TABLE 4-36: FUNDAMENTAL ADDRESSING MODES SUPPORTED

### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing     |

|-------|----------------------------------------------|

|       | mode specified in the instruction can differ |

|       | for the source and destination EA.           |

|       | However, the 4-bit Wb (register offset)      |

|       | field is shared between both source and      |

|       | destination (but typically only used by      |

|       | one).                                        |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the Data Pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 will always be directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9, and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.3.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

### 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXMCX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and

three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data by blocks (or 'rows') of 64 instructions (192 bytes) at a time or by single program memory word; the user can erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

### 5.1 Table Instructions and Flash Programming

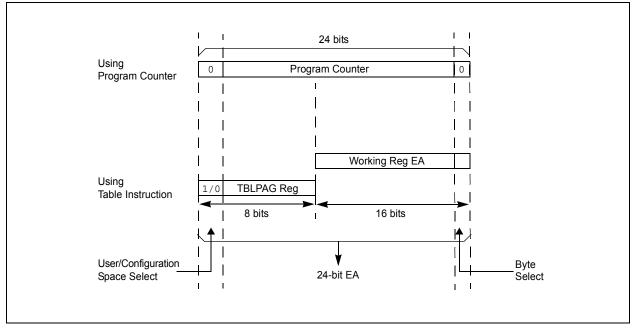

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 22. "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., the UART Receive register and Input Capture 1 buffer) and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers, and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJXXXMCX06A/X08A/X10A peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

### TABLE 8-1: PERIPHERALS WITH DMA SUPPORT

| Peripheral         | IRQ Number |

|--------------------|------------|

| INTO               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels. Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data, either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- · Word or byte-sized data transfers.

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral.

- Indirect Addressing of DMA RAM locations with or without automatic post-increment.

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral.

- One-Shot Block Transfers Terminating DMA transfer after one block transfer.

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete.

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately.

- · Automatic or manual initiation of block transfers.

- Each channel can select from 20 possible sources of data sources or destinations.

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

### REGISTER 17-1: QEIXCON: QEIX CONTROL REGISTER (CONTINUED)

| bit 4-3 | <b>TQCKPS&lt;1:0&gt;:</b> Timer Input Clock Prescale Select bits<br>11 = 1:256 prescale value<br>10 = 1:64 prescale value<br>01 = 1:8 prescale value<br>00 = 1:1 prescale value<br>(Prescaler utilized for 16-Bit Timer mode only.)    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2   | POSRES: Position Counter Reset Enable bit<br>1 = Index pulse resets position counter<br>0 = Index pulse does not reset position counter<br>(Bit only applies when QEIM<2:0> = 100 or 110.)                                             |

| bit 1   | <b>TQCS:</b> Timer Clock Source Select bit<br>1 = External clock from QEA pin (on the rising edge)<br>0 = Internal clock (Tcy)                                                                                                         |

| bit 0   | <pre>UPDN_SRC: Position Counter Direction Selection Control bit<sup>(1)</sup> 1 = QEB pin state defines position counter direction 0 = Control/status bit, UPDN (QEICON&lt;11&gt;), defines Position Counter (POSxCNT) direction</pre> |

Note 1: When configured for QEI mode, the control bit is a 'don't care'.

| U-0                 | U-0                                                                                                            | U-0                                   | R/W-0           | R/W-0              | R/W-0            | R/W-0            | R/W-0              |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|--------------------|------------------|------------------|--------------------|--|--|--|--|

|                     | _                                                                                                              | —                                     | DISSCK          | DISSDO             | MODE16           | SMP              | CKE <sup>(1)</sup> |  |  |  |  |

| bit 15              | l                                                                                                              |                                       |                 |                    |                  | 1                | bit                |  |  |  |  |

|                     |                                                                                                                |                                       |                 |                    |                  |                  |                    |  |  |  |  |

| R/W-0               | R/W-0                                                                                                          | R/W-0                                 | R/W-0           | R/W-0              | R/W-0            | R/W-0            | R/W-0              |  |  |  |  |

| SSEN <sup>(3)</sup> | СКР                                                                                                            | MSTEN                                 |                 | SPRE<2:0>(2        | )                | PPRE-            | <1:0> <b>(2)</b>   |  |  |  |  |

| bit 7               |                                                                                                                |                                       |                 |                    |                  |                  | bit                |  |  |  |  |

|                     |                                                                                                                |                                       |                 |                    |                  |                  |                    |  |  |  |  |

| Legend:             |                                                                                                                |                                       |                 |                    |                  |                  |                    |  |  |  |  |

| R = Readable        |                                                                                                                | W = Writable                          |                 | -                  | nented bit, read |                  |                    |  |  |  |  |

| -n = Value at F     | POR                                                                                                            | '1' = Bit is set                      |                 | '0' = Bit is clea  | ared             | x = Bit is unkr  | nown               |  |  |  |  |

|                     |                                                                                                                |                                       | o.1             |                    |                  |                  |                    |  |  |  |  |

| bit 15-13           | -                                                                                                              | nted: Read as '                       |                 |                    |                  |                  |                    |  |  |  |  |

| bit 12              |                                                                                                                | able SCKx Pin                         | ·               | • •                |                  |                  |                    |  |  |  |  |

|                     |                                                                                                                | SPI clock is disa<br>SPI clock is ena |                 |                    |                  |                  |                    |  |  |  |  |

| bit 11              | DISSDO: Dis                                                                                                    | sable SDOx Pin                        | bit             |                    |                  |                  |                    |  |  |  |  |

|                     | 1 = SDOx pir                                                                                                   | n is not used by                      | module; pin f   | functions as I/O   |                  |                  |                    |  |  |  |  |

|                     | 0 = SDOx pir                                                                                                   | n is controlled b                     | y the module    |                    |                  |                  |                    |  |  |  |  |

| bit 10              | MODE16: Word/Byte Communication Select bit                                                                     |                                       |                 |                    |                  |                  |                    |  |  |  |  |

|                     |                                                                                                                | nication is word-                     | • • •           |                    |                  |                  |                    |  |  |  |  |

| bit 9               |                                                                                                                | ication is byte-                      |                 |                    |                  |                  |                    |  |  |  |  |

| DIL 9               | Master mode                                                                                                    | Data Input Samp                       | Die Phase bit   |                    |                  |                  |                    |  |  |  |  |

|                     | 1 = Input dat                                                                                                  | a sampled at e                        |                 |                    |                  |                  |                    |  |  |  |  |

|                     | -                                                                                                              | a sampled at m                        | iddle of data o | output time        |                  |                  |                    |  |  |  |  |

|                     | SMP must be                                                                                                    | e cleared when                        | SPIx is used    | in Slave mode      |                  |                  |                    |  |  |  |  |

| bit 8               |                                                                                                                | lock Edge Sele                        |                 |                    |                  |                  |                    |  |  |  |  |

|                     |                                                                                                                | •                                     |                 | on from active o   | lock state to Id | le clock state ( | see bit 6)         |  |  |  |  |

|                     |                                                                                                                |                                       |                 | on from Idle clo   |                  |                  |                    |  |  |  |  |

| bit 7               |                                                                                                                | e Select Enable                       |                 | de) <sup>(3)</sup> |                  |                  |                    |  |  |  |  |

|                     |                                                                                                                | used for Slave r                      |                 |                    |                  |                  |                    |  |  |  |  |

| L:1 0               | 0 = SSx pin not used by module. Pin controlled by port function.                                               |                                       |                 |                    |                  |                  |                    |  |  |  |  |

| bit 6               | <b>CKP:</b> Clock Polarity Select bit<br>1 = Idle state for clock is a high level; active state is a low level |                                       |                 |                    |                  |                  |                    |  |  |  |  |

|                     |                                                                                                                |                                       | •               | e state is a high  |                  |                  |                    |  |  |  |  |

| bit 5               |                                                                                                                | ster Mode Enab                        |                 | C                  |                  |                  |                    |  |  |  |  |

|                     | 1 = Master m                                                                                                   | ode                                   |                 |                    |                  |                  |                    |  |  |  |  |

|                     |                                                                                                                | loue                                  |                 |                    |                  |                  |                    |  |  |  |  |

- 2: Do not set both the primary and secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

| R/W-0                        | R/W-0                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                         | U-0                                                                                                                                                                       | U-0                          | U-0              | U-0                | U-0   |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|--------------------|-------|

| FRMEN                        | SPIFSD                                                                                                                                                                                   | FRMPOL                                                                                                                                                                                                                        |                                                                                                                                                                           | _                            |                  |                    | _     |

| bit 15                       |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    | bit 8 |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| U-0                          | U-0                                                                                                                                                                                      | U-0                                                                                                                                                                                                                           | U-0                                                                                                                                                                       | U-0                          | U-0              | R/W-0              | U-0   |

|                              | —                                                                                                                                                                                        | —                                                                                                                                                                                                                             |                                                                                                                                                                           | —                            |                  | FRMDLY             | —     |

| bit 7                        |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    | bit C |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| Legend:                      |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| R = Readable                 | e bit                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                                  | bit                                                                                                                                                                       | U = Unimplen                 | nented bit, read | l as '0'           |       |

| -n = Value at I              | POR                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                              |                                                                                                                                                                           | '0' = Bit is clea            | ared             | x = Bit is unknown |       |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| bit 15                       |                                                                                                                                                                                          | ned SPIx Supp                                                                                                                                                                                                                 |                                                                                                                                                                           |                              |                  |                    |       |

| bit 15                       | 1 = Framed S                                                                                                                                                                             | Plx support en                                                                                                                                                                                                                | abled (SSx p                                                                                                                                                              | in used as fram              | e Sync pulse ir  | nput/output)       |       |

|                              | 1 = Framed S<br>0 = Framed S                                                                                                                                                             | Plx support en<br>Plx support dis                                                                                                                                                                                             | abled ( <del>SSx</del> p<br>sabled                                                                                                                                        |                              | e Sync pulse ir  | nput/output)       |       |

| bit 15<br>bit 14             | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar                                                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse                                                                                                                                                                            | abled ( <del>SSx</del> p<br>sabled<br>Direction Cor                                                                                                                       |                              | e Sync pulse ir  | nput/output)       |       |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar<br>1 = Frame Sy                                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input                                                                                                                                                          | abled ( <del>SSx</del> p<br>sabled<br>Direction Cor<br>(slave)                                                                                                            |                              | e Sync pulse ir  | nput/output)       |       |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar<br>1 = Frame Sy<br>0 = Frame Sy                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse                                                                                                                                                                            | abled (SSx p<br>sabled<br>Direction Coi<br>(slave)<br>tt (master)                                                                                                         |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra                                                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu                                                                                                                                        | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit                                                                                       |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy                                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls                                                                                                                       | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high                                                                           |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act                                                                                                    | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low                                                                |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14<br>bit 13             | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen                                                | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act                                                                                 | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'                                                          | ntrol bit                    | e Sync pulse ir  | nput/output)       |       |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy                                | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br>ted: Read as '<br>me Sync Pulse<br>nc pulse coinci                           | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first                      | trol bit<br>bit<br>bit clock | e Sync pulse ir  | nput/output)       |       |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy<br>0 = Frame Sy | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br><b>ted:</b> Read as 'u<br>me Sync Pulse<br>nc pulse coinci<br>nc pulse prece | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first<br>cdes first bit cl | trol bit<br>bit<br>bit clock |                  | nput/output)       |       |

### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | R/W-0  | R/W-0 |

|--------------|-------|--------------|-------|--------------|------------------|--------|-------|

| —            | —     | —            | —     |              | —                | AMSK9  | AMSK8 |

| bit 15       |       |              |       |              |                  |        | bit 8 |

|              |       |              |       |              |                  |        |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

| AMSK7        | AMSK6 | AMSK5        | AMSK4 | AMSK3        | AMSK2            | AMSK1  | AMSK0 |

| bit 7        |       |              |       |              |                  | •      | bit 0 |

|              |       |              |       |              |                  |        |       |

| Legend:      |       |              |       |              |                  |        |       |

| R = Readable | bit   | W = Writable | bit   | U = Unimpler | mented bit, read | as '0' |       |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSKx: Mask for Address bit x Select bits

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

| U-0             | U-0                                                     | R/W-0                                                                       | R/W-0         | r-0                          | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|-----------------|---------------------------------------------------------|-----------------------------------------------------------------------------|---------------|------------------------------|------------------|-----------------|-------|--|--|--|

| —               | -                                                       | CSIDL                                                                       | ABAT          | _                            |                  | REQOP<2:0>      |       |  |  |  |

| bit 15          |                                                         |                                                                             |               |                              |                  |                 | bit   |  |  |  |

| R-1             | R-0                                                     | R-0                                                                         | U-0           | R/W-0                        | U-0              | U-0             | R/W-0 |  |  |  |

|                 | OPMODE<2:0                                              | >                                                                           | _             | CANCAP                       |                  | _               | WIN   |  |  |  |

| bit 7           |                                                         |                                                                             |               |                              |                  |                 | bit   |  |  |  |

| Legend:         |                                                         | r = Reserved                                                                | bit           |                              |                  |                 |       |  |  |  |

| R = Readable    | bit                                                     | W = Writable                                                                | bit           | U = Unimpler                 | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value at I | POR                                                     | '1' = Bit is se                                                             |               | ʻ0' = Bit is cle             | -                | x = Bit is unkr | nown  |  |  |  |

| bit 15-14       | Unimpleme                                               | nted: Read as                                                               | 'O'           |                              |                  |                 |       |  |  |  |

| bit 13          | -                                                       | p in Idle Mode I                                                            |               |                              |                  |                 |       |  |  |  |

|                 |                                                         | •                                                                           |               | levice enters Id             | le mode          |                 |       |  |  |  |

|                 |                                                         | e module opera                                                              |               |                              |                  |                 |       |  |  |  |

| bit 12          |                                                         | t All Pending Tr                                                            |               |                              |                  |                 |       |  |  |  |

|                 |                                                         | ll transmit buffe<br>will clear this bi                                     |               | nsmission<br>smissions are a | aborted          |                 |       |  |  |  |

| bit 11          | Reserved:                                               | Do no use                                                                   |               |                              |                  |                 |       |  |  |  |

| bit 10-8        | REQOP<2:0>: Request Operation Mode bits                 |                                                                             |               |                              |                  |                 |       |  |  |  |

|                 | 111 = Set Listen All Messages mode                      |                                                                             |               |                              |                  |                 |       |  |  |  |

|                 | 110 = Reserved – do not use                             |                                                                             |               |                              |                  |                 |       |  |  |  |

|                 |                                                         | rved – do not us                                                            |               |                              |                  |                 |       |  |  |  |

|                 |                                                         | onfiguration mo<br>sten Only Mode                                           |               |                              |                  |                 |       |  |  |  |

|                 |                                                         | oopback mode                                                                | 5             |                              |                  |                 |       |  |  |  |

|                 |                                                         | isable mode                                                                 |               |                              |                  |                 |       |  |  |  |

|                 | 000 <b>= Set N</b>                                      | ormal Operatio                                                              | n mode        |                              |                  |                 |       |  |  |  |

| bit 7-5         |                                                         | 2:0>: Operation                                                             |               |                              |                  |                 |       |  |  |  |

|                 |                                                         | le is in Listen A                                                           | II Messages n | node                         |                  |                 |       |  |  |  |

|                 | 110 = Reserved                                          |                                                                             |               |                              |                  |                 |       |  |  |  |

|                 | 101 = Reserved<br>100 = Module is in Configuration mode |                                                                             |               |                              |                  |                 |       |  |  |  |

|                 | 011 = Module is in Listen Only mode                     |                                                                             |               |                              |                  |                 |       |  |  |  |

|                 | 010 = Module is in Loopback mode                        |                                                                             |               |                              |                  |                 |       |  |  |  |

|                 |                                                         | 001 = Module is in Disable mode<br>000 = Module is in Normal Operation mode |               |                              |                  |                 |       |  |  |  |

| bit 4           |                                                         | nted: Read as                                                               | -             | ue                           |                  |                 |       |  |  |  |

| bit 3           | -                                                       |                                                                             |               | Capture Event                | Enable bit       |                 |       |  |  |  |

| bit 5           |                                                         | •                                                                           |               | nessage receiv               |                  |                 |       |  |  |  |

|                 |                                                         | CAN capture                                                                 |               | licectage recent             | •                |                 |       |  |  |  |

| bit 2-1         | Unimpleme                                               | nted: Read as                                                               | '0'           |                              |                  |                 |       |  |  |  |

| bit 0           | WIN: SFR                                                | Map Window Se                                                               | elect bit     |                              |                  |                 |       |  |  |  |

|                 | 1 = Use filte                                           | r window                                                                    |               |                              |                  |                 |       |  |  |  |

|                 | 0 = Use buff                                            |                                                                             |               |                              |                  |                 |       |  |  |  |

| R/W-0                  | R/W-0        | R/W-0                                                                                                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W    | /-0   |  |  |

|------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|-----------------|--------|-------|--|--|

| F15M                   | SK<1:0>      | F14MS                                                                                                                 | K<1:0>           | F13MS            | SK<1:0>         | F12MS           | K<1:0> |       |  |  |

| bit 15                 |              |                                                                                                                       |                  |                  |                 | •               |        | bit 8 |  |  |

|                        |              |                                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| R/W-0                  | R/W-0        | R/W-0                                                                                                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W    | /-0   |  |  |

| F11M                   | SK<1:0>      | F10MS                                                                                                                 | K<1:0>           | F9MS             | K<1:0>          | F8MSł           | <<1:0> |       |  |  |

| bit 7                  |              |                                                                                                                       |                  |                  |                 |                 |        | bit C |  |  |

|                        |              |                                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| Legend:                |              |                                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| R = Readable           | e bit        | W = Writable                                                                                                          | bit              | U = Unimplen     | nented bit, rea | d as '0'        |        |       |  |  |

| -n = Value at          | POR          | '1' = Bit is set                                                                                                      |                  | '0' = Bit is cle | ared            | x = Bit is unkn | iown   |       |  |  |

|                        |              |                                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| bit 15-14              | F15MSK<1:0   | )>: Mask Sourc                                                                                                        | e for Filter 15  | bit              |                 |                 |        |       |  |  |

|                        |              | ed; do not use                                                                                                        |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 2 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 1 reg<br>ince Mask 0 reg                                                                                    |                  |                  |                 |                 |        |       |  |  |

| bit 13-12              | -            | >: Mask Sourc                                                                                                         |                  |                  |                 |                 |        |       |  |  |

| 511 10 12              |              | ed; do not use                                                                                                        |                  | bit              |                 |                 |        |       |  |  |

|                        |              | ince Mask 2 reg                                                                                                       | gisters contain  | n mask           |                 |                 |        |       |  |  |

|                        | •            | ince Mask 1 reg                                                                                                       | •                |                  |                 |                 |        |       |  |  |

|                        | -            | ince Mask 0 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| bit 11-10              |              | >: Mask Sourc                                                                                                         | e for Filter 13  | bit              |                 |                 |        |       |  |  |

|                        |              | ed; do not use                                                                                                        | niatora contain  | maak             |                 |                 |        |       |  |  |

|                        |              | 10 = Acceptance Mask 2 registers contain mask<br>01 = Acceptance Mask 1 registers contain mask                        |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 0 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| bit 9-8                | -            | >: Mask Sourc                                                                                                         |                  |                  |                 |                 |        |       |  |  |

|                        | 11 = Reserve | ed; do not use                                                                                                        |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 2 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 1 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| <b>h</b> it <b>7</b> C |              | ince Mask 0 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| bit 7-6                |              | Hask Sourced; do not use                                                                                              | e for Fliter 11  | DIT              |                 |                 |        |       |  |  |

|                        |              | ince Mask 2 reg                                                                                                       | nisters contain  | mask             |                 |                 |        |       |  |  |

|                        |              | ince Mask 1 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

|                        | 00 = Accepta | ince Mask 0 reg                                                                                                       | jisters contain  | n mask           |                 |                 |        |       |  |  |

| bit 5-4                | F10MSK<1:0   | >: Mask Sourc                                                                                                         | e for Filter 10  | bit              |                 |                 |        |       |  |  |

|                        |              | ed; do not use                                                                                                        |                  |                  |                 |                 |        |       |  |  |

|                        |              | <ul><li>10 = Acceptance Mask 2 registers contain mask</li><li>01 = Acceptance Mask 1 registers contain mask</li></ul> |                  |                  |                 |                 |        |       |  |  |

|                        | •            | ince Mask 1 reg                                                                                                       | •                |                  |                 |                 |        |       |  |  |

| bit 3-2                |              | : Mask Source                                                                                                         |                  |                  |                 |                 |        |       |  |  |

| 511 0 2                |              | ed; do not use                                                                                                        |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 2 reg                                                                                                       | gisters contain  | n mask           |                 |                 |        |       |  |  |

|                        | 01 = Accepta | ince Mask 1 reg                                                                                                       | gisters contain  | n mask           |                 |                 |        |       |  |  |

|                        | -            | ince Mask 0 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

| bit 1-0                |              | : Mask Source                                                                                                         | for Filter 8 bit | İ                |                 |                 |        |       |  |  |

|                        |              | ed; do not use                                                                                                        | 1.1              |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 2 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 1 reg                                                                                                       |                  |                  |                 |                 |        |       |  |  |

|                        |              | ince Mask 0 reg                                                                                                       | JISICIS CUITAIL  | masn             |                 |                 |        |       |  |  |

### REGISTER 21-19: CiFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

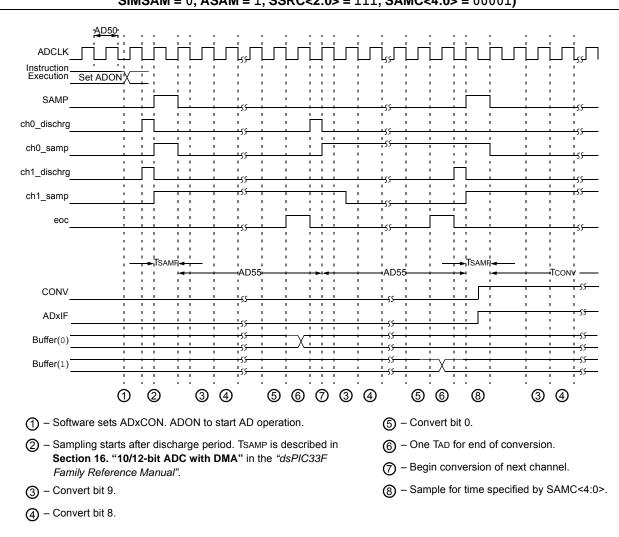

### 22.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

### 22.5 ADC Resources

Many useful resources related to ADC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en546066                                                                                                                          |

### 22.5.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools