Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 20 MIPS                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 30K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

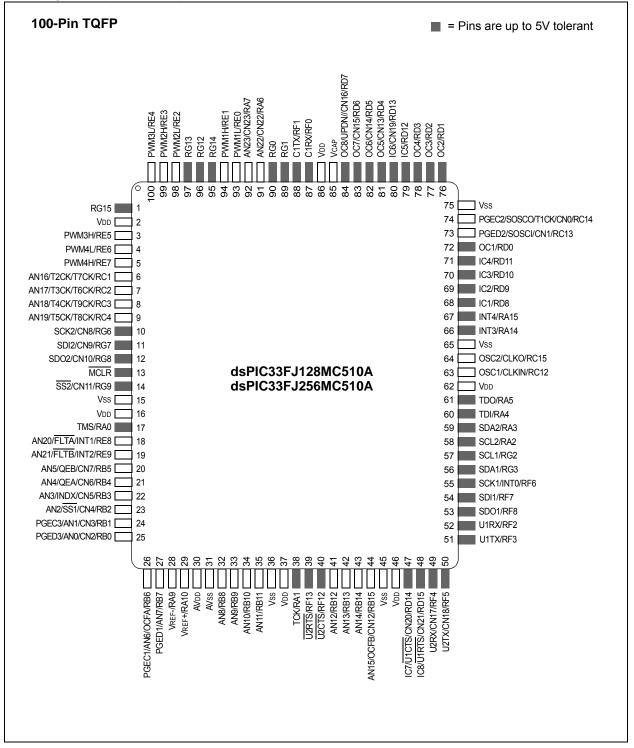

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc710a-h-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Pin Diagrams (Continued)**

### **Table of Contents**

| dsPI | C33F Product Families                                                                            |     |

|------|--------------------------------------------------------------------------------------------------|-----|

| 1.0  | Device Overview                                                                                  |     |

| 2.0  | Guidelines for Getting Started with 16-bit Digital Signal Controllers                            | 19  |

| 3.0  | CPU                                                                                              |     |

| 4.0  | Memory Organization                                                                              |     |

| 5.0  | Flash Program Memory                                                                             | 73  |

| 6.0  | Reset                                                                                            |     |

| 7.0  | Interrupt Controller                                                                             |     |

| 8.0  | Direct Memory Access (DMA)                                                                       | 133 |

| 9.0  | Oscillator Configuration                                                                         |     |

| 10.0 | Power-Saving Features                                                                            | 153 |

|      | I/O Ports                                                                                        |     |

| 12.0 | Timer1                                                                                           |     |

| 13.0 | Timer2/3, Timer4/5, Timer6/7 and Timer8/9                                                        |     |

| 14.0 | Input Capture                                                                                    |     |

|      | Output Compare                                                                                   |     |

| 16.0 | Motor Control PWM Module                                                                         |     |

| 17.0 |                                                                                                  |     |

|      | Serial Peripheral Interface (SPI)                                                                |     |

| 19.0 | Inter-Integrated Circuit (I <sup>2</sup> C™)                                                     |     |

| 20.0 | Universal Asynchronous Receiver Transmitter (UART)                                               |     |

|      | Enhanced CAN Module                                                                              |     |

| 22.0 | 10-bit/12-bit Analog-to-Digital Converter (ADC)                                                  |     |

| 23.0 | Special Features                                                                                 |     |

| 24.0 | Instruction Set Summary                                                                          |     |

| 25.0 | Development Support                                                                              |     |

| 26.0 | Electrical Characteristics                                                                       |     |

|      | High Temperature Electrical Characteristics                                                      |     |

|      | DC and AC Device Characteristics Graphs                                                          |     |

|      | Packaging Information                                                                            |     |

|      | ndix A: Migrating from dsPIC33FJXXXMCX06/X08/X10 Devices to dsPIC33FJXXXMCX06A/X08A/X10A Devices |     |

|      | ndix B: Revision History                                                                         |     |

|      |                                                                                                  |     |

|      | Nicrochip Web Site                                                                               |     |

|      | omer Change Notification Service                                                                 |     |

|      | omer Support                                                                                     |     |

|      | er Response                                                                                      |     |

| Prod | uct Identification System                                                                        | 371 |

NOTES:

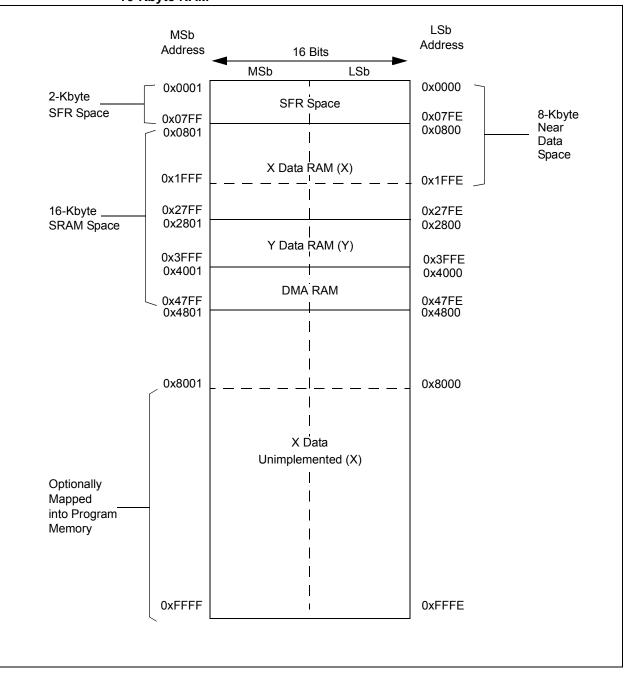

#### 4.0 MEMORY ORGANIZATION

Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to Section 3. "Data Memory" (DS70202) and Section 4. "Program Memory" (DS70203) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06A/X08A/X10A architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJXXXMCX06A/X08A/X10A devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in **Section 4.6** "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space. Memory usage for the dsPIC33FJXXXMCX06A/X08A/X10A family of devices is shown in Figure 4-1.

|                            | dsPIC33FJ64MCXXXA                                  | dsPIC33FJ128MCXXXA                                 | dsPIC33FJ256MCXXXA     |                                  |

|----------------------------|----------------------------------------------------|----------------------------------------------------|------------------------|----------------------------------|

| Ā                          | GOTO Instruction                                   | GOTO Instruction                                   | GOTO Instruction       | 0x000000<br>0x000002             |

|                            | Reset Address                                      | Reset Address                                      | Reset Address          | 0x000002<br>0x000004             |

|                            | Interrupt Vector Table                             | Interrupt Vector Table                             | Interrupt Vector Table | 0x0000FE                         |

|                            | Reserved                                           | Reserved                                           | Reserved               | 0x000100<br>0x000104             |

|                            | Alternate Vector Table                             | Alternate Vector Table                             | Alternate Vector Table | 0x0001FE                         |

| User Memory Space          | User Program<br>Flash Memory<br>(22K instructions) | User Program<br>Flash Memory<br>(44K instructions) | User Program           | 0x000200<br>0x00ABFE<br>0x00AC00 |

| Jory                       |                                                    |                                                    | (88K instructions)     |                                  |

| len                        |                                                    |                                                    |                        | 0x0157FE                         |

| er N                       | Linimplemented                                     |                                                    |                        | 0x015800                         |

| N                          | Unimplemented<br>(Read '0's)                       |                                                    |                        | <b>-</b> -                       |

|                            | (Read 0.5)                                         | Unimplemented                                      |                        | 0x02ABFE<br>0x02AC00             |

|                            |                                                    | (Read '0's)                                        | Unimplemented          |                                  |

|                            |                                                    |                                                    | (Read '0's)            |                                  |

| •                          |                                                    |                                                    | (Read 0.3)             | 0x7FFFFE                         |

| <b>Å</b>                   |                                                    |                                                    |                        | 0x800000                         |

|                            | Reserved                                           | Reserved                                           | Reserved               |                                  |

| ace                        | Device Configuration                               | Device Configuration                               | Device Configuration   | 0xF7FFFE<br>0xF80000             |

| g<br>S                     | Registers                                          | Device Configuration<br>Registers                  | Registers              | 0xF80017                         |

| Configuration Memory Space | Reserved                                           | Reserved                                           | Reserved               | 0xF80010                         |

| Confi                      | DEVID (2)                                          | <br>DEVID (2)                                      | DEVID (2)              | 0xFEFFFE<br>0xFF0000             |

| <u> </u>                   | ==::=(=)                                           |                                                    | ==::= (=)              | 0xFFFFFE                         |

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES

## FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 16-Kbyte RAM

#### TABLE 4-32: PORTG REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TRISG     | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 | —      | _      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | —     | _     | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| PORTG     | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1    | RG0    | xxxx          |

| LATG      | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1  | LATG0  | xxxx          |

| ODCG      | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | —     | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-33: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3 | Bit 2     | Bit 1   | Bit 0 | All<br>Resets   |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|------------|-------|-----------|---------|-------|-----------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _         | _      | —      | —      | —         | VREGS | EXTR    | SWR    | SWDTEN | WDTO       | SLEEP | IDLE      | BOR     | POR   | xxxx(1)         |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >      | —      | 1      | NOSC<2:0  | >     | CLKLOCK | _      | LOCK   | _          | CF    | —         | LPOSCEN | OSWEN | 0300 <b>(2)</b> |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | •      | DOZEN  | F      | RCDIV<2:0 | )>    | PLLPOS  | T<1:0> | _      |            | F     | PLLPRE<4: | :0>     |       | 3040            |

| PLLFBD    | 0746 |        | —      | _         | _      | —      |        | —         |       |         |        | F      | PLLDIV<8:0 | >     |           |         |       | 0030            |

| OSCTUN    | 0748 |        | —      | _         | _      | _      | _      | _         |       | —       | —      |        |            | TUN   | l<5:0>    |         |       | 0000            |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and type of Reset.

#### TABLE 4-34: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1           | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-----------------|-------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | —      | —      | _      | _     | _     | _     | ERASE | _     | -     | NVMOP<3:0> |       | 0000 <b>(1)</b> |       |               |

| NVMKEY    | 0766 |        |        | _      |        | _      | —      |       | _     |       |       |       | NVMKE | Y<7:0>     |       |                 |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-35: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | C2MD  | C1MD   | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3      | 0774 | T9MD   | T8MD   | T7MD   | T6MD   | _      | _      | -     | _     | _      | _     | —     | -      | -      | —     | I2C2MD | AD2MD | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

#### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3 (CONTINUED)

- bit 1 SI2C2IF: I2C2 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 T7IF: Timer7 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| U-0          | R/W-1                                           | R/W-0                                     | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|-------------------------------------------------|-------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| _            |                                                 | C2RXIP<2:0>                               | 1011 0         | _                |                 | INT4IP<2:0>     | 10110 |  |  |  |  |  |

| bit 15       |                                                 |                                           |                |                  |                 |                 | bit 8 |  |  |  |  |  |

|              |                                                 |                                           |                |                  |                 |                 |       |  |  |  |  |  |

| U-0          | R/W-1                                           | R/W-0                                     | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|              |                                                 | INT3IP<2:0>                               |                | —                |                 | T9IP<2:0>       |       |  |  |  |  |  |

| bit 7        |                                                 |                                           |                |                  |                 |                 | bit 0 |  |  |  |  |  |

| Legend:      |                                                 |                                           |                |                  |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                          | W = Writable t                            | bit            | U = Unimple      | mented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value a | t POR                                           | '1' = Bit is set                          |                | '0' = Bit is cle | eared           | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15       | Unimplom                                        | ented: Read as 'o                         | <b>`</b>       |                  |                 |                 |       |  |  |  |  |  |

| bit 13       | -                                               | 0>: ECAN2 Rece                            |                | adv Interrunt Pi | riority hits    |                 |       |  |  |  |  |  |

|              |                                                 | rupt is priority 7 (h                     |                | •                | ionty bits      |                 |       |  |  |  |  |  |

|              | •                                               |                                           | g. eet p. en   | ()               |                 |                 |       |  |  |  |  |  |

|              | •                                               |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              | •<br>001 = Inter                                | rupt is priority 1                        |                |                  |                 |                 |       |  |  |  |  |  |

|              |                                                 | rupt source is disa                       | abled          |                  |                 |                 |       |  |  |  |  |  |

| bit 11       | Unimpleme                                       | ented: Read as 'o                         | )'             |                  |                 |                 |       |  |  |  |  |  |

| bit 10-8     | INT4IP<2:0>: External Interrupt 4 Priority bits |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              | 111 = Inter                                     | rupt is priority 7 (h                     | nighest priori | ty interrupt)    |                 |                 |       |  |  |  |  |  |

|              | •                                               |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              | •                                               |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              |                                                 | rupt is priority 1                        |                |                  |                 |                 |       |  |  |  |  |  |

|              |                                                 | rupt source is disa                       |                |                  |                 |                 |       |  |  |  |  |  |

| bit 7        | -                                               | ented: Read as 'o                         |                |                  |                 |                 |       |  |  |  |  |  |

| bit 6-4      |                                                 | >: External Interr                        |                |                  |                 |                 |       |  |  |  |  |  |

|              | ⊥⊥⊥ = inten<br>•                                | rupt is priority 7 (h                     | lignest priori | ty interrupt)    |                 |                 |       |  |  |  |  |  |

|              | •                                               |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              | •                                               |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              |                                                 | rupt is priority 1<br>rupt source is disa | abled          |                  |                 |                 |       |  |  |  |  |  |

| bit 3        |                                                 | ented: Read as '0                         |                |                  |                 |                 |       |  |  |  |  |  |

| bit 2-0      | -                                               | Timer9 Interrupt                          |                |                  |                 |                 |       |  |  |  |  |  |

|              | 111 = Inter                                     | rupt is priority 7 (h                     | nighest priori | ty interrupt)    |                 |                 |       |  |  |  |  |  |

|              | •                                               |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              | •                                               |                                           |                |                  |                 |                 |       |  |  |  |  |  |

|              | 001 = Inter                                     | rupt is priority 1                        |                |                  |                 |                 |       |  |  |  |  |  |

|              |                                                 | rupt source is disa                       | abled          |                  |                 |                 |       |  |  |  |  |  |

|              |                                                 |                                           | abled          |                  |                 |                 |       |  |  |  |  |  |

#### REGISTER 7-28: IPC13: INTERRUPT PRIORITY CONTROL REGISTER 13

REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0         | U-0                                                                                                                                | R/W-0                                  | R/W-1, HC                          | R/W-0                         | R/W-0                      | R/W-0              | R/W-0          |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------|-------------------------------|----------------------------|--------------------|----------------|--|--|--|--|--|

| I2CEN         |                                                                                                                                    | I2CSIDL                                | SCLREL                             | IPMIEN                        | A10M                       | DISSLW             | SMEN           |  |  |  |  |  |

| bit 15        | -                                                                                                                                  |                                        |                                    |                               |                            |                    | bit 8          |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                              | R/W-0                                  | R/W-0, HC                          | R/W-0, HC                     | R/W-0, HC                  | R/W-0, HC          | R/W-0, HC      |  |  |  |  |  |

| GCEN          | STREN                                                                                                                              | ACKDT                                  | ACKEN                              | RCEN                          | PEN                        | RSEN               | SEN            |  |  |  |  |  |

| bit 7         | OTTLEN                                                                                                                             | AGIND I                                | AUNEN                              | ROLIN                         |                            | ROLIN              | bit            |  |  |  |  |  |

|               |                                                                                                                                    |                                        |                                    |                               |                            |                    |                |  |  |  |  |  |

| Legend:       |                                                                                                                                    | U = Unimpler                           | mented bit, rea                    | d as '0'                      |                            |                    |                |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                              | W = Writable                           | bit                                | HS = Hardwar                  | e Settable bit             | HC = Hardwar       | e Clearable bi |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                | '1' = Bit is set                       | t                                  | '0' = Bit is cle              | ared                       | x = Bit is unkn    | own            |  |  |  |  |  |

| bit 15        | <b>12CEN:</b> 12Cx                                                                                                                 | (Enable bit                            |                                    |                               |                            |                    |                |  |  |  |  |  |

| DIL 15        |                                                                                                                                    |                                        | le and configu                     | res the SDAX                  | and SCI v nine             | as serial port pir | 16             |  |  |  |  |  |

|               |                                                                                                                                    |                                        |                                    |                               | ed by port func            |                    | 15             |  |  |  |  |  |

| bit 14        | Unimpleme                                                                                                                          | nted: Read as                          | ʻ0 <b>'</b>                        |                               |                            |                    |                |  |  |  |  |  |

| bit 13        | I2CSIDL: St                                                                                                                        | op in Idle Mode                        | e bit                              |                               |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    |                                        | eration when d<br>ition in Idle mo |                               | n Idle mode                |                    |                |  |  |  |  |  |

| bit 12        |                                                                                                                                    |                                        | ontrol bit (wher                   |                               | I <sup>2</sup> C slave)    |                    |                |  |  |  |  |  |

|               | 1 = Release                                                                                                                        |                                        |                                    | r operating as                |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    | Lx clock low (c                        | lock stretch)                      |                               |                            |                    |                |  |  |  |  |  |

|               | If STREN =                                                                                                                         | 1:                                     |                                    |                               |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    |                                        |                                    |                               |                            | elease clock). H   | lardware clea  |  |  |  |  |  |

|               |                                                                                                                                    |                                        | nission. Hardw                     | are clear at en               | d of slave rece            | ption.             |                |  |  |  |  |  |

|               | If STREN =                                                                                                                         |                                        | v oply write '1'                   | to rologgo clo                | k) Hardwara a              | lear at beginnin   | a of clavo     |  |  |  |  |  |

|               | transmission                                                                                                                       |                                        |                                    |                               | sk). Haluwale c            | acar at beginnin   | y of slave     |  |  |  |  |  |

| bit 11        | IPMIEN: Inte                                                                                                                       | elligent Periphe                       | ral Manageme                       | nt Interface (IF              | MI) Enable bit             |                    |                |  |  |  |  |  |

|               | 1 = IPMI mo                                                                                                                        | de is enabled;                         | all addresses A                    | Acknowledged                  | ·                          |                    |                |  |  |  |  |  |

|               | 0 = IPMI mo                                                                                                                        | de disabled                            |                                    |                               |                            |                    |                |  |  |  |  |  |

| bit 10        | A10M: 10-B                                                                                                                         | it Slave Addres                        | s bit                              |                               |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    | D is a 10-bit sla<br>D is a 7-bit slav |                                    |                               |                            |                    |                |  |  |  |  |  |

| bit 9         |                                                                                                                                    | sable Slew Rat                         |                                    |                               |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    | e control disabl                       |                                    |                               |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    | e control enabl                        |                                    |                               |                            |                    |                |  |  |  |  |  |

| bit 8         |                                                                                                                                    | Bus Input Level                        |                                    |                               |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    | /O pin threshol<br>SMBus input th      | ds compliant w<br>iresholds        | ith SMBus spe                 | ecification                |                    |                |  |  |  |  |  |

| bit 7         | GCEN: Gen                                                                                                                          | eral Call Enabl                        | e bit (when ope                    | erating as I <sup>2</sup> C s | slave)                     |                    |                |  |  |  |  |  |

|               | 1 = Enable<br>receptio                                                                                                             | -                                      | a general call                     | address is rec                | eived in the I20           | CxRSR (module      | is enabled for |  |  |  |  |  |

|               |                                                                                                                                    | l call address d                       | isabled                            |                               |                            |                    |                |  |  |  |  |  |

| bit 6         | STREN: SC                                                                                                                          | Lx Clock Streto                        | h Enable bit (w                    | hen operating                 | as l <sup>2</sup> C slave) |                    |                |  |  |  |  |  |

|               | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit. |                                        |                                    |                               |                            |                    |                |  |  |  |  |  |

|               | 1 = Enable software or receive clock stretching                                                                                    |                                        |                                    |                               |                            |                    |                |  |  |  |  |  |

|               |                                                                                                                                    |                                        |                                    |                               |                            |                    |                |  |  |  |  |  |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | R/W-0  | R/W-0 |

|--------------|-------|--------------|-------|--------------|------------------|--------|-------|

| —            | —     | —            | —     |              | —                | AMSK9  | AMSK8 |

| bit 15       |       |              |       |              |                  |        | bit 8 |

|              |       |              |       |              |                  |        |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

| AMSK7        | AMSK6 | AMSK5        | AMSK4 | AMSK3        | AMSK2            | AMSK1  | AMSK0 |

| bit 7        |       |              |       |              |                  | •      | bit 0 |

|              |       |              |       |              |                  |        |       |

| Legend:      |       |              |       |              |                  |        |       |

| R = Readable | bit   | W = Writable | bit   | U = Unimpler | mented bit, read | as '0' |       |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSKx: Mask for Address bit x Select bits

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

#### REGISTER 21-12: CiBUFPNT1: ECAN™ FILTER 0-3 BUFFER POINTER REGISTER

|                 | R/W-0         | R/W-0                                | R/W-0           | R/W-0             | R/W-0         | R/W-0           | R/W-0 |

|-----------------|---------------|--------------------------------------|-----------------|-------------------|---------------|-----------------|-------|

|                 | F3BP          | <3:0>                                |                 |                   | F2BI          | ><3:0>          |       |

| bit 15          |               |                                      |                 |                   |               |                 | bit 8 |

|                 |               |                                      |                 |                   |               |                 |       |

| R/W-0           | R/W-0         | R/W-0                                | R/W-0           | R/W-0             | R/W-0         | R/W-0           | R/W-0 |

|                 | F1BP          | <3:0>                                |                 |                   | F0B           | P<3:0>          |       |

| bit 7           |               |                                      |                 |                   |               |                 | bit 0 |

| Legend:         |               |                                      |                 |                   |               |                 |       |

| R = Readable    | hit           | W = Writable                         | hit             | U = Unimplem      | ented hit rea | d as '0'        |       |

| -n = Value at F |               | '1' = Bit is set                     |                 | '0' = Bit is clea |               | x = Bit is unki | nown  |

|                 | •••           | 2.1.0 000                            |                 | 0 2000 0000       |               |                 |       |

| bit 15-12       | F3BP<3:0>:    | RX Buffer Writt                      | en when Filte   | er 3 Hits bits    |               |                 |       |

|                 |               | hits received in                     |                 | -                 |               |                 |       |

|                 |               | hits received in                     | NRX Buffer 1    | 4                 |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | 0001 = Filter | hits received ir                     | n RX Buffer 1   |                   |               |                 |       |

|                 | 0000 = Filter | hits received in                     | n RX Buffer 0   |                   |               |                 |       |

| bit 11-8        |               | RX Buffer Writt                      |                 |                   |               |                 |       |

|                 |               | hits received in<br>hits received in |                 | -                 |               |                 |       |

|                 | •             |                                      | li o C Ballor I |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 |               | hits received in hits received in    |                 |                   |               |                 |       |

| bit 7-4         |               | RX Buffer Writt                      |                 |                   |               |                 |       |

|                 |               | hits received in<br>hits received in |                 | -                 |               |                 |       |

|                 | •             |                                      | THAT Durier 1   | -                 |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 |               | hits received in hits received in    |                 |                   |               |                 |       |

| bit 3-0         | F0BP<3:0>:    | RX Buffer Writt                      | en when Filte   | er 0 Hits bits    |               |                 |       |

|                 |               | hits received in                     |                 |                   |               |                 |       |

|                 | 1110 = Filter | hits received ir                     | n RX Buffer 1   | 4                 |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | 0001 = Filter | hits received in                     |                 |                   |               |                 |       |

|                 |               | TIILS IECEIVEU II                    |                 |                   |               |                 |       |

### 22.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices have up to 32 ADC input channels. These devices also have up to 2 ADC modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

### 22.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported.

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device.

A block diagram of the ADC is shown in Figure 22-1.

### 22.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>)

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>)

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>)

- g) Turn on ADC module (ADxCON1<15>)

- 2. Configure ADC interrupt (if required):

- a) Clear the ADxIF bit

- b) Select ADC interrupt priority

### 22.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM Buffer Pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

## 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

#### 25.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

#### 25.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 25.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 25.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 25.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 25.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

### 25.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 25.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 25.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 25.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

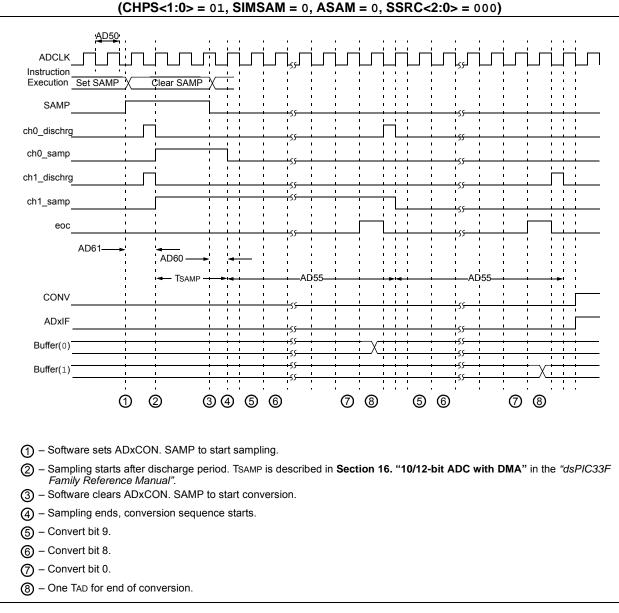

#### FIGURE 26-28: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01 SIMSAM = 0 ASAM = 0 SSRC<2:0> = 000)

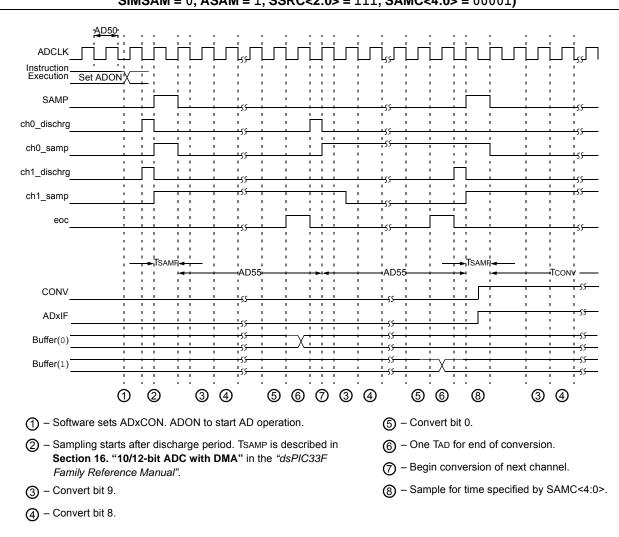

## FIGURE 26-29:ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01,<br/>SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

#### 29.0 **PACKAGING INFORMATION**

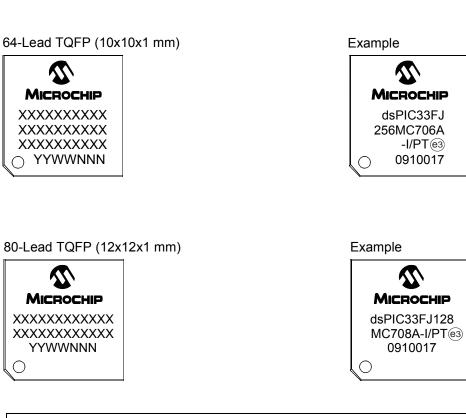

#### 29.1 **Package Marking Information**

64-Lead QFN (9x9x0.9mm)

| Legend | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

(

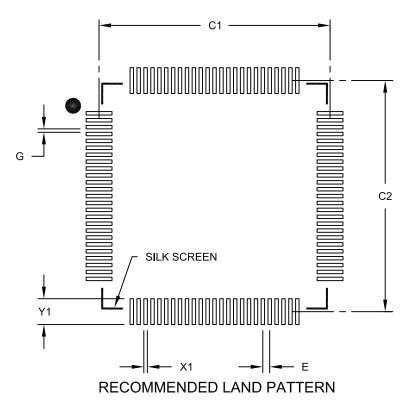

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                     |    | MILLIMETERS |       |      |

|---------------------------|----|-------------|-------|------|

| Dimension Limits          |    | MIN         | NOM   | MAX  |

| Contact Pitch             | E  | 0.40 BSC    |       |      |

| Contact Pad Spacing       | C1 |             | 13.40 |      |

| Contact Pad Spacing       | C2 |             | 13.40 |      |

| Contact Pad Width (X100)  | X1 |             |       | 0.20 |

| Contact Pad Length (X100) | Y1 |             |       | 1.50 |

| Distance Between Pads     | G  | 0.20        |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                                                   | ds                                     | PIC 33 FJ 256 MC7 10 A T I / PT - XXX                                               | Examples:                                                                                                                                                     |  |

|---------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tape and Reel Flag<br>Temperature Rang<br>Package | hily<br>Size (KB)<br>g (if applic<br>e |                                                                                     | <ul> <li>a) dsPIC33FJ256MC710ATI/PT:<br/>Motor Control dsPIC33,<br/>64-Kbyte program memory,<br/>64-pin, Industrial temperature,<br/>TQFP package.</li> </ul> |  |

| Architecture:                                     | 33 =                                   | 16-bit Digital Signal Controller                                                    |                                                                                                                                                               |  |

| Flash Memory Family:                              | FJ =                                   | Flash program memory, 3.3V                                                          |                                                                                                                                                               |  |

| Product Group:                                    | MC5 =<br>MC7 =                         | Motor Control family<br>Motor Control family                                        |                                                                                                                                                               |  |

| Pin Count:                                        | 06 =<br>08 =<br>10 =                   | 64-pin<br>80-pin<br>100-pin                                                         |                                                                                                                                                               |  |

| Temperature Range:                                | I =<br>E =<br>H =                      | -40°C to +85°C (Industrial)<br>-40°C to +125°C (Extended)<br>-40°C to +150°C (High) |                                                                                                                                                               |  |

| Package:                                          | PT =<br>PF =<br>MR =                   | 14x14 mm TQFP (Thin Quad Flatpack)                                                  |                                                                                                                                                               |  |

| Pattern                                           | Three-dig<br>(blank oth                | it QTP, SQTP, Code or Special Requirements<br>erwise)                               |                                                                                                                                                               |  |