Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                 |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 256KB (256K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 30K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10/12b                                                                      |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc710at-i-pf |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXMCX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and

three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data by blocks (or 'rows') of 64 instructions (192 bytes) at a time or by single program memory word; the user can erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

### 5.1 Table Instructions and Flash Programming

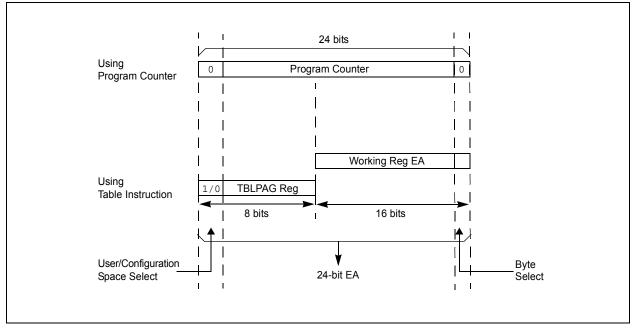

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| R/W-0         | R/W-0                                                                                                  | U-0                                                      | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|----------------------|------------------|----------------|---------|--|--|--|

| T6IF          | DMA4IF                                                                                                 | _                                                        | OC8IF            | OC7IF                | OC6IF            | OC5IF          | IC6IF   |  |  |  |

| bit 15        |                                                                                                        |                                                          |                  |                      |                  |                | bit 8   |  |  |  |

| R/W-0         | R/W-0                                                                                                  | R/W-0                                                    | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |  |  |  |

| IC5IF         | IC4IF                                                                                                  | IC3IF                                                    | DMA3IF           | C1IF                 | C1RXIF           | SPI2IF         | SPI2EIF |  |  |  |

| bit 7         |                                                                                                        |                                                          |                  |                      | I                |                | bit (   |  |  |  |

| Legend:       |                                                                                                        |                                                          |                  |                      |                  |                |         |  |  |  |

| R = Readable  | e bit                                                                                                  | W = Writable                                             | bit              | U = Unimple          | mented bit, read | l as '0'       |         |  |  |  |

| -n = Value at | POR                                                                                                    | '1' = Bit is set                                         |                  | '0' = Bit is cle     | eared            | x = Bit is unk | nown    |  |  |  |

| bit 15        | T6IF: Timer6                                                                                           | Interrupt Flag                                           | Status bit       |                      |                  |                |         |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                         |                  |                      |                  |                |         |  |  |  |

| bit 14        |                                                                                                        | •                                                        |                  | Complete Interi      | rupt Flag Status | bit            |         |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                         |                  | ·                    |                  |                |         |  |  |  |

| bit 13        |                                                                                                        | ted: Read as '                                           |                  |                      |                  |                |         |  |  |  |

| bit 12        | OC8IF: Outpu                                                                                           | ut Compare Ch                                            | annel 8 Interr   | upt Flag Status      | s bit            |                |         |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                         |                  |                      |                  |                |         |  |  |  |

| bit 11        | OC7IF: Outpu                                                                                           | C7IF: Output Compare Channel 7 Interrupt Flag Status bit |                  |                      |                  |                |         |  |  |  |

|               |                                                                                                        | = Interrupt request has occurred                         |                  |                      |                  |                |         |  |  |  |

|               |                                                                                                        | 0 = Interrupt request has not occurred                   |                  |                      |                  |                |         |  |  |  |

| bit 10        | <b>OC6IF:</b> Output Compare Channel 6 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                                          |                  |                      |                  |                |         |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                         |                  |                      |                  |                |         |  |  |  |

| bit 9         | OC5IF: Output Compare Channel 5 Interrupt Flag Status bit                                              |                                                          |                  |                      |                  |                |         |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                         |                  |                      |                  |                |         |  |  |  |

| bit 8         | •                                                                                                      | Capture Chann                                            |                  | -lag Status hit      |                  |                |         |  |  |  |

| bit o         | 1 = Interrupt                                                                                          | request has oc<br>request has no                         | curred           | lag Status bit       |                  |                |         |  |  |  |

| bit 7         | •                                                                                                      | Capture Chann                                            |                  | -lao Status bit      |                  |                |         |  |  |  |

|               | •                                                                                                      | request has oc                                           | •                |                      |                  |                |         |  |  |  |

|               |                                                                                                        | request has no                                           |                  |                      |                  |                |         |  |  |  |

| bit 6         | IC4IF: Input C                                                                                         | Capture Chann                                            | el 4 Interrupt I | -lag Status bit      |                  |                |         |  |  |  |

|               |                                                                                                        | request has oc                                           |                  |                      |                  |                |         |  |  |  |

| bit 5         | -                                                                                                      | request has no<br>Capture Chann                          |                  | -<br>Elaa Status hit |                  |                |         |  |  |  |

| bit 5         | 1 = Interrupt                                                                                          | request has oc<br>request has no                         | curred           | ay status bit        |                  |                |         |  |  |  |

| bit 4         | •                                                                                                      | •                                                        |                  | omnlete Inter        | rupt Flag Status | hit            |         |  |  |  |

|               | 1 = Interrupt                                                                                          | request has oc<br>request has no                         | curred           |                      | apting Status    | JA             |         |  |  |  |

| bit 3         | -                                                                                                      | l Event Interrup                                         |                  | bit                  |                  |                |         |  |  |  |

| Sit U         |                                                                                                        | request has oc                                           | -                |                      |                  |                |         |  |  |  |

|               |                                                                                                        | request has no                                           |                  |                      |                  |                |         |  |  |  |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| R/W-0         | U-0                                                                                            | R/W-0                                                      | U-0             | U-0              | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| FLTAIF        | —                                                                                              | DMA5IF                                                     |                 | _                | QEIIF            | PWMIF           | C2IF  |  |  |  |  |

| bit 15        |                                                                                                | •                                                          |                 | ÷                |                  |                 | bit 8 |  |  |  |  |

| R/W-0         | R/W-0                                                                                          | R/W-0                                                      | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| C2RXIF        | INT4IF                                                                                         | INT3IF                                                     | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |  |  |  |  |

| bit 7         |                                                                                                |                                                            |                 |                  |                  | 0.202           | bit C |  |  |  |  |

| Legend:       |                                                                                                |                                                            |                 |                  |                  |                 |       |  |  |  |  |

| R = Readabl   | e bit                                                                                          | W = Writable                                               | bit             | U = Unimplei     | mented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at | POR                                                                                            | '1' = Bit is set                                           |                 | '0' = Bit is cle | eared            | x = Bit is unkn | iown  |  |  |  |  |

|               |                                                                                                |                                                            |                 |                  |                  |                 |       |  |  |  |  |

| bit 15        | FLTAIF: PWN                                                                                    | / Fault A Interr                                           | upt Flag Statu  | us bit           |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has oc                                             |                 |                  |                  |                 |       |  |  |  |  |

|               | •                                                                                              | request has no                                             |                 |                  |                  |                 |       |  |  |  |  |

| bit 14        | -                                                                                              | ted: Read as '                                             |                 |                  |                  |                 |       |  |  |  |  |

| bit 13        |                                                                                                |                                                            |                 | Complete Interr  | rupt Flag Status | bit             |       |  |  |  |  |

|               |                                                                                                | request has oco<br>request has not                         |                 |                  |                  |                 |       |  |  |  |  |

| bit 12-11     | •                                                                                              | ted: Read as '                                             |                 |                  |                  |                 |       |  |  |  |  |

| bit 10        | -                                                                                              | vent Interrupt F                                           |                 |                  |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has oc                                             | 0               |                  |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has not                                            |                 |                  |                  |                 |       |  |  |  |  |

| bit 9         | PWMIF: PWN                                                                                     | PWMIF: PWM Interrupt Flag Status bit                       |                 |                  |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has occ<br>request has not                         |                 |                  |                  |                 |       |  |  |  |  |

| bit 8         | C2IF: ECAN2                                                                                    | <b>C2IF:</b> ECAN2 Event Interrupt Flag Status bit         |                 |                  |                  |                 |       |  |  |  |  |

|               | •                                                                                              | = Interrupt request has occurred                           |                 |                  |                  |                 |       |  |  |  |  |

|               | 0 = Interrupt r                                                                                | request has not                                            | occurred        |                  |                  |                 |       |  |  |  |  |

| bit 7         |                                                                                                | C2RXIF: ECAN2 Receive Data Ready Interrupt Flag Status bit |                 |                  |                  |                 |       |  |  |  |  |

|               | <ol> <li>Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol> |                                                            |                 |                  |                  |                 |       |  |  |  |  |

| bit 6         | -                                                                                              | nal Interrupt 4                                            |                 | it               |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has oc                                             | -               | it.              |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has not                                            |                 |                  |                  |                 |       |  |  |  |  |

| bit 5         | INT3IF: Exter                                                                                  | INT3IF: External Interrupt 3 Flag Status bit               |                 |                  |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has oc                                             |                 |                  |                  |                 |       |  |  |  |  |

|               | -                                                                                              | request has not                                            |                 |                  |                  |                 |       |  |  |  |  |

| bit 4         |                                                                                                | Interrupt Flag                                             |                 |                  |                  |                 |       |  |  |  |  |

|               | •                                                                                              | request has oco<br>request has not                         |                 |                  |                  |                 |       |  |  |  |  |

| bit 3         | -                                                                                              | Interrupt Flag                                             |                 |                  |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has oc                                             |                 |                  |                  |                 |       |  |  |  |  |

|               | •                                                                                              | request has not                                            |                 |                  |                  |                 |       |  |  |  |  |

| bit 2         | MI2C2IF: I2C                                                                                   | 2 Master Even                                              | ts Interrupt FI | ag Status bit    |                  |                 |       |  |  |  |  |

|               |                                                                                                | request has oc                                             |                 |                  |                  |                 |       |  |  |  |  |

|               | 0 = Interrupt r                                                                                | request has not                                            | occurred        |                  |                  |                 |       |  |  |  |  |

### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

#### R/W-0 U-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 FLTAIE DMA5IE \_\_\_\_ QEIIE **PWMIE** C2IE \_\_\_\_ \_\_\_\_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 C2RXIE INT4IE INT3IE T9IE T8IE MI2C2IE SI2C2IE T7IE bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLTAIE: PWM Fault A Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 14 Unimplemented: Read as '0' bit 13 DMA5IE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 12-11 Unimplemented: Read as '0' bit 10 **QEIIE:** QEI Event Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 9 **PWMIE:** PWM Error Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 8 C2IE: ECAN2 Event Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 7 C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 6 INT4IE: External Interrupt 4 Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 5 INT3IE: External Interrupt 3 Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 4 **T9IE:** Timer9 Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 3 **T8IE:** Timer8 Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 2 MI2C2IE: I2C2 Master Events Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled

#### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0                                | U-0                                                            | U-0                                                                                                    | U-0            | U-0              | U-0             | U-0             | U-0    |  |  |  |

|------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|--------|--|--|--|

| _                                  | —                                                              | _                                                                                                      | —              | —                | —               | —               | _      |  |  |  |

| bit 15                             |                                                                |                                                                                                        | •              | •                |                 |                 | bit 8  |  |  |  |

|                                    |                                                                |                                                                                                        |                |                  |                 |                 |        |  |  |  |

| R/W-0                              | R/W-0                                                          | R/W-0                                                                                                  | R/W-0          | U-0              | R/W-0           | R/W-0           | R/W-0  |  |  |  |

| C2TXIE                             | C1TXIE                                                         | DMA7IE                                                                                                 | DMA6IE         | —                | U2EIE           | U1EIE           | FLTBIE |  |  |  |

| bit 7                              |                                                                |                                                                                                        |                |                  |                 |                 | bit (  |  |  |  |

| Legend:                            |                                                                |                                                                                                        |                |                  |                 |                 |        |  |  |  |

| R = Readab                         | le bit                                                         | W = Writable                                                                                           | bit            | U = Unimpler     | mented bit, rea | d as '0'        |        |  |  |  |

| -n = Value at POR '1' = Bit is set |                                                                |                                                                                                        |                | '0' = Bit is cle | ared            | x = Bit is unki | nown   |  |  |  |

| bit 15-8<br>bit 7                  | •                                                              | ted: Read as '                                                                                         |                | nterrunt Enabl   | e hit           |                 |        |  |  |  |

| bit 7                              | C2TXIE: ECA                                                    | N2 Transmit D                                                                                          | ata Request li | nterrupt Enable  | e bit           |                 |        |  |  |  |

|                                    |                                                                | request enable<br>request not ena                                                                      |                |                  |                 |                 |        |  |  |  |

| bit 6                              | C1TXIE: ECAN1 Transmit Data Request Interrupt Enable bit       |                                                                                                        |                |                  |                 |                 |        |  |  |  |

|                                    |                                                                | request enable<br>request not ena                                                                      |                |                  |                 |                 |        |  |  |  |

| bit 5                              | DMA7IE: DMA Channel 7 Data Transfer Complete Enable Status bit |                                                                                                        |                |                  |                 |                 |        |  |  |  |

|                                    |                                                                | request enable<br>request not ena                                                                      |                |                  |                 |                 |        |  |  |  |

| bit 4                              | DMA6IE: DM                                                     | A Channel 6 D                                                                                          | ata Transfer C | complete Enab    | le Status bit   |                 |        |  |  |  |

|                                    |                                                                | request enable<br>request not ena                                                                      |                |                  |                 |                 |        |  |  |  |

| bit 3                              | Unimplemen                                                     | ted: Read as '                                                                                         | 0'             |                  |                 |                 |        |  |  |  |

| bit 2                              | U2EIE: UART                                                    | Γ2 Error Interru                                                                                       | pt Enable bit  |                  |                 |                 |        |  |  |  |

|                                    |                                                                | request enable                                                                                         |                |                  |                 |                 |        |  |  |  |

| bit 1                              | •                                                              | <ul> <li>0 = Interrupt request not enabled</li> <li>U1EIE: UART1 Error Interrupt Enable bit</li> </ul> |                |                  |                 |                 |        |  |  |  |

|                                    | 1 = Interrupt ı                                                | request enable<br>request not ena                                                                      | d              |                  |                 |                 |        |  |  |  |

| bit 0                              | •                                                              | V Fault B Interr                                                                                       |                |                  |                 |                 |        |  |  |  |

| -                                  | ו = Interrupt ו                                                | request enable<br>request not ena                                                                      | d              |                  |                 |                 |        |  |  |  |

| U-0       | U-0           | U-0                                    | U-0             | U-0               | R/W-1             | R/W-0       | R/W-0 |

|-----------|---------------|----------------------------------------|-----------------|-------------------|-------------------|-------------|-------|

| —         | —             | —                                      | —               | —                 |                   | DMA1IP<2:0> |       |

|           |               | bit                                    |                 |                   |                   |             |       |

| U-0       | R/W-1         | R/W-0                                  | R/W-0           | U-0               | R/W-1             | R/W-0       | R/W-0 |

| —         |               | AD1IP<2:0>                             |                 | —                 |                   | U1TXIP<2:0> |       |

| bit 7     |               |                                        |                 |                   |                   |             | bit   |

| Legend:   |               |                                        |                 |                   |                   |             |       |

| -         | le bit        | W = Writable                           | bit             | U = Unimplei      | mented bit. rea   | d as '0'    |       |

|           |               |                                        |                 | -                 |                   |             | nown  |

|           |               |                                        |                 |                   |                   |             |       |

| bit 15-11 | Unimpleme     | nted: Read as 'o                       | o'              |                   |                   |             |       |

| bit 10-8  | DMA1IP<2:0    | 0>: DMA Channe                         | el 1 Data Tra   | nsfer Complete    | e Interrupt Prior | ity bits    |       |

|           | 111 = Interru | upt is priority 7 (I                   | highest priori  | ty interrupt)     | -                 | -           |       |

|           | •             |                                        |                 |                   |                   |             |       |

|           | •             |                                        |                 |                   |                   |             |       |

|           |               |                                        | abled           |                   |                   |             |       |

| bit 7     |               | -                                      |                 |                   |                   |             |       |

| bit 6-4   | -             |                                        |                 | e Interrupt Prio  | rity bits         |             |       |

|           |               |                                        |                 | -                 | -                 |             |       |

|           | •             |                                        |                 |                   |                   |             |       |

|           | •             |                                        |                 |                   |                   |             |       |

|           | 001 = Interru | upt is priority 1                      |                 |                   |                   |             |       |

|           |               | upt source is dis                      | abled           |                   |                   |             |       |

| bit 3     | Unimpleme     | nted: Read as '                        | כי              |                   |                   |             |       |

| bit 2-0   | U1TXIP<2:0    | >: UART1 Trans                         | smitter Interru | upt Priority bits |                   |             |       |

|           | 111 = Interru | upt is priority 7 (I                   | highest priori  | ty interrupt)     |                   |             |       |

|           | •             |                                        |                 |                   |                   |             |       |

|           | •             |                                        |                 |                   |                   |             |       |

|           |               |                                        |                 |                   |                   |             |       |

|           |               | upt is priority 1<br>upt source is dis |                 |                   |                   |             |       |

#### REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

NOTES:

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0      | R/W-0                  | U-0        | U-0                    | R/W-0      | R/W-0      |

|-------|------------------------|------------|------------------------|------------|------------------------|------------|------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5(2) | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2) | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2) | IRQSEL0(2) |

| bit 7 |                        |            |                        |            |                        |            | bit 0      |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: See Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

#### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | <b>XWCOL3:</b> Channel 3 DMA RAM Write Collision Flag bit<br>1 = Write collision detected                             |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| bit 2 | <ul> <li>0 = No write collision detected</li> <li>XWCOL2: Channel 2 DMA RAM Write Collision Flag bit</li> </ul>       |

|       | <ul> <li>1 = Write collision detected</li> <li>0 = No write collision detected</li> </ul>                             |

| bit 1 | XWCOL1: Channel 1 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected |

| R/W-0            | R/W-0                    | R/W-0                                             | R/W-0                              | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

|------------------|--------------------------|---------------------------------------------------|------------------------------------|-------------------|------------------|-----------------|---------|

| FAOV4H           | FAOV4L                   | FAOV3H                                            | FAOV3L                             | FAOV2H            | FAOV2L           | FAOV1H          | FAOV1L  |

| bit 15           |                          |                                                   |                                    |                   |                  |                 | bit 8   |

| R/W-0            | U-0                      | U-0                                               | U-0                                | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

| FLTAM            | 0-0                      | 0-0                                               | 0-0                                | FAEN4             | FAEN3            | FAEN2           | FAEN1   |

| bit 7            | —                        | _                                                 |                                    | FALIN4            | FAENS            | FALINZ          | bit C   |

|                  |                          |                                                   |                                    |                   |                  |                 | DILC    |

| Legend:          |                          |                                                   |                                    |                   |                  |                 |         |

| R = Readable     | e bit                    | W = Writable                                      | bit                                | U = Unimplen      | nented bit, read | d as '0'        |         |

| -n = Value at    | POR                      | '1' = Bit is set                                  |                                    | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 7<br>bit 6-4 | 0 = The Fault            | t A input pin fur                                 | ches all contro                    |                   |                  | ed in FLTACON   | √<15:8> |

| bit 3            | 1 = PWM4H/<br>0 = PWM4H/ | t Input A Enabl<br>PWM4L pin pai<br>PWM4L pin pai | r is controlled<br>r is not contro |                   |                  |                 |         |

| bit 2            | 1 = PWM3H/               | t Input A Enabl<br>PWM3L pin pai<br>PWM3L pin pai | r is controlled                    |                   |                  |                 |         |

| bit 1            | 1 = PWM2H/               | t Input A Enabl<br>PWM2L pin pai<br>PWM2L pin pai | r is controlled                    |                   |                  |                 |         |

| bit 0            | 1 = PWM1H/               | t Input A Enabl<br>PWM1L pin pai<br>PWM1L pin pai | r is controlled                    |                   |                  |                 |         |

### REGISTER 16-9: PxFLTACON: PWMx FAULT A CONTROL REGISTER

REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0         | U-0                    | R/W-0                                                                                                        | R/W-1, HC                             | R/W-0                         | R/W-0                      | R/W-0              | R/W-0          |  |  |  |  |

|---------------|------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|----------------------------|--------------------|----------------|--|--|--|--|

| I2CEN         |                        | I2CSIDL                                                                                                      | SCLREL                                | IPMIEN                        | A10M                       | DISSLW             | SMEN           |  |  |  |  |

| bit 15        | -                      |                                                                                                              |                                       |                               |                            |                    | bit 8          |  |  |  |  |

| R/W-0         | R/W-0                  | R/W-0                                                                                                        | R/W-0, HC                             | R/W-0, HC                     | R/W-0, HC                  | R/W-0, HC          | R/W-0, HC      |  |  |  |  |

| GCEN          | STREN                  | ACKDT                                                                                                        | ACKEN                                 | RCEN                          | PEN                        | RSEN               | SEN            |  |  |  |  |

| bit 7         | OTTLEN                 | AGIND I                                                                                                      | AUNEN                                 | ROLIN                         |                            | ROLIN              | bit            |  |  |  |  |

|               |                        |                                                                                                              |                                       |                               |                            |                    |                |  |  |  |  |

| Legend:       |                        | U = Unimpler                                                                                                 | mented bit, rea                       | d as '0'                      |                            |                    |                |  |  |  |  |

| R = Readable  | e bit                  | W = Writable                                                                                                 | bit                                   | HS = Hardwar                  | e Settable bit             | HC = Hardwar       | e Clearable bi |  |  |  |  |

| -n = Value at | POR                    | '1' = Bit is set                                                                                             | t                                     | '0' = Bit is cle              | ared                       | x = Bit is unkn    | own            |  |  |  |  |

| bit 15        | <b>12CEN:</b> 12Cx     | (Enable bit                                                                                                  |                                       |                               |                            |                    |                |  |  |  |  |

| DIL 15        |                        |                                                                                                              | le and configu                        | res the SDAX                  | and SCI v nine             | as serial port pir | 16             |  |  |  |  |

|               |                        |                                                                                                              |                                       |                               | ed by port func            |                    | 15             |  |  |  |  |

| bit 14        | Unimpleme              | nted: Read as                                                                                                | <b>'</b> 0 <b>'</b>                   |                               |                            |                    |                |  |  |  |  |

| bit 13        | I2CSIDL: St            | op in Idle Mode                                                                                              | e bit                                 |                               |                            |                    |                |  |  |  |  |

|               |                        |                                                                                                              | eration when d<br>ition in Idle mo    |                               | n Idle mode                |                    |                |  |  |  |  |

| bit 12        |                        |                                                                                                              |                                       |                               | I <sup>2</sup> C slave)    |                    |                |  |  |  |  |

|               |                        | <b>SCLREL:</b> SCLx Release Control bit (when operating as I <sup>2</sup> C slave)<br>1 = Release SCLx clock |                                       |                               |                            |                    |                |  |  |  |  |

|               |                        | Lx clock low (c                                                                                              | lock stretch)                         |                               |                            |                    |                |  |  |  |  |

|               | If STREN =             | 1:                                                                                                           |                                       |                               |                            |                    |                |  |  |  |  |

|               |                        |                                                                                                              |                                       |                               |                            | elease clock). H   | lardware clea  |  |  |  |  |

|               |                        |                                                                                                              | nission. Hardw                        | are clear at en               | d of slave rece            | ption.             |                |  |  |  |  |

|               | If STREN =             |                                                                                                              | v oply write '1'                      | to rologgo clo                | k) Hardwara a              | lear at beginnin   | a of clavo     |  |  |  |  |

|               | transmission           |                                                                                                              |                                       |                               | sk). Haluwale c            | acar at beginnin   | y of slave     |  |  |  |  |

| bit 11        | IPMIEN: Inte           | elligent Periphe                                                                                             | ral Manageme                          | nt Interface (IF              | MI) Enable bit             |                    |                |  |  |  |  |

|               | 1 = IPMI mo            | de is enabled;                                                                                               | all addresses A                       | Acknowledged                  | ·                          |                    |                |  |  |  |  |

|               | 0 = IPMI mo            | de disabled                                                                                                  |                                       |                               |                            |                    |                |  |  |  |  |

| bit 10        | A10M: 10-B             | it Slave Addres                                                                                              | s bit                                 |                               |                            |                    |                |  |  |  |  |

|               |                        | D is a 10-bit sla<br>D is a 7-bit slav                                                                       |                                       |                               |                            |                    |                |  |  |  |  |

| bit 9         |                        | sable Slew Rat                                                                                               |                                       |                               |                            |                    |                |  |  |  |  |

|               |                        | e control disabl                                                                                             |                                       |                               |                            |                    |                |  |  |  |  |

|               |                        | e control enabl                                                                                              |                                       |                               |                            |                    |                |  |  |  |  |

| bit 8         |                        | Bus Input Level                                                                                              |                                       |                               |                            |                    |                |  |  |  |  |

|               |                        | /O pin threshol<br>SMBus input th                                                                            | ds compliant w<br>iresholds           | ith SMBus spe                 | ecification                |                    |                |  |  |  |  |

| bit 7         | GCEN: Gen              | eral Call Enabl                                                                                              | e bit (when ope                       | erating as I <sup>2</sup> C s | slave)                     |                    |                |  |  |  |  |

|               | 1 = Enable<br>receptio | -                                                                                                            | a general call                        | address is rec                | eived in the I20           | CxRSR (module      | is enabled for |  |  |  |  |

|               |                        | l call address d                                                                                             | isabled                               |                               |                            |                    |                |  |  |  |  |

| bit 6         | STREN: SC              | Lx Clock Streto                                                                                              | h Enable bit (w                       | hen operating                 | as l <sup>2</sup> C slave) |                    |                |  |  |  |  |

|               |                        | unction with th                                                                                              |                                       | . 0                           | ,                          |                    |                |  |  |  |  |

|               |                        |                                                                                                              |                                       |                               |                            |                    |                |  |  |  |  |

|               |                        |                                                                                                              | eive clock strete<br>eive clock stret |                               |                            |                    |                |  |  |  |  |

### 20.3 UART Control Registers

### REGISTER 20-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0                                                                                                                                         | R/W-0                           | R/W-0                          | R/W-0                              | U-0                         | R/W-0             | R/W-0               |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------|------------------------------------|-----------------------------|-------------------|---------------------|--|--|

| UARTEN <sup>(1)</sup> | _                                                                                                                                           | USIDL                           | IREN <sup>(2)</sup>            | RTSMD                              | —                           | UEN               | <1:0>               |  |  |

| bit 15                |                                                                                                                                             |                                 |                                |                                    |                             |                   | bit 8               |  |  |

|                       |                                                                                                                                             |                                 |                                |                                    |                             |                   |                     |  |  |

| R/W-0, HC             | R/W-0                                                                                                                                       | R/W-0, HC                       | R/W-0                          | R/W-0                              | R/W-0                       | R/W-0             | R/W-0               |  |  |

| WAKE                  | LPBACK                                                                                                                                      | ABAUD                           | URXINV                         | BRGH                               | PDSEI                       | _<1:0>            | STSEL               |  |  |

| bit 7                 |                                                                                                                                             |                                 |                                |                                    |                             |                   | bit C               |  |  |

| Legend:               |                                                                                                                                             | HC = Hardwa                     | re Clearable k                 | nit                                |                             |                   |                     |  |  |

| R = Readable          | hit                                                                                                                                         | W = Writable                    |                                |                                    | mented bit, read            | l as '0'          |                     |  |  |

| -n = Value at F       |                                                                                                                                             | '1' = Bit is set                |                                | '0' = Bit is cle                   |                             | x = Bit is unkn   | 0.470               |  |  |

|                       | OR                                                                                                                                          | I - DILIS SEL                   |                                |                                    | aleu                        |                   | OWIT                |  |  |

| bit 15                | UARTEN: UA                                                                                                                                  | RTx Enable bi                   | t(1)                           |                                    |                             |                   |                     |  |  |

|                       | 1 = UARTx is                                                                                                                                | s enabled: all L                | JARTx pins are                 | e controlled by                    | UARTx as defi               | ned by UEN<1:     | 0>                  |  |  |

|                       | 0 = UARTx is                                                                                                                                |                                 |                                |                                    | port latches; L             |                   |                     |  |  |

|                       | minimal                                                                                                                                     |                                 | - 1                            |                                    |                             |                   |                     |  |  |

| bit 14                | •                                                                                                                                           | ted: Read as '                  |                                |                                    |                             |                   |                     |  |  |

| bit 13                | <b>USIDL:</b> Stop in Idle Mode bit<br>1 = Discontinue module operation when device enters Idle mode.                                       |                                 |                                |                                    |                             |                   |                     |  |  |

|                       |                                                                                                                                             |                                 |                                |                                    | dle mode.                   |                   |                     |  |  |

| bit 12                | <ul> <li>0 = Continue module operation in Idle mode</li> <li>IREN: IrDA<sup>®</sup> Encoder and Decoder Enable bit<sup>(2)</sup></li> </ul> |                                 |                                |                                    |                             |                   |                     |  |  |

|                       |                                                                                                                                             | oder and deco                   |                                | e bit                              |                             |                   |                     |  |  |

|                       |                                                                                                                                             | oder and deco                   |                                |                                    |                             |                   |                     |  |  |

| bit 11                | <b>RTSMD:</b> Mode Selection for $\overline{\text{UxRTS}}$ Pin bit                                                                          |                                 |                                |                                    |                             |                   |                     |  |  |

|                       |                                                                                                                                             | in in Simplex n                 |                                |                                    |                             |                   |                     |  |  |

|                       | $0 = \overline{\text{UxRTS}} p$                                                                                                             | in in Flow Con                  | trol mode                      |                                    |                             |                   |                     |  |  |

| bit 10                | Unimplemen                                                                                                                                  | ted: Read as '                  | 0'                             |                                    |                             |                   |                     |  |  |

| bit 9-8               | UEN<1:0>: UARTx Enable bits                                                                                                                 |                                 |                                |                                    |                             |                   |                     |  |  |

|                       |                                                                                                                                             |                                 |                                |                                    | d; UxCTS pin c              | ontrolled by por  | t latches           |  |  |

|                       |                                                                                                                                             | UxRX, UxCTS                     |                                |                                    | d and used<br>ed; UxCTS pin | controlled by pr  | ort latches         |  |  |

|                       |                                                                                                                                             |                                 |                                |                                    | JxRTS/BCLK pi               |                   |                     |  |  |

| bit 7                 | WAKE: Wake                                                                                                                                  | -up on Start bi                 | t Detect Durin                 | g Sleep Mode                       | Enable bit                  | -                 |                     |  |  |

|                       | 1 = UARTx w                                                                                                                                 | vill continue to                | sample the U>                  | RX pin. Interru                    | upt generated o             | n the falling edg | ge; bit cleared     |  |  |

|                       | in hardwa                                                                                                                                   | are on the follo                |                                |                                    |                             |                   |                     |  |  |

|                       | 0 = No wake                                                                                                                                 | •                               |                                |                                    |                             |                   |                     |  |  |

| bit 6                 |                                                                                                                                             | RTx Loopback                    |                                | bit                                |                             |                   |                     |  |  |

|                       |                                                                                                                                             | oopback mode<br>k mode is disal |                                |                                    |                             |                   |                     |  |  |

| bit 5                 | -                                                                                                                                           | p-Baud Enable                   |                                |                                    |                             |                   |                     |  |  |

| DIL D                 |                                                                                                                                             |                                 |                                | e next charact                     | er – requires re            | ception of a Svr  | nc field (0x55)     |  |  |

|                       |                                                                                                                                             |                                 |                                |                                    | -                           |                   |                     |  |  |

|                       | belore of                                                                                                                                   | her data; clear                 | ed in nardwar                  | e upon comple                      |                             |                   |                     |  |  |

|                       |                                                                                                                                             | her data; clear<br>e measuremen |                                |                                    |                             |                   |                     |  |  |

|                       | 0 = Baud rate                                                                                                                               | e measuremen                    | t disabled or o<br>(DS70188) i | completed<br>n the <i>"dsPIC</i> 3 | 33F/PIC24H Fa               | mily Reference    | e <i>Manual"</i> fo |  |  |

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on the UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on the UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters</li> </ul> |

| bit 5   | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                                   |