Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc506a-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX10A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | _       |         | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX08A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | —       | _       | _       | _       | _       | _       | _      | _      | _      |        | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX06A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE  | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       |         | _       | _       | _       | _       | _      | _      | _      | _      | CN21IE  | CN20IE  | _      | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _       | _       | _       | _       | _       | —       | —      | _      | -      | -      | CN21PUE | CN20PUE | _      | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>       | R/W-0 <sup>(1)</sup>                | U-0            | U-0                  | U-0                  | U-0                   | U-0                  |

|-----------------------|----------------------------|-------------------------------------|----------------|----------------------|----------------------|-----------------------|----------------------|

| WR                    | WREN                       | WRERR                               | _              | _                    | _                    |                       |                      |

| bit 15                |                            |                                     |                |                      | •                    |                       | bit                  |

|                       | D 444 o(1)                 |                                     |                | D 444 o(1)           | D # 44 o(1)          | D # 4 ( a ( 1 )       | <b>D</b> (1)         |

| U-0                   | R/W-0 <sup>(1)</sup>       | U-0                                 | U-0            | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup> |

|                       | ERASE                      |                                     | —              |                      | NVMOF                | ><3:0> <sup>(2)</sup> |                      |

| bit 7                 |                            |                                     |                |                      |                      |                       | bit                  |

| Legend:               |                            | SO = Settable                       | e Only bit     |                      |                      |                       |                      |

| R = Readable          | bit                        | W = Writable                        | bit            | U = Unimple          | mented bit, read     | 1 as '0'              |                      |

| -n = Value at F       | POR                        | '1' = Bit is set                    |                | '0' = Bit is cle     | ared                 | x = Bit is unkr       | nown                 |

| bit 15                | WR: Write Co               | ontrol bit                          |                |                      |                      |                       |                      |

|                       |                            |                                     | v program o    | r erase operatio     | on. The operation    | on is self-timed      | and the hit i        |

|                       |                            | by hardware on                      |                |                      |                      |                       |                      |

|                       | 0 = Program                | or erase opera                      | ition is compl | ete and inactive     | е                    |                       |                      |

| bit 14                | WREN: Write                | e Enable bit                        |                |                      |                      |                       |                      |

|                       |                            | lash program/e                      |                |                      |                      |                       |                      |

|                       |                            | ash program/er                      | -              | ns                   |                      |                       |                      |

| bit 13                |                            | ite Sequence E                      | U              |                      |                      |                       |                      |

|                       |                            |                                     |                |                      | r termination ha     | is occurred (bit      | is set               |

|                       |                            | ically on any se<br>gram or erase o | •              | ,                    | 1                    |                       |                      |

| bit 12-7              |                            | nted: Read as '                     | -              |                      | y                    |                       |                      |

| bit 6                 | -                          | se/Program Ena                      |                |                      |                      |                       |                      |

| bit 0                 |                            | -                                   |                | d by NV/MOP<         | 3:0> on the next     | t WR command          | I                    |

|                       |                            |                                     |                |                      | P<3:0> on the n      |                       |                      |

| bit 5-4               |                            | ted: Read as '                      | -              | ,                    |                      |                       |                      |

| bit 3-0               | -                          | >: NVM Operat                       |                | <sub>S</sub> (2)     |                      |                       |                      |

|                       | If ERASE = 1               |                                     |                |                      |                      |                       |                      |

|                       | 1111 <b>= Mem</b>          | ory bulk erase                      | operation      |                      |                      |                       |                      |

|                       | 1110 = Rese                |                                     |                |                      |                      |                       |                      |

|                       |                            | e General Segn<br>e Secure Segm     |                |                      |                      |                       |                      |

|                       | 1011 = Rese                | •                                   | ent            |                      |                      |                       |                      |

|                       | 0011 = No o                |                                     |                |                      |                      |                       |                      |

|                       |                            | ory page erase                      | operation      |                      |                      |                       |                      |

|                       | 0001 = No o                |                                     | <i>.</i>       |                      |                      |                       |                      |

|                       | 0000 = Erase               | e a single Confi                    | guration regis | ster byte            |                      |                       |                      |

|                       | If ERASE = 0               |                                     |                |                      |                      |                       |                      |

|                       | 1111 = No oj               |                                     |                |                      |                      |                       |                      |

|                       | 1110 = Rese                |                                     |                |                      |                      |                       |                      |

|                       | 1101 = No o<br>1100 = No o |                                     |                |                      |                      |                       |                      |

|                       | 1011 = Rese                |                                     |                |                      |                      |                       |                      |

|                       |                            | ory word progra                     | am operation   |                      |                      |                       |                      |

|                       | 0010 = No o                |                                     |                |                      |                      |                       |                      |

|                       |                            | ory row program                     |                | aiotor buto          |                      |                       |                      |

|                       | 0000 = Progi               | ram a single Co                     | miguration re  | egister byte         |                      |                       |                      |

| Note 1: The           | ese bits can onl           | ly be reset on F                    | OR.            |                      |                      |                       |                      |

|                       |                            |                                     |                |                      |                      |                       |                      |

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

2: All other combinations of NVMOP<3:0> are unimplemented.

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | —                            |

| POR (RCON<0>)     | POR                                                  | —                            |

#### TABLE 6-1:RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

#### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

#### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. The System Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| REGISTER 7-12: | IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| R/W-0         | R/W-0           | U-0                                                 | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|-----------------|-----------------------------------------------------|------------------|------------------|------------------|-----------------|---------|

| T6IE          | DMA4IE          |                                                     | OC8IE            | OC7IE            | OC6IE            | OC5IE           | IC6IE   |

| bit 15        |                 | ·                                                   |                  |                  |                  |                 | bit 8   |

| R/W-0         | R/W-0           | R/W-0                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IE         | IC4IE           | IC3IE                                               | DMA3IE           | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |

| bit 7         | 1               |                                                     |                  |                  |                  |                 | bit 0   |

| Legend:       |                 |                                                     |                  |                  |                  |                 |         |

| R = Readable  | e bit           | W = Writable                                        | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                                    |                  | '0' = Bit is cle | eared            | x = Bit is unki | nown    |

| bit 15        | T6IF: Timer6    | Interrupt Enabl                                     | e bit            |                  |                  |                 |         |

|               |                 | request enabled                                     |                  |                  |                  |                 |         |

|               |                 | equest not ena                                      |                  |                  |                  |                 |         |

| bit 14        |                 | A Channel 4 D                                       |                  | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | request enableo<br>request not ena                  |                  |                  |                  |                 |         |

| bit 13        |                 | ted: Read as '                                      |                  |                  |                  |                 |         |

| bit 12        | -               | ut Compare Ch                                       |                  | unt Enable bit   |                  |                 |         |

| 51(12         | •               | request enabled                                     |                  |                  |                  |                 |         |

|               |                 | equest not ena                                      |                  |                  |                  |                 |         |

| bit 11        | •               | ut Compare Ch                                       |                  | upt Enable bit   |                  |                 |         |

|               |                 | request enabled<br>request not ena                  |                  |                  |                  |                 |         |

| bit 10        | •               | ut Compare Ch                                       |                  | upt Enable bit   |                  |                 |         |

|               | 1 = Interrupt r | request enabled                                     | b                |                  |                  |                 |         |

|               | •               | request not ena                                     |                  |                  |                  |                 |         |

| bit 9         | 1 = Interrupt r | ut Compare Ch<br>request enableo<br>request not ena | b                | upt Enable bit   |                  |                 |         |

| bit 8         |                 | Capture Channe                                      |                  | Enable bit       |                  |                 |         |

|               | 1 = Interrupt r | request enable<br>request not ena                   | d                |                  |                  |                 |         |

| bit 7         | IC5IE: Input C  | Capture Channe                                      | el 5 Interrupt I | Enable bit       |                  |                 |         |

|               |                 | request enable<br>request not ena                   |                  |                  |                  |                 |         |

| bit 6         | IC4IE: Input C  | Capture Channe                                      | el 4 Interrupt I | Enable bit       |                  |                 |         |

|               |                 | request enableo<br>request not ena                  |                  |                  |                  |                 |         |

| bit 5         | •               | Capture Channe                                      |                  | Enable bit       |                  |                 |         |

|               | 1 = Interrupt r | request enabled<br>request not ena                  | d                |                  |                  |                 |         |

| bit 4         | DMA3IE: DM      | A Channel 3 D                                       | ata Transfer C   | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | request enabled<br>request not ena                  |                  |                  |                  |                 |         |

| bit 3         | -               | Event Interrup                                      |                  |                  |                  |                 |         |

|               |                 | equest enable                                       |                  |                  |                  |                 |         |

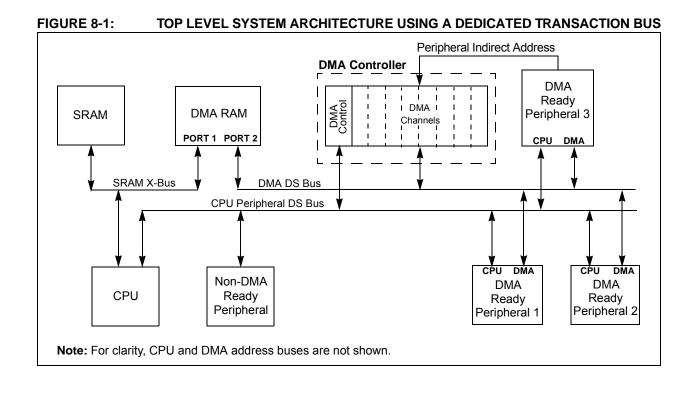

#### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | <b>XWCOL3:</b> Channel 3 DMA RAM Write Collision Flag bit<br>1 = Write collision detected                             |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| bit 2 | <ul> <li>0 = No write collision detected</li> <li>XWCOL2: Channel 2 DMA RAM Write Collision Flag bit</li> </ul>       |

|       | <ul> <li>1 = Write collision detected</li> <li>0 = No write collision detected</li> </ul>                             |

| bit 1 | XWCOL1: Channel 1 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected |

| R/W-0         | R/W-0                      | R/W-0                                 | R/W-0   | R/W-0            | R/W-0            | R/W-0           | U-0                  |

|---------------|----------------------------|---------------------------------------|---------|------------------|------------------|-----------------|----------------------|

| T5MD          | T4MD                       | T3MD                                  | T2MD    | T1MD             | QEI1MD           | PWMMD           | —                    |

| bit 15        |                            | •                                     | L       |                  |                  |                 | bit 8                |

|               |                            |                                       |         |                  |                  |                 |                      |

| R/W-0         | R/W-0                      | R/W-0                                 | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0                |

| I2C1MD        | U2MD                       | U1MD                                  | SPI2MD  | SPI1MD           | C2MD             | C1MD            | AD1MD <sup>(1)</sup> |

| bit 7         |                            |                                       |         |                  |                  |                 | bit C                |

|               |                            |                                       |         |                  |                  |                 |                      |

| Legend:       |                            |                                       |         |                  |                  |                 |                      |

| R = Readabl   |                            | W = Writable                          | bit     |                  | nented bit, read |                 |                      |

| -n = Value at | POR                        | '1' = Bit is set                      |         | '0' = Bit is cle | ared             | x = Bit is unkr | lown                 |

| L:4 / F       |                            | - Madula Diach                        | I- 1-14 |                  |                  |                 |                      |

| bit 15        |                            | 5 Module Disat<br>odule is disable    |         |                  |                  |                 |                      |

|               |                            | odule is enable                       |         |                  |                  |                 |                      |

| bit 14        |                            | 4 Module Disat                        |         |                  |                  |                 |                      |

|               | 1 = Timer4 m               | odule is disable                      | ed      |                  |                  |                 |                      |

|               | 0 = Timer4 m               | odule is enable                       | d       |                  |                  |                 |                      |

| bit 13        |                            | 3 Module Disab                        |         |                  |                  |                 |                      |

|               |                            | odule is disable                      |         |                  |                  |                 |                      |

| bit 10        |                            | odule is enable<br>2 Module Disat     |         |                  |                  |                 |                      |

| bit 12        | -                          | odule is disable                      |         |                  |                  |                 |                      |

|               | -                          | odule is enable                       |         |                  |                  |                 |                      |

| bit 11        | T1MD: Timer                | 1 Module Disab                        | ole bit |                  |                  |                 |                      |

|               | 1 = Timer1 m               | odule is disable                      | ed      |                  |                  |                 |                      |

|               | 0 = Timer1 m               | odule is enable                       | d       |                  |                  |                 |                      |

| bit 10        |                            | 11 Module Disa                        | ble bit |                  |                  |                 |                      |

|               |                            | dule is disabled<br>dule is enabled   |         |                  |                  |                 |                      |

| bit 9         |                            | /M Module Disa                        | hle hit |                  |                  |                 |                      |

| bit 5         |                            | dule is disabled                      |         |                  |                  |                 |                      |

|               |                            | dule is enabled                       |         |                  |                  |                 |                      |

| bit 8         | Unimplemen                 | ted: Read as '                        | )'      |                  |                  |                 |                      |

| bit 7         | 12C1MD: 12C                | 1 Module Disab                        | ole bit |                  |                  |                 |                      |

|               |                            | lule is disabled                      |         |                  |                  |                 |                      |

|               |                            | lule is enabled                       |         |                  |                  |                 |                      |

| bit 6         |                            | 2 Module Disa                         |         |                  |                  |                 |                      |

|               |                            | nodule is disable<br>nodule is enable |         |                  |                  |                 |                      |

| bit 5         |                            | 1 Module Disa                         |         |                  |                  |                 |                      |

|               | 1 = UART1 m                | nodule is disable                     | ed      |                  |                  |                 |                      |

|               | 0 = UART1 m                | nodule is enable                      | ed      |                  |                  |                 |                      |

| bit 4         | SPI2MD: SPI                | 2 Module Disat                        | ole bit |                  |                  |                 |                      |

|               |                            | lule is disabled                      |         |                  |                  |                 |                      |

|               | $0 = SPI2 \mod 10^{\circ}$ | dule is enabled                       |         |                  |                  |                 |                      |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** The PCFGx bits have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

NOTES:

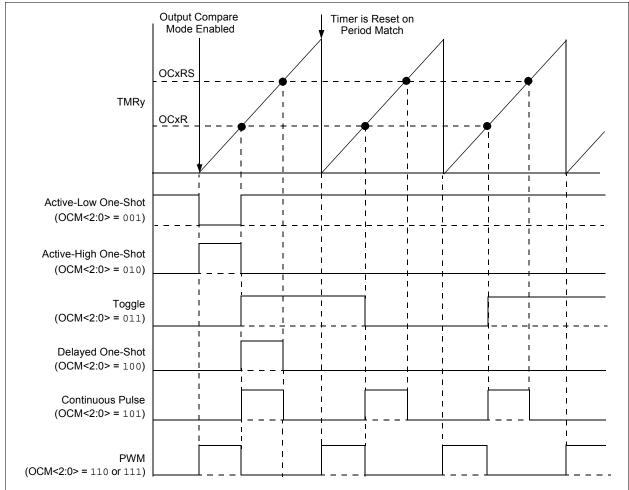

### 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode bits (OCM<2:0>) in the Output Compare Control register (OCxCON<2:0>). Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

| Note: | See Section 13. "Output Compare"      |

|-------|---------------------------------------|

|       | (DS70209) in the "dsPIC33F/PIC24H     |

|       | Family Reference Manual" for OCxR and |

|       | OCxRS register restrictions.          |

| OCM<2:0> | Mode OCx Pin Initial State   |                                                                        | OCx Interrupt Generation         |

|----------|------------------------------|------------------------------------------------------------------------|----------------------------------|

| 000      | Module Disabled              | Controlled by GPIO register                                            | _                                |

| 001      | Active-Low One-Shot 0        |                                                                        | OCx rising edge                  |

| 010      | Active-High One-Shot         | 1                                                                      | OCx falling edge                 |

| 011      | Toggle                       | Current output is maintained                                           | OCx rising and falling edge      |

| 100      | Delayed One-Shot             | 0                                                                      | OCx falling edge                 |

| 101      | Continuous Pulse             | 0                                                                      | OCx falling edge                 |

| 110      | PWM without Fault Protection | <ul><li>'0' if OCxR is zero,</li><li>'1' if OCxR is non-zero</li></ul> | No interrupt                     |

| 111      | PWM with Fault Protection    | <ul><li>'0' if OCxR is zero,</li><li>'1' if OCxR is non-zero</li></ul> | OCFA falling edge for OC1 to OC4 |

#### FIGURE 15-2: OUTPUT COMPARE OPERATION

#### REGISTER 21-2: CiCTRL2: ECAN™ CONTROL REGISTER 2

| U-0             | U-0                | U-0                                | U-0             | U-0                                | U-0        | U-0                | U-0   |  |  |

|-----------------|--------------------|------------------------------------|-----------------|------------------------------------|------------|--------------------|-------|--|--|

| —               | —                  | —                                  | _               | —                                  | —          | —                  | —     |  |  |

| bit 15          |                    |                                    |                 |                                    |            | bit 8              |       |  |  |

|                 |                    |                                    |                 |                                    |            |                    |       |  |  |

| U-0             | U-0                | U-0                                | R-0             | R-0                                | R-0        | R-0                | R-0   |  |  |

| —               | —                  | —                                  |                 |                                    | DNCNT<4:0> |                    |       |  |  |

| bit 7           |                    |                                    |                 |                                    |            |                    | bit 0 |  |  |

|                 |                    |                                    |                 |                                    |            |                    |       |  |  |

| Legend:         |                    |                                    |                 |                                    |            |                    |       |  |  |

| R = Readable    | e bit              | W = Writable                       | bit             | U = Unimplemented bit, read as '0' |            |                    |       |  |  |

| -n = Value at I | POR                | '1' = Bit is set                   |                 | '0' = Bit is cle                   | ared       | x = Bit is unknown |       |  |  |

|                 |                    |                                    |                 |                                    |            |                    |       |  |  |

| bit 15-5        | Unimplemen         | ted: Read as '                     | )'              |                                    |            |                    |       |  |  |

| bit 4-0         | DNCNT<4:0>         | •: DeviceNet™                      | Filter Bit Num  | ber bits                           |            |                    |       |  |  |

|                 | 10010-1111         | 1 = Invalid sele                   | ection          |                                    |            |                    |       |  |  |

|                 | 10001 <b>= Con</b> | npare up to data                   | a byte 3, bit 6 | with EID<17>                       |            |                    |       |  |  |

|                 | •                  |                                    |                 |                                    |            |                    |       |  |  |

|                 | •                  |                                    |                 |                                    |            |                    |       |  |  |

|                 | •                  |                                    |                 |                                    |            |                    |       |  |  |

|                 |                    | npare up to data<br>not compare da |                 | with EID<0>                        |            |                    |       |  |  |

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                             |

|-----------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0>  | FSS      | Immediate      | Secure Segment Program Flash Code Protection Size bits                                                                                  |

|           |          |                | (FOR 128K and 256K DEVICES)                                                                                                             |

|           |          |                | x11 = No secure program Flash segment                                                                                                   |

|           |          |                | <u>Secure space is 8K IW less BS:</u><br>110 = Standard security; secure program Flash segment starts at end of<br>BS, ends at 0x003FFE |

|           |          |                | 010 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x003FFE                                              |

|           |          |                | Secure space is 16K IW less BS:                                                                                                         |

|           |          |                | 101 = Standard security; secure program Flash segment starts at end of BS, ends at 0x007FFE                                             |

|           |          |                | 001 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x007FFE                                              |

|           |          |                | Secure space is 32K IW less BS:                                                                                                         |

|           |          |                | 100 = Standard security; secure program Flash segment starts at end of<br>BS, ends at 0x00FFFE                                          |

|           |          |                | 000 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x00FFFE                                              |

|           |          |                | (FOR 64K DEVICES)                                                                                                                       |

|           |          |                | x11 = No Secure program Flash segment                                                                                                   |

|           |          |                | Secure space is 4K IW less BS:<br>110 = Standard security; secure program Flash segment starts at end of                                |

|           |          |                | BS, ends at 0x001FFE<br>010 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x001FFE                      |

|           |          |                | Secure space is 8K IW less BS:<br>101 = Standard security; secure program Flash segment starts at end of                                |

|           |          |                | BS, ends at 0x003FFE                                                                                                                    |

|           |          |                | 001 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x003FFE                                              |

|           |          |                | Secure space is 16K IW less BS:                                                                                                         |

|           |          |                | 100 = Standard security; secure program Flash segment starts at end of BS, ends at 007FFEh                                              |

|           |          |                | 000 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x007FFE                                              |

| RSS<1:0>  | FSS      | Immediate      | Secure Segment RAM Code Protection bits<br>11 = No secure RAM defined                                                                   |

|           |          |                | 10 = Secure RAM is 256 bytes less BS RAM                                                                                                |

|           |          |                | 01 = Secure RAM is 2048 bytes less BS RAM<br>00 = Secure RAM is 4096 bytes less BS RAM                                                  |

| GSS<1:0>  | FGS      | Immediate      | General Segment Code-Protect bits<br>11 = User program memory is not code-protected                                                     |

|           |          |                | <ul> <li>10 = Standard security; general program Flash segment starts at end of<br/>SS, ends at EOM</li> </ul>                          |

|           |          |                | 0x = High security; general program Flash segment starts at end of SS,<br>ends at EOM                                                   |

#### TABLE 23-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

## 25.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 25.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 25.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 25.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# FIGURE 26-26: CAN MODULE I/O TIMING CHARACTERISTICS

#### TABLE 26-42: ECAN™ TECHNOLOGY MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                                        |                               | (unless | d Operation<br>otherwise<br>ng temper | se stated | )<br>-40°C ≤ | <b>3.0V to 3.6V</b><br>$F_A \le +85^{\circ}C$ for Industrial<br>$F_A \le +125^{\circ}C$ for Extended |

|--------------------|--------------------------------------------------------|-------------------------------|---------|---------------------------------------|-----------|--------------|------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol                                                 | Characteristic <sup>(1)</sup> | Min     | n Typ Max                             |           | Units        | Conditions                                                                                           |

| CA10               | TioF                                                   | Port Output Fall Time         |         | _                                     | _         | ns           | See parameter D032                                                                                   |

| CA11               | TioR                                                   | Port Output Rise Time         | —       | _                                     | _         | ns           | See parameter D031                                                                                   |

| CA20               | CA20 Tcwf Pulse Width to Trigger<br>CAN Wake-up Filter |                               |         | _                                     |           | ns           | —                                                                                                    |

**Note 1:** These parameters are characterized but not tested in manufacturing.

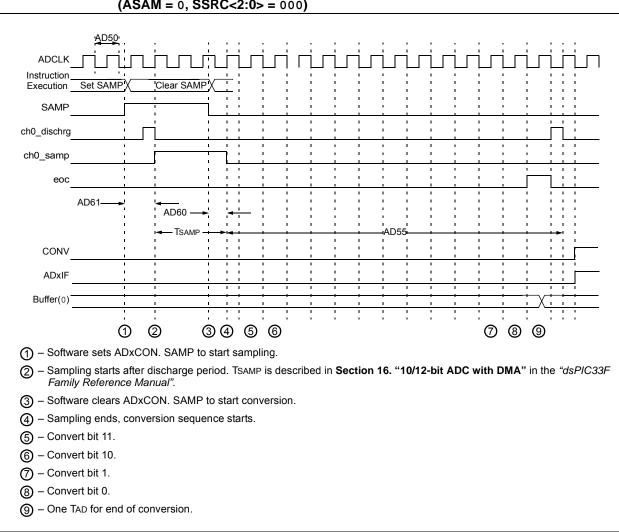

#### FIGURE 26-27: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

## 27.0 HIGH TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJXXXMCX06A/X08A/X10A electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 26.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter DC10 in **Section 26.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33FJXXXMCX06A/X08A/X10A high temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(4)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(5)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(5)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\geq 3.0 V^{(5)}$    | 0.3V to 5.6V         |

| Voltage on VCAP with respect to Vss                                               | 2.25V to 2.75V       |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(2)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      |                      |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 2 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 4 mA                 |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sunk by all ports combined                                        | 10 mA                |

| Maximum current sourced by all ports combined <sup>(2)</sup>                      | 10 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 27-2).

- **3:** Unlike devices at 125°C and below, the specifications in this section also apply to the CLKOUT, VREF+, VREF-, SCLx, SDAx, PGECx, and PGEDx pins.

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Refer to the "Pin Diagrams" section for 5V tolerant pins.

#### 27.1 High Temperature DC Characteristics

#### TABLE 27-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                   | Temperature Range | Max MIPS                     |

|----------------|-----------------------------|-------------------|------------------------------|

| Characteristic | (in Volts)                  | (in °C)           | dsPIC33FJXXXMCX06A/X08A/X10A |

| HDC5           | VBOR to 3.6V <sup>(1)</sup> | -40°C to +150°C   | 20                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 26-11 for the minimum and maximum BOR values.

#### TABLE 27-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40 | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40 | _           | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | I   | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (   | TJ - TA)/θJ | A    | W    |

#### TABLE 27-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARA         | CTERISTIC | ERISTICS (unless otherwise sta |                               |  |  | pnditions: 3.0V to 3.6V<br>ed)<br>-40°C $\leq$ TA $\leq$ +150°C for High Temperature |  |  |  |

|------------------|-----------|--------------------------------|-------------------------------|--|--|--------------------------------------------------------------------------------------|--|--|--|

| Parameter<br>No. | Symbol    | Characteristic                 | Min Typ Max Units Conditions  |  |  |                                                                                      |  |  |  |

| Operating V      | Voltage   |                                |                               |  |  |                                                                                      |  |  |  |

| HDC10            | Supply Vo | Itage                          |                               |  |  |                                                                                      |  |  |  |

|                  | Vdd       |                                | 3.0 3.3 3.6 V -40°C to +150°C |  |  |                                                                                      |  |  |  |

#### TABLE 27-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARAC                                                                                                     | TERISTICS     |      | (unless oth | perating Co<br>erwise state<br>emperature            | ed) | <b>0V to 3.6V</b><br>≤ +150°C for High Temperature |  |  |

|---------------------------------------------------------------------------------------------------------------|---------------|------|-------------|------------------------------------------------------|-----|----------------------------------------------------|--|--|

| Parameter<br>No.                                                                                              | Typical       | Мах  | Units       | Conditions                                           |     |                                                    |  |  |

| Power-Down                                                                                                    | Current (IPD) |      |             |                                                      |     |                                                    |  |  |

| HDC60e                                                                                                        | 250           | 2000 | μA          | +150°C 3.3V Base Power-Down Current <sup>(1,3)</sup> |     |                                                    |  |  |

| Note 1. Base IPD is measured with all perinherals and clocks shut down. All I/Os are configured as inputs and |               |      |             |                                                      |     |                                                    |  |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

| AC<br>CHARACTERISTICSStandard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |        |                                 |           |      |     | 2     |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------|-----------|------|-----|-------|------------|

| Param<br>No.                                                                                                                                                                 | Symbol | Characteristic                  | Min       | Тур  | Max | Units | Conditions |

|                                                                                                                                                                              |        | Clock                           | A Parame  | ters |     |       |            |

| HAD50                                                                                                                                                                        | TAD    | ADC Clock Period <sup>(1)</sup> | 147       |      | _   | ns    |            |

| TIAD 50                                                                                                                                                                      | IAD    |                                 | 177       |      |     | 113   |            |

| TIAD 30                                                                                                                                                                      | IAD    |                                 | version R | ate  |     | 113   |            |

#### TABLE 27-17: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 27-18: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| -            | AC<br>TERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |          |      |     |       |            |  |  |  |

|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-----|-------|------------|--|--|--|

| Param<br>No. | Symbol          | Characteristic                                                                                                                                           | Min      | Тур  | Max | Units | Conditions |  |  |  |

|              |                 | Cloc                                                                                                                                                     | k Parame | ters |     |       |            |  |  |  |

| HAD50        | Tad             | ADC Clock Period <sup>(1)</sup>                                                                                                                          | 104      | _    |     | ns    | _          |  |  |  |

|              | Conversion Rate |                                                                                                                                                          |          |      |     |       |            |  |  |  |

| HAD56        | FCNV            | / Throughput Rate <sup>(1)</sup> — — 800 Ksps —                                                                                                          |          |      |     |       |            |  |  |  |

| N            |                 |                                                                                                                                                          |          |      |     |       |            |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

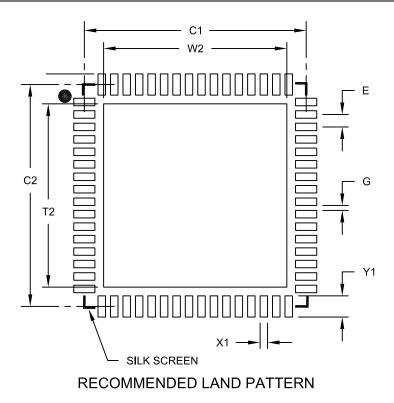

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length

|                            | MILLIMETERS      |      |      |      |

|----------------------------|------------------|------|------|------|

| Dimensior                  | Dimension Limits |      |      | MAX  |

| Contact Pitch              | Contact Pitch E  |      |      |      |

| Optional Center Pad Width  | W2               |      |      | 7.35 |

| Optional Center Pad Length | T2               |      |      | 7.35 |

| Contact Pad Spacing        | C1               |      | 8.90 |      |

| Contact Pad Spacing        | C2               |      | 8.90 |      |

| Contact Pad Width (X64)    | X1               |      |      | 0.30 |

| Contact Pad Length (X64)   | Y1               |      |      | 0.85 |

| Distance Between Pads      | G                | 0.20 |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2149A

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-62076-343-8

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.