Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betano                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 69                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-TQFP                                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc508a-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3 Special MCU Features

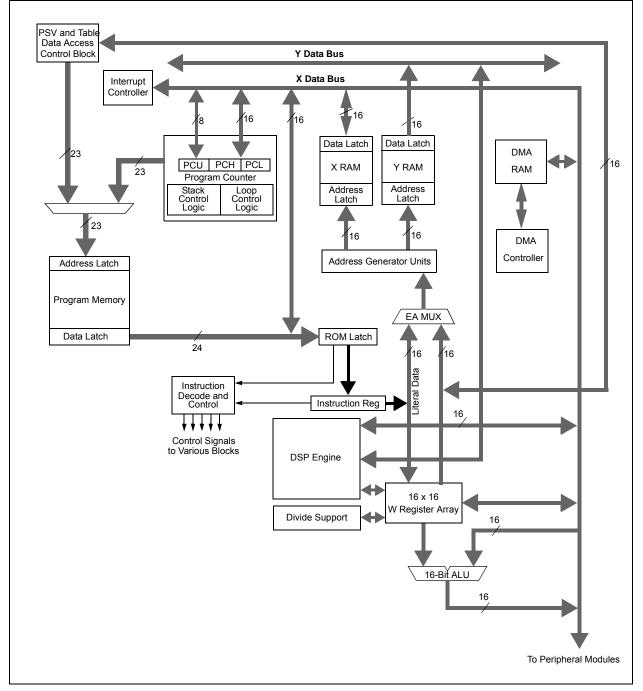

The dsPIC33FJXXXMCX06A/X08A/X10A devices feature a 17-bit by 17-bit, single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJXXXMCX06A/X08A/X10A devices support 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without a loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

#### FIGURE 3-1: dsPIC33FJXXXMCX06A/X08A/X10A CPU CORE BLOCK DIAGRAM

#### 4.2 Data Address Space

The dsPIC33FJXXXMCX06A/X08A/X10A CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 through Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJXXXMCX06A/X08A/X10A devices implement a total of up to 30 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes of each word have even addresses, while the Most Significant Bytes have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> microcontrollers and improve data space memory usage efficiency, the dsPIC33FJXXXMCX06A/X08A/X10A instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSb of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSb of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJXXXMCX06A/X08A/X10A core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Please refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

#### TABLE 4-9: 8-OUTPUT PWM REGISTER MAP

| SFR Name  | Addr. | Bit 15  | Bit 14                     | Bit 13                           | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8                  | Bit 7               | Bit 6      | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0               | Reset State         |

|-----------|-------|---------|----------------------------|----------------------------------|--------|--------|--------|---------|------------------------|---------------------|------------|---------------------|---------------------|--------|--------|--------|---------------------|---------------------|

| P1TCON    | 01C0  | PTEN    | - PTSIDL                   |                                  |        |        |        | _       | PTOPS<3:0> PTCKPS<1:0> |                     |            |                     |                     |        | PTMO   | D<1:0> | 0000 0000 0000 0000 |                     |

| P1TMR     | 01C2  | PTDIR   |                            | PWM Timer Count Value Register 0 |        |        |        |         |                        |                     |            |                     | 0000 0000 0000 0000 |        |        |        |                     |                     |

| P1TPER    | 01C4  | _       |                            |                                  |        |        |        | F       | PWM Time               | Base Perio          | od Registe | r                   |                     |        |        |        |                     | 0000 0000 0000 0000 |

| P1SECMP   | 01C6  | SEVTDIR |                            |                                  |        |        |        | PW      | M Special              | Event Corr          | pare Regi  | ster                |                     |        |        |        |                     | 0000 0000 0000 0000 |

| PWM1CON1  | 01C8  |         | _                          | _                                | _      | PMOD4  | PMOD3  | PMOD2   | PMOD1                  | PEN4H               | PEN3H      | PEN2H               | PEN1H               | PEN4L  | PEN3L  | PEN2L  | PEN1L               | 0000 0000 1111 1111 |

| PWM1CON2  | 01CA  |         | _                          | _                                | _      |        | SEVOP  | °S<3:0> |                        | -                   | _          | _                   | _                   | _      | IUE    | OSYNC  | UDIS                | 0000 0000 0000 0000 |

| P1DTCON1  | 01CC  | DTBPS   | 6<1:0>                     |                                  |        | DTB<   | <5:0>  |         |                        | DTAPS<1:0> DTA<5:0> |            |                     |                     |        | <5:0>  |        |                     | 0000 0000 0000 0000 |

| P1DTCON2  | 01CE  |         | _                          | _                                | _      | _      | _      | _       | _                      | DTS4A               | DTS4I      | DTS3A               | DTS3I               | DTS2A  | DTS2I  | DTS1A  | DTS1I               | 0000 0000 0000 0000 |

| P1FLTACON | 01D0  | FAOV4H  | FAOV4L                     | FAOV3H                           | FAOV3L | FAOV2H | FAOV2L | FAOV1H  | FAOV1L                 | FLTAM               | _          | _                   | _                   | FAEN4  | FAEN3  | FAEN2  | FAEN1               | 0000 0000 0000 0000 |

| P1FLTBCON | 01D2  | FBOV4H  | FBOV4L                     | FBOV3H                           | FBOV3L | FBOV2H | FBOV2L | FBOV1H  | FBOV1L                 | FLTBM               | _          | _                   | _                   | FBEN4  | FBEN3  | FBEN2  | FBEN1               | 0000 0000 0000 0000 |

| P10VDCON  | 01D4  | POVD4H  | POVD4L                     | POVD3H                           | POVD3L | POVD2H | POVD2L | POVD1H  | POVD1L                 | POUT4H              | POUT4L     | POUT3H              | POUT3L              | POUT2H | POUT2L | POUT1H | POUT1L              | 1111 1111 0000 0000 |

| P1DC1     | 01D6  |         |                            |                                  |        |        |        | PW      | /I Duty Cyc            | le #1 Regis         | ster       |                     |                     |        |        |        |                     | 0000 0000 0000 0000 |

| P1DC2     | 01D8  |         | PWM Duty Cycle #2 Register |                                  |        |        |        |         |                        |                     |            |                     | 0000 0000 0000 0000 |        |        |        |                     |                     |

| P1DC3     | 01DA  |         | PWM Duty Cycle #3 Register |                                  |        |        |        |         |                        |                     |            |                     | 0000 0000 0000 0000 |        |        |        |                     |                     |

| P1DC4     | 01DC  |         | PWM Duty Cycle #4 Register |                                  |        |        |        |         |                        |                     |            | 0000 0000 0000 0000 |                     |        |        |        |                     |                     |

Legend: u = uninitialized bit, - = unimplemented, read as '0'

#### TABLE 4-10: QEI REGISTER MAP

| SFR<br>Name    | Addr | Bit 15 | Bit 14                 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                           | Bit 8 | Bit 7 | Bit 6  | Bit 5    | Bit 4    | Bit 3  | Bit 2    | Bit 1  | Bit 0    |      | Reset State | e      |

|----------------|------|--------|------------------------|---------|--------|--------|--------|---------------------------------|-------|-------|--------|----------|----------|--------|----------|--------|----------|------|-------------|--------|

| <b>QEI1CON</b> | 01E0 | CNTERR | —                      | QEISIDL | INDX   | UPDN   | Q      | EIM<2:0                         | )>    | SWPAB | PCDOUT | TQGATE   | TQCKP    | S<1:0> | POSRES   | TQCS   | UPDN_SRC | 0000 | 0000 000    | 0 0000 |

| DFLT1CON       | 01E2 | _      | —                      | _       | _      | _      | IMV<   | IMV<1:0> CEID QEOUT QECK<2:0> 0 |       |       |        |          |          | 0000   | 0000 000 | 0 0000 |          |      |             |        |

| POS1CNT        | 01E4 |        | Position Counter<15:0> |         |        |        |        |                                 |       |       |        | 0000     | 0000 000 | 0 0000 |          |        |          |      |             |        |

| MAX1CNT        | 01E6 |        | Maximum Count<15:0>    |         |        |        |        |                                 |       |       | 1111   | 1111 111 | 1 1111   |        |          |        |          |      |             |        |

Legend: u = uninitialized bit, — = unimplemented, read as '0'

#### TABLE 4-11: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                 | Bit 7                        | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-----------------------|------------------------------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       |        | _       |        |        | _      |        | I2C1 Receive Register |                              |       |            |             |              |       |       | 0000  |               |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | _                     |                              |       |            | I2C1 Trans  | mit Register |       |       |       | OOFF          |

| I2C1BRG  | 0204        | —       | _      | _       | -      |        | —      | —      |                       | Baud Rate Generator Register |       |            |             |              |       | 0000  |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                  | GCEN                         | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                 | IWCOL                        | I2COV | D_A        | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |                       |                              |       | I2C1 Addre | ss Register |              |       |       |       | 0000          |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      | —      |        |                       |                              | 120   | 1 Address  | Mask Regis  | ster         |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7                        | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|------------------------------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        | —       | -      | —       | —      | —      | —      | —      | —     | I2C2 Receive Register        |       |            |             |              |       |       |       | 0000          |

| I2C2TRN  | 0212        | _       | _      | _       | _      | _      | _      | _      | _     |                              |       |            | I2C2 Transı | nit Register |       |       |       | OOFF          |

| I2C2BRG  | 0214        | _       | _      | _       | _      | _      | _      | _      |       | Baud Rate Generator Register |       |            |             |              |       | 0000  |       |               |

| I2C2CON  | 0216        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN                         | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL                        | I2COV | D_A        | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        | _       | _      | _       | _      | _      | _      |        |       |                              |       | I2C2 Addre | ss Register |              |       |       |       | 0000          |

| I2C2MSK  | 021C        | —       |        |         | —      | -      |        |        |       |                              | 120   | 2 Address  | Mask Regis  | ter          |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1

| File Name  | Addr          | Bit 15             | Bit 14 | Bit 13                 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7                                                         | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------------------|--------|------------------------|--------|--------|--------|--------|------------|---------------------------------------------------------------|----------|--------|-------|-------|-----------|--------|--------|---------------|

|            | 0400-<br>041E |                    |        |                        |        |        |        |        | See defini | tion when V                                                   | WIN = x  |        |       |       |           |        |        |               |

| C1BUFPNT1  | 0420          |                    | F3BF   | <b>2</b> <3:0>         |        |        | F2BF   | P<3:0> |            |                                                               | F1BP     | <3:0>  |       |       | F0BP      | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |                    | F7BF   | °<3:0>                 |        |        | F6BF   | P<3:0> |            |                                                               | F5BP     | <3:0>  |       |       | F4BP<3:0> |        |        |               |

| C1BUFPNT3  | 0424          |                    | F11B   | D<3:0>                 |        |        | F10B   | P<3:0> |            | F9BP<3:0> F8BP<3:0>                                           |          |        |       |       |           |        |        | 0000          |

| C1BUFPNT4  | 0426          |                    | F15BI  | <b>&gt;&lt;3:0&gt;</b> |        |        | F14B   | P<3:0> |            |                                                               | F13BF    | P<3:0> |       |       | F12BF     | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | MIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |                    |        |                        | EID<   | :15:8> |        |        |            |                                                               |          |        | EID<  | 7:0>  |           |        |        | xxxx          |

| C1RXM1SID  | 0434          |                    |        |                        | SID<   | :10:3> |        |        |            | SID<2:0> — MIDE — EID<17:16>                                  |          |        |       |       |           |        |        |               |

| C1RXM1EID  | 0436          |                    |        |                        | EID<   | :15:8> |        |        |            | EID<7:0>                                                      |          |        |       |       |           |        |        |               |

| C1RXM2SID  | 0438          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | MIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |                    |        |                        | EID<   | :15:8> |        |        |            |                                                               |          |        | EID<  | 7:0>  |           |        |        | xxxx          |

| C1RXF0SID  | 0440          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | EXIDE | —         | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          | EID<15:8> EID<7:0> |        |                        |        |        |        |        |            |                                                               |          |        | xxxx  |       |           |        |        |               |

| C1RXF1SID  | 0444          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | EXIDE | —         | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |                    |        |                        | EID<   | :15:8> |        |        |            |                                                               |          |        | EID<  | 7:0>  |           |        |        | xxxx          |

| C1RXF2SID  | 0448          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | EXIDE | —         | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |                    |        |                        | EID<   | :15:8> |        |        |            | EID<7:0>                                                      |          |        |       |       |           |        |        | xxxx          |

| C1RXF3SID  | 044C          |                    |        |                        | SID<   | :10:3> |        |        |            | SID<2:0> — EXIDE — EID<17:16>                                 |          |        |       |       |           |        | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |                    |        |                        | EID<   | :15:8> |        |        |            | EID<7:0>                                                      |          |        |       |       |           |        |        | xxxx          |

| C1RXF4SID  | 0450          |                    |        |                        | SID<   | :10:3> |        |        |            | SID<2:0> — EXIDE — EID<17:16>                                 |          |        |       |       |           |        |        | xxxx          |

| C1RXF4EID  | 0452          |                    |        |                        | EID<   | :15:8> |        |        |            |                                                               |          |        | EID<  | 7:0>  |           |        |        | xxxx          |

| C1RXF5SID  | 0454          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | EXIDE | —         | EID<   | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |                    |        |                        | EID<   | :15:8> |        |        |            |                                                               |          |        | EID<  | 7:0>  |           |        |        | xxxx          |

| C1RXF6SID  | 0458          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | EXIDE | —         | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |                    |        |                        | EID<   | :15:8> |        |        |            |                                                               |          |        | EID<  | 7:0>  |           |        |        | xxxx          |

| C1RXF7SID  | 045C          |                    |        |                        | SID<   | :10:3> |        |        |            |                                                               | SID<2:0> |        | —     | EXIDE | —         | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |                    |        |                        | EID<   | :15:8> |        |        |            | EID<7:0>                                                      |          |        |       |       |           |        |        | xxxx          |

| C1RXF8SID  | 0460          |                    |        |                        | SID<   | :10:3> |        |        |            | SID<2:0> — EXIDE — EID<17:16>                                 |          |        |       |       |           |        | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |                    |        |                        | EID<   | :15:8> |        |        |            | EID<7:0>                                                      |          |        |       |       |           |        |        | xxxx          |

| C1RXF9SID  | 0464          |                    |        |                        | SID<   | :10:3> |        |        |            | SID<2:0>         —         EXIDE         —         EID<17:16> |          |        |       |       |           |        | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |                    |        |                        | EID<   | :15:8> |        |        |            | EID<7:0>                                                      |          |        |       |       |           |        |        | xxxx          |

| C1RXF10SID | 0468          |                    |        |                        | SID<   | :10:3> |        |        |            | SID<2:0> — EXIDE — EID<17:16>                                 |          |        |       |       |           |        | 17:16> | xxxx          |

| C1RXF10EID | 046A          | EID<15:8>          |        |                        |        |        |        |        |            |                                                               | EID<7:0> |        |       |       |           |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-36: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing     |

|-------|----------------------------------------------|

|       | mode specified in the instruction can differ |

|       | for the source and destination EA.           |

|       | However, the 4-bit Wb (register offset)      |

|       | field is shared between both source and      |

|       | destination (but typically only used by      |

|       | one).                                        |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the Data Pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 will always be directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9, and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Set up NVMCO | N for row programming operations | 3     |                                       |

|----------------|----------------------------------|-------|---------------------------------------|

| MOV            | #0x4001, W0                      | ;     |                                       |

| MOV            | W0, NVMCON                       | ;     | Initialize NVMCON                     |

| ; Set up a poi | nter to the first program memory | / loc | ation to be written                   |

| ; program memo | ry selected, and writes enabled  |       |                                       |

| MOV            | #0x0000, W0                      | ;     |                                       |

| MOV            | W0, TBLPAG                       | ;     | Initialize PM Page Boundary SFR       |

| MOV            | #0x6000, W0                      | ;     | An example program memory address     |

| ; Perform the  | TBLWT instructions to write the  | latc  | hes                                   |

| ; 0th_program_ | word                             |       |                                       |

| MOV            | #LOW_WORD_0, W2                  | ;     |                                       |

| MOV            | #HIGH_BYTE_0, W3                 | ;     |                                       |

| TBLWTL         | W2, [W0]                         | ;     | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; 1st_program_ | word                             |       |                                       |

| MOV            | #LOW_WORD_1, W2                  | ;     |                                       |

| MOV            | #HIGH_BYTE_1, W3                 | ;     |                                       |

| TBLWTL         | W2, [W0]                         | ;     | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; 2nd_program  | _word                            |       |                                       |

|                | #LOW_WORD_2, W2                  | ;     |                                       |

|                | <pre>#HIGH_BYTE_2, W3</pre>      | ;     |                                       |

|                | W2, [W0]                         |       | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| •              |                                  |       |                                       |

| •              |                                  |       |                                       |

| •              |                                  |       |                                       |

| ; 63rd_program | —                                |       |                                       |

| MOV            | #LOW_WORD_31, W2                 | ;     |                                       |

| MOV            | #HIGH_BYTE_31, W3                | ;     |                                       |

|                | W2, [W0]                         |       | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

|                |                                  |       |                                       |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | ;                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ; Insert two NOPs after the             |

| NOP  |             | ; erase command is asserted             |

|      |             |                                         |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | <ol> <li>Stack error trap has occurred</li> </ol>  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

#### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit                                             |

|-------|--------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit                                                           |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>    |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit                                                          |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>    |

#### U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 IC7IP<2:0> IC8IP<2:0> \_ \_\_\_\_ bit 15 bit 8 U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 AD2IP<2:0> INT1IP<2:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 IC8IP<2:0>: Input Capture Channel 8 Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 IC7IP<2:0>: Input Capture Channel 7 Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 7 Unimplemented: Read as '0' bit 6-4 AD2IP<2:0>: ADC2 Conversion Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 INT1IP<2:0>: External Interrupt 1 Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled

#### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0      | R/W-0                  | U-0        | U-0                    | R/W-0      | R/W-0      |

|-------|------------------------|------------|------------------------|------------|------------------------|------------|------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5(2) | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2) | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2) | IRQSEL0(2) |

| bit 7 |                        |            |                        |            |                        |            | bit 0      |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: See Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

### 9.1 CPU Clocking System

There are seven system clock options provided by the dsPIC33FJXXXMCX06A/X08A/X10A:

- FRC Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- LPRC Oscillator

- FRC Oscillator with Postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The FRC (Fast RC) internal oscillator runs at a nominal frequency of 7.37 MHz. The user software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> bits (CLKDIV<10:8>).

The primary oscillator can use one of the following as its clock source:

- 1. XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 2. HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 3. EC (External Clock): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC (Low-Power RC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 26-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 23.1 "Configuration Bits**" for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose between twelve different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected), Fosc, is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device and speeds up to 40 MHz are supported by the dsPIC33FJXXXMCX06A/X08A/X10A architecture.

Instruction execution speed or device operating frequency, FCY, is given by the following equation:

#### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

#### 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides a significant amount of flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected to be in the range of 0.8 MHz to 8 MHz. Since the minimum prescale factor is 2, this implies that FIN must be chosen to be in the range of 1.6 MHz to 16 MHz. The prescale factor, 'N1', is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL feedback divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor, 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor, 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

For a primary oscillator or FRC oscillator output, 'FIN', the PLL output, 'FOSC', is given by the following equation:

#### EQUATION 9-2: Fosc CALCULATION

$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$

NOTES:

| R/W-0              | U-0                                                             | R/W-0                             | U-0              | U-0                            | U-0           | U-0                  | U-0            |  |  |  |

|--------------------|-----------------------------------------------------------------|-----------------------------------|------------------|--------------------------------|---------------|----------------------|----------------|--|--|--|

| TON <sup>(1)</sup> | _                                                               | TSIDL <sup>(2)</sup>              |                  | _                              | _             | _                    | _              |  |  |  |

| bit 15             |                                                                 |                                   |                  | •                              |               |                      | bit 8          |  |  |  |

|                    |                                                                 |                                   |                  |                                |               |                      |                |  |  |  |

| U-0                | R/W-0                                                           | R/W-0                             | R/W-0            | U-0                            | U-0           | R/W-0                | U-0            |  |  |  |

|                    | TGATE <sup>(1)</sup>                                            | TCKPS                             | <1:0> <b>(1)</b> | —                              |               | TCS <sup>(1,3)</sup> |                |  |  |  |

| bit 7              |                                                                 |                                   |                  |                                |               |                      | bit (          |  |  |  |

|                    |                                                                 |                                   |                  |                                |               |                      |                |  |  |  |

| Legend:            | . 1. 11                                                         |                                   |                  |                                |               |                      |                |  |  |  |

| R = Readable       |                                                                 | W = Writable                      | DIt              | U = Unimplen                   |               |                      |                |  |  |  |

| -n = Value at      | POR                                                             | '1' = Bit is set                  |                  | '0' = Bit is clea              | ared          | x = Bit is unknown   |                |  |  |  |

| bit 15             | TON: Timery                                                     | On bit <sup>(1)</sup>             |                  |                                |               |                      |                |  |  |  |

|                    | 1 = Starts 16-                                                  |                                   |                  |                                |               |                      |                |  |  |  |

|                    | 0 = Stops 16-                                                   |                                   |                  |                                |               |                      |                |  |  |  |

| bit 14             | Unimplemen                                                      | ted: Read as '                    | )'               |                                |               |                      |                |  |  |  |

| bit 13             | TSIDL: Stop i                                                   | in Idle Mode bit                  | (2)              |                                |               |                      |                |  |  |  |

|                    |                                                                 |                                   |                  | device enters Id               | le mode       |                      |                |  |  |  |

|                    | 0 = Continue                                                    | module operati                    | on in Idle mo    | ode                            |               |                      |                |  |  |  |

| bit 12-7           | -                                                               | ted: Read as '                    |                  |                                |               |                      |                |  |  |  |

| bit 6              | TGATE: Timery Gated Time Accumulation Enable bit <sup>(1)</sup> |                                   |                  |                                |               |                      |                |  |  |  |

|                    | When TCS =                                                      |                                   |                  |                                |               |                      |                |  |  |  |

|                    | This bit is ign                                                 |                                   |                  |                                |               |                      |                |  |  |  |

|                    | When TCS =<br>1 = Gated tim                                     | <u>0:</u><br>ne accumulatior      | enabled          |                                |               |                      |                |  |  |  |

|                    |                                                                 | ne accumulation                   |                  |                                |               |                      |                |  |  |  |

| bit 5-4            | TCKPS<1:0>                                                      | : Timer3 Input                    | Clock Presca     | ale Select bits <sup>(1)</sup> |               |                      |                |  |  |  |

|                    | 11 <b>= 1:256</b>                                               | ·                                 |                  |                                |               |                      |                |  |  |  |

|                    | 10 <b>= 1:64</b>                                                |                                   |                  |                                |               |                      |                |  |  |  |

|                    | 01 = 1:8                                                        |                                   |                  |                                |               |                      |                |  |  |  |

| <b>h</b> :+ 0 0    | 00 = 1:1                                                        | tod. Dood oo '                    | <b>、</b>         |                                |               |                      |                |  |  |  |

| bit 3-2            | •                                                               | ted: Read as '0<br>Clock Source S |                  |                                |               |                      |                |  |  |  |

| bit 1              | ,                                                               |                                   |                  |                                |               |                      |                |  |  |  |

|                    | 1 = External c<br>0 = Internal c                                | clock from TyCł<br>lock (Ecy)     | c pin (on the    | nsing edge)                    |               |                      |                |  |  |  |

| bit 0              |                                                                 | ited: Read as '                   | )'               |                                |               |                      |                |  |  |  |

|                    | P                                                               |                                   | -                |                                |               |                      |                |  |  |  |

|                    |                                                                 |                                   |                  | = 1), these bits               | have no effec | t on Timery operat   | tion; all time |  |  |  |

| fur                | nctions are set th                                              | hrough T2CON                      |                  |                                |               |                      |                |  |  |  |

REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

### 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

#### 22.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

#### 22.5 ADC Resources

Many useful resources related to ADC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en546066                                                                                                                          |

#### 22.5.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| DC CHA       | RACTER | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |                    |            |        |                                                                                                                                                                                   |

|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                                                                                                                                                                          | Min                | Тур <sup>(1)</sup> | Max        | Units  | Conditions                                                                                                                                                                        |

|              | VIL    | Input Low Voltage                                                                                                                                                                                                                                                                       |                    |                    |            |        |                                                                                                                                                                                   |

| DI10         |        | I/O Pins                                                                                                                                                                                                                                                                                | Vss                | —                  | 0.2 VDD    | V      |                                                                                                                                                                                   |

| DI15         |        | MCLR                                                                                                                                                                                                                                                                                    | Vss                | —                  | 0.2 VDD    | V      |                                                                                                                                                                                   |

| DI16         |        | I/O Pins with OSC1 or SOSCI                                                                                                                                                                                                                                                             | Vss                | _                  | 0.2 VDD    | V      |                                                                                                                                                                                   |

| DI18         |        | I/O Pins with I <sup>2</sup> C™                                                                                                                                                                                                                                                         | Vss                | _                  | 0.3 VDD    | V      | SMBus disabled                                                                                                                                                                    |

| DI19         |        | I/O Pins with I <sup>2</sup> C                                                                                                                                                                                                                                                          | Vss                | _                  | 0.8 V      | V      | SMBus enabled                                                                                                                                                                     |

|              | VIH    | Input High Voltage                                                                                                                                                                                                                                                                      |                    |                    |            |        |                                                                                                                                                                                   |

| DI20         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup>                                                                                                                                                                                                          | 0.7 Vdd<br>0.7 Vdd | _                  | Vdd<br>5.5 | V<br>V |                                                                                                                                                                                   |

| DI28         |        | SDAx, SCLx                                                                                                                                                                                                                                                                              | 0.7 Vdd            | —                  | 5.5        | V      | SMBus disabled                                                                                                                                                                    |

| DI29         |        | SDAx, SCLx                                                                                                                                                                                                                                                                              | 2.1                | _                  | 5.5        | V      | SMBus enabled                                                                                                                                                                     |

|              | ICNPU  | CNx Pull-up Current                                                                                                                                                                                                                                                                     |                    |                    |            |        |                                                                                                                                                                                   |

| DI30         |        |                                                                                                                                                                                                                                                                                         | 50                 | 250                | 400        | μA     | VDD = 3.3V, VPIN = VSS                                                                                                                                                            |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>                                                                                                                                                                                                                                                  |                    |                    |            |        |                                                                                                                                                                                   |

| DI50         |        | I/O Pins 5V Tolerant <sup>(4)</sup>                                                                                                                                                                                                                                                     | —                  | —                  | ±2         | μA     | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                                                                                                                                  |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                                                                                                                                                                                                                                 | _                  | —                  | ±1         | μA     | $\label{eq:VSS} \begin{split} &Vss \leq V \text{PIN} \leq V \text{DD}, \\ &\text{Pin at high-impedance,} \\ &-40^\circ\text{C} \leq \text{TA} \leq +85^\circ\text{C} \end{split}$ |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                                                                                                                                                                                                                                 | —                  | —                  | ±2         | μA     | Shared with external reference pins, -40°C $\leq$ TA $\leq$ +85°C                                                                                                                 |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                                                                                                                                                                                                                                 | _                  | —                  | ±3.5       | μA     | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance,<br>-40°C $\leq$ TA $\leq$ +125°C                                                                                               |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                                                                                                                                                                                                                                 | _                  | —                  | ±8         | μA     | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                                          |

| DI55         |        | MCLR                                                                                                                                                                                                                                                                                    | —                  | _                  | ±2         | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                                                          |

| DI56         |        | OSC1                                                                                                                                                                                                                                                                                    | _                  | —                  | ±2         | μA     | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and }H{\sf S} \text{ modes} \end{split}$                                             |

#### TABLE 26-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (VSS 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

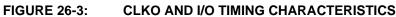

| AC CHARACTERISTICS |        |                                   | Standard Ope<br>(unless other<br>Operating tem | wise state         | <b>ed)</b><br>-40°C ≤ | Ta≤ +8 | 5°C for I  | ndustrial<br>Extended |

|--------------------|--------|-----------------------------------|------------------------------------------------|--------------------|-----------------------|--------|------------|-----------------------|

| Param<br>No.       | Symbol | Character                         | Min                                            | Typ <sup>(1)</sup> | Max                   | Units  | Conditions |                       |

| DO31               | TioR   | Port Output Rise Time             |                                                |                    | 10                    | 25     | ns         |                       |

| DO32               | TIOF   | Port Output Fall Time             | ;                                              | _                  | 10                    | 25     | ns         | _                     |

| DI35               | TINP   | INTx Pin High or Low Time (input) |                                                | 20                 |                       |        | ns         | —                     |

| DI40               | Trbp   | CNx High or Low Time (input)      |                                                | 2                  |                       | _      | TCY        | _                     |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

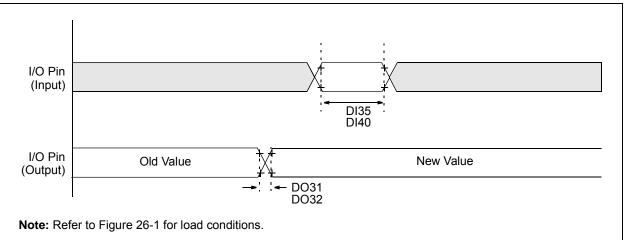

### FIGURE 26-29:ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01,<br/>SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

### APPENDIX B: REVISION HISTORY

#### Revision A (May 2009)

This is the initial released version of the document.

### **Revision B (October 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits.

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

#### TABLE B-1: MAJOR SECTION UPDATES

| Section Name                                                                                                         | Update Description                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|