Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc510at-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJXXXMCX06A/X08A/X10A devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJXXXMCX06A/X08A/X10A instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum 'C' compiler efficiency. For most instructions, the dsPIC33FJXXXMCX06A/X08A/X10A devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1 and the programmer's model for the dsPIC33FJXXXMCX06A/X08A/X10A is shown in Figure 3-2.

#### 3.1 Data Addressing Overview

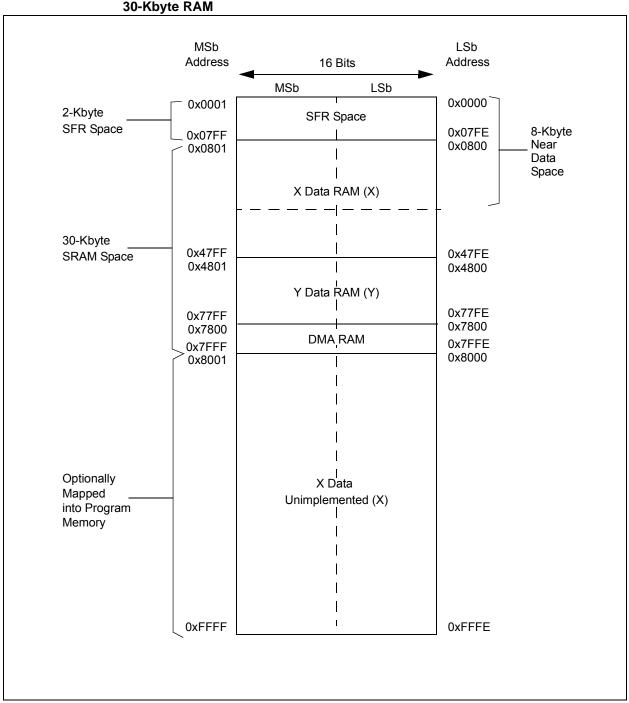

The data space can be addressed as 32K words or 64 Kbytes, and is split into two blocks referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

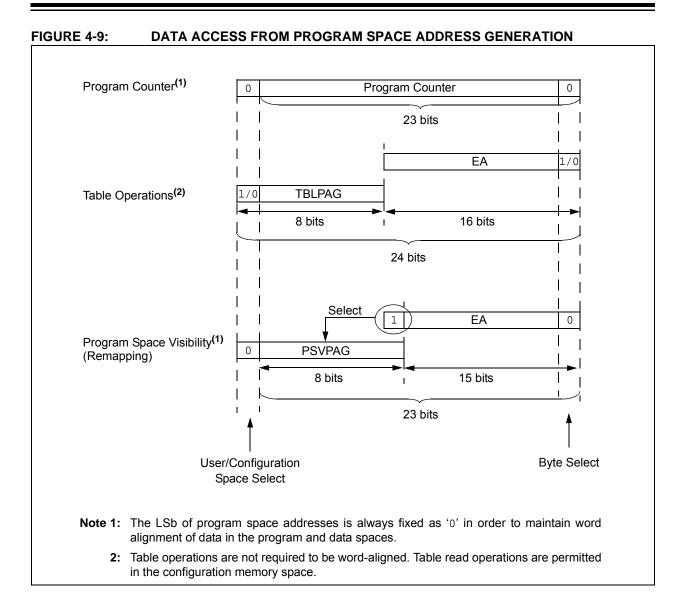

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page register (PSVPAG). The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers but may be used as general purpose RAM.

#### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers, and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM memory data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

## FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 30-Kbyte RAM

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXMCX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and

three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data by blocks (or 'rows') of 64 instructions (192 bytes) at a time or by single program memory word; the user can erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

#### 5.1 Table Instructions and Flash Programming

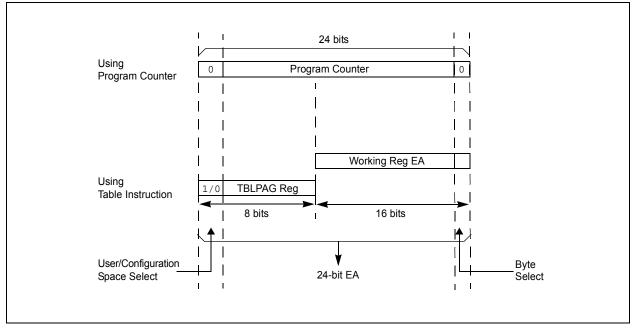

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| R/W-0         | R-0                                                                                                   | U-0                                  | U-0         | U-0              | U-0              | U-0             | U-0    |  |

|---------------|-------------------------------------------------------------------------------------------------------|--------------------------------------|-------------|------------------|------------------|-----------------|--------|--|

| ALTIVT        | DISI                                                                                                  | —                                    | _           | —                | —                |                 | —      |  |

| bit 15        |                                                                                                       |                                      |             |                  |                  |                 | bit 8  |  |

|               |                                                                                                       |                                      |             |                  |                  |                 |        |  |

| U-0           | U-0                                                                                                   | U-0                                  | R/W-0       | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

| —             | —                                                                                                     | —                                    | INT4EP      | INT3EP           | INT2EP           | INT1EP          | INT0EP |  |

| bit 7         |                                                                                                       |                                      |             |                  |                  |                 | bit 0  |  |

|               |                                                                                                       |                                      |             |                  |                  |                 |        |  |

| Legend:       |                                                                                                       |                                      |             |                  |                  |                 |        |  |

| R = Readable  |                                                                                                       | W = Writable                         |             | -                | nented bit, read |                 |        |  |

| -n = Value at | POR                                                                                                   | '1' = Bit is set                     |             | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |

|               |                                                                                                       |                                      |             |                  |                  |                 |        |  |

| bit 15        |                                                                                                       | ole Alternate In                     | •           | lable bit        |                  |                 |        |  |

|               |                                                                                                       | nate Interrupt \<br>lard (default) v |             |                  |                  |                 |        |  |

| bit 14        |                                                                                                       | struction Statu                      |             |                  |                  |                 |        |  |

|               |                                                                                                       | ruction is activ                     |             |                  |                  |                 |        |  |

|               | 0 = DISI inst                                                                                         | ruction is not a                     | ictive      |                  |                  |                 |        |  |

| bit 13-5      | Unimplemen                                                                                            | ted: Read as '                       | 0'          |                  |                  |                 |        |  |

| bit 4         | INT4EP: Exte                                                                                          | ernal Interrupt 4                    | Edge Detect | Polarity Select  | bit              |                 |        |  |

|               |                                                                                                       | on negative ed                       |             |                  |                  |                 |        |  |

|               | -                                                                                                     | on positive edg                      |             |                  |                  |                 |        |  |

| bit 3         |                                                                                                       | •                                    | •           | Polarity Select  | bit              |                 |        |  |

|               |                                                                                                       | on negative ed<br>on positive edg    |             |                  |                  |                 |        |  |

| bit 2         | -                                                                                                     |                                      |             | Polarity Select  | bit              |                 |        |  |

| SIT Z         | <b>INT2EP:</b> External Interrupt 2 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge |                                      |             |                  |                  |                 |        |  |

|               | 0 = Interrupt on positive edge                                                                        |                                      |             |                  |                  |                 |        |  |

| bit 1         | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit                                          |                                      |             |                  |                  |                 |        |  |

|               | 1 = Interrupt on negative edge                                                                        |                                      |             |                  |                  |                 |        |  |

|               | •                                                                                                     | on positive edg                      |             |                  |                  |                 |        |  |

| bit 0         |                                                                                                       |                                      |             | Polarity Select  | bit              |                 |        |  |

|               |                                                                                                       | on negative ed                       |             |                  |                  |                 |        |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0           | R/W-0                                                      | R/W-0                                                                                                  | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |

|---------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------|-------------------|-----------------|-----------------|--------|--|

| —             | DMA1IF                                                     | AD1IF                                                                                                  | U1TXIF           | U1RXIF            | SPI1IF          | SPI1EIF         | T3IF   |  |

| bit 15        |                                                            |                                                                                                        |                  |                   |                 |                 | bit 8  |  |

| R/W-0         | R/W-0                                                      | R/W-0                                                                                                  | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |

| T2IF          | OC2IF                                                      | IC2IF                                                                                                  | DMA01IF          | T1IF              | OC1IF           | IC1IF           | INT0IF |  |

| bit 7         | L.                                                         |                                                                                                        |                  |                   |                 |                 | bit (  |  |

| Legend:       |                                                            |                                                                                                        |                  |                   |                 |                 |        |  |

| R = Readable  | e bit                                                      | W = Writable                                                                                           | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |  |

| -n = Value at | POR                                                        | '1' = Bit is se                                                                                        | t                | '0' = Bit is clea | ared            | x = Bit is unkn | iown   |  |

| bit 15        | Unimplemen                                                 | ted: Read as                                                                                           | ʻ0'              |                   |                 |                 |        |  |

| bit 14        | -                                                          |                                                                                                        | ata Transfer C   | omplete Interro   | upt Flag Status | s bit           |        |  |

|               |                                                            | request has oc                                                                                         |                  |                   |                 |                 |        |  |

|               | •                                                          | request has no                                                                                         |                  |                   |                 |                 |        |  |

| bit 13        |                                                            |                                                                                                        | Complete Interr  | upt Flag Status   | s bit           |                 |        |  |

|               |                                                            | request has oc<br>request has no                                                                       |                  |                   |                 |                 |        |  |

| bit 12        | <b>U1TXIF:</b> UART1 Transmitter Interrupt Flag Status bit |                                                                                                        |                  |                   |                 |                 |        |  |

|               |                                                            | request has oc                                                                                         |                  |                   |                 |                 |        |  |

|               | -                                                          | request has no                                                                                         |                  |                   |                 |                 |        |  |

| bit 11        |                                                            |                                                                                                        | nterrupt Flag S  | Status bit        |                 |                 |        |  |

|               |                                                            | request has oc<br>request has no                                                                       |                  |                   |                 |                 |        |  |

| bit 10        | •                                                          | •                                                                                                      | ot Flag Status b | oit               |                 |                 |        |  |

|               |                                                            | request has oc                                                                                         |                  |                   |                 |                 |        |  |

|               | -                                                          | request has no                                                                                         |                  |                   |                 |                 |        |  |

| bit 9         |                                                            |                                                                                                        | pt Flag Status I | bit               |                 |                 |        |  |

|               |                                                            | request has oc<br>request has no                                                                       |                  |                   |                 |                 |        |  |

| bit 8         | •                                                          | Interrupt Flag                                                                                         |                  |                   |                 |                 |        |  |

|               |                                                            | request has oc                                                                                         |                  |                   |                 |                 |        |  |

|               | •                                                          | request has no                                                                                         |                  |                   |                 |                 |        |  |

| bit 7         |                                                            | Interrupt Flag                                                                                         |                  |                   |                 |                 |        |  |

|               |                                                            | request has oc<br>request has no                                                                       |                  |                   |                 |                 |        |  |

| bit 6         | -                                                          | -                                                                                                      |                  | upt Flag Status   | bit             |                 |        |  |

|               |                                                            | <b>OC2IF:</b> Output Compare Channel 2 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                  |                   |                 |                 |        |  |

|               | •                                                          | request has no                                                                                         |                  |                   |                 |                 |        |  |

| bit 5         |                                                            | -                                                                                                      | el 2 Interrupt F | lag Status bit    |                 |                 |        |  |

|               |                                                            | request has oc<br>request has no                                                                       |                  |                   |                 |                 |        |  |

| bit 4         | -                                                          | -                                                                                                      | ata Transfer C   | omplete Interri   | upt Flag Status | s bit           |        |  |

|               |                                                            | request has oc                                                                                         |                  |                   |                 |                 |        |  |

|               | -                                                          | request has no                                                                                         |                  |                   |                 |                 |        |  |

| bit 3         |                                                            | Interrupt Flag<br>request has or                                                                       |                  |                   |                 |                 |        |  |

|               |                                                            |                                                                                                        |                  |                   |                 |                 |        |  |

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0         | R/W-0                                                                                                                                    | U-0                              | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|----------------------|------------------|----------------|---------|

| T6IF          | DMA4IF                                                                                                                                   | _                                | OC8IF            | OC7IF                | OC6IF            | OC5IF          | IC6IF   |

| bit 15        |                                                                                                                                          |                                  |                  |                      |                  |                | bit 8   |

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                            | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |

| IC5IF         | IC4IF                                                                                                                                    | IC3IF                            | DMA3IF           | C1IF                 | C1RXIF           | SPI2IF         | SPI2EIF |

| bit 7         |                                                                                                                                          |                                  |                  |                      | I                |                | bit (   |

| Legend:       |                                                                                                                                          |                                  |                  |                      |                  |                |         |

| R = Readable  | e bit                                                                                                                                    | W = Writable                     | bit              | U = Unimple          | mented bit, read | l as '0'       |         |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is set                 |                  | '0' = Bit is cle     | eared            | x = Bit is unk | nown    |

| bit 15        | T6IF: Timer6                                                                                                                             | Interrupt Flag                   | Status bit       |                      |                  |                |         |

|               |                                                                                                                                          | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 14        |                                                                                                                                          | •                                |                  | Complete Interi      | rupt Flag Status | bit            |         |

|               |                                                                                                                                          | request has oc<br>request has no |                  | ·                    |                  |                |         |

| bit 13        |                                                                                                                                          | ted: Read as '                   |                  |                      |                  |                |         |

| bit 12        | OC8IF: Outpu                                                                                                                             | ut Compare Ch                    | annel 8 Interr   | upt Flag Status      | s bit            |                |         |

|               |                                                                                                                                          | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 11        | OC7IF: Outpu                                                                                                                             | ut Compare Ch                    | annel 7 Interr   | upt Flag Status      | s bit            |                |         |

|               |                                                                                                                                          | request has oc                   |                  |                      |                  |                |         |

|               |                                                                                                                                          | request has no                   |                  |                      |                  |                |         |

| bit 10        | •                                                                                                                                        | ut Compare Ch                    |                  | upt Flag Status      | s bit            |                |         |

|               |                                                                                                                                          | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 9         | -                                                                                                                                        | ut Compare Ch                    |                  | upt Flag Status      | s bit            |                |         |

|               |                                                                                                                                          | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 8         | •                                                                                                                                        | Capture Chann                    |                  | -lag Status hit      |                  |                |         |

| bit o         | 1 = Interrupt                                                                                                                            | request has oc<br>request has no | curred           | lag Status bit       |                  |                |         |

| bit 7         | •                                                                                                                                        | Capture Chann                    |                  | -lao Status bit      |                  |                |         |

|               | •                                                                                                                                        | request has oc                   | •                |                      |                  |                |         |

|               |                                                                                                                                          | request has no                   |                  |                      |                  |                |         |

| bit 6         | IC4IF: Input C                                                                                                                           | Capture Chann                    | el 4 Interrupt I | -lag Status bit      |                  |                |         |

|               |                                                                                                                                          | request has oc                   |                  |                      |                  |                |         |

| bit 5         | -                                                                                                                                        | request has no<br>Capture Chappe |                  | -<br>Elaa Status hit |                  |                |         |

| bit 5         | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |                                  |                  |                      |                  |                |         |

| bit 4         | •                                                                                                                                        | •                                |                  | omnlete Inter        | rupt Flag Status | hit            |         |

|               | 1 = Interrupt                                                                                                                            | request has oc<br>request has no | curred           |                      | apting Status    | JA             |         |

| bit 3         | -                                                                                                                                        | l Event Interrup                 |                  | bit                  |                  |                |         |

| Sit U         |                                                                                                                                          | request has oc                   | -                |                      |                  |                |         |

|               |                                                                                                                                          | request has no                   |                  |                      |                  |                |         |

#### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| R/W-0              | U-0                              | R/W-0                             | U-0              | U-0                            | U-0           | U-0                  | U-0            |

|--------------------|----------------------------------|-----------------------------------|------------------|--------------------------------|---------------|----------------------|----------------|

| TON <sup>(1)</sup> | _                                | TSIDL <sup>(2)</sup>              |                  | _                              | _             | _                    | _              |

| bit 15             |                                  |                                   |                  | •                              |               |                      | bit 8          |

|                    |                                  |                                   |                  |                                |               |                      |                |

| U-0                | R/W-0                            | R/W-0                             | R/W-0            | U-0                            | U-0           | R/W-0                | U-0            |

|                    | TGATE <sup>(1)</sup>             | TCKPS                             | <1:0> <b>(1)</b> | —                              |               | TCS <sup>(1,3)</sup> |                |

| bit 7              |                                  |                                   |                  |                                |               |                      | bit (          |

|                    |                                  |                                   |                  |                                |               |                      |                |

| Legend:            | . 1. 11                          |                                   |                  |                                |               |                      |                |

| R = Readable       |                                  | W = Writable                      | DIt              | U = Unimplen                   |               |                      |                |

| -n = Value at      | POR                              | '1' = Bit is set                  |                  | '0' = Bit is clea              | ared          | x = Bit is unkno     | own            |

| bit 15             | TON: Timery                      | On bit <sup>(1)</sup>             |                  |                                |               |                      |                |

|                    | 1 = Starts 16-                   |                                   |                  |                                |               |                      |                |

|                    | 0 = Stops 16-                    |                                   |                  |                                |               |                      |                |

| bit 14             | Unimplemen                       | ted: Read as '                    | )'               |                                |               |                      |                |

| bit 13             | TSIDL: Stop i                    | in Idle Mode bit                  | (2)              |                                |               |                      |                |

|                    |                                  |                                   |                  | device enters Id               | le mode       |                      |                |

|                    | 0 = Continue                     | module operati                    | on in Idle mo    | ode                            |               |                      |                |

| bit 12-7           | -                                | ted: Read as '                    |                  |                                |               |                      |                |

| bit 6              | TGATE: Time                      | ery Gated Time                    | Accumulatio      | n Enable bit <sup>(1)</sup>    |               |                      |                |

|                    | When TCS =                       |                                   |                  |                                |               |                      |                |

|                    | This bit is ign                  |                                   |                  |                                |               |                      |                |

|                    | When TCS =<br>1 = Gated tim      | <u>0:</u><br>ne accumulatior      | enabled          |                                |               |                      |                |

|                    |                                  | ne accumulation                   |                  |                                |               |                      |                |

| bit 5-4            | TCKPS<1:0>                       | : Timer3 Input                    | Clock Presca     | ale Select bits <sup>(1)</sup> |               |                      |                |

|                    | 11 <b>= 1:256</b>                | ·                                 |                  |                                |               |                      |                |

|                    | 10 = 1:64                        |                                   |                  |                                |               |                      |                |

|                    | 01 = 1:8                         |                                   |                  |                                |               |                      |                |

| <b>h</b> :+ 0 0    | 00 = 1:1                         | tod. Dood oo '                    | <b>、</b>         |                                |               |                      |                |

| bit 3-2            | •                                | ted: Read as '0<br>Clock Source S |                  |                                |               |                      |                |

| bit 1              | ,                                |                                   |                  |                                |               |                      |                |

|                    | 1 = External c<br>0 = Internal c | clock from TyCł<br>lock (Ecy)     | C pin (on the    | nsing edge)                    |               |                      |                |

| bit 0              |                                  | ited: Read as '                   | )'               |                                |               |                      |                |

|                    | P                                |                                   | -                |                                |               |                      |                |

|                    |                                  |                                   |                  | = 1), these bits               | have no effec | t on Timery operat   | tion; all time |

| fur                | nctions are set th               | hrough T2CON                      |                  |                                |               |                      |                |

REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

## 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0 = Send ACK during Acknowledge                                                                                                                                                                                                             |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                 |

|       | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul>                             |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                 |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte</li> <li>0 = Receive sequence not in progress</li> </ul>                                                              |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                           |

|       | <ul> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence</li> <li>0 = Stop condition not in progress</li> </ul>                                                                            |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                |

|       | 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence                                                                                                                        |

|       | 0 = Repeated Start condition not in progress                                                                                                                                                                                                |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                 |

|       | <ul> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li> <li>0 = Start condition not in progress</li> </ul>                                                                         |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | R/W-0  | R/W-0 |

|--------------|-------|--------------|-------|--------------|------------------|--------|-------|

| —            | —     | —            | —     |              | —                | AMSK9  | AMSK8 |

| bit 15       |       |              |       |              |                  |        | bit 8 |

|              |       |              |       |              |                  |        |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

| AMSK7        | AMSK6 | AMSK5        | AMSK4 | AMSK3        | AMSK2            | AMSK1  | AMSK0 |

| bit 7        |       |              |       |              |                  | •      | bit 0 |

|              |       |              |       |              |                  |        |       |

| Legend:      |       |              |       |              |                  |        |       |

| R = Readable | bit   | W = Writable | bit   | U = Unimpler | mented bit, read | as '0' |       |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSKx: Mask for Address bit x Select bits

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

#### **REGISTER 22-2:** ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED) (where x = 1 or 2)

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses channel input selects for Sample A on first sample and Sample B on next sample

- 0 = Always uses channel input selects for Sample A

## 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

#### 25.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| DC CH4       | DC CHARACTERISTICS                                                                                                                    |                                                                                                                                    |     | Standard Operating Conditions: 3.0V to 3(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}$ $-40^{\circ}C \le TA \le +125$ |     |                                                     |                                                                                                                   |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol                                                                                                                                | Characteristic                                                                                                                     | Min | Тур                                                                                                                                                         | Max | Units                                               | Conditions                                                                                                        |  |  |

|              |                                                                                                                                       | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - All pins not<br>defined by 4x or 8x driver pins                           | _   | _                                                                                                                                                           | 0.4 | V                                                   | IOL $\leq$ 3 mA, VDD = 3.3V                                                                                       |  |  |

| DO10         | Vol                                                                                                                                   | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - RA2, RA3,<br>RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3 | _   | _                                                                                                                                                           | 0.4 | V                                                   | Iol $\leq$ 6 mA, VDD = 3.3V                                                                                       |  |  |

|              |                                                                                                                                       | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - OSC2, CLKO,<br>RC15                                                       | _   | _                                                                                                                                                           | 0.4 | V                                                   | IOL $\leq$ 10 mA, VDD = 3.3V                                                                                      |  |  |

|              |                                                                                                                                       | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - All pins not<br>defined by 4x or 8x driver pins                        | 2.4 | _                                                                                                                                                           | _   | V                                                   | $IOL \ge -3 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                               |  |  |

| DO20 Vон     | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA2, RA3,<br>RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3 | 2.4                                                                                                                                | _   | _                                                                                                                                                           | V   | $IOL \ge -6 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |                                                                                                                   |  |  |

|              |                                                                                                                                       | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - OSC2,<br>CLKO, RC15                                                    | 2.4 | _                                                                                                                                                           | _   | V                                                   | IoL ≥ -10 mA, VDD = 3.3V                                                                                          |  |  |

|              |                                                                                                                                       | Output High Voltage<br>I/O Pins:                                                                                                   | 1.5 | _                                                                                                                                                           | _   |                                                     | IOH ≥ -6 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                      |  |  |

|              |                                                                                                                                       | 2x Source Driver Pins - All pins not defined by 4x or 8x driver pins                                                               | 2.0 | _                                                                                                                                                           | _   | V                                                   | IOH ≥ -5 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                      |  |  |

|              |                                                                                                                                       |                                                                                                                                    | 3.0 | _                                                                                                                                                           | _   |                                                     | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                      |  |  |

|              |                                                                                                                                       | <b>Output High Voltage</b><br>4x Source Driver Pins - RA2, RA3,                                                                    | 1.5 | _                                                                                                                                                           | _   |                                                     | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                     |  |  |

| DO20A Voh1   | RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3                                                                          | 2.0                                                                                                                                | _   | _                                                                                                                                                           | v   | IOH ≥ -11 mA, VDD = 3.3V<br>See <b>Note 1</b>       |                                                                                                                   |  |  |

|              |                                                                                                                                       |                                                                                                                                    | 3.0 | _                                                                                                                                                           | _   |                                                     | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                      |  |  |

|              |                                                                                                                                       | Output High Voltage<br>8x Source Driver Pins - OSC2,                                                                               | 1.5 | _                                                                                                                                                           | _   |                                                     | $\label{eq:IOH} \begin{array}{l} \mbox{IOH} \geq -16 \mbox{ mA, VDD} = 3.3 V \\ \mbox{See } Note \ 1 \end{array}$ |  |  |

|              |                                                                                                                                       | CLKO, RC15                                                                                                                         | 2.0 | _                                                                                                                                                           | _   | v                                                   | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                     |  |  |

|              |                                                                                                                                       |                                                                                                                                    | 3.0 | _                                                                                                                                                           |     |                                                     | IOH ≥ -4 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                      |  |  |

#### TABLE 26-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

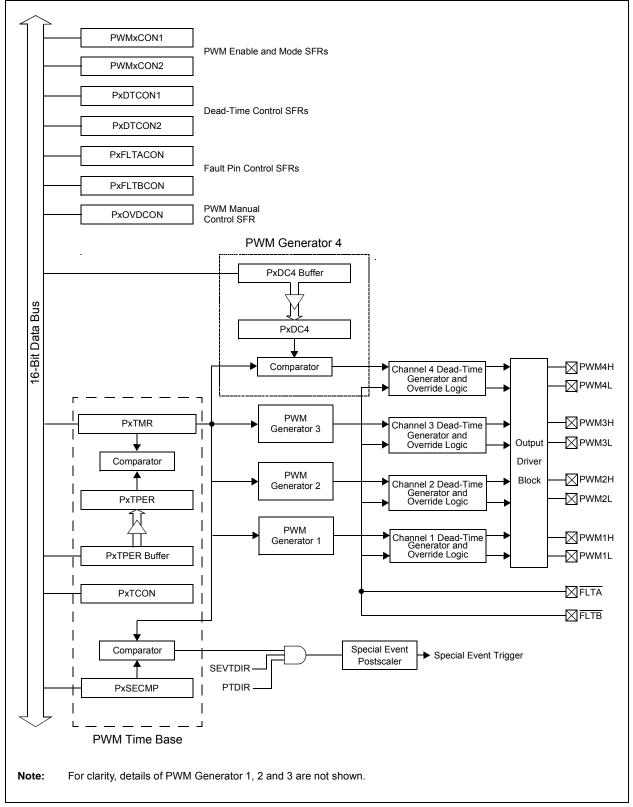

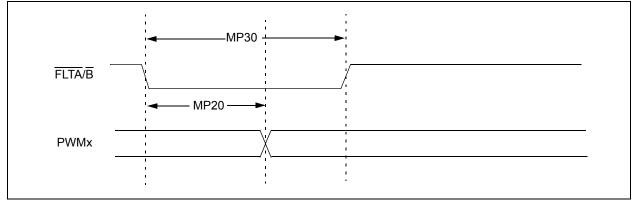

#### FIGURE 26-9: MOTOR CONTROL PWM MODULE FAULT TIMING CHARACTERISTICS

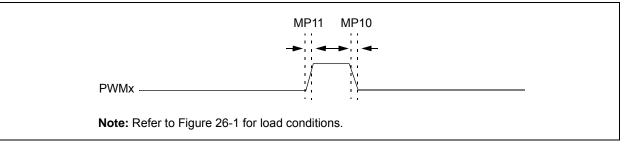

#### FIGURE 26-10: MOTOR CONTROL PWM MODULE TIMING CHARACTERISTICS

#### TABLE 26-28: MOTOR CONTROL PWM MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | (unless                      | rd Opera<br>otherwis<br>ng tempe | se stateo<br>rature | <b>1)</b><br>-40°C ≤  ⊺ | <b>3.0V to 3.6V</b><br>$FA \le +85^{\circ}C$ for Industrial<br>$FA \le +125^{\circ}C$ for Extended |

|--------------------|--------|------------------------------------|------------------------------|----------------------------------|---------------------|-------------------------|----------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>      | Min Typ Max Units Conditions |                                  |                     | Conditions              |                                                                                                    |

| MP10               | TFPWM  | PWM Output Fall Time               | _                            | —                                | —                   | ns                      | See parameter D032                                                                                 |

| MP11               | TRPWM  | PWM Output Rise Time               | _                            | —                                | —                   | ns                      | See parameter D031                                                                                 |

| MP20               | Tfd    | Fault Input ↓ to PWM<br>I/O Change | —                            | —                                | 50                  | ns                      | _                                                                                                  |

| MP30               | Tfh    | Minimum Pulse Width                | 50                           | _                                | _                   | ns                      | —                                                                                                  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

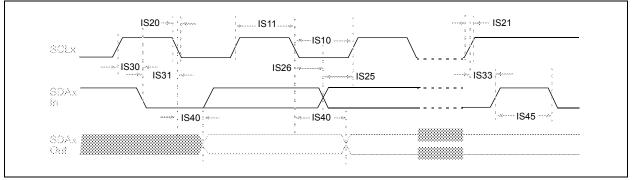

# FIGURE 26-24: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

| АС СНА       |         | STICS                     |                           | Standard Op<br>(unless othe<br>Operating ten | rwise st | <b>ated)</b><br>e -40° | ns: 3.0V to 3.6V<br>$C \le TA \le +85^{\circ}C$ for Industrial<br>$C \le TA \le +125^{\circ}C$ for Extended |

|--------------|---------|---------------------------|---------------------------|----------------------------------------------|----------|------------------------|-------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Charac                    | teristic                  | Min                                          | Max      | Units                  | Conditions                                                                                                  |

| IS10         | TLO:SCL | Clock Low Time            | 100 kHz mode              | 4.7                                          | —        | μS                     | Device must operate at a minimum of 1.5 MHz                                                                 |

|              |         |                           | 400 kHz mode              | 1.3                                          | —        | μS                     | Device must operate at a minimum of 10 MHz                                                                  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                          |          | μS                     | _                                                                                                           |

| IS11         | THI:SCL | Clock High Time           | 100 kHz mode              | 4.0                                          | —        | μS                     | Device must operate at a minimum of 1.5 MHz                                                                 |

|              |         |                           | 400 kHz mode              | 0.6                                          | _        | μS                     | Device must operate at a minimum of 10 MHz                                                                  |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                          |          | μS                     | —                                                                                                           |

| IS20         | TF:SCL  | SDAx and SCLx             | 100 kHz mode              | —                                            | 300      | ns                     | CB is specified to be from                                                                                  |

|              |         | Fall Time                 | 400 kHz mode              | 20 + 0.1 Св                                  | 300      | ns                     | 10 to 400 pF                                                                                                |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | —                                            | 100      | ns                     |                                                                                                             |

| IS21         | TR:SCL  | SDAx and SCLx             | 100 kHz mode              | _                                            | 1000     | ns                     | CB is specified to be from                                                                                  |

|              |         | Rise Time                 | 400 kHz mode              | 20 + 0.1 Св                                  | 300      | ns                     | 10 to 400 pF                                                                                                |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | _                                            | 300      | ns                     |                                                                                                             |

| IS25         | TSU:DAT | Data Input                | 100 kHz mode              | 250                                          |          | ns                     | _                                                                                                           |

|              |         | Setup Time                | 400 kHz mode              | 100                                          |          | ns                     |                                                                                                             |

|              |         | 1 MHz mode <sup>(1)</sup> | 100                       |                                              | ns       |                        |                                                                                                             |

| IS26         | THD:DAT | Data Input                | 100 kHz mode              | 0                                            |          | μs                     | _                                                                                                           |

|              |         | Hold Time                 | 400 kHz mode              | 0                                            | 0.9      | μs                     |                                                                                                             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0                                            | 0.3      | μS                     |                                                                                                             |

| IS30         | TSU:STA | Start Condition           | 100 kHz mode              | 4.7                                          |          | μs                     | Only relevant for Repeated                                                                                  |

|              |         | Setup Time                | 400 kHz mode              | 0.6                                          | _        | μS                     | Start condition                                                                                             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.25                                         | —        | μS                     |                                                                                                             |

| IS31         | THD:STA | Start Condition           | 100 kHz mode              | 4.0                                          | —        | μS                     | After this period, the first                                                                                |

|              |         | Hold Time                 | 400 kHz mode              | 0.6                                          | —        | μS                     | clock pulse is generated                                                                                    |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.25                                         | —        | μs                     |                                                                                                             |

| IS33         | Tsu:sto | Stop Condition            | 100 kHz mode              | 4.7                                          | —        | μs                     | —                                                                                                           |

|              |         | Setup Time                | 400 kHz mode              | 0.6                                          | —        | μS                     |                                                                                                             |