Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 40 MIPs                                                                          |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| lumber of I/O             | 53                                                                               |

| Program Memory Size       | 64KB (64K x 8)                                                                   |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 16K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| ata Converters            | A/D 16x10b/12b                                                                   |

| scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C (TA)                                                               |

| lounting Type             | Surface Mount                                                                    |

| ackage / Case             | 64-VFQFN Exposed Pad                                                             |

| upplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc706a-e-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

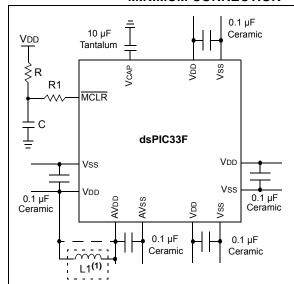

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

Note 1: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $1\Omega$  and the inductor capacity greater than 10 mA.

Where

$$f = \frac{FCNV}{2} \qquad \text{(i.e., ADC conversion rate/2)}$$

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 26.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 23.2** "On-Chip Voltage Regulator" for details.

### 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- · Device Reset

- · Device Programming and Debugging

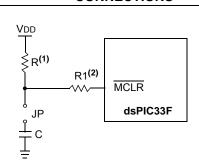

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the  $\overline{\text{MCLR}}$  pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

- Note 1:  $R \le 10 \text{ k}\Omega$  is recommended. A suggested starting value is  $10 \text{ k}\Omega$ . Ensure that the MCLR pin VIH and VIL specifications are met.

- 2:  $R1 \le 470\Omega$  will limit any current flowing into  $\overline{MCLR}$  from the external capacitor, C, in the event of  $\overline{MCLR}$  pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the  $\overline{MCLR}$  pin VIH and VIL specifications are met.

| NOTES: |  |

|--------|--|

|        |  |

### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX10A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | _       | -       | _       | _       | _       | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | _       | _       | _       | _       | _       |        | -      | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX08A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | AII<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | _       | -       | -       | -       | -       | _      | _      | _      | _      | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | _       | -       | -       | -       | -       | _      | _      | _      | _      | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX06A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE  | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | -       | _       | _      | -      | -      | _      | CN21IE  | CN20IE  | _      | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | _       | _       | _       | _       | _       |        |        | _      | _      | CN21PUE | CN20PUE | _      | CN18PUE | CN17PUE | CN16PUE | 0000          |

egend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-9: 8-OUTPUT PWM REGISTER MAP

| SFR Name  | Addr. | Bit 15                     | Bit 14                             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                               | Bit 7               | Bit 6      | Bit 5               | Bit 4               | Bit 3  | Bit 2               | Bit 1  | Bit 0  | Reset State         |

|-----------|-------|----------------------------|------------------------------------|--------|--------|--------|--------|--------|-------------------------------------|---------------------|------------|---------------------|---------------------|--------|---------------------|--------|--------|---------------------|

| P1TCON    | 01C0  | PTEN                       | _                                  | PTSIDL | _      | _      | _      | _      | — PTOPS<3:0> PTCKPS<1:0> PTMOD<1:0> |                     |            |                     |                     |        | 0000 0000 0000 0000 |        |        |                     |

| P1TMR     | 01C2  | PTDIR                      |                                    |        |        |        |        | F      | PWM Time                            | Count Val           | ue Registe | r                   |                     |        |                     |        |        | 0000 0000 0000 0000 |

| P1TPER    | 01C4  | ı                          | PWM Time Base Period Register      |        |        |        |        |        |                                     |                     |            |                     | 0000 0000 0000 0000 |        |                     |        |        |                     |

| P1SECMP   | 01C6  | SEVTDIR                    | PWM Special Event Compare Register |        |        |        |        |        |                                     |                     |            | 0000 0000 0000 0000 |                     |        |                     |        |        |                     |

| PWM1CON1  | 01C8  | ı                          | _                                  | _      | -      | PMOD4  | PMOD3  | PMOD2  | PMOD1                               | PEN4H               | PEN3H      | PEN2H               | PEN1H               | PEN4L  | PEN3L               | PEN2L  | PEN1L  | 0000 0000 1111 1111 |

| PWM1CON2  | 01CA  | _                          | _                                  | _      | _      |        | SEVOP  | S<3:0> |                                     | -                   | 1          | _                   | _                   | _      | IUE                 | OSYNC  | UDIS   | 0000 0000 0000 0000 |

| P1DTCON1  | 01CC  | DTBPS                      | S<1:0>                             |        |        | DTB<   | <5:0>  |        |                                     | DTAPS<1:0> DTA<5:0> |            |                     |                     |        | <5:0>               |        |        | 0000 0000 0000 0000 |

| P1DTCON2  | 01CE  | _                          | _                                  | _      | _      | _      | _      | 1      | _                                   | DTS4A               | DTS4I      | DTS3A               | DTS3I               | DTS2A  | DTS2I               | DTS1A  | DTS1I  | 0000 0000 0000 0000 |

| P1FLTACON | 01D0  | FAOV4H                     | FAOV4L                             | FAOV3H | FAOV3L | FAOV2H | FAOV2L | FAOV1H | FAOV1L                              | FLTAM               | 1          | _                   | _                   | FAEN4  | FAEN3               | FAEN2  | FAEN1  | 0000 0000 0000 0000 |

| P1FLTBCON | 01D2  | FBOV4H                     | FBOV4L                             | FBOV3H | FBOV3L | FBOV2H | FBOV2L | FBOV1H | FBOV1L                              | FLTBM               | 1          | _                   | _                   | FBEN4  | FBEN3               | FBEN2  | FBEN1  | 0000 0000 0000 0000 |

| P10VDCON  | 01D4  | POVD4H                     | POVD4L                             | POVD3H | POVD3L | POVD2H | POVD2L | POVD1H | POVD1L                              | POUT4H              | POUT4L     | POUT3H              | POUT3L              | POUT2H | POUT2L              | POUT1H | POUT1L | 1111 1111 0000 0000 |

| P1DC1     | 01D6  |                            |                                    |        |        |        |        | PWN    | □ Duty Cyc                          | le #1 Regi          | ster       |                     |                     |        |                     |        |        | 0000 0000 0000 0000 |

| P1DC2     | 01D8  |                            | PWM Duty Cycle #2 Register         |        |        |        |        |        |                                     |                     |            |                     |                     |        | 0000 0000 0000 0000 |        |        |                     |

| P1DC3     | 01DA  |                            | PWM Duty Cycle #3 Register         |        |        |        |        |        |                                     |                     |            |                     |                     |        | 0000 0000 0000 0000 |        |        |                     |

| P1DC4     | 01DC  | PWM Duty Cycle #4 Register |                                    |        |        |        |        |        |                                     |                     |            | 0000 0000 0000 0000 |                     |        |                     |        |        |                     |

**Legend:** u = uninitialized bit, — = unimplemented, read as '0'

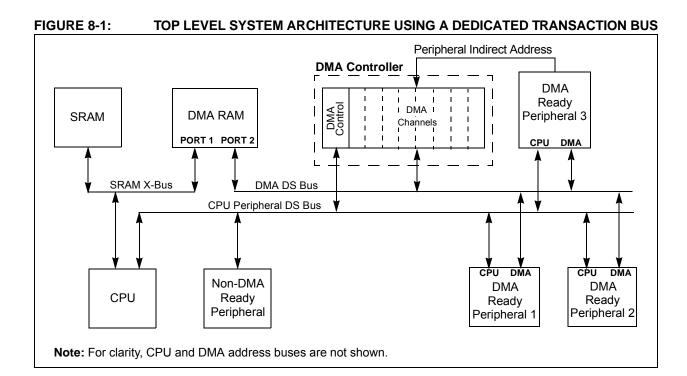

### 8.1 DMAC Registers

Each DMAC Channel x (x = 0, 1, 2, 3, 4, 5, 6 or 7) contains the following registers:

- A 16-Bit DMA Channel Control register (DMAxCON)

- A 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- A 16-Bit DMA RAM Primary Start Address Offset register (DMAxSTA)

- A 16-Bit DMA RAM Secondary Start Address Offset register (DMAxSTB)

- A 16-Bit DMA Peripheral Address register (DMAxPAD)

- A 10-Bit DMA Transfer Count register (DMAxCNT)

An additional pair of status registers, DMACS0 and DMACS1, are common to all DMAC channels.

### REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-------|-----|-----|-------|

| CHEN   | SIZE  | DIR   | HALF  | NULLW | _   | _   | _     |

| bit 15 |       |       |       |       |     |     | bit 8 |

| U-0   | U-0 | R/W-0      | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|------------|-------|-----|-----|-------|-------|

| _     | _   | AMODE<1:0> |       | _   | _   | MODE  | <1:0> |

| bit 7 |     |            |       |     |     |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15   | CHEN: Channel Enable bit                                                                                                                                                                         |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Channel enabled                                                                                                                                                                              |

|          | 0 = Channel disabled                                                                                                                                                                             |

| bit 14   | SIZE: Data Transfer Size bit                                                                                                                                                                     |

|          | 1 = Byte<br>0 = Word                                                                                                                                                                             |

| bit 13   | DIR: Transfer Direction bit (source/destination bus select)                                                                                                                                      |

|          | <ul><li>1 = Read from DMA RAM address; write to peripheral address</li><li>0 = Read from peripheral address; write to DMA RAM address</li></ul>                                                  |

| bit 12   | HALF: Early Block Transfer Complete Interrupt Select bit                                                                                                                                         |

|          | <ul><li>1 = Initiate block transfer complete interrupt when half of the data has been moved</li><li>0 = Initiate block transfer complete interrupt when all of the data has been moved</li></ul> |

| bit 11   | NULLW: Null Data Peripheral Write Mode Select bit                                                                                                                                                |

|          | <ul><li>1 = Null data write to peripheral in addition to DMA RAM write (DIR bit must also be clear)</li><li>0 = Normal operation</li></ul>                                                       |

| bit 10-6 | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 5-4  | AMODE<1:0>: DMA Channel Operating Mode Select bits                                                                                                                                               |

|          | 11 = Reserved                                                                                                                                                                                    |

|          | 10 = Peripheral Indirect Addressing mode                                                                                                                                                         |

|          | <ul><li>01 = Register Indirect without Post-Increment mode</li><li>00 = Register Indirect with Post-Increment mode</li></ul>                                                                     |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 1-0  | MODE<1:0>: DMA Channel Operating Mode Select bits                                                                                                                                                |

|          | 11 = One-Shot, Ping-Pong modes enabled (one block transfer from/to each DMA RAM buffer)                                                                                                          |

10 = Continuous, Ping-Pong modes enabled 01 = One-Shot, Ping-Pong modes disabled 00 = Continuous, Ping-Pong modes disabled

### REGISTER 16-4: PXSECMP: PWMx SPECIAL EVENT COMPARE REGISTER

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|------------------------|-------|------------------|-------|-------|-------|-------|-------|--|--|--|--|

| SEVTDIR <sup>(1)</sup> |       | SEVTCMP<14:8>(2) |       |       |       |       |       |  |  |  |  |

| bit 15                 |       |                  |       |       |       |       | bit 8 |  |  |  |  |

| R/W-0           | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|

| SEVTCMP<7:0>(2) |       |       |       |       |       |       |       |

| bit 7           |       |       |       |       |       |       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 SEVTDIR: Special Event Trigger Time Base Direction bit<sup>(1)</sup>

1 = A Special Event Trigger will occur when the PWM time base is counting downwards

0 = A Special Event Trigger will occur when the PWM time base is counting upwards

bit 14-0 SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup>

Note 1: SEVTDIR is compared with PTDIR (PTMR<15>) to generate the Special Event Trigger.

2: SEVTCMP<14:0> is compared with PTMR<14:0> to generate the Special Event Trigger.

### 21.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization Mode

- · Disable Mode

- · Normal Operation Mode

- · Listen Only Mode

- · Listen All Messages Mode

- · Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- · Baud Rate and Interrupt Configuration Registers

- · Bus Timing Registers

- · Identifier Acceptance Filter Registers

- · Identifier Acceptance Mask Registers

#### 21.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note:

Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set, and the TXREQ bit is cleared.

#### 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

#### 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

### 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = 111. In this mode, the data which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

#### 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

#### REGISTER 21-1: CiCTRL1: ECAN™ CONTROL REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | r-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-----|-------|-------|-----|-------|------------|-------|

| _      | _   | CSIDL | ABAT  | _   |       | REQOP<2:0> |       |

| bit 15 |     |       |       |     |       |            | bit 8 |

| R-1   | R-0         | R-0 | U-0 | R/W-0  | U-0 | U-0 | R/W-0 |

|-------|-------------|-----|-----|--------|-----|-----|-------|

|       | OPMODE<2:0> |     | _   | CANCAP | _   | _   | WIN   |

| bit 7 |             |     |     |        |     |     | bit 0 |

**Legend:** r = Reserved bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 CSIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12 ABAT: Abort All Pending Transmissions bit

1 = Signal all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions are aborted

bit 11 Reserved: Do no use

bit 10-8 **REQOP<2:0>:** Request Operation Mode bits

111 = Set Listen All Messages mode

110 = Reserved – do not use

101 = Reserved – do not use

100 = Set Configuration mode

011 = Set Listen Only Mode

010 = Set Loopback mode

001 = Set Disable mode

000 = Set Normal Operation mode

bit 7-5 **OPMODE<2:0>:** Operation Mode bits

111 = Module is in Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Loopback mode

001 = Module is in Disable mode

000 = Module is in Normal Operation mode

bit 4 Unimplemented: Read as '0'

bit 3 CANCAP: CAN Message Receive Timer Capture Event Enable bit

1 = Enable input capture based on CAN message receive

0 = Disable CAN capture

bit 2-1 **Unimplemented:** Read as '0'

bit 0 WIN: SFR Map Window Select bit

1 = Use filter window

0 = Use buffer window

### REGISTER 21-5: CiFIFO: ECAN™ FIFO STATUS REGISTER

| U-0    | U-0 | R-0 | R-0 | R-0 | R-0   | R-0 | R-0   |

|--------|-----|-----|-----|-----|-------|-----|-------|

| _      | _   |     |     | FBP | <5:0> |     |       |

| bit 15 |     |     |     |     |       |     | bit 8 |

| U-0   | U-0 | R-0 | R-0 | R-0 | R-0    | R-0 | R-0   |

|-------|-----|-----|-----|-----|--------|-----|-------|

| _     | _   |     |     | FNR | 3<5:0> |     |       |

| bit 7 |     |     |     |     |        |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **FBP<5:0>:** FIFO Write Buffer Pointer bits

011111 = RB31 buffer 011110 = RB30 buffer

•

•

000001 = TRB1 buffer 000000 = TRB0 buffer

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 FNRB<5:0>: FIFO Next Read Buffer Pointer bits

011111 = RB31 buffer 011110 = RB30 buffer

•

•

000001 = TRB1 buffer 000000 = TRB0 buffer

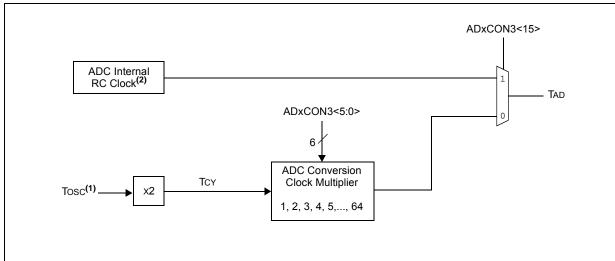

### FIGURE 22-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

- Note 1: Refer to Figure 9-2 for the derivation of Fosc when the PLL is enabled. If the PLL is not used, Fosc is equal to the clock source frequency, Tosc = 1/Fosc.

- 2: See the ADC electrical specifications for the exact RC clock value.

### REGISTER 22-9: ADxPCFGH: ADCx PORT CONFIGURATION REGISTER HIGH<sup>(1,2,3,4)</sup>

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG31 | PCFG30 | PCFG29 | PCFG28 | PCFG27 | PCFG26 | PCFG25 | PCFG24 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG23 | PCFG22 | PCFG21 | PCFG20 | PCFG19 | PCFG18 | PCFG17 | PCFG16 |

| bit 7  |        |        |        |        |        |        | bit 0  |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **PCFG<31:16>:** ADC Port Configuration Control bits

- 1 = Port pin in Digital mode; port read input enabled; ADC input multiplexer connected to AVss

- 0 = Port pin in Analog mode; port read input disabled; ADC samples pin voltage

- **Note 1:** On devices without 32 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on the device.

- 2: ADC2 only supports analog inputs, AN0-AN15; therefore, no ADC2 port Configuration register exists.

- 3: PCFGx = ANx, where x = 16 through 31.

- **4:** The PCFGx bits have no effect if the ADC module is disabled by setting the ADxMD bit in the PMDx register. In this case, all port pins multiplexed with ANx will be in Digital mode.

### REGISTER 22-10: ADXPCFGL: ADCX PORT CONFIGURATION REGISTER LOW(1,2,3,4)

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| PCFG15 | PCFG14 | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 15 |        |        |        |        |        |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PCFG7 | PCFG6 | PCFG5 | PCFG4 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 15-0 **PCFG<15:0>:** ADC Port Configuration Control bits

- 1 = Port pin in Digital mode; port read input enabled; ADC input multiplexer connected to AVss

- 0 = Port pin in Analog mode; port read input disabled; ADC samples pin voltage

- **Note 1:** On devices without 16 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on the device.

- 2: On devices with two analog-to-digital modules, both AD1PCFGL and AD2PCFGL will affect the configuration of port pins multiplexed with AN0-AN15.

- 3: PCFGx = ANx, where x = 0 through 15.

- **4:** The PCFGx bits have no effect if the ADC module is disabled by setting the ADxMD bit in the PMDx register. In this case, all port pins multiplexed with ANx will be in Digital mode.

### 26.1 DC Characteristics

TABLE 26-1: OPERATING MIPS vs. VOLTAGE

| Param | V <sub>DD</sub> Range    | Temp Range      | Max MIPS                     |

|-------|--------------------------|-----------------|------------------------------|

| No.   | (in Volts)               | (in °C)         | dsPIC33FJXXXMCX06A/X08A/X10A |

| _     | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C  | 40                           |

| _     | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C | 40                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 26-11 for the minimum and maximum BOR values.

#### **TABLE 26-2: THERMAL OPERATING CONDITIONS**

| Rating                                                                                                                 | Symbol | Min         | Тур         | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| dsPIC33FJXXXMCX06A/X08A/X10A                                                                                           |        |             |             |      |      |

| Operating Junction Temperature Range                                                                                   | TJ     | -40         | _           | +125 | °C   |

| Operating Ambient Temperature Range                                                                                    | TA     | -40         | _           | +85  | °C   |

| Extended Temperature Devices                                                                                           |        |             |             |      |      |

| Operating Junction Temperature Range                                                                                   | TJ     | -40         | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                    | TA     | -40         | _           | +125 | °C   |

| Power Dissipation: Internal Chip Power Dissipation: $PINT = VDD \ x \ (IDD - \Sigma \ IOH)$ I/O Pin Power Dissipation: | PD     | PINT + PI/O |             |      | W    |

| I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)                                                              |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                                                      | PDMAX  | (           | ΓJ — TA)/θJ | IA   | W    |

#### **TABLE 26-3: THERMAL PACKAGING CHARACTERISTICS**

| Characteristic                                        | Symbol | Тур | Max | Unit | Notes |

|-------------------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θЈА    | 40  | -   | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θЈА    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 80-pin TQFP (12x12x1 mm)  | θЈА    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θЈА    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θЈА    | 28  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

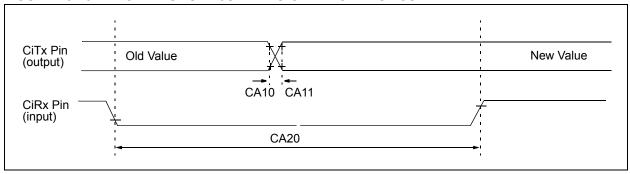

### FIGURE 26-26: CAN MODULE I/O TIMING CHARACTERISTICS

TABLE 26-42: ECAN™ TECHNOLOGY MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |     |     |       |                    |

|--------------------|--------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>             | Min                                                                                                                                                                                                                                              | Тур | Max | Units | Conditions         |

| CA10               | TioF   | Port Output Fall Time                     | _                                                                                                                                                                                                                                                | _   | _   | ns    | See parameter D032 |

| CA11               | TioR   | Port Output Rise Time                     | _                                                                                                                                                                                                                                                | _   | _   | ns    | See parameter D031 |

| CA20               | Tcwf   | Pulse Width to Trigger CAN Wake-up Filter | 120                                                                                                                                                                                                                                              |     | _   | ns    | _                  |

Note 1: These parameters are characterized but not tested in manufacturing.

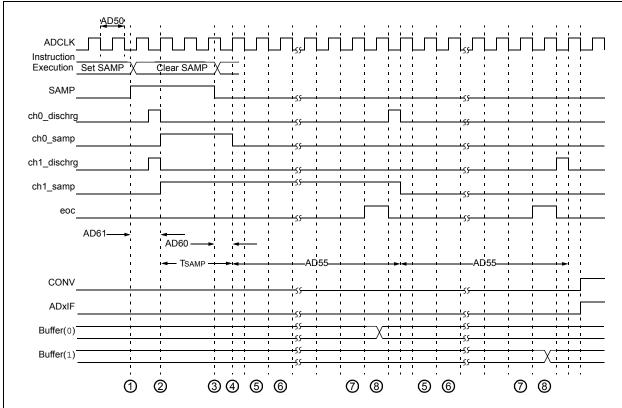

FIGURE 26-28: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000)

- 1 Software sets ADxCON. SAMP to start sampling.

- 2 Sampling starts after discharge period. TSAMP is described in Section 16. "10/12-bit ADC with DMA" in the "dsPIC33F Family Reference Manual".

- 3 Software clears ADxCON. SAMP to start conversion.

- 4 Sampling ends, conversion sequence starts.

- (5) Convert bit 9.

- 6 Convert bit 8.

- (7) Convert bit 0.

- (8) One TAD for end of conversion.

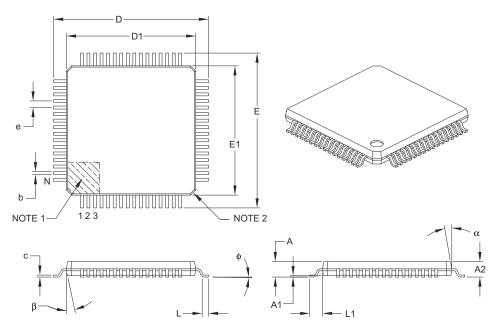

### 64-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         |           |      | MILLIMETERS |  |  |  |

|--------------------------|---------------|-----------|------|-------------|--|--|--|

| Dime                     | ension Limits | MIN       | NOM  | MAX         |  |  |  |

| Number of Leads          | N             | 64        |      |             |  |  |  |

| Lead Pitch               | е             | 0.50 BSC  |      |             |  |  |  |

| Overall Height           | Α             | -         | _    | 1.20        |  |  |  |

| Molded Package Thickness | A2            | 0.95      | 1.00 | 1.05        |  |  |  |

| Standoff                 | A1            | 0.05      | _    | 0.15        |  |  |  |

| Foot Length              | L             | 0.45      | 0.60 | 0.75        |  |  |  |

| Footprint                | L1            | 1.00 REF  |      |             |  |  |  |

| Foot Angle               | ф             | 0°        | 3.5° | 7°          |  |  |  |

| Overall Width            | E             | 12.00 BSC |      |             |  |  |  |

| Overall Length           | D             | 12.00 BSC |      |             |  |  |  |

| Molded Package Width     | E1            | 10.00 BSC |      |             |  |  |  |

| Molded Package Length    | D1            | 10.00 BSC |      |             |  |  |  |

| Lead Thickness           | С             | 0.09      | _    | 0.20        |  |  |  |

| Lead Width               | b             | 0.17      | 0.22 | 0.27        |  |  |  |

| Mold Draft Angle Top     | α             | 11°       | 12°  | 13°         |  |  |  |

| Mold Draft Angle Bottom  | β             | 11°       | 12°  | 13°         |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

| dsPIC33FJXXXMCX06A/X08A/X10A |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|

| NOTES:                       |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |