Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc706a-i-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.1.1 PROGRAM MEMORY ORGANIZATION

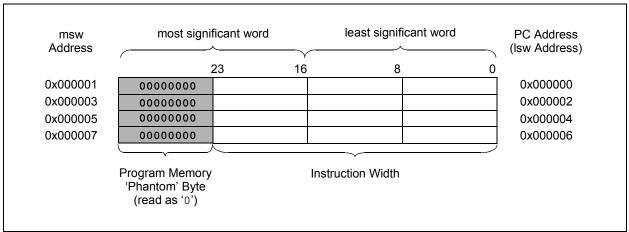

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXMCX06A/X08A/X10A devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXMCX06A/X08A/X10A devices also have two interrupt vector tables located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector **Table**".

FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

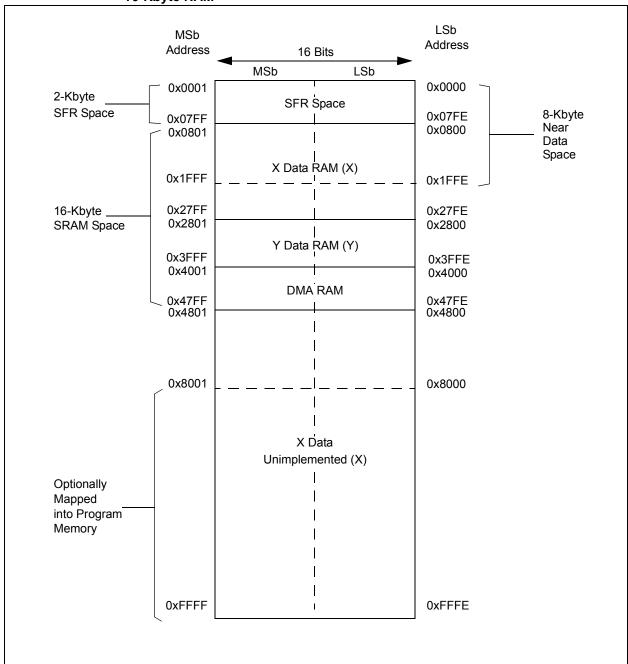

FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 16-Kbyte RAM

### TABLE 4-28: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      | _      | 1     | _     | _     | 1     | _     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | 1     | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | _      | _     | _     | _     | -     | _     | RC4    | RC3    | RC2    | RC1    | _     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  | _      | ı      | ı     | ı     | _     | ı     | _     | LATC4  | LATC3  | LATC2  | LATC1  | ı     | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-29: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-30: PORTE REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | AII<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISE     | 02D8 | _      | _      | _      | _      | _      | _      | TRISE9 | TRISE8 | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 01FF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | RE9    | RE8    | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx          |

| LATE      | 02DC | -      | _      | _      | _      | _      | _      | LATE9  | LATE8  | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

dsPIC33FJXXXMCX06A/X08A/X10A

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-31: PORTF REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF     | 02DE | _      | _      | TRISF13 | TRISF12 | _      | _      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF     | 02E0 | _      | _      | RF13    | RF12    | _      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF      | 02E2 | _      | ı      | LATF13  | LATF12  | -      | -      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF      | 06DE | _      | _      | ODCF13  | ODCF12  | -      | 1      |       | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### **EXAMPLE 5-2: LOADING THE WRITE BUFFERS**

```

; Set up NVMCON for row programming operations

#0x4001, W0

; Initialize NVMCON

MOV

W0, NVMCON

; Set up a pointer to the first program memory location to be written

; program memory selected, and writes enabled

#0x0000, W0

MOV

W0, TBLPAG

; Initialize PM Page Boundary SFR

#0x6000, W0

MOV

; An example program memory address

; Perform the TBLWT instructions to write the latches

; Oth_program_word

#LOW_WORD_0, W2

MOV

#HIGH_BYTE_0, W3

;

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3, [W0++]

; Write PM high byte into program latch

; 1st_program_word

MOV

#LOW_WORD_1, W2

MOV

#HIGH_BYTE_1, W3

;

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3, [W0++]

; Write PM high byte into program latch

; 2nd_program_word

#LOW_WORD_2, W2

MOV

#HIGH_BYTE_2, W3

MOV

;

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3, [W0++]

; Write PM high byte into program latch

; 63rd_program_word

#LOW_WORD_31, W2

MOV

MOV

#HIGH_BYTE_31, W3

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3, [W0++]

; Write PM high byte into program latch

```

#### **EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE**

```

DISI

; Block all interrupts with priority <7

; for next 5 instructions

MOV

#0x55, W0

WO, NVMKEY

; Write the 55 key

VOM

MOV

#0xAA, W1

MOV

W1, NVMKEY

; Write the AA key

BSET NVMCON, #WR

; Start the erase sequence

NOP

; Insert two NOPs after the

NOP

; erase command is asserted

```

TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address           | AIVT Address          | Interrupt Source                   |

|------------------|--------------------------------------|-----------------------|-----------------------|------------------------------------|

| 54               | 46                                   | 0x000070              | 0x000170              | DMA4 – DMA Channel 4               |

| 55               | 47                                   | 0x000072              | 0x000172              | T6 – Timer6                        |

| 56               | 48                                   | 0x000074              | 0x000174              | T7 – Timer7                        |

| 57               | 49                                   | 0x000076              | 0x000176              | SI2C2 – I2C2 Slave Events          |

| 58               | 50                                   | 0x000078              | 0x000178              | MI2C2 – I2C2 Master Events         |

| 59               | 51                                   | 0x00007A              | 0x00017A              | T8 – Timer8                        |

| 60               | 52                                   | 0x00007C              | 0x00017C              | T9 – Timer9                        |

| 61               | 53                                   | 0x00007E              | 0x00017E              | INT3 – External Interrupt 3        |

| 62               | 54                                   | 0x000080              | 0x000180              | INT4 – External Interrupt 4        |

| 63               | 55                                   | 0x000082              | 0x000182              | C2RX – ECAN2 Receive Data Ready    |

| 64               | 56                                   | 0x000084              | 0x000184              | C2 – ECAN2 Event                   |

| 65               | 57                                   | 0x000086              | 0x000186              | PWM – PWM Period Match             |

| 66               | 58                                   | 0x000088              | 0x000188              | QEI – Position Counter Compare     |

| 69               | 61                                   | 0x00008E              | 0x00018E              | DMA5 – DMA Channel 5               |

| 70               | 62                                   | 0x000090              | 0x000190              | Reserved                           |

| 71               | 63                                   | 0x000092              | 0x000192              | FLTA – MCPWM Fault A               |

| 72               | 64                                   | 0x000094              | 0x000194              | FLTB – MCPWM Fault B               |

| 73               | 65                                   | 0x000096              | 0x000196              | U1E – UART1 Error                  |

| 74               | 66                                   | 0x000098              | 0x000198              | U2E – UART2 Error                  |

| 75               | 67                                   | 0x00009A              | 0x00019A              | Reserved                           |

| 76               | 68                                   | 0x00009C              | 0x00019C              | DMA6 – DMA Channel 6               |

| 77               | 69                                   | 0x00009E              | 0x00019E              | DMA7 – DMA Channel 7               |

| 78               | 70                                   | 0x0000A0              | 0x0001A0              | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                                   | 0x0000A2              | 0x0001A2              | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 72-117                               | 0x0000A4-<br>0x0000FE | 0x0001A4-<br>0x0001FE | Reserved                           |

TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x000008    | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0  | R-0  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|------|-----|-----|-----|-----|-----|-------|

| ALTIVT | DISI | _   | _   | _   | _   | _   | _     |

| bit 15 |      | •   |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| _     | _   | _   | INT4EP | INT3EP | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 ALTIVT: Enable Alternate Interrupt Vector Table bit

1 = Use Alternate Interrupt Vector Table0 = Use standard (default) vector table

bit 14 DISI: DISI Instruction Status bit

1 = DISI instruction is active 0 = DISI instruction is not active

bit 13-5 **Unimplemented:** Read as '0'

bit 4 INT4EP: External Interrupt 4 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 3 INT3EP: External Interrupt 3 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 0 INT0EP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0  |

|--------|--------|--------|--------|-----|-------|-------|--------|

| C2TXIE | C1TXIE | DMA7IE | DMA6IE | _   | U2EIE | U1EIE | FLTBIE |

| bit 7  |        |        |        |     |       |       | bit 0  |

Legend:

bit 3

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7 C2TXIE: ECAN2 Transmit Data Request Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 6 C1TXIE: ECAN1 Transmit Data Request Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 5 DMA7IE: DMA Channel 7 Data Transfer Complete Enable Status bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 4 DMA6IE: DMA Channel 6 Data Transfer Complete Enable Status bit

1 = Interrupt request enabled 0 = Interrupt request not enabled Unimplemented: Read as '0'

bit 2 **U2EIE:** UART2 Error Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 1 **U1EIE:** UART1 Error Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 0 FLTBIE: PWM Fault B Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

# 8.0 DIRECT MEMORY ACCESS (DMA)

Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 22. "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., the UART Receive register and Input Capture 1 buffer) and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers, and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJXXXMCX06A/X08A/X10A peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

TABLE 8-1: PERIPHERALS WITH DMA SUPPORT

| Peripheral         | IRQ Number |

|--------------------|------------|

| INT0               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels. Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data, either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- · Word or byte-sized data transfers.

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral.

- Indirect Addressing of DMA RAM locations with or without automatic post-increment.

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral.

- One-Shot Block Transfers Terminating DMA transfer after one block transfer.

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete.

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately.

- · Automatic or manual initiation of block transfers.

- Each channel can select from 20 possible sources of data sources or destinations.

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

#### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|

| STA<15:8> |       |       |       |       |       |       |       |  |

| bit 15    |       |       |       |       |       |       | bit 8 |  |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| STA<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7    |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **STA<15:0>:** Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | STB<  | 15:8> |       |       | ļ     |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | STB   | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

#### REGISTER 16-1: PXTCON: PWMX TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| PTEN   | _   | PTSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0      | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0  | R/W-0 |

|-------|------------|-------|-------------|-------|-------|--------|-------|

|       | PTOPS<3:0> |       | PTCKPS<1:0> |       | PTMO  | D<1:0> |       |

| bit 7 |            |       |             |       |       |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 PTEN: PWM Time Base Timer Enable bit

1 = PWM time base is on 0 = PWM time base is off

bit 14 **Unimplemented:** Read as '0'

bit 13 PTSIDL: PWM Time Base Stop in Idle Mode bit

1 = PWM time base halts in CPU Idle mode

0 = PWM time base runs in CPU Idle mode

bit 12-8 **Unimplemented:** Read as '0'

bit 7-4 PTOPS<3:0>: PWM Time Base Output Postscale Select bits

1111 = 1:16 postscale

.

0001 = 1:2 postscale

0000 = 1:1 postscale

bit 3-2 PTCKPS<1:0>: PWM Time Base Input Clock Prescale Select bits

11 = PWM time base input clock period is 64 Tcy (1:64 prescale)

10 = PWM time base input clock period is 16 Tcy (1:16 prescale)

01 = PWM time base input clock period is 4 Tcy (1:4 prescale)

00 = PWM time base input clock period is Tcy (1:1 prescale)

bit 1-0 PTMOD<1:0>: PWM Time Base Mode Select bits

11 = PWM time base operates in a Continuous Up/Down Count mode with interrupts for double PWM updates

10 = PWM time base operates in a Continuous Up/Down Count mode

01 = PWM time base operates in a Single Pulse mode

00 = PWM time base operates in a Free-Running mode

#### REGISTER 16-8: PXDTCON2: PWMx DEAD-TIME CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DTS4A | DTS4I | DTS3A | DTS3I | DTS2A | DTS2I | DTS1A | DTS1I |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8

Unimplemented: Read as '0'

bit 7

DTS4A: Dead-Time Select for PWM4 Signal Going Active bit

1 = Dead time provided from Unit B

0 = Dead time provided from Unit A

bit 6

DTS4I: Dead-Time Select for PWM4 Signal Going Inactive bit

1 = Dead time provided from Unit B

0 = Dead time provided from Unit A

bit 5

DTS3A: Dead-Time Select for PWM3 Signal Going Active bit

1 = Dead time provided from Unit B

0 = Dead time provided from Unit A

bit 4 DTS3I: Dead-Time Select for PWM3 Signal Going Inactive bit

1 = Dead time provided from Unit B0 = Dead time provided from Unit A

bit 3 DTS2A: Dead-Time Select for PWM2 Signal Going Active bit

1 = Dead time provided from Unit B0 = Dead time provided from Unit A

bit 2 DTS2I: Dead-Time Select for PWM2 Signal Going Inactive bit

1 = Dead time provided from Unit B0 = Dead time provided from Unit A

bit 1 DTS1A: Dead-Time Select for PWM1 Signal Going Active bit

1 = Dead time provided from Unit B0 = Dead time provided from Unit A

bit 0 DTS1I: Dead-Time Select for PWM1 Signal Going Inactive bit

1 = Dead time provided from Unit B0 = Dead time provided from Unit A

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| _      | _   | _   | _   | _   | _   | AMSK9 | AMSK8 |

| bit 15 |     |     |     |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-0 AMSKx: Mask for Address bit x Select bits

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

#### REGISTER 21-16: CIRXFnSID: ECAN™ ACCEPTANCE FILTER n STANDARD IDENTIFIER (n = 0, 1, ...,15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | SID<  | 10:3> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x    | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x  |

|-------|----------|-------|-----|-------|-----|-------|--------|

|       | SID<2:0> |       | _   | EXIDE | _   | EID<1 | 17:16> |

| bit 7 | pit 7    |       |     |       |     |       | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Message address bit, SIDx, must be '1' to match filter 0 = Message address bit, SIDx, must be '0' to match filter

bit 4 **Unimplemented:** Read as '0'

bit 3 **EXIDE:** Extended Identifier Enable bit

If MIDE = 1, then:

1 = Match only messages with extended identifier addresses0 = Match only messages with standard identifier addresses

If MIDE = 0, then: Ignore EXIDE bit.

bit 2 **Unimplemented:** Read as '0'

bit 1-0 EID<17:16>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter 0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-17: CIRXFnEID: ECAN™ ACCEPTANCE FILTER n EXTENDED IDENTIFIER (n = 0, 1, ..., 15)

| R/W-x        | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| EID<15:8>    |       |       |       |       |       |       |       |  |

| bit 15 bit 8 |       |       |       |       |       |       |       |  |

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| EID<7:0>    |       |       |       |       |       |       |       |  |

| bit 7 bit 0 |       |       |       |       |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **EID<15:0>:** Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### 24.0 INSTRUCTION SET SUMMARY

Note:

This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33F instruction set is identical to that of the dsPIC30F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- · DSP operations

- Control operations

Table 24-1 shows the general symbols used in describing the instructions.

The dsPIC33F instruction set summary in Table 24-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions may use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication and may include:

- · The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

FIGURE 26-12: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS

**TABLE 26-30: QEI INDEX PULSE TIMING REQUIREMENTS**

| AC CHARACTERISTICS |        |                                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |     |                                                      |            |

|--------------------|--------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                 |                                                                                                                                                                                                        | Min | Max | Units                                                | Conditions |

| TQ50               | TqiL   | Filter Time to Recognize with Digital Filter  | 3 * N * Tcy                                                                                                                                                                                            | _   | ns  | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 (Note 2)     |            |

| TQ51               | TqiH   | Filter Time to Recognize with Digital Filter  | 3 * N * Tcy                                                                                                                                                                                            |     | ns  | N = 1, 2, 4, 16, 32, 64, 128 and 256 <b>(Note 2)</b> |            |

| TQ55               | Tqidxr | Index Pulse Recognized Counter Reset (ungated | 3 Tcy                                                                                                                                                                                                  |     | ns  | _                                                    |            |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on falling edge.

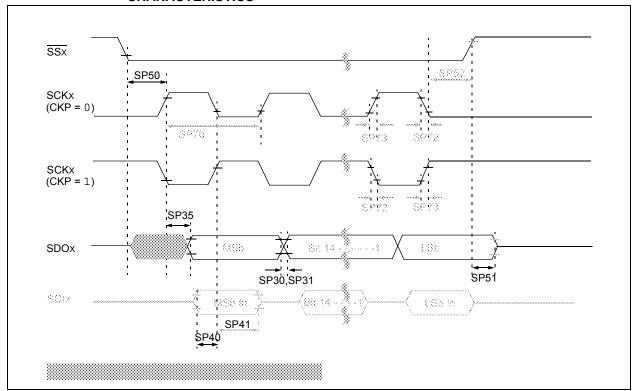

FIGURE 26-21: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

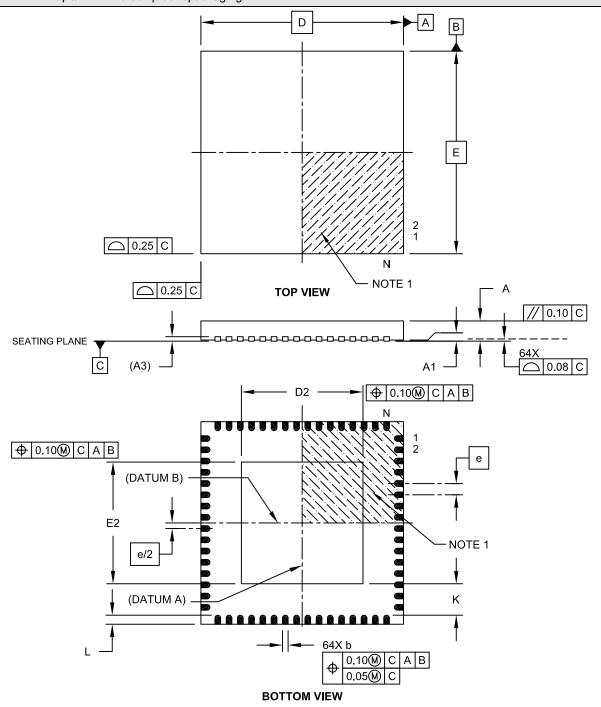

#### 29.2 Package Details

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-154A Sheet 1 of 2

| dsPIC33FJXXXWCXU6A/XU8A/X1UA |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|

| NOTES:                       |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

#### **INDEX**

| A                                                              |

|----------------------------------------------------------------|

| A/D Converter                                                  |

| DMA                                                            |

| Initialization245                                              |

| Key Features245                                                |

| AC Characteristics                                             |

| ADC Module336                                                  |

| ADC Module (10-bit Mode)                                       |

| ADC Module (12-bit Mode)                                       |

| Internal RC Accuracy292                                        |

| Load Conditions                                                |

| ADC Module                                                     |

| ADC1 Register Map52                                            |

| ADC2 Register Map52                                            |

| Alternate Vector Interrupt Table (AIVT)85                      |

| Arithmetic Logic Unit (ALU)29                                  |

| Assembler                                                      |

| MPASM Assembler276                                             |

| В                                                              |

| _                                                              |

| Barrel Shifter                                                 |

| Bit-Reversed Addressing                                        |

| Example                                                        |

| Implementation                                                 |

| Sequence Table (16-Entry)67                                    |

| Block Diagrams                                                 |

| 16-Bit Timer1 Module                                           |

| A/D Module                                                     |

| Connections for On-Chip Voltage Regulator                      |

| Device Clock (Oscillator)                                      |

| Device Clock (PLL)                                             |

| DSP Engine                                                     |

| dsPIC33F                                                       |

| dsPIC33F CPU Core                                              |

| ECAN Technology                                                |

| I <sup>2</sup> C Module 204                                    |

| Input Capture         173           Output Compare         175 |

| Programmer's Model                                             |

| PWM Module 180                                                 |

| Quadrature Encoder Interface                                   |

| Reset System79                                                 |

| Shared Port Structure                                          |

| SPI Module                                                     |

|                                                                |

| Timer2 (16-Bit)                                                |

| Top Level System Architecture Using Dedicated                  |

| Transaction Bus134                                             |

| UART Module                                                    |

| Watchdog Timer (WDT)                                           |

| Brown-out Reset (BOR)                                          |

| ,                                                              |

| C                                                              |

| C Compilers                                                    |

| MPLAB C18276                                                   |

| Clock Switching151                                             |

| Enabling151                                                    |

| Sequence151                                                    |

| Code Examples                                                  |

| Erasing a Program Memory Page76                                |

| Initiating a Programming Sequence77                            |

| Loading Write Buffers77                                        |

| Port Write/Read162                                             |

| PWRSAV Instruction Syntax153                                   |

| Code Protection                        | 259, 266 |

|----------------------------------------|----------|

| CodeGuard Security                     | 259, 266 |

| Configuration Bits                     | 259      |

| Configuration Register Map             | 259      |

| Configuring Analog Port Pins           |          |

| CPU                                    |          |

| Control Register                       | 26       |

| CPU Clocking System                    |          |

| PLL                                    |          |

| Selection                              |          |

| Sources                                |          |

|                                        |          |

| Customer Change Notification Service   |          |

| Customer Notification Service          |          |

| Customer Support                       | 369      |

| D                                      |          |

| _                                      |          |

| Data Accumulators and Adder/Subtracter |          |

| Data Space Write Saturation            |          |

| Overflow and Saturation                |          |

| Round Logic                            | 32       |

| Write Back                             | 32       |

| Data Address Space                     | 37       |

| Alignment                              |          |

| Memory Map for dsPIC33FJXXXMCX06A/X08  |          |

| Devices with 16-Kbyte RAM              |          |

| Memory Map for dsPIC33FJXXXMCX06A/X08  |          |

| Devices with 30-Kbyte RAM              |          |

| Memory Map for dsPIC33FJXXXMCX06A/X08  | Λ/V10Λ   |

|                                        |          |

| Devices with 8-Kbyte RAM               |          |

| Near Data Space                        |          |

| Software Stack                         |          |

| Width                                  | 37       |

| DC and AC Characteristics              |          |

| Graphs and Tables                      | 339      |

| DC Characteristics                     |          |

| Doze Current (IDOZE)                   | 285, 331 |

| High Temperature                       | 330      |

| I/O Pin Input Specifications           | 286      |

| I/O Pin Output Specifications          |          |

| Idle Current (IIDLE)                   |          |

| Operating Current (IDD)                |          |

| Operating MIPS vs. Voltage             |          |

| Power-Down Current (IPD)               |          |

| Power-down Current (IPD)               |          |

| Program Memory                         |          |

|                                        |          |

| Temperature and Voltage                |          |

| Temperature and Voltage Specifications |          |

| Thermal Operating Conditions           |          |

| Development Support                    | 275      |

| DMA Module                             |          |

| DMA Register Map                       |          |

| DMAC Registers                         | 135      |

| DMAxCNT                                | 135      |

| DMAxCON                                | 135      |

| DMAxPAD                                | 135      |

| DMAxREQ                                |          |

| DMAxSTA                                |          |

| DMAxSTB                                |          |

| DSP Engine                             |          |

| Multiplier                             |          |

|                                        | 31       |

| Multiplier                             | 3′       |

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Temperature Rang     | nily ———————————————————————————————————— |                                                                                     | Examples:  a) dsPIC33FJ256MC' Motor Control dsPI 64-Kbyte program 64-pin, Industrial te TQFP package. |

|----------------------|-------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Architecture:        | 33 =                                      | 16-bit Digital Signal Controller                                                    |                                                                                                       |

| Flash Memory Family: | FJ =                                      | Flash program memory, 3.3V                                                          |                                                                                                       |

| Product Group:       | MC5 =<br>MC7 =                            | Motor Control family<br>Motor Control family                                        |                                                                                                       |

| Pin Count:           | 06 = 08 = 10 =                            | 64-pin<br>80-pin<br>100-pin                                                         |                                                                                                       |

| Temperature Range:   |                                           | -40°C to +85°C (Industrial)<br>-40°C to +125°C (Extended)<br>-40°C to +150°C (High) |                                                                                                       |

| Package:             | PT =<br>PF =<br>MR =                      |                                                                                     |                                                                                                       |

| Pattern              | Three-digi<br>(blank oth                  | t QTP, SQTP, Code or Special Requirements erwise)                                   |                                                                                                       |

710ATI/PT: IC33, memory, emperature,