Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc706at-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

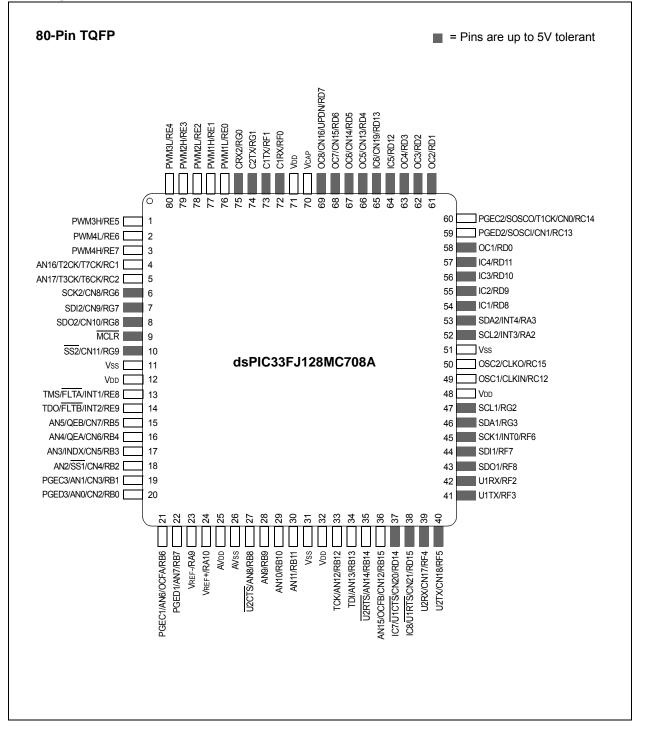

### **Pin Diagrams (Continued)**

### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = CPU interrupt priority level is 7 (15), user interrupts disabled                                                                       |

|         | 110 = CPU interrupt priority level is 6 (14)                                                                                                 |

|         | 101 = CPU interrupt priority level is 5 (13)                                                                                                 |

|         | 100 = CPU interrupt priority level is 4 (12)                                                                                                 |

|         | 011 = CPU interrupt priority level is 3 (11)<br>010 = CPU interrupt priority level is 2 (10)                                                 |

|         | 001 = CPU interrupt priority level is 1 (9)                                                                                                  |

|         | 000 = CPU interrupt priority level is 0 (8)                                                                                                  |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                   |

|         | 1 = REPEAT loop in progress                                                                                                                  |

|         | 0 = REPEAT loop not in progress                                                                                                              |

| bit 3   | N: MCU ALU Negative bit                                                                                                                      |

|         | 1 = Result was negative                                                                                                                      |

|         | 0 = Result was non-negative (zero or positive)                                                                                               |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                     |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state. |

|         | 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)                                                                   |

|         | 0 = No overflow occurred                                                                                                                     |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                          |

|         | 1 = An operation which affects the Z bit has set it at some time in the past                                                                 |

|         | 0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)                                               |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                  |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                         |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                        |

|         |                                                                                                                                              |

- **Note 1:** This bit may be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

- 4: This bit may be read or cleared (not set). Clearing this bit will clear SA and SB.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXMCX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and

three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data by blocks (or 'rows') of 64 instructions (192 bytes) at a time or by single program memory word; the user can erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

### 5.1 Table Instructions and Flash Programming

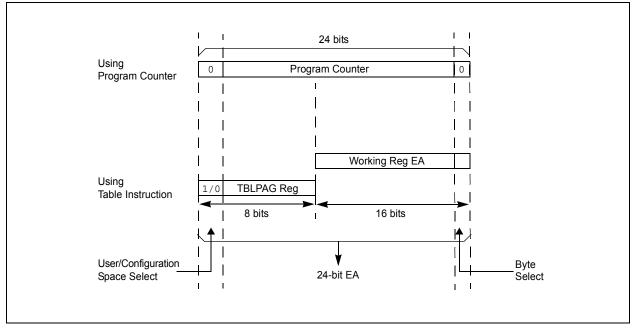

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| R/W-0         | R/W-0                                                                                                                        | U-0                                                                                                                      | R/W-0      | R/W-0            | R/W-0            | R/W-0          | R/W-0   |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|------------------|------------------|----------------|---------|--|--|--|

| T6IF          | DMA4IF                                                                                                                       | _                                                                                                                        | OC8IF      | OC7IF            | OC6IF            | OC5IF          | IC6IF   |  |  |  |

| bit 15        |                                                                                                                              |                                                                                                                          |            |                  |                  |                | bit 8   |  |  |  |

| R/W-0         | R/W-0                                                                                                                        | R/W-0                                                                                                                    | R/W-0      | R/W-0            | R/W-0            | R/W-0          | R/W-0   |  |  |  |

| IC5IF         | IC4IF                                                                                                                        | IC3IF                                                                                                                    | DMA3IF     | C1IF             | C1RXIF           | SPI2IF         | SPI2EIF |  |  |  |

| bit 7         |                                                                                                                              |                                                                                                                          |            |                  | I                |                | bit (   |  |  |  |

| Legend:       |                                                                                                                              |                                                                                                                          |            |                  |                  |                |         |  |  |  |

| R = Readable  | e bit                                                                                                                        | W = Writable                                                                                                             | bit        | U = Unimple      | mented bit, read | l as '0'       |         |  |  |  |

| -n = Value at | POR                                                                                                                          | '1' = Bit is set                                                                                                         |            | '0' = Bit is cle | eared            | x = Bit is unk | nown    |  |  |  |

| bit 15        | T6IF: Timer6                                                                                                                 | Interrupt Flag                                                                                                           | Status bit |                  |                  |                |         |  |  |  |

|               |                                                                                                                              | request has oc<br>request has no                                                                                         |            |                  |                  |                |         |  |  |  |

| bit 14        |                                                                                                                              | •                                                                                                                        |            | Complete Interi  | rupt Flag Status | bit            |         |  |  |  |

|               |                                                                                                                              | request has oc<br>request has no                                                                                         |            | ·                |                  |                |         |  |  |  |

| bit 13        |                                                                                                                              | ted: Read as '                                                                                                           |            |                  |                  |                |         |  |  |  |

| bit 12        | OC8IF: Output Compare Channel 8 Interrupt Flag Status bit                                                                    |                                                                                                                          |            |                  |                  |                |         |  |  |  |

|               |                                                                                                                              | request has oc<br>request has no                                                                                         |            |                  |                  |                |         |  |  |  |

| bit 11        | <b>OC7IF:</b> Output Compare Channel 7 Interrupt Flag Status bit                                                             |                                                                                                                          |            |                  |                  |                |         |  |  |  |

|               | 1 = Interrupt request has occurred                                                                                           |                                                                                                                          |            |                  |                  |                |         |  |  |  |

|               | 0 = Interrupt request has not occurred                                                                                       |                                                                                                                          |            |                  |                  |                |         |  |  |  |

| bit 10        | OC6IF: Output Compare Channel 6 Interrupt Flag Status bit                                                                    |                                                                                                                          |            |                  |                  |                |         |  |  |  |

|               |                                                                                                                              | request has oc<br>request has no                                                                                         |            |                  |                  |                |         |  |  |  |

| bit 9         | -                                                                                                                            | ut Compare Ch                                                                                                            |            | upt Flag Status  | s bit            |                |         |  |  |  |

|               | 1 = Interrupt request has occurred                                                                                           |                                                                                                                          |            |                  |                  |                |         |  |  |  |

| bit 8         |                                                                                                                              | <ul> <li>Interrupt request has not occurred</li> <li>IC6IF: Input Capture Channel 6 Interrupt Flag Status bit</li> </ul> |            |                  |                  |                |         |  |  |  |

| bit o         | 1 = Interrupt                                                                                                                | request has oc<br>request has no                                                                                         | curred     | lag Status bit   |                  |                |         |  |  |  |

| bit 7         | •                                                                                                                            | -                                                                                                                        |            | -lao Status bit  |                  |                |         |  |  |  |

|               | IC5IF: Input Capture Channel 5 Interrupt Flag Status bit<br>1 = Interrupt request has occurred                               |                                                                                                                          |            |                  |                  |                |         |  |  |  |

|               | 0 = Interrupt request has not occurred                                                                                       |                                                                                                                          |            |                  |                  |                |         |  |  |  |

| bit 6         | IC4IF: Input Capture Channel 4 Interrupt Flag Status bit                                                                     |                                                                                                                          |            |                  |                  |                |         |  |  |  |

|               | 1 = Interrupt request has occurred                                                                                           |                                                                                                                          |            |                  |                  |                |         |  |  |  |

| bit 5         | <ul> <li>0 = Interrupt request has not occurred</li> <li>IC3IF: Input Capture Channel 3 Interrupt Flag Status bit</li> </ul> |                                                                                                                          |            |                  |                  |                |         |  |  |  |

| bit 5         | 1 = Interrupt                                                                                                                | request has oc<br>request has no                                                                                         | curred     | ay status bit    |                  |                |         |  |  |  |

| bit 4         | •                                                                                                                            | •                                                                                                                        |            | omnlete Inter    | rupt Flag Status | hit            |         |  |  |  |

|               | 1 = Interrupt                                                                                                                | request has oc<br>request has no                                                                                         | curred     |                  | apting Status    | JA             |         |  |  |  |

| bit 3         | -                                                                                                                            | l Event Interrup                                                                                                         |            | bit              |                  |                |         |  |  |  |

| Sit U         |                                                                                                                              | -                                                                                                                        | -          |                  |                  |                |         |  |  |  |

|               | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                       |                                                                                                                          |            |                  |                  |                |         |  |  |  |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| REGISTER 7-12: | IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| R/W-0         | R/W-0                                                                                                              | U-0                                                 | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|

| T6IE          | DMA4IE                                                                                                             |                                                     | OC8IE            | OC7IE            | OC6IE            | OC5IE           | IC6IE   |  |  |  |

| bit 15        |                                                                                                                    | ·                                                   |                  |                  |                  |                 | bit 8   |  |  |  |

| R/W-0         | R/W-0                                                                                                              | R/W-0                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| IC5IE         | IC4IE                                                                                                              | IC3IE                                               | DMA3IE           | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |  |  |  |

| bit 7         | ł                                                                                                                  |                                                     |                  |                  |                  |                 | bit 0   |  |  |  |

| Legend:       |                                                                                                                    |                                                     |                  |                  |                  |                 |         |  |  |  |

| R = Readable  | e bit                                                                                                              | W = Writable                                        | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |

| -n = Value at | POR                                                                                                                | '1' = Bit is set                                    |                  | '0' = Bit is cle | eared            | x = Bit is unki | nown    |  |  |  |

| bit 15        | T6IF: Timer6                                                                                                       | Interrupt Enabl                                     | e bit            |                  |                  |                 |         |  |  |  |

|               |                                                                                                                    | request enabled                                     |                  |                  |                  |                 |         |  |  |  |

|               |                                                                                                                    | request not ena                                     |                  |                  |                  |                 |         |  |  |  |

| bit 14        |                                                                                                                    | A Channel 4 D                                       |                  | Complete Interi  | rupt Enable bit  |                 |         |  |  |  |

|               |                                                                                                                    | request enableo<br>request not ena                  |                  |                  |                  |                 |         |  |  |  |

| bit 13        |                                                                                                                    | ted: Read as '                                      |                  |                  |                  |                 |         |  |  |  |

| bit 12        | -                                                                                                                  |                                                     |                  | unt Enable bit   |                  |                 |         |  |  |  |

| 51(12         | <b>OC8IE:</b> Output Compare Channel 8 Interrupt Enable bit<br>1 = Interrupt request enabled                       |                                                     |                  |                  |                  |                 |         |  |  |  |

|               |                                                                                                                    | equest not ena                                      |                  |                  |                  |                 |         |  |  |  |

| bit 11        | OC7IE: Output Compare Channel 7 Interrupt Enable bit                                                               |                                                     |                  |                  |                  |                 |         |  |  |  |

|               |                                                                                                                    | request enabled<br>request not ena                  |                  |                  |                  |                 |         |  |  |  |

| bit 10        | •                                                                                                                  | ut Compare Ch                                       |                  | upt Enable bit   |                  |                 |         |  |  |  |

|               | 1 = Interrupt r                                                                                                    | request enabled                                     | b                |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                  | request not ena                                     |                  |                  |                  |                 |         |  |  |  |

| bit 9         | 1 = Interrupt r                                                                                                    | ut Compare Ch<br>request enableo<br>request not ena | b                | upt Enable bit   |                  |                 |         |  |  |  |

| bit 8         |                                                                                                                    | Capture Channe                                      |                  | Enable bit       |                  |                 |         |  |  |  |

|               | 1 = Interrupt r                                                                                                    | request enable<br>request not ena                   | d                |                  |                  |                 |         |  |  |  |

| bit 7         | IC5IE: Input Capture Channel 5 Interrupt Enable bit                                                                |                                                     |                  |                  |                  |                 |         |  |  |  |

|               |                                                                                                                    | request enable<br>request not ena                   |                  |                  |                  |                 |         |  |  |  |

| bit 6         | IC4IE: Input C                                                                                                     | Capture Channe                                      | el 4 Interrupt I | Enable bit       |                  |                 |         |  |  |  |

|               |                                                                                                                    | request enabled                                     |                  |                  |                  |                 |         |  |  |  |

| bit 5         | <ul> <li>0 = Interrupt request not enabled</li> <li>IC3IE: Input Capture Channel 3 Interrupt Enable bit</li> </ul> |                                                     |                  |                  |                  |                 |         |  |  |  |

|               | 1 = Interrupt r                                                                                                    | request enabled<br>request not ena                  | d                |                  |                  |                 |         |  |  |  |

| bit 4         | DMA3IE: DM                                                                                                         | A Channel 3 D                                       | ata Transfer C   | Complete Interi  | rupt Enable bit  |                 |         |  |  |  |

|               |                                                                                                                    | request enabled<br>request not ena                  |                  |                  |                  |                 |         |  |  |  |

| bit 3         | -                                                                                                                  | Event Interrup                                      |                  |                  |                  |                 |         |  |  |  |

|               |                                                                                                                    | equest enable                                       |                  |                  |                  |                 |         |  |  |  |

| U-0          | R/W-1                                                                                                                | R/W-0                 | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| _            |                                                                                                                      | T8IP<2:0>             |                |                   |                 | MI2C2IP<2:0>    |       |  |  |  |  |

| bit 15       | ·                                                                                                                    |                       |                |                   | •               |                 | bit   |  |  |  |  |

|              |                                                                                                                      |                       |                |                   |                 |                 |       |  |  |  |  |

| U-0          | R/W-1                                                                                                                | R/W-0                 | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                                                                                                      | SI2C2IP<2:0>          |                | —                 |                 | T7IP<2:0>       | 1.11  |  |  |  |  |

| bit 7        |                                                                                                                      |                       |                |                   |                 |                 | bit   |  |  |  |  |

| Legend:      |                                                                                                                      |                       |                |                   |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                                                               | W = Writable b        | oit            | U = Unimple       | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                                                                                                | '1' = Bit is set      |                | '0' = Bit is cle  | eared           | x = Bit is unkr | iown  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                            | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |

| bit 14-12    | -                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

|              | <b>T8IP&lt;2:0&gt;:</b> Timer8 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1                                                                                        |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 000 = Inter                                                                                                          | rupt source is disa   | abled          |                   |                 |                 |       |  |  |  |  |

| bit 11       | Unimpleme                                                                                                            | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |

| bit 10-8     | MI2C2IP<2:0>: I2C2 Master Events Interrupt Priority bits                                                             |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                           |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                      |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                  |                       |                |                   |                 |                 |       |  |  |  |  |

| bit 7        |                                                                                                                      | ented: Read as '0     |                |                   |                 |                 |       |  |  |  |  |

| bit 6-4      | -                                                                                                                    | :0>: I2C2 Slave E     |                | unt Priority hite |                 |                 |       |  |  |  |  |

| DIL 0-4      |                                                                                                                      |                       |                |                   |                 |                 |       |  |  |  |  |

|              | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>•</li> </ul>                            |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                   |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 000 = Interrupt source is disabled                                                                                   |                       |                |                   |                 |                 |       |  |  |  |  |

| bit 3        | Unimpleme                                                                                                            | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |

| bit 2-0      | T7IP<2:0>:                                                                                                           | Timer7 Interrupt      | Priority bits  |                   |                 |                 |       |  |  |  |  |

|              | 111 = Inter                                                                                                          | rupt is priority 7 (h | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |

|              | •                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

|              | •                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |

|              | 001 = Inter                                                                                                          | rupt is priority 1    |                |                   |                 |                 |       |  |  |  |  |

|              |                                                                                                                      | rupt source is disa   |                |                   |                 |                 |       |  |  |  |  |

### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

**EQUATION 9-3:**

**XT WITH PLL MODE**

= 40 MIPS

**EXAMPLE**

$FCY = \frac{FOSC}{2} = \frac{1}{2} \left( \frac{10000000 \cdot 32}{2 \cdot 2} \right)$

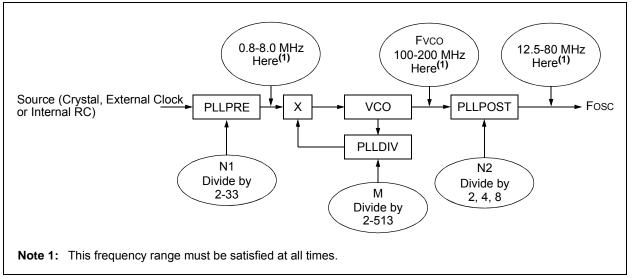

For example, suppose a 10 MHz crystal is being used with "XT with PLL" as the selected oscillator mode. If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz. If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 \* 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

### FIGURE 9-2: dsPIC33FJXXXMCX06A/X08A/X10A PLL BLOCK DIAGRAM

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Note |

|--------------------------------------------------|-------------------|-------------|------------|----------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | xx          | 111        | 1, 2     |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | xx          | 110        | 1        |

| Low-Power RC Oscillator (LPRC)                   | Internal          | XX          | 101        | 1        |

| Secondary (Timer1) Oscillator (Sosc)             | Secondary         | xx          | 100        | 1        |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | -        |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -        |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1        |

| Primary Oscillator (HS)                          | Primary           | 10          | 010        | _        |

| Primary Oscillator (XT)                          | Primary           | 01          | 010        | —        |

| Primary Oscillator (EC)                          | Primary           | 00          | 010        | 1        |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal          | XX          | 001        | 1        |

| Fast RC Oscillator (FRC)                         | Internal          | xx          | 000        | 1        |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | SPI1MD: SPI1 Module Disable bit               |

|-------|-----------------------------------------------|

|       | 1 = SPI1 module is disabled                   |

|       | 0 = SPI1 module is enabled                    |

| bit 2 | C2MD: ECAN2 Module Disable bit                |

|       | 1 = ECAN2 module is disabled                  |

|       | 0 = ECAN2 module is enabled                   |

| bit 1 | C1MD: ECAN1 Module Disable bit                |

|       | 1 = ECAN1 module is disabled                  |

|       | 0 = ECAN1 module is enabled                   |

| bit 0 | AD1MD: ADC1 Module Disable bit <sup>(1)</sup> |

|       | 1 = ADC1 module is disabled                   |

|       | 0 = ADC1 module is enabled                    |

**Note 1:** The PCFGx bits have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit                                                        |

|-------|----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Output Compare 4 module is disabled</li><li>0 = Output Compare 4 module is enabled</li></ul> |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul> |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul> |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                        |

|       | 1 = Output Compare 1 module is disabled                                                                  |

|       | 0 = Output Compare 1 module is enabled                                                                   |

|       |                                                                                                          |

| R/W-0           | U-0                                                                                          | R/W-0                                                                                  | R-0                                                                | R/W-0                                            | R/W-0                                  | R/W-0                          | R/W-0                  |  |  |

|-----------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|--------------------------------|------------------------|--|--|

| CNTERR          | _                                                                                            | QEISIDL                                                                                | INDEX                                                              | UPDN                                             |                                        | QEIM<2:0>                      | •                      |  |  |

| bit 15          |                                                                                              |                                                                                        |                                                                    |                                                  |                                        |                                | bit 8                  |  |  |

|                 |                                                                                              |                                                                                        |                                                                    |                                                  |                                        |                                |                        |  |  |

| R/W-0           | R/W-0                                                                                        | R/W-0                                                                                  | R/W-0                                                              | R/W-0                                            | R/W-0                                  | R/W-0                          | R/W-0                  |  |  |

| SWPAB           | PCDOUT                                                                                       | TQGATE                                                                                 | TQCK                                                               | PS<1:0>                                          | POSRES                                 | TQCS                           | UPDN_SRC <sup>(1</sup> |  |  |

| bit 7           |                                                                                              |                                                                                        |                                                                    |                                                  |                                        |                                | bit (                  |  |  |

| Legend:         |                                                                                              |                                                                                        |                                                                    |                                                  |                                        |                                |                        |  |  |

| R = Readable    | bit                                                                                          | W = Writable                                                                           | bit                                                                | U = Unimple                                      | mented bit, read                       | d as '0'                       |                        |  |  |

| -n = Value at F | POR                                                                                          | '1' = Bit is set                                                                       |                                                                    | '0' = Bit is cle                                 | eared                                  | x = Bit is un                  | known                  |  |  |

| bit 15          | 1 = Position c<br>0 = No positio                                                             | ount Error Statu<br>count error has<br>on count error h<br>g only applies              | occurred<br>has occurred                                           | <b>2:0&gt; =</b> '110' oi                        | r'100')                                |                                |                        |  |  |

| bit 14          | -                                                                                            | ted: Read as '                                                                         |                                                                    |                                                  | ,                                      |                                |                        |  |  |

| bit 13          | QEISIDL: Sto                                                                                 | p in Idle Mode                                                                         | bit                                                                |                                                  |                                        |                                |                        |  |  |

|                 |                                                                                              | ue module ope<br>module operat                                                         |                                                                    |                                                  | dle mode                               |                                |                        |  |  |

| bit 12          | INDEX: Index Pin State Status bit (read-only)                                                |                                                                                        |                                                                    |                                                  |                                        |                                |                        |  |  |

|                 | 1 = Index pin<br>0 = Index pin                                                               | -                                                                                      |                                                                    |                                                  |                                        |                                |                        |  |  |

| bit 11          | UPDN: Position Counter Direction Status bit                                                  |                                                                                        |                                                                    |                                                  |                                        |                                |                        |  |  |

|                 | 0 = Position c                                                                               | ounter directio<br>ounter directio<br>t when QEIM<                                     | n is negative                                                      | (-)                                              | when QEIM<2:                           | <b>0&gt; =</b> 001.)           |                        |  |  |

| bit 10-8        | QEIM<2:0>: Quadrature Encoder Interface Mode Select bits                                     |                                                                                        |                                                                    |                                                  |                                        |                                |                        |  |  |

|                 | 110 = Quadra<br>101 = Quadra<br>100 = Quadra<br>011 = Unuser<br>010 = Unuser<br>001 = Starts | ature Encoder<br>Iture Encoder Ir<br>ature Encoder<br>d (module disa<br>d (module disa | Interface ena<br>Iterface enabl<br>Interface ena<br>bled)<br>bled) | bled (x4 mode<br>ed (x2 mode) w<br>bled (x2 mode | ) with Index Pul                       | se Reset of p<br>nter Reset by | match (MAXCNT          |  |  |

| bit 7           | SWPAB: Phase A and Phase B Input Swap Select bit                                             |                                                                                        |                                                                    |                                                  |                                        |                                |                        |  |  |

|                 |                                                                                              | and Phase B ir<br>and Phase B ir                                                       |                                                                    |                                                  |                                        |                                |                        |  |  |

| bit 6           | PCDOUT: Po                                                                                   | sition Counter                                                                         | Direction Sta                                                      | te Output Enal                                   | ble bit                                |                                |                        |  |  |

|                 |                                                                                              |                                                                                        |                                                                    |                                                  | l logic controls s<br>ormal I/O pin op |                                | 1)                     |  |  |

| bit 5           | TQGATE: Tin                                                                                  | ner Gated Time                                                                         | e Accumulatio                                                      | on Enable bit                                    |                                        |                                |                        |  |  |

|                 | •                                                                                            | ed time accum<br>ed time accum                                                         |                                                                    | ed                                               |                                        |                                |                        |  |  |

### REGISTER 17-1: QEIXCON: QEIX CONTROL REGISTER

Note 1: When configured for QEI mode, the control bit is a 'don't care'.

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0 = Send ACK during Acknowledge                                                                                                                                                                                                             |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                 |

|       | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul>                             |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                 |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte</li> <li>0 = Receive sequence not in progress</li> </ul>                                                              |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                           |

|       | <ul> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence</li> <li>0 = Stop condition not in progress</li> </ul>                                                                            |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                |

|       | 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence                                                                                                                        |

|       | 0 = Repeated Start condition not in progress                                                                                                                                                                                                |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                 |

|       | <ul> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li> <li>0 = Start condition not in progress</li> </ul>                                                                         |

| REGISTER                           | 21-5: CiFIFC                                                                          | ): ECAN™ FIF           | O STATU     | IS REGISTER      |                |                 |       |

|------------------------------------|---------------------------------------------------------------------------------------|------------------------|-------------|------------------|----------------|-----------------|-------|

| U-0                                | U-0                                                                                   | R-0                    | R-0         | R-0              | R-0            | R-0             | R-0   |

| _                                  | _                                                                                     |                        |             | FBF              | °<5:0>         |                 |       |

| bit 15                             |                                                                                       |                        |             |                  |                |                 | bit 8 |

| U-0                                | U-0                                                                                   | R-0                    | R-0         | R-0              | R-0            | R-0             | R-0   |

| _                                  |                                                                                       |                        |             | FNR              | B<5:0>         |                 |       |

| bit 7                              |                                                                                       | •                      |             |                  |                |                 | bit ( |

| Legend:                            |                                                                                       |                        |             |                  |                |                 |       |

| R = Readable bit W = Writable bit  |                                                                                       |                        |             | U = Unimpler     | nented bit, re | ad as '0'       |       |

| -n = Value at POR (1' = Bit is set |                                                                                       |                        |             | '0' = Bit is cle | ared           | x = Bit is unkn | iown  |

| bit 13-8                           | <pre>FBP&lt;3:0&gt;: FI 011111 = RB 011110 = RB</pre>                                 | 30 buffer<br>B1 buffer | Pointer bit | S                |                |                 |       |

| bit 7-6                            | Unimplemen                                                                            | ted: Read as '0'       |             |                  |                |                 |       |

| bit 5-0                            | FNRB<5:0>:<br>011111 = RB<br>011110 = RB<br>•<br>•<br>•<br>000001 = TR<br>000000 = TR | B1 buffer              | Buffer Po   | inter bits       |                |                 |       |

### REGISTER 21-24: CIRXOVF1: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                                                        | C= Clearable bit     |                    |  |  |

|-------------------|--------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | it W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-0 RXOVF15:RXOVF0: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

#### **REGISTER 21-25:** CiRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                                                     | C= Clearable bit     | C= Clearable bit   |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

bit 15-0 RXOVF31:RXOVF16: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

## TABLE 26-21:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHA               | RACTER                | ISTICS                                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                                    |                       |                |                                                                                        |  |  |

|----------------------|-----------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------|----------------|----------------------------------------------------------------------------------------|--|--|

| Param<br>No.         | Symbol                | Characteristic <sup>(1)</sup>                                            | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup>                                 | Max                   | Units          | Conditions                                                                             |  |  |

| SY10                 | ТмсL                  | MCLR Pulse Width (low)                                                   | 2                                                                                                                                                                                                                                                                                       | _                                                  |                       | μS             | -40°C to +85°C                                                                         |  |  |

| SY11<br>SY12<br>SY13 | Tpwrt<br>Tpor<br>Tioz | Power-up Timer Period<br>Power-on Reset Delay<br>I/O High-Impedance from |                                                                                                                                                                                                                                                                                         | 2<br>4<br>8<br>16<br>32<br>64<br>128<br>10<br>0.72 | <br><br><br>30<br>1.2 | ms<br>μs<br>μs | -40°C to +85°C<br>User programmable<br>-40°C to +85°C<br>—                             |  |  |

| SY20                 | Twdt1                 | MCLR Low or Watchdog<br>Timer Reset<br>Watchdog Timer Time-out<br>Period | -                                                                                                                                                                                                                                                                                       |                                                    |                       |                | See Section 23.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21 (Table 26-19) |  |  |

| SY30                 | Tost                  | Oscillator Start-up Timer<br>Period                                      | -                                                                                                                                                                                                                                                                                       | 1024 Tosc                                          | —                     | -              | Tosc = OSC1 period                                                                     |  |  |

| SY35                 | TFSCM                 | Fail-Safe Clock Monitor<br>Delay                                         |                                                                                                                                                                                                                                                                                         | 500                                                | 900                   | μS             | -40°C to +85°C                                                                         |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

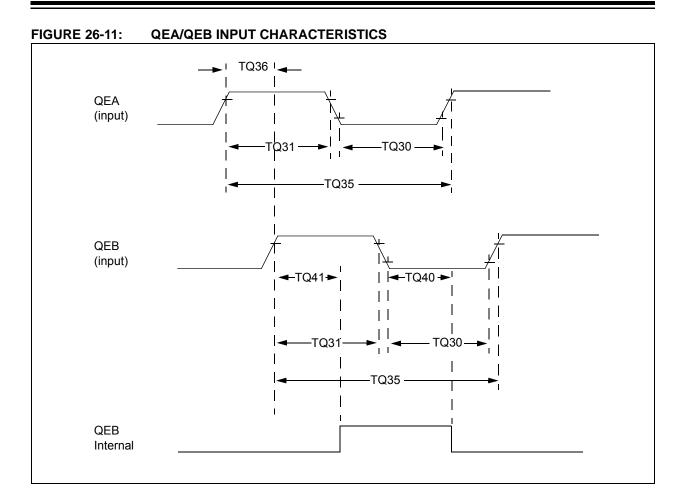

### TABLE 26-29: QUADRATURE DECODER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                     | (unle | dard Operating<br>ss otherwise s<br>ating temperatu | stated)<br>re -40°0 | C ≤ TA ≤ · | <b>to 3.6V</b><br>+85°C for Industrial<br>125°C for Extended |

|--------------------|--------|-----------------------------------------------------|-------|-----------------------------------------------------|---------------------|------------|--------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                       |       | Тур <sup>(2)</sup>                                  | Мах                 | Units      | Conditions                                                   |

| TQ30               | TQUL   | Quadrature Input Low Time                           |       | 6 Tcy                                               | _                   | ns         | —                                                            |

| TQ31               | ΤουΗ   | Quadrature Input High Time                          |       | 6 Tcy                                               |                     | ns         | —                                                            |

| TQ35               | TQUIN  | Quadrature Input Period                             |       | 12 TCY                                              | _                   | ns         | —                                                            |

| TQ36               | TQUP   | Quadrature Phase Period                             |       | 3 TCY                                               | —                   | ns         | —                                                            |

| TQ40               | TQUFL  | Filter Time to Recognize Low<br>with Digital Filter | /     | 3 * N * Tcy                                         | —                   | ns         | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 3)</b>      |

| TQ41               | TQUFH  | Filter Time to Recognize Hig with Digital Filter    | h     | 3 * N * Tcy                                         | —                   | ns         | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 3)</b>      |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.