Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc710a-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0             | U-0                         | U-0                                    | R/W-0          | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|-----------------------------|----------------------------------------|----------------|---------------------|------------------|------------------|-------|

| _               |                             | —                                      | US             | EDT <sup>(1)</sup>  |                  | DL<2:0>          |       |

| bit 15          |                             |                                        |                |                     |                  |                  | bit   |

| R/W-0           | R/W-0                       | R/W-1                                  | R/W-0          | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                        | SATDW                                  | ACCSAT         | IPL3 <sup>(2)</sup> | PSV              | RND              | IF    |

| bit 7           |                             |                                        |                |                     | I                |                  | bit ( |

| Legend:         |                             | C = Clearabl                           | a hit          |                     |                  |                  |       |

| R = Readabl     | e bit                       | W = Writable                           |                | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle |                             | 'x = Bit is unk                        |                |                     | mented bit, read |                  |       |

|                 |                             |                                        |                |                     | ,                |                  |       |

| bit 15-13       | -                           | ted: Read as                           |                |                     |                  |                  |       |

| bit 12          |                             | tiply Unsigned                         | •              | ol bit              |                  |                  |       |

|                 | U U                         | ne multiplies a<br>ne multiplies a     | 0              |                     |                  |                  |       |

| bit 11          | •                           | C Loop Termina                         | •              | <sub>oit</sub> (1)  |                  |                  |       |

|                 | •                           | •                                      |                | f current loop it   | eration          |                  |       |

|                 | 0 = No effect               | <b>J</b>                               |                |                     |                  |                  |       |

| bit 10-8        | <b>DL&lt;2:0&gt;:</b> DO    | Loop Nesting                           | Level Status b | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b> | ops active                             |                |                     |                  |                  |       |

|                 | •                           |                                        |                |                     |                  |                  |       |

|                 | 001 = 1 DO lo               | op active                              |                |                     |                  |                  |       |

|                 | 000 <b>= 0</b> DO <b>lo</b> | ops active                             |                |                     |                  |                  |       |

| bit 7           |                             | Saturation Ena                         |                |                     |                  |                  |       |

|                 |                             | ator A saturation<br>ator A saturation |                |                     |                  |                  |       |

| bit 6           |                             | Saturation Ena                         |                |                     |                  |                  |       |

|                 |                             | ator B saturatio                       |                |                     |                  |                  |       |

|                 | 0 = Accumula                | ator B saturation                      | on disabled    |                     |                  |                  |       |

| bit 5           | SATDW: Data                 | a Space Write                          | from DSP Eng   | ine Saturation      | Enable bit       |                  |       |

|                 |                             | ce write satura                        |                |                     |                  |                  |       |

| bit 4           |                             | ce write satura<br>cumulator Satu      |                | Soloct bit          |                  |                  |       |

|                 |                             | ration (super s                        |                |                     |                  |                  |       |

|                 |                             | ration (normal                         |                |                     |                  |                  |       |

| bit 3           | IPL3: CPU In                | terrupt Priority                       | Level Status I | oit 3 <b>(2)</b>    |                  |                  |       |

|                 |                             | rupt priority le                       | U U            |                     |                  |                  |       |

| 1.11.0          |                             | rupt priority le                       |                |                     |                  |                  |       |

| bit 2           | -                           | -                                      | •              | ace Enable bit      |                  |                  |       |

|                 | •                           | space visible i<br>space not visit     | •              | се                  |                  |                  |       |

| bit 1           | -                           | ng Mode Sele                           | -              |                     |                  |                  |       |

|                 |                             | onventional) re                        |                | ed                  |                  |                  |       |

|                 |                             | (convergent)                           | -              |                     |                  |                  |       |

| bit 0           | •                           | Fractional Mu                          | •              |                     |                  |                  |       |

|                 |                             | ode enabled for<br>I mode enable       |                |                     |                  |                  |       |

|                 |                             | i noue enable                          | ייסט ווחו      | upiy ops            |                  |                  |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

NOTES:

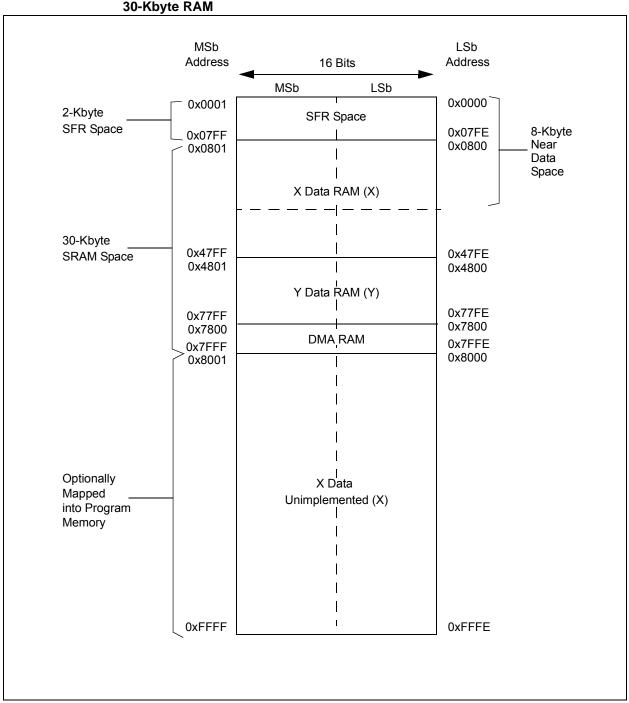

## FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 30-Kbyte RAM

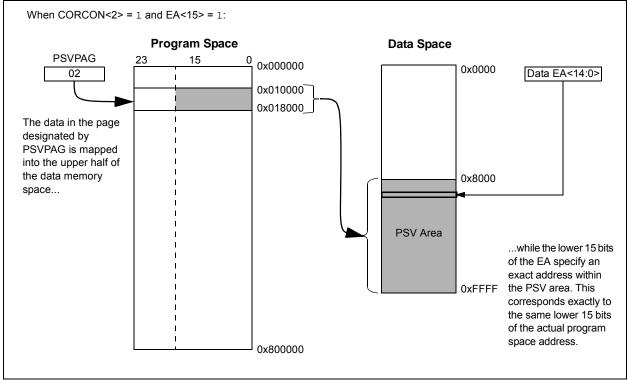

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

## Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV and are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data using PSV to execute in a single cycle.

#### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

© 2009-2012 Microchip Technology Inc.

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address           | AIVT Address          | Interrupt Source                   |

|------------------|--------------------------------------|-----------------------|-----------------------|------------------------------------|

| 54               | 46                                   | 0x000070              | 0x000170              | DMA4 – DMA Channel 4               |

| 55               | 47                                   | 0x000072              | 0x000172              | T6 – Timer6                        |

| 56               | 48                                   | 0x000074              | 0x000174              | T7 – Timer7                        |

| 57               | 49                                   | 0x000076              | 0x000176              | SI2C2 – I2C2 Slave Events          |

| 58               | 50                                   | 0x000078              | 0x000178              | MI2C2 – I2C2 Master Events         |

| 59               | 51                                   | 0x00007A              | 0x00017A              | T8 – Timer8                        |

| 60               | 52                                   | 0x00007C              | 0x00017C              | T9 – Timer9                        |

| 61               | 53                                   | 0x00007E              | 0x00017E              | INT3 – External Interrupt 3        |

| 62               | 54                                   | 0x000080              | 0x000180              | INT4 – External Interrupt 4        |

| 63               | 55                                   | 0x000082              | 0x000182              | C2RX – ECAN2 Receive Data Ready    |

| 64               | 56                                   | 0x000084              | 0x000184              | C2 – ECAN2 Event                   |

| 65               | 57                                   | 0x000086              | 0x000186              | PWM – PWM Period Match             |

| 66               | 58                                   | 0x000088              | 0x000188              | QEI – Position Counter Compare     |

| 69               | 61                                   | 0x00008E              | 0x00018E              | DMA5 – DMA Channel 5               |

| 70               | 62                                   | 0x000090              | 0x000190              | Reserved                           |

| 71               | 63                                   | 0x000092              | 0x000192              | FLTA – MCPWM Fault A               |

| 72               | 64                                   | 0x000094              | 0x000194              | FLTB – MCPWM Fault B               |

| 73               | 65                                   | 0x000096              | 0x000196              | U1E – UART1 Error                  |

| 74               | 66                                   | 0x000098              | 0x000198              | U2E – UART2 Error                  |

| 75               | 67                                   | 0x00009A              | 0x00019A              | Reserved                           |

| 76               | 68                                   | 0x00009C              | 0x00019C              | DMA6 – DMA Channel 6               |

| 77               | 69                                   | 0x00009E              | 0x00019E              | DMA7 – DMA Channel 7               |

| 78               | 70                                   | 0x0000A0              | 0x0001A0              | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                                   | 0x0000A2              | 0x0001A2              | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 72-117                               | 0x0000A4-<br>0x0000FE | 0x0001A4-<br>0x0001FE | Reserved                           |

#### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

#### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

| REGISTER 7-12: | IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| R/W-0         | R/W-0           | U-0                                                 | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|-----------------|-----------------------------------------------------|------------------|------------------|------------------|-----------------|---------|

| T6IE          | DMA4IE          |                                                     | OC8IE            | OC7IE            | OC6IE            | OC5IE           | IC6IE   |

| bit 15        |                 | ·                                                   |                  |                  |                  |                 | bit 8   |

| R/W-0         | R/W-0           | R/W-0                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IE         | IC4IE           | IC3IE                                               | DMA3IE           | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |

| bit 7         | ł               |                                                     |                  |                  |                  |                 | bit 0   |

| Legend:       |                 |                                                     |                  |                  |                  |                 |         |

| R = Readable  | e bit           | W = Writable                                        | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                                    |                  | '0' = Bit is cle | eared            | x = Bit is unki | nown    |

| bit 15        | T6IF: Timer6    | Interrupt Enabl                                     | e bit            |                  |                  |                 |         |

|               |                 | request enabled                                     |                  |                  |                  |                 |         |

|               |                 | request not ena                                     |                  |                  |                  |                 |         |

| bit 14        |                 | A Channel 4 D                                       |                  | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | request enableo<br>request not ena                  |                  |                  |                  |                 |         |

| bit 13        |                 | ted: Read as '                                      |                  |                  |                  |                 |         |

| bit 12        | -               | ut Compare Ch                                       |                  | unt Enable bit   |                  |                 |         |

| 51(12         | •               | request enabled                                     |                  |                  |                  |                 |         |

|               |                 | equest not ena                                      |                  |                  |                  |                 |         |

| bit 11        | •               | ut Compare Ch                                       |                  | upt Enable bit   |                  |                 |         |

|               |                 | request enabled<br>request not ena                  |                  |                  |                  |                 |         |

| bit 10        | •               | ut Compare Ch                                       |                  | upt Enable bit   |                  |                 |         |

|               | 1 = Interrupt r | request enabled                                     | b                |                  |                  |                 |         |

|               | •               | request not ena                                     |                  |                  |                  |                 |         |

| bit 9         | 1 = Interrupt r | ut Compare Ch<br>request enableo<br>request not ena | b                | upt Enable bit   |                  |                 |         |

| bit 8         |                 | Capture Channe                                      |                  | Enable bit       |                  |                 |         |

|               | 1 = Interrupt r | request enable<br>request not ena                   | d                |                  |                  |                 |         |

| bit 7         | IC5IE: Input C  | Capture Channe                                      | el 5 Interrupt I | Enable bit       |                  |                 |         |

|               |                 | request enable<br>request not ena                   |                  |                  |                  |                 |         |

| bit 6         | IC4IE: Input C  | Capture Channe                                      | el 4 Interrupt I | Enable bit       |                  |                 |         |

|               |                 | request enableo<br>request not ena                  |                  |                  |                  |                 |         |

| bit 5         | •               | Capture Channe                                      |                  | Enable bit       |                  |                 |         |

|               | 1 = Interrupt r | request enabled<br>request not ena                  | d                |                  |                  |                 |         |

| bit 4         | DMA3IE: DM      | A Channel 3 D                                       | ata Transfer C   | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | request enabled<br>request not ena                  |                  |                  |                  |                 |         |

| bit 3         | -               | Event Interrup                                      |                  |                  |                  |                 |         |

|               |                 | equest enable                                       |                  |                  |                  |                 |         |

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0               | U-0             | U-0                               | U-0            | U-0              | U-0             | U-0             | U-0    |

|-------------------|-----------------|-----------------------------------|----------------|------------------|-----------------|-----------------|--------|

| —                 | —               | _                                 | —              | —                | —               | —               | _      |

| bit 15            |                 |                                   | •              | •                |                 |                 | bit 8  |

|                   |                 |                                   |                |                  |                 |                 |        |

| R/W-0             | R/W-0           | R/W-0                             | R/W-0          | U-0              | R/W-0           | R/W-0           | R/W-0  |

| C2TXIE            | C1TXIE          | DMA7IE                            | DMA6IE         | —                | U2EIE           | U1EIE           | FLTBIE |

| bit 7             |                 |                                   |                |                  |                 |                 | bit (  |

| Legend:           |                 |                                   |                |                  |                 |                 |        |

| R = Readab        | le bit          | W = Writable                      | bit            | U = Unimpler     | mented bit, rea | d as '0'        |        |

| -n = Value a      | t POR           | '1' = Bit is set                  |                | '0' = Bit is cle | ared            | x = Bit is unki | nown   |

| bit 15-8<br>bit 7 | •               | ted: Read as '                    |                | nterrunt Enabl   | e hit           |                 |        |

| bit 7             | C2TXIE: ECA     | N2 Transmit D                     | ata Request li | nterrupt Enable  | e bit           |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 6             | C1TXIE: ECA     | N1 Transmit D                     | ata Request I  | nterrupt Enable  | e bit           |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 5             | DMA7IE: DM      | A Channel 7 D                     | ata Transfer C | complete Enab    | le Status bit   |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 4             | DMA6IE: DM      | A Channel 6 D                     | ata Transfer C | complete Enab    | le Status bit   |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 3             | Unimplemen      | ted: Read as '                    | 0'             |                  |                 |                 |        |

| bit 2             | U2EIE: UART     | Γ2 Error Interru                  | pt Enable bit  |                  |                 |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 1             | •               | T1 Error Interru                  |                |                  |                 |                 |        |

|                   | 1 = Interrupt ı | request enable<br>request not ena | d              |                  |                 |                 |        |

| bit 0             | •               | V Fault B Interr                  |                |                  |                 |                 |        |

| -                 | ו = Interrupt ו | request enable<br>request not ena | d              |                  |                 |                 |        |

| U-0          | R/W-1              | R/W-0                     | R/W-0          | U-0              | U-0             | U-0             | U-0   |

|--------------|--------------------|---------------------------|----------------|------------------|-----------------|-----------------|-------|

| _            |                    | FLTAIP<2:0>               |                | _                | —               | —               |       |

| bit 15       | ·                  |                           |                | ·                |                 | •               | bit 8 |

|              |                    |                           |                |                  |                 |                 |       |

| U-0          | R/W-1              | R/W-0                     | R/W-0          | U-0              | U-1             | U-0             | U-0   |

| —            |                    | DMA5IP<2:0>               |                |                  |                 |                 | —     |

| bit 7        |                    |                           |                |                  |                 |                 | bit 0 |

|              |                    |                           |                |                  |                 |                 |       |

| Legend:      |                    |                           |                |                  |                 |                 |       |

| R = Readab   | le bit             | W = Writable              | bit            | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value a | t POR              | '1' = Bit is set          |                | '0' = Bit is cle | ared            | x = Bit is unkn | own   |

|              |                    |                           |                |                  |                 |                 |       |

| bit 15       | Unimpleme          | ented: Read as '          | 0'             |                  |                 |                 |       |

| bit 14-12    | FLTAIP<2:0         | <b>D&gt;:</b> PWM Fault A | Interrupt Pri  | ority bits       |                 |                 |       |

|              | 111 = Inter        | rupt is priority 7 (      | highest priori | ty interrupt)    |                 |                 |       |

|              | •                  |                           |                |                  |                 |                 |       |

|              | •                  |                           |                |                  |                 |                 |       |

|              | 001 = Inter        | rupt is priority 1        |                |                  |                 |                 |       |

|              | 000 <b>= Inter</b> | rupt source is dis        | abled          |                  |                 |                 |       |

| bit 11-7     | Unimpleme          | ented: Read as '          | 0'             |                  |                 |                 |       |

| bit 6-4      | DMA5IP<2           | :0>: DMA Chann            | el 5 Data Tra  | nsfer Complete   | Interrupt Prior | rity bits       |       |

|              | 111 = Inter        | rupt is priority 7 (      | highest priori | ty interrupt)    |                 |                 |       |

|              | •                  |                           |                |                  |                 |                 |       |

|              | •                  |                           |                |                  |                 |                 |       |

|              |                    | rupt is priority 1        |                |                  |                 |                 |       |

|              | 000 <b>= Inter</b> | rupt source is dis        | abled          |                  |                 |                 |       |

| bit 3-0      | Unimpleme          | ented: Read as '          | 0'             |                  |                 |                 |       |

|              |                    |                           |                |                  |                 |                 |       |

#### REGISTER 7-30: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| R/W-0              | U-0                              | R/W-0                             | U-0              | U-0                            | U-0           | U-0                  | U-0            |

|--------------------|----------------------------------|-----------------------------------|------------------|--------------------------------|---------------|----------------------|----------------|

| TON <sup>(1)</sup> | _                                | TSIDL <sup>(2)</sup>              |                  | _                              | _             | _                    | _              |

| bit 15             |                                  |                                   |                  | •                              |               |                      | bit 8          |

|                    |                                  |                                   |                  |                                |               |                      |                |

| U-0                | R/W-0                            | R/W-0                             | R/W-0            | U-0                            | U-0           | R/W-0                | U-0            |

|                    | TGATE <sup>(1)</sup>             | TCKPS                             | <1:0> <b>(1)</b> | —                              |               | TCS <sup>(1,3)</sup> |                |

| bit 7              |                                  |                                   |                  |                                |               |                      | bit (          |

|                    |                                  |                                   |                  |                                |               |                      |                |

| Legend:            | . 1. 11                          |                                   |                  |                                |               |                      |                |

| R = Readable       |                                  | W = Writable                      | DIt              | U = Unimplen                   |               |                      |                |

| -n = Value at      | POR                              | '1' = Bit is set                  |                  | '0' = Bit is clea              | ared          | x = Bit is unkno     | own            |

| bit 15             | TON: Timery                      | On bit <sup>(1)</sup>             |                  |                                |               |                      |                |

|                    | 1 = Starts 16-                   |                                   |                  |                                |               |                      |                |

|                    | 0 = Stops 16-                    |                                   |                  |                                |               |                      |                |

| bit 14             | Unimplemen                       | ted: Read as '                    | )'               |                                |               |                      |                |

| bit 13             | TSIDL: Stop i                    | in Idle Mode bit                  | (2)              |                                |               |                      |                |

|                    |                                  |                                   |                  | device enters Id               | le mode       |                      |                |

|                    | 0 = Continue                     | module operati                    | on in Idle mo    | ode                            |               |                      |                |

| bit 12-7           | -                                | ted: Read as '                    |                  |                                |               |                      |                |

| bit 6              | TGATE: Time                      | ery Gated Time                    | Accumulatio      | n Enable bit <sup>(1)</sup>    |               |                      |                |

|                    | When TCS =                       |                                   |                  |                                |               |                      |                |

|                    | This bit is ign                  |                                   |                  |                                |               |                      |                |

|                    | When TCS =<br>1 = Gated tim      | <u>0:</u><br>ne accumulatior      | enabled          |                                |               |                      |                |

|                    |                                  | ne accumulation                   |                  |                                |               |                      |                |

| bit 5-4            | TCKPS<1:0>                       | : Timer3 Input                    | Clock Presca     | ale Select bits <sup>(1)</sup> |               |                      |                |

|                    | 11 <b>= 1:256</b>                | ·                                 |                  |                                |               |                      |                |

|                    | 10 <b>= 1:64</b>                 |                                   |                  |                                |               |                      |                |

|                    | 01 = 1:8                         |                                   |                  |                                |               |                      |                |

| <b>h</b> :+ 0 0    | 00 = 1:1                         | tod. Dood oo '                    | <b>、</b>         |                                |               |                      |                |

| bit 3-2            | •                                | ted: Read as '0<br>Clock Source S |                  |                                |               |                      |                |

| bit 1              | ,                                |                                   |                  |                                |               |                      |                |

|                    | 1 = External c<br>0 = Internal c | clock from TyCł<br>lock (Ecy)     | C pin (on the    | nsing edge)                    |               |                      |                |

| bit 0              |                                  | ited: Read as '                   | )'               |                                |               |                      |                |

|                    | P                                |                                   | -                |                                |               |                      |                |

|                    |                                  |                                   |                  | = 1), these bits               | have no effec | t on Timery operat   | tion; all time |

| fur                | nctions are set th               | hrough T2CON                      |                  |                                |               |                      |                |

REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

## 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

| R/W-0         | R/W-0               | R/W-0             | R/W-0                | R/W-0                              | R/W-0                | R/W-0                | R/W-0                |

|---------------|---------------------|-------------------|----------------------|------------------------------------|----------------------|----------------------|----------------------|

| FBOV4H        | FBOV4L              | FBOV3H            | FBOV3L               | FBOV2H                             | FBOV2L               | FBOV1H               | FBOV1L               |

| bit 15        |                     |                   |                      |                                    |                      |                      | bit 8                |

|               |                     |                   |                      |                                    |                      |                      |                      |

| R/W-0         | U-0                 | U-0               | U-0                  | R/W-0                              | R/W-0                | R/W-0                | R/W-0                |

| FLTBM         | —                   | —                 | —                    | FBEN4 <sup>(1)</sup>               | FBEN3 <sup>(1)</sup> | FBEN2 <sup>(1)</sup> | FBEN1 <sup>(1)</sup> |

| bit 7         |                     |                   |                      |                                    |                      |                      | bit (                |

| Legend:       |                     |                   |                      |                                    |                      |                      |                      |

| R = Readable  | bit                 | W = Writable      | hit                  |                                    | nented bit, read     | l as '0'             |                      |

| -n = Value at |                     | '1' = Bit is set  |                      | '0' = Bit is clea                  |                      | x = Bit is unkr      | own                  |

|               |                     |                   |                      |                                    | arcu                 |                      | lowin                |

| bit 15-8      | FBOVxH<4:1          | >:FBOVxI <4:      | 1>: Fault Inpu       | t B PWM Over                       | ride Value bits      |                      |                      |

|               |                     |                   | •                    |                                    | ault input even      | t                    |                      |

|               |                     |                   |                      |                                    | Fault input eve      |                      |                      |

| bit 7         | FLTBM: Faul         | t B Mode bit      |                      |                                    |                      |                      |                      |

|               |                     |                   |                      | Cycle-by-Cycle                     |                      |                      |                      |

|               |                     | • •               |                      | ol pins to the sta                 | ates programm        | ed in FLTBCON        | V<15:8>              |

| bit 6-4       | •                   | ted: Read as '    |                      |                                    |                      |                      |                      |

| bit 3         |                     | t Input B Enabl   |                      | . –                                | _                    |                      |                      |

|               |                     |                   |                      | by Fault Input<br>lled by Fault In |                      |                      |                      |

| bit 2         |                     | t Input B Enabl   |                      |                                    | put D                |                      |                      |

|               |                     |                   |                      | by Fault Input                     | B                    |                      |                      |

|               |                     |                   |                      | lled by Fault In                   |                      |                      |                      |

| bit 1         | FBEN2: Fault        | t Input B Enabl   | e bit <sup>(1)</sup> |                                    |                      |                      |                      |

|               |                     |                   |                      | by Fault Input                     |                      |                      |                      |

|               |                     |                   |                      | lled by Fault In                   | put B                |                      |                      |

| bit 0         |                     | t Input B Enabl   |                      |                                    |                      |                      |                      |

|               |                     |                   |                      | by Fault Input<br>lled by Fault In |                      |                      |                      |

|               | $\alpha = PWW11H/P$ | 21/1/1/11 nin noi | r in not contro      |                                    |                      |                      |                      |

#### REGISTER 16-10: PxFLTBCON: PWMx FAULT B CONTROL REGISTER

**Note 1:** Fault A pin has priority over Fault B pin, if enabled.

#### 25.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 25.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 25.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 25.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 25.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

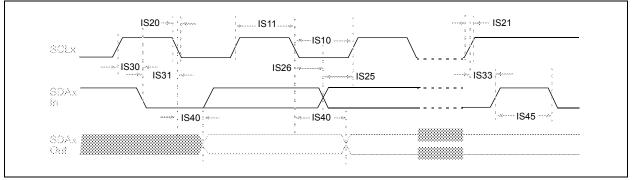

# FIGURE 26-24: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

| AC CH        | ARACTER       | RISTICS                                              | (unless oth                       | nerwise    | ture -40°C ≤                     | Ta≤ -    | <b>/ to 3.6V</b><br>+85°C for Industrial<br>125°C for Extended                               |  |  |  |  |  |

|--------------|---------------|------------------------------------------------------|-----------------------------------|------------|----------------------------------|----------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| Param<br>No. | Symbol        | Characteristic                                       | Min.                              | Тур        | Max.                             | Units    | Conditions                                                                                   |  |  |  |  |  |

|              | Device Supply |                                                      |                                   |            |                                  |          |                                                                                              |  |  |  |  |  |

| AD01         | AVDD          | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 3.0 | —          | Lesser of<br>VDD + 0.3<br>or 3.6 | V        | —                                                                                            |  |  |  |  |  |

| AD02         | AVss          | Module Vss Supply                                    | Vss - 0.3                         | —          | Vss + 0.3                        | V        |                                                                                              |  |  |  |  |  |

|              |               |                                                      | Reference                         | ce Inpu    | ts                               |          |                                                                                              |  |  |  |  |  |

| AD05         | VREFH         | Reference Voltage High                               | AVss + 2.5                        | _          | AVdd                             | V        | _                                                                                            |  |  |  |  |  |

| AD05a        |               |                                                      | 3.0                               | —          | 3.6                              | V        | Vrefh = AVdd<br>Vrefl = AVss = 0                                                             |  |  |  |  |  |

| AD06         | VREFL         | Reference Voltage Low                                | AVss                              | _          | AVDD – 2.5                       | V        | —                                                                                            |  |  |  |  |  |

| AD06a        |               |                                                      | 0                                 | —          | 0                                | V        | Vrefh = AVdd<br>Vrefl = AVss = 0                                                             |  |  |  |  |  |

| AD07         | Vref          | Absolute Reference<br>Voltage                        | 2.5                               | _          | 3.6                              | V        | Vref = Vrefh - Vrefl                                                                         |  |  |  |  |  |

| AD08         | IREF          | Current Drain                                        | —                                 | _          | 10                               | μA       | ADC off                                                                                      |  |  |  |  |  |

| AD08a        | IAD           | Operating Current                                    |                                   | 7.0<br>2.7 | 9.0<br>3.2                       | mA<br>mA | 10-bit ADC mode, see <b>Note 1</b><br>12-bit ADC mode, see <b>Note 1</b>                     |  |  |  |  |  |

|              |               |                                                      | Analog                            | g Input    |                                  |          |                                                                                              |  |  |  |  |  |

| AD12         | VINH          | Input Voltage Range VINH                             | VINL                              | _          | VREFH                            | $\vee$   | This voltage reflects Sample<br>and Hold Channels 0, 1, 2 and<br>3 (CH0-CH3), positive input |  |  |  |  |  |

| AD13         | VINL          | Input Voltage Range Vın∟                             | Vrefl                             | _          | AVss + 1V                        | V        | This voltage reflects Sample<br>and Hold Channels 0, 1, 2 and<br>3 (CH0-CH3), negative input |  |  |  |  |  |

| AD17         | Rin           | Recommended<br>Impedance of Analog<br>Voltage Source | _                                 | _          | 200<br>200                       | Ω<br>Ω   | 10-bit ADC<br>12-bit ADC                                                                     |  |  |  |  |  |

#### TABLE 26-43: ADC MODULE SPECIFICATIONS

Note 1: These parameters are not characterized or tested in manufacturing.

#### TABLE 27-9: INTERNAL LPRC ACCURACY

| AC<br>CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                    |   |                    |   |                                                  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---|--------------------|---|--------------------------------------------------|--|--|

| Param<br>No.          | Characteristic Min Typ Max Units Conditions                                                                                                              |                    |   |                    |   |                                                  |  |  |

|                       | LPRC @ 32.768 kHz <sup>(1)</sup>                                                                                                                         |                    |   |                    |   |                                                  |  |  |

| HF21                  | LPRC                                                                                                                                                     | -70 <sup>(2)</sup> | _ | +70 <sup>(2)</sup> | % | $-40^{\circ}C \leq TA \leq +150^{\circ}C \qquad$ |  |  |

Note 1: Change of LPRC frequency as VDD changes.

2: Characterized but not tested.

#### TABLE 27-10: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| -            | AC<br>TERISTICS       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               |     | 10  | 25  | ns    | _          |  |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 28  | _   |     | ns    | _          |  |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 35  |     |     | ns    | _          |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

#### TABLE 27-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICSStandard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                       |                                              |     | ated) |     |       |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------|-----|-------|-----|-------|------------|

| Param<br>No.                                                                                                                                                                 | Symbol                | Characteristic <sup>(1)</sup>                | Min | Тур   | Max | Units | Conditions |

| HSP35                                                                                                                                                                        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    |     | 10    | 25  | ns    | _          |

| HSP36                                                                                                                                                                        | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge | 35  | —     | —   | ns    | _          |

| HSP40                                                                                                                                                                        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 28  | —     | —   | ns    | _          |

| HSP41                                                                                                                                                                        |                       | Hold Time of SDIx Data Input to SCKx Edge    | 35  | —     | —   | ns    | _          |

**Note 1:** These parameters are characterized but not tested in manufacturing.

#### TABLE 27-14: ADC MODULE SPECIFICATIONS

| AC<br>CHARACTERISTICSStandard Operating Conditions: $3.0V$ to $3.6V$ (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le Ta \le +150^{\circ}C$ for High Temperature |        |                                             |  |          |           | •        |                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------|--|----------|-----------|----------|--------------------------------------------------|--|

| Param<br>No.                                                                                                                                                                         | Symbol | Characteristic Min Typ Max Units Conditions |  |          |           |          |                                                  |  |

| Reference Inputs                                                                                                                                                                     |        |                                             |  |          |           |          |                                                  |  |

| HAD08                                                                                                                                                                                | IREF   | Current Drain                               |  | 250<br>— | 600<br>50 | μΑ<br>μΑ | ADC operating, See Note 1<br>ADC off, See Note 1 |  |

Note 1: These parameters are not characterized or tested in manufacturing.

#### TABLE 27-15: ADC MODULE SPECIFICATIONS (12-BIT MODE)<sup>(3)</sup>

| -                                                                                  | AC<br>TERISTICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |          |          |           |                   |                                                  |  |

|------------------------------------------------------------------------------------|-----------------|------------------------------------------------------|----------|----------|-----------|-------------------|--------------------------------------------------|--|

| Param<br>No.                                                                       | Symbol          | Characteristic                                       | Min      | Тур      | Max       | Units             | Conditions                                       |  |

| ADC Accuracy (12-bit Mode) – Measurements with external VREF+/VREF- <sup>(1)</sup> |                 |                                                      |          |          |           |                   |                                                  |  |

| AD23a                                                                              | Gerr            | Gain Error                                           | _        | 5        | 10        | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |

| AD24a                                                                              | EOFF            | Offset Error                                         | _        | 2        | 5         | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| ADC Accuracy (12-bit Mode) – Measurements with internal VREF+/VREF- <sup>(1)</sup> |                 |                                                      |          |          |           |                   |                                                  |  |

| AD23a                                                                              | Gerr            | Gain Error                                           | 2        | 10       | 20        | LSb               | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD24a                                                                              | EOFF            | Offset Error                                         | 2        | 5        | 10        | LSb               | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

|                                                                                    |                 | Dynamic                                              | Performa | nce (12- | -bit Mode | e) <sup>(2)</sup> | •                                                |  |

| HAD33a                                                                             | Fnyq            | Input Signal Bandwidth                               | _        | _        | 200       | kHz               | _                                                |  |

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

**2:** These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

#### TABLE 27-16: ADC MODULE SPECIFICATIONS (10-BIT MODE)<sup>(3)</sup>

| Min<br>lode) – Measi<br>— | Typ<br>urement:<br>3 | Max<br>s with ex                                               | Units<br>ternal V                                                                | Conditions<br>/REF+/VREF-( <sup>1)</sup><br>VINL = AVSS = VREFL = 0V,                                           |  |  |

|---------------------------|----------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| lode) – Measi<br>—        | 1                    | 1                                                              | 1                                                                                |                                                                                                                 |  |  |

| —                         | 3                    | 6                                                              | LSb                                                                              | VINL = AVSS = VREFL = 0V,                                                                                       |  |  |

|                           |                      |                                                                |                                                                                  | AVDD = VREFH = 3.6V                                                                                             |  |  |

| —                         | 2                    | 5                                                              | LSb                                                                              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                                                                |  |  |

| lode) – Meas              | urement              | s with in                                                      | ternal V                                                                         | REF+/VREF- <sup>(1)</sup>                                                                                       |  |  |

|                           | 7                    | 15                                                             | LSb                                                                              | VINL = AVSS = 0V, AVDD = 3.6V                                                                                   |  |  |

| —                         | 3                    | 7                                                              | LSb                                                                              | VINL = AVSS = 0V, AVDD = 3.6V                                                                                   |  |  |

| nic Performa              | nce (10-             | bit Mode                                                       | ) <sup>(2)</sup>                                                                 | •                                                                                                               |  |  |

| lth —                     | —                    | 400                                                            | kHz                                                                              | —                                                                                                               |  |  |

|                           | mic Performa         | Iode) – Measurement   — 7   — 3   mic Performance (10-   Ith — | Iode) – Measurements with in   — 7 15   — 3 7   mic Performance (10-bit Mode 400 | Node) – Measurements with internal V<br>— 7 15 LSb<br>— 3 7 LSb<br>nic Performance (10-bit Mode) <sup>(2)</sup> |  |  |

**e 1:** These parameters are characterized, but are tested at 20 ksps only.

**2:** These parameters are characterized by similarity, but are not tested in manufacturing.

**3:** Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

| CHARAG       | AC<br>CTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                  |      |     |       |            |

|--------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|-------|------------|

| Param<br>No. | Symbol           | Characteristic                                                                                                                                          | Min              | Тур  | Max | Units | Conditions |

|              |                  | Cloc                                                                                                                                                    | k Parame         | ters |     |       |            |

|              | -                | (1 - 2 - 2) + (1)                                                                                                                                       |                  |      |     |       |            |

| HAD50        | TAD              | ADC Clock Period <sup>(1)</sup>                                                                                                                         | 147              | —    | —   | ns    | —          |

| HAD50        | IAD              |                                                                                                                                                         | 147<br>version R | ate  |     | ns    | _          |

#### TABLE 27-17: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 27-18: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| -               | AC<br>TERISTICS                                                      | Standard Operating Condition<br>Operating temperature -40°C |          |      |     |       | ed)        |

|-----------------|----------------------------------------------------------------------|-------------------------------------------------------------|----------|------|-----|-------|------------|

| Param<br>No.    | Symbol                                                               | Characteristic                                              | Min      | Тур  | Max | Units | Conditions |

|                 |                                                                      | Cloc                                                        | k Parame | ters |     |       |            |

| HAD50           | TAD                                                                  | ADC Clock Period <sup>(1)</sup>                             | 104      |      |     | ns    | _          |

| Conversion Rate |                                                                      |                                                             |          |      |     |       |            |

| HAD56           | FCNV                                                                 | Throughput Rate <sup>(1)</sup>                              |          |      | 800 | Ksps  |            |

| N               | These perspectaves are characterized but not tested in manufacturing |                                                             |          |      |     |       |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

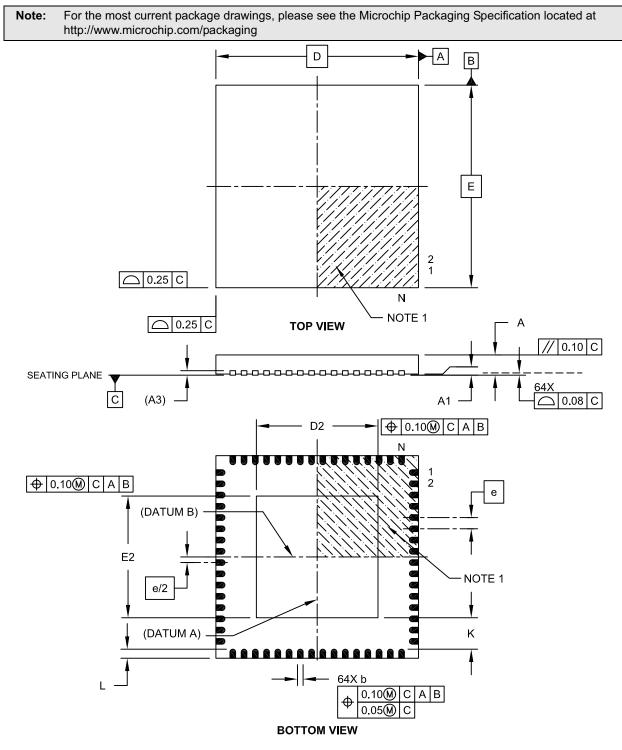

#### 29.2 Package Details

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

#### Revision D (June 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

#### TABLE B-3: MAJOR SECTION UPDATES

| Section Name                                                                        | Update Description                                                                              |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Updated the Recommended Minimum Connection (see Figure 2-1).                                    |

| Section 9.0 "Oscillator Configuration"                                              | Updated the COSC<2:0> and NOSC<2:0> bit value definitions for '001' (see Register 9-1).         |

| Section 22.0 "10-bit/12-bit Analog-to-Digital Converter (ADC)"                      | Updated the Analog-to-Digital Conversion Clock Period Block Diagram (see Figure 22-2).          |

| Section 23.0 "Special Features"                                                     | Added Note 3 to the On-chip Voltage Regulator Connections (see Figure 23-1).                    |

| Section 26.0 "Electrical Characteristics"                                           | Updated "Absolute Maximum Ratings".                                                             |

|                                                                                     | Updated Operating MIPS vs. Voltage (see Table 26-1).                                            |

|                                                                                     | Removed parameter DC18 from the DC Temperature and Voltage Specifications (see Table 26-4).     |

|                                                                                     | Updated the notes in the following tables:                                                      |

|                                                                                     | Table 26-5                                                                                      |

|                                                                                     | Table 26-6                                                                                      |

|                                                                                     | Table 26-7                                                                                      |

|                                                                                     | Table 26-8                                                                                      |

|                                                                                     | Updated the I/O Pin Output Specifications (see Table 26-10).                                    |