Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | - ·                                                                              |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc710a-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

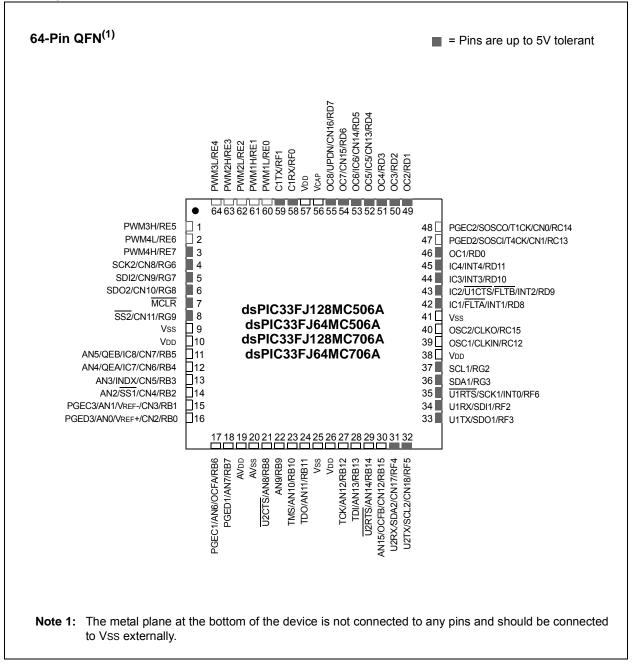

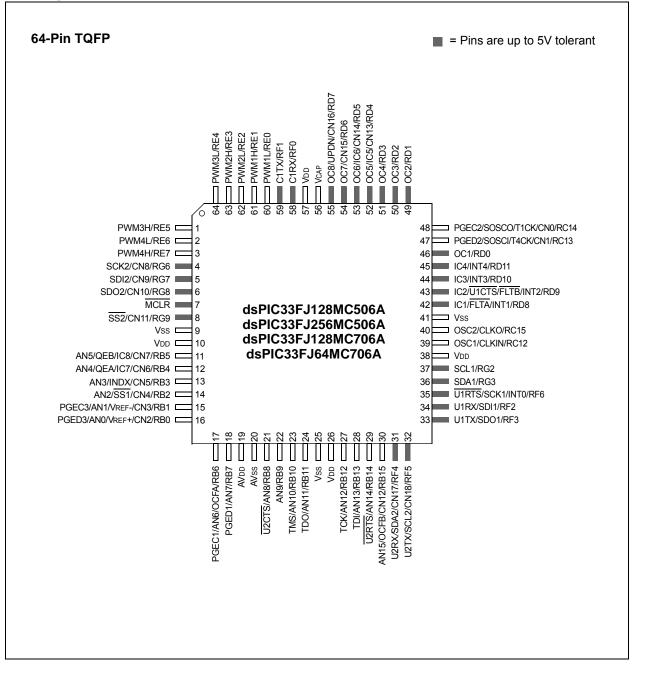

#### Pin Diagrams

### **Pin Diagrams (Continued)**

## **Table of Contents**

| dsPI | C33F Product Families                                                                            |     |

|------|--------------------------------------------------------------------------------------------------|-----|

| 1.0  | Device Overview                                                                                  |     |

| 2.0  | Guidelines for Getting Started with 16-bit Digital Signal Controllers                            | 19  |

| 3.0  | CPU                                                                                              |     |

| 4.0  | Memory Organization                                                                              |     |

| 5.0  | Flash Program Memory                                                                             | 73  |

| 6.0  | Reset                                                                                            |     |

| 7.0  | Interrupt Controller                                                                             |     |

| 8.0  | Direct Memory Access (DMA)                                                                       | 133 |

| 9.0  | Oscillator Configuration                                                                         |     |

| 10.0 | Power-Saving Features                                                                            | 153 |

|      | I/O Ports                                                                                        |     |

| 12.0 | Timer1                                                                                           |     |

| 13.0 | Timer2/3, Timer4/5, Timer6/7 and Timer8/9                                                        |     |

| 14.0 | Input Capture                                                                                    |     |

|      | Output Compare                                                                                   |     |

| 16.0 | Motor Control PWM Module                                                                         |     |

| 17.0 |                                                                                                  |     |

|      | Serial Peripheral Interface (SPI)                                                                |     |

| 19.0 | Inter-Integrated Circuit (I <sup>2</sup> C™)                                                     |     |

| 20.0 | Universal Asynchronous Receiver Transmitter (UART)                                               |     |

|      | Enhanced CAN Module                                                                              |     |

| 22.0 | 10-bit/12-bit Analog-to-Digital Converter (ADC)                                                  |     |

| 23.0 | Special Features                                                                                 |     |

| 24.0 | Instruction Set Summary                                                                          |     |

| 25.0 | Development Support                                                                              |     |

| 26.0 | Electrical Characteristics                                                                       |     |

|      | High Temperature Electrical Characteristics                                                      |     |

|      | DC and AC Device Characteristics Graphs                                                          |     |

|      | Packaging Information                                                                            |     |

|      | ndix A: Migrating from dsPIC33FJXXXMCX06/X08/X10 Devices to dsPIC33FJXXXMCX06A/X08A/X10A Devices |     |

|      | ndix B: Revision History                                                                         |     |

|      | (                                                                                                |     |

|      | Nicrochip Web Site                                                                               |     |

|      | omer Change Notification Service                                                                 |     |

|      | omer Support                                                                                     |     |

|      | er Response                                                                                      |     |

| Prod | uct Identification System                                                                        | 371 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 3.4 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0                  | R-0                                                                  | R/C-0                                                                                                   | R/C-0             | R-0               | R/C-0              | R -0              | R/W-0          |  |  |  |  |

|----------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|-------------------|--------------------|-------------------|----------------|--|--|--|--|

| OA                   | OB                                                                   | SA <sup>(1)</sup>                                                                                       | SB <sup>(1)</sup> | OAB               | SAB <sup>(4)</sup> | DA                | DC             |  |  |  |  |

| bit 15               |                                                                      |                                                                                                         |                   |                   |                    |                   | bit 8          |  |  |  |  |

|                      |                                                                      |                                                                                                         |                   |                   |                    |                   |                |  |  |  |  |

| R/W-0 <sup>(3)</sup> |                                                                      | R/W-0 <sup>(3)</sup>                                                                                    | R-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0          |  |  |  |  |

|                      | IPL<2:0> <sup>(2)</sup>                                              |                                                                                                         | RA                | N                 | OV                 | Z                 | С              |  |  |  |  |

| bit 7                |                                                                      |                                                                                                         |                   |                   |                    |                   | bit (          |  |  |  |  |

| Legend:              |                                                                      |                                                                                                         |                   |                   |                    |                   |                |  |  |  |  |

| C = Cleara           | ble bit                                                              | R = Readable                                                                                            | e bit             | U = Unimple       | mented bit, read   | as '0'            |                |  |  |  |  |

| S = Settabl          | e bit                                                                | W = Writable                                                                                            | bit               | -n = Value at     | POR                |                   |                |  |  |  |  |

| '1' = Bit is s       | set                                                                  | '0' = Bit is clea                                                                                       | ared              | x = Bit is unk    | nown               |                   |                |  |  |  |  |

|                      |                                                                      |                                                                                                         |                   |                   |                    |                   |                |  |  |  |  |

| bit 15               |                                                                      | ator A Overflov                                                                                         |                   |                   |                    |                   |                |  |  |  |  |

|                      | 1 = Accumulator A overflowed<br>0 = Accumulator A has not overflowed |                                                                                                         |                   |                   |                    |                   |                |  |  |  |  |

| bit 14               |                                                                      |                                                                                                         |                   |                   |                    |                   |                |  |  |  |  |

| DIL 14               |                                                                      | <b>OB:</b> Accumulator B Overflow Status bit<br>1 = Accumulator B overflowed                            |                   |                   |                    |                   |                |  |  |  |  |

|                      |                                                                      | ator B has not c                                                                                        |                   |                   |                    |                   |                |  |  |  |  |

| bit 13               | SA: Accumul                                                          | SA: Accumulator A Saturation 'Sticky' Status bit <sup>(1)</sup>                                         |                   |                   |                    |                   |                |  |  |  |  |

|                      |                                                                      | 1 = Accumulator A is saturated or has been saturated at some time<br>0 = Accumulator A is not saturated |                   |                   |                    |                   |                |  |  |  |  |

| bit 12               | SB: Accumul                                                          | SB: Accumulator B Saturation 'Sticky' Status bit <sup>(1)</sup>                                         |                   |                   |                    |                   |                |  |  |  |  |

|                      |                                                                      | ator B is saturat<br>ator B is not sat                                                                  |                   | en saturated at   | t some time        |                   |                |  |  |  |  |

| bit 11               | <b>0AB:</b> 0A    C                                                  | OAB: OA    OB Combined Accumulator Overflow Status bit                                                  |                   |                   |                    |                   |                |  |  |  |  |

|                      |                                                                      | 1 = Accumulators A or B have overflowed                                                                 |                   |                   |                    |                   |                |  |  |  |  |

|                      |                                                                      | ccumulators A                                                                                           |                   |                   | (4)                |                   |                |  |  |  |  |

| bit 10               |                                                                      | B Combined Ad                                                                                           |                   |                   |                    | 4 <sup>1</sup>    | 1              |  |  |  |  |

|                      |                                                                      | ccumulator A or                                                                                         |                   |                   | urated at some     | time in the pas   | t              |  |  |  |  |

| bit 9                | -                                                                    | DA: DO Loop Active bit                                                                                  |                   |                   |                    |                   |                |  |  |  |  |

|                      |                                                                      | 1 = DO loop in progress                                                                                 |                   |                   |                    |                   |                |  |  |  |  |

| hit 0                | •                                                                    | ot in progress<br>U Half Carry/Bo                                                                       |                   |                   |                    |                   |                |  |  |  |  |

| bit 8                | 1 = A carry-o                                                        | out from the 4th                                                                                        |                   | for byte-sized    | data) or 8th low-  | order bit (for wo | ord-sized data |  |  |  |  |

|                      | 0 = No carry                                                         | sult occurred<br>-out from the 4<br>he result occur                                                     |                   | oit (for byte-siz | ed data) or 8th    | low-order bit (   | for word-sized |  |  |  |  |

| Note 1:              | This bit may be rea                                                  | ad or cleared (r                                                                                        | not set).         |                   |                    |                   |                |  |  |  |  |

| 2:                   | The IPL<2:0> bits<br>level. The value in                             | are concatenat                                                                                          | ed with the IF    |                   |                    |                   |                |  |  |  |  |

|                      | IPL<3> = 1.<br>The IPI <2:0> Stat                                    | ue bite are rear                                                                                        |                   |                   |                    |                   |                |  |  |  |  |

| 3:                   | THE IPLSZUP STAT                                                     | e IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).                                     |                   |                   |                    |                   |                |  |  |  |  |

4: This bit may be read or cleared (not set). Clearing this bit will clear SA and SB.

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = CPU interrupt priority level is 7 (15), user interrupts disabled                                                                       |

|         | 110 = CPU interrupt priority level is 6 (14)                                                                                                 |

|         | 101 = CPU interrupt priority level is 5 (13)                                                                                                 |

|         | 100 = CPU interrupt priority level is 4 (12)                                                                                                 |

|         | 011 = CPU interrupt priority level is 3 (11)<br>010 = CPU interrupt priority level is 2 (10)                                                 |

|         | 001 = CPU interrupt priority level is 1 (9)                                                                                                  |

|         | 000 = CPU interrupt priority level is 0 (8)                                                                                                  |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                   |

|         | 1 = REPEAT loop in progress                                                                                                                  |

|         | 0 = REPEAT loop not in progress                                                                                                              |

| bit 3   | N: MCU ALU Negative bit                                                                                                                      |

|         | 1 = Result was negative                                                                                                                      |

|         | 0 = Result was non-negative (zero or positive)                                                                                               |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                     |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state. |

|         | 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)                                                                   |

|         | 0 = No overflow occurred                                                                                                                     |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                          |

|         | 1 = An operation which affects the Z bit has set it at some time in the past                                                                 |

|         | 0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)                                               |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                  |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                         |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                        |

|         |                                                                                                                                              |

- **Note 1:** This bit may be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

- 4: This bit may be read or cleared (not set). Clearing this bit will clear SA and SB.

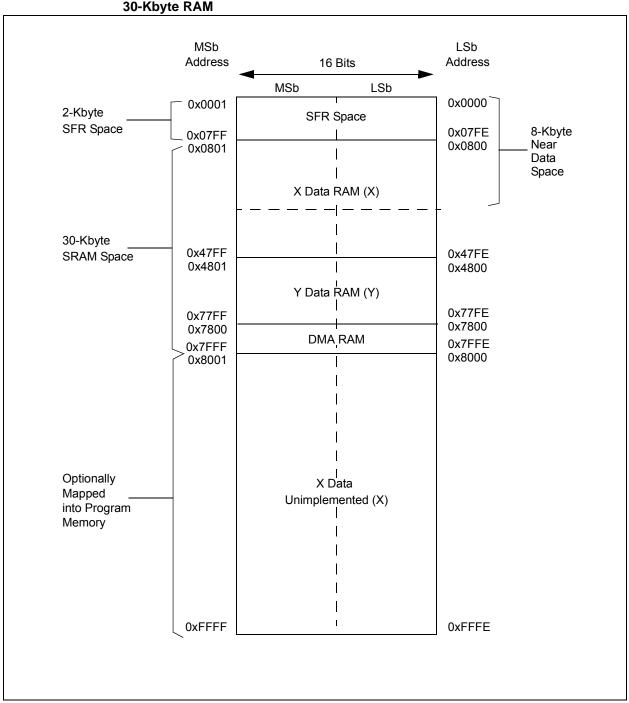

# FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 30-Kbyte RAM

# TABLE 4-20: ECAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 OR 1

| File Name  | Addr | Bit 15  | Bit 14       | Bit 13        | Bit 12                    | Bit 11  | Bit 10  | Bit 9    | Bit 8  | Bit 7                    | Bit 6    | Bit 5  | Bit 4     | Bit 3              | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

|------------|------|---------|--------------|---------------|---------------------------|---------|---------|----------|--------|--------------------------|----------|--------|-----------|--------------------|----------|----------|--------|---------------|

| C1CTRL1    | 0400 | -       | _            | CSIDL         | ABAT                      | —       | RE      | QOP<2:0  | >      | OPI                      | MODE<2:0 | >      | -         | CANCAP             | _        | _        | WIN    | 0480          |

| C1CTRL2    | 0402 | _       | _            | _             | _                         | _       | _       | _        | _      | _                        | _        | _      |           | DI                 | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404 | _       | _            | — FILHIT<4:0> |                           |         |         |          |        | _                        |          |        | I         | CODE<6:0>          | >        |          |        | 0000          |

| C1FCTRL    | 0406 | D       | DMABS<2:0> — |               |                           | _       | —       | —        | —      | —                        | —        | —      |           |                    | FSA<4:0> |          |        | 0000          |

| C1FIFO     | 0408 | _       | F            |               |                           |         | P<5:0>  |          |        | —                        | —        |        | FNRB<5:0> |                    |          | 01       |        | 0000          |

| C1INTF     | 040A | _       | —            | TXBO          | TXBP                      | RXBP    | TXWAR   | RXWAR    | EWARN  | IVRIF                    | WAKIF    | ERRIF  | —         | FIFOIF             | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C | _       | —            | _             | _                         | _       | _       | _        | _      | IVRIE                    | WAKIE    | ERRIE  | _         | FIFOIE             | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E |         |              |               | TERRCN                    | T<7:0>  |         |          |        | RERRCNT<7:0>             |          |        |           |                    | 0000     |          |        |               |

| C1CFG1     | 0410 | _       | —            | _             | _                         | _       | _       | _        | _      | SJW<1                    | 1:0>     |        |           | BRP<               | :5:0>    |          |        | 0000          |

| C1CFG2     | 0412 | _       | WAKFIL       | _             | _                         | _       | SE      | G2PH<2:0 | >      | SEG2PHTS                 | SAM      | SI     | EG1PH<2:  | :0>                | Р        | RSEG<2:0 | )>     | 0000          |

| C1FEN1     | 0414 | FLTEN15 | FLTEN14      | FLTEN13       | FLTEN12                   | FLTEN11 | FLTEN10 | FLTEN9   | FLTEN8 | FLTEN7                   | FLTEN6   | FLTEN5 | FLTEN4    | FLTEN3             | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418 | F7MSk   | <<1:0>       | F6MSI         | //SK<1:0> F5MSK<1:0> F4MS |         |         | F4MSH    | <1:0>  | F3MSK<1:0> F2MSK<1:0> F1 |          |        | F1MSK     | SK<1:0> F0MSK<1:0> |          |          | 0000   |               |

| C1FMSKSEL2 | 041A | F15MS   | K<1:0>       | F14MS         | K<1:0>                    | F13MS   | SK<1:0> | F12MS    | K<1:0> | F11MSK                   | <1:0>    | F10MS  | K<1:0>    | F9MSK              | (<1:0>   | F8MS     | K<1:0> | 0000          |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0

| File Name | Addr          | Bit 15  | Bit 14                      | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8      | Bit 7       | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-----------------------------|---------|---------|---------|---------|---------|------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         | See definition when WIN = x |         |         |         |         |         |            |             |         |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14                     | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8     | RXFUL7      | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30                     | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24    | RXFUL23     | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14                     | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8     | RXOVF7      | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30                     | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24    | RXOVF23     | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1                      | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>    | TXEN0       | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | 81<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3                      | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>    | TXEN2       | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | 81<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5                      | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>    | TXEN4       | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | 81<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7                      | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>    | TXEN6       | TXABAT6 | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | 81<1:0> | xxxx          |

| C1RXD     | 0440          |         |                             |         |         |         |         | EC      | AN1 Receiv | ved Data W  | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         |                             |         |         |         |         | EC      | CAN1 Trans | mit Data Wo | ord     |         |         |         |         |         |         | xxxx          |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-36: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing     |

|-------|----------------------------------------------|

|       | mode specified in the instruction can differ |

|       | for the source and destination EA.           |

|       | However, the 4-bit Wb (register offset)      |

|       | field is shared between both source and      |

|       | destination (but typically only used by      |

|       | one).                                        |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the Data Pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 will always be directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9, and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

# 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

| U-0           | R/W-0                                                                                                  | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------|-----------------|-----------------|--------|--|--|--|--|

| —             | DMA1IF                                                                                                 | AD1IF                            | U1TXIF           | U1RXIF            | SPI1IF          | SPI1EIF         | T3IF   |  |  |  |  |

| bit 15        |                                                                                                        |                                  |                  |                   |                 |                 | bit 8  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                  | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

| T2IF          | OC2IF                                                                                                  | IC2IF                            | DMA01IF          | T1IF              | OC1IF           | IC1IF           | INT0IF |  |  |  |  |

| bit 7         | L.                                                                                                     |                                  | 1                |                   |                 |                 | bit (  |  |  |  |  |

| Legend:       |                                                                                                        |                                  |                  |                   |                 |                 |        |  |  |  |  |

| R = Readable  | e bit                                                                                                  | W = Writable                     | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |  |  |  |  |

| -n = Value at | POR                                                                                                    | '1' = Bit is se                  | t                | '0' = Bit is clea | ared            | x = Bit is unkn | iown   |  |  |  |  |

| bit 15        | Unimplemen                                                                                             | ted: Read as                     | ʻ0'              |                   |                 |                 |        |  |  |  |  |

| bit 14        | -                                                                                                      |                                  | ata Transfer C   | omplete Interro   | upt Flag Status | s bit           |        |  |  |  |  |

|               |                                                                                                        | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | •                                                                                                      | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 13        |                                                                                                        |                                  | Complete Interr  | upt Flag Status   | s bit           |                 |        |  |  |  |  |

|               | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>    |                                  |                  |                   |                 |                 |        |  |  |  |  |

| bit 12        | U1TXIF: UART1 Transmitter Interrupt Flag Status bit                                                    |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               |                                                                                                        | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | 0 = Interrupt request has not occurred                                                                 |                                  |                  |                   |                 |                 |        |  |  |  |  |

| bit 11        | <b>U1RXIF:</b> UART1 Receiver Interrupt Flag Status bit<br>1 = Interrupt request has occurred          |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               |                                                                                                        | request has oc<br>request has no |                  |                   |                 |                 |        |  |  |  |  |

| bit 10        | SPI1IF: SPI1 Event Interrupt Flag Status bit                                                           |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               | 1 = Interrupt request has occurred                                                                     |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               | -                                                                                                      | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 9         | SPI1EIF: SPI1 Fault Interrupt Flag Status bit                                                          |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               | <ol> <li>I = Interrupt request has occurred</li> <li>I = Interrupt request has not occurred</li> </ol> |                                  |                  |                   |                 |                 |        |  |  |  |  |

| bit 8         | •                                                                                                      | Interrupt Flag                   |                  |                   |                 |                 |        |  |  |  |  |

|               | 1 = Interrupt request has occurred                                                                     |                                  |                  |                   |                 |                 |        |  |  |  |  |

|               | 0 = Interrupt request has not occurred                                                                 |                                  |                  |                   |                 |                 |        |  |  |  |  |

| bit 7         |                                                                                                        | Interrupt Flag                   |                  |                   |                 |                 |        |  |  |  |  |

|               | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                  |                  |                   |                 |                 |        |  |  |  |  |

| bit 6         | -                                                                                                      | -                                | nannel 2 Interru | upt Flag Status   | bit             |                 |        |  |  |  |  |

|               |                                                                                                        | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | •                                                                                                      | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 5         | •                                                                                                      | -                                | el 2 Interrupt F | lag Status bit    |                 |                 |        |  |  |  |  |

|               | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                  |                  |                   |                 |                 |        |  |  |  |  |

| bit 4         | -                                                                                                      | -                                | ata Transfer C   | omplete Interri   | upt Flag Status | s bit           |        |  |  |  |  |

|               |                                                                                                        | request has oc                   |                  |                   |                 |                 |        |  |  |  |  |

|               | -                                                                                                      | request has no                   |                  |                   |                 |                 |        |  |  |  |  |

| bit 3         |                                                                                                        | Interrupt Flag                   |                  |                   |                 |                 |        |  |  |  |  |

|               | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                  |                  |                   |                 |                 |        |  |  |  |  |

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0          | U-0                                                                       | U-0                                                        | U-0             | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------|------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| —            | —                                                                         | —                                                          | —               | —                 |                 | DMA1IP<2:0>     |       |  |  |  |  |  |

| bit 15       |                                                                           |                                                            |                 |                   |                 |                 | bit   |  |  |  |  |  |

| U-0          | R/W-1                                                                     | R/W-0                                                      | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

| _            |                                                                           | AD1IP<2:0>                                                 |                 | —                 |                 | U1TXIP<2:0>     |       |  |  |  |  |  |

| bit 7        |                                                                           |                                                            |                 |                   |                 |                 | bit   |  |  |  |  |  |

| Legend:      |                                                                           |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                    | W = Writable                                               | bit             | U = Unimplei      | mented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a |                                                                           | '1' = Bit is set                                           |                 | '0' = Bit is cle  |                 | x = Bit is unkr | nown  |  |  |  |  |  |

|              |                                                                           |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 15-11    | Unimpleme                                                                 | nted: Read as 'o                                           | o'              |                   |                 |                 |       |  |  |  |  |  |

| bit 10-8     | DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              | 111 = Interru                                                             | 111 = Interrupt is priority 7 (highest priority interrupt) |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                         |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                         | •                                                          |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                           | upt is priority 1<br>upt source is dis                     | abled           |                   |                 |                 |       |  |  |  |  |  |

| bit 7        |                                                                           | nted: Read as '(                                           |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 6-4      | AD1IP<2:0>: ADC1 Conversion Complete Interrupt Priority bits              |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                         | •                                                          |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                         | •                                                          |                 |                   |                 |                 |       |  |  |  |  |  |

|              | 001 = Interru                                                             | •<br>001 = Interrupt is priority 1                         |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                           | 000 = Interrupt source is disabled                         |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 3        | Unimpleme                                                                 | nted: Read as '                                            | כי              |                   |                 |                 |       |  |  |  |  |  |

| bit 2-0      | U1TXIP<2:0                                                                | >: UART1 Trans                                             | smitter Interru | upt Priority bits |                 |                 |       |  |  |  |  |  |

|              | 111 = Interru                                                             | 111 = Interrupt is priority 7 (highest priority interrupt) |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                         |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                         |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                        |                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                           | upt is priority 1<br>upt source is dis                     |                 |                   |                 |                 |       |  |  |  |  |  |

#### REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0                               | U-0                                                                                              | U-0                                                                                                      | U-0            | R-0               | R-0           | R-0             | R-0   |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|-------------------|---------------|-----------------|-------|--|--|--|--|

|                                   | _                                                                                                | _                                                                                                        | _              | ILR<3:0>          |               |                 |       |  |  |  |  |

| oit 15                            |                                                                                                  | <b>.</b>                                                                                                 |                |                   |               |                 | bit 8 |  |  |  |  |

|                                   |                                                                                                  |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

| U-0                               | R-0                                                                                              | R-0                                                                                                      | R-0            | R-0               | R-0           | R-0             | R-0   |  |  |  |  |

| —                                 |                                                                                                  |                                                                                                          |                | VECNUM<6:0>       | >             |                 |       |  |  |  |  |

| oit 7                             |                                                                                                  |                                                                                                          |                |                   |               |                 | bit ( |  |  |  |  |

|                                   |                                                                                                  |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

| <b>₋egend:</b><br>R = Readab      | la hit                                                                                           | W = Writable                                                                                             | h:t            |                   | opted bit rea | ad aa (0)       |       |  |  |  |  |

|                                   |                                                                                                  |                                                                                                          |                | U = Unimplem      |               |                 |       |  |  |  |  |

| n = Value at POR '1' = Bit is set |                                                                                                  |                                                                                                          |                | '0' = Bit is clea | ared          | x = Bit is unkr | IOWN  |  |  |  |  |

| oit 15-12                         | Unimpleme                                                                                        | ented: Read as the                                                                                       | 0'             |                   |               |                 |       |  |  |  |  |

| pit 11-8                          | ILR<3:0>: New CPU Interrupt Priority Level bits                                                  |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

|                                   | 1111 = CPU interrupt priority level is 15                                                        |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

|                                   | •                                                                                                |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

|                                   | •                                                                                                |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

|                                   | •<br>0001 - CDI Linterrupt priority lovel is 1                                                   |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

|                                   | 0001 = CPU interrupt priority level is 1<br>0000 = CPU interrupt priority level is 0             |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

| oit 7                             | Unimpleme                                                                                        | ented: Read as '                                                                                         | 0'             |                   |               |                 |       |  |  |  |  |

| oit 6-0                           | VECNUM<                                                                                          | 6:0>: Vector Nun                                                                                         | nber of Pendir | ng Interrupt bits |               |                 |       |  |  |  |  |

|                                   |                                                                                                  | VECNUM<6:0>: Vector Number of Pending Interrupt bits<br>0111111 = Interrupt vector pending is number 135 |                |                   |               |                 |       |  |  |  |  |

|                                   | •                                                                                                |                                                                                                          | Ū              |                   |               |                 |       |  |  |  |  |

|                                   | •                                                                                                |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

|                                   | •                                                                                                | Interrupt vector                                                                                         | nondina in nu  | mbor 0            |               |                 |       |  |  |  |  |

|                                   | 0000001 = Interrupt vector pending is number 9<br>0000000 = Interrupt vector pending is number 8 |                                                                                                          |                |                   |               |                 |       |  |  |  |  |

#### REGISTER 7-33: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

## 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "**Pin Diagrams**" section for the available pins and their functionality.

## 11.3 Configuring Analog Port Pins

The ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the ADC port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: |                                             |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJXXXMCX06A/X08A/X10A devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN Interrupt Enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the Weak Pull-up Enable bits (CNxPUE) for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFF00, WO | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

|      |            |                                   |

# 16.0 MOTOR CONTROL PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Motor Control PWM" (DS70187) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This module simplifies the task of generating multiple, synchronized Pulse-Width Modulated (PWM) outputs. In particular, the following power and motion control applications are supported by the PWM module:

- · 3-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

The PWM module has the following features:

- Eight PWM I/O pins with four duty cycle generators

- · Up to 16-bit resolution

- 'On-the-fly' PWM frequency changes

- Edge and Center-Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation

- Special Event' comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

- Duty cycle updates are configurable to be immediate or synchronized to the PWM time base

This module contains four duty cycle generators, numbered 1 through 4. The module has eight PWM output pins, numbered PWM1H/PWM1L through PWM4H/PWM4L. The eight I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

The PWM module allows several modes of operation which are beneficial for specific power control applications.

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                      |

- Note 1: Refer to Section 17. "UART" (DS70188) in the "dsPIC33F/PIC24H Family Reference Manual" for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

## 21.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

### 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

### 21.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set, and the TXREQ bit is cleared.

## 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

### 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

### 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = 111. In this mode, the data which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

### 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

| U-0             | U-0                                                                                                                                                  | R/W-0            | R/W-0           | r-0               | R/W-1            | R/W-0           | R/W-0 |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|

|                 | _                                                                                                                                                    | CSIDL            | ABAT            | —                 |                  | REQOP<2:0>      |       |  |  |