Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 64KB (64K × 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc710at-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

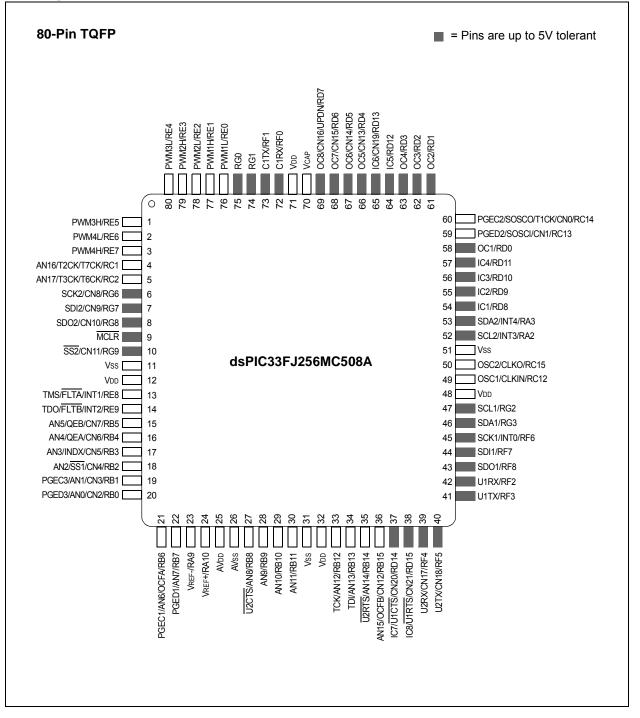

#### **Pin Diagrams (Continued)**

NOTES:

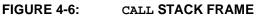

## 4.2.7 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXMCX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | concatenates the SRL register to the MSb |  |  |  |  |  |  |

|       | of the PC prior to the push.             |  |  |  |  |  |  |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33FJXXXMCX06A/X08A/X10A devices support data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

## 4.3 Instruction Addressing Modes

The addressing modes in Table 4-36 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

## 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the following form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (i.e., the addressing mode can only be Register Direct) which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

| Note: | Not all instructions support all the   |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|

|       | addressing modes given above. Individ- |  |  |  |  |  |  |  |  |

|       | ual instructions may support different |  |  |  |  |  |  |  |  |

|       | subsets of these addressing modes.     |  |  |  |  |  |  |  |  |

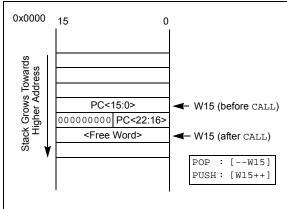

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

1. TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.  TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is as follows:

- 1. Read eight rows of program memory (512 instructions) and store it in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5 using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMC | ON for block erase operation         |                                         |

|---------------|--------------------------------------|-----------------------------------------|

| MOV           | #0x4042, W0                          | ;                                       |

| MOV           | W0, NVMCON                           | ; Initialize NVMCON                     |

| ; Init pointe | r to row to be ERASED                |                                         |

| MOV           | <pre>#tblpage(PROG_ADDR), W0</pre>   | ;                                       |

| MOV           | W0, TBLPAG                           | ; Initialize PM Page Boundary SFR       |

| MOV           | <pre>#tbloffset(PROG_ADDR), W0</pre> | ; Initialize in-page EA[15:0] pointer   |

| TBLWT         | L WO, [WO]                           | ; Set base address of erase block       |

| DISI          | #5                                   | ; Block all interrupts with priority <7 |

|               |                                      | ; for next 5 instructions               |

| MOV           | #0x55, W0                            |                                         |

| MOV           | W0, NVMKEY                           | ; Write the 55 key                      |

| MOV           | #0xAA, W1                            | ;                                       |

| MOV           | W1, NVMKEY                           | ; Write the AA key                      |

| BSET          | NVMCON, #WR                          | ; Start the erase sequence              |

| NOP           |                                      | ; Insert two NOPs after the erase       |

| NOP           |                                      | ; command is asserted                   |

|               |                                      |                                         |

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256MCX06A/X08A/X10A devices, this bit is unimplemented and reads back a programmed value.

### 7.3 Interrupt Control and Status Registers

dsPIC33FJXXXMCX06A/X08A/X10A devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- IEC0 through IEC4

- IPC0 through IPC17

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS) as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals. The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number (VECNUM<6:0>) and Interrupt level bit (ILR<3:0>) fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32 in the following pages.

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                              | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|--------------------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|

|                                                                    |       |       | PAD             | <15:8>                             |       |       |       |

| bit 15                                                             |       |       |                 |                                    |       |       | bit 8 |

|                                                                    |       |       |                 |                                    |       |       |       |

| R/W-0                                                              | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                    |       |       | PAE             | )<7:0>                             |       |       |       |

| bit 7                                                              |       |       |                 |                                    |       |       | bit 0 |

|                                                                    |       |       |                 |                                    |       |       |       |

| Legend:                                                            |       |       |                 |                                    |       |       |       |

| R = Readable bit W = Writable bit                                  |       |       | bit             | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |       |       | x = Bit is unki | nown                               |       |       |       |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0       | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------------|-------|

| _      | —   | —   | _   | —   | —   | CNT<9:8>(2) |       |

| bit 15 |     |     |     |     |     |             | bit 8 |

| R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |

| bit 7 bit 0             |       |       |       |       |       |       |       |  |

| Legend:           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** Number of DMA transfers = CNT<9:0> + 1.

NOTES:

| REGISTEF     |              | R/W-0                           |                       |                   |                |                | U-0                  |  |  |

|--------------|--------------|---------------------------------|-----------------------|-------------------|----------------|----------------|----------------------|--|--|

|              | R/W-0        |                                 | R/W-0                 | U-0               | U-0            | U-0            | 0-0                  |  |  |

| T9MD         | T8MD         | T7MD                            | T6MD                  |                   |                | —              |                      |  |  |

| bit 15       |              |                                 |                       |                   |                |                | bit                  |  |  |

|              |              |                                 |                       |                   |                |                |                      |  |  |

| U-0          | U-0          | U-0                             | U-0                   | U-0               | U-0            | R/W-0          | R/W-0                |  |  |

|              | —            | —                               |                       | —                 |                | I2C2MD         | AD2MD <sup>(1)</sup> |  |  |

| bit 7        |              |                                 |                       |                   |                |                | bit                  |  |  |

| Legend:      |              |                                 |                       |                   |                |                |                      |  |  |

| R = Readal   | ble bit      | W = Writable                    | bit                   | U = Unimplem      | ented bit. rea | id as '0'      |                      |  |  |

| -n = Value a | at POR       | '1' = Bit is set                |                       | '0' = Bit is clea |                | x = Bit is unk | nown                 |  |  |

|              |              |                                 |                       |                   |                |                |                      |  |  |

| bit 15       | T9MD: Timer  | 9 Module Disal                  | ole bit               |                   |                |                |                      |  |  |

|              | 1 = Timer9 m | odule is disable                | ed                    |                   |                |                |                      |  |  |

|              | 0 = Timer9 m | odule is enable                 | ed                    |                   |                |                |                      |  |  |

| bit 14       | T8MD: Timer8 | 3 Module Disat                  | ole bit               |                   |                |                |                      |  |  |

|              | 1 = Timer8 m | odule is disable                | ed                    |                   |                |                |                      |  |  |

|              | 0 = Timer8 m | odule is enable                 | ed                    |                   |                |                |                      |  |  |

| bit 13       | T7MD: Timer7 | 7 Module Disal                  | ole bit               |                   |                |                |                      |  |  |

|              |              | odule is disable                |                       |                   |                |                |                      |  |  |

|              | 0 = Timer7 m | odule is enable                 | ed                    |                   |                |                |                      |  |  |

| bit 12       | T6MD: Timer6 | 6 Module Disat                  | ole bit               |                   |                |                |                      |  |  |

|              |              | odule is disable                |                       |                   |                |                |                      |  |  |

|              | 0 = Timer6 m | odule is enable                 | ed                    |                   |                |                |                      |  |  |

| bit 11-2     | Unimplement  | ted: Read as '                  | 0'                    |                   |                |                |                      |  |  |

| bit 1        | 12C2MD: 12C2 | I2C2MD: I2C2 Module Disable bit |                       |                   |                |                |                      |  |  |

|              |              | ule is disabled                 |                       |                   |                |                |                      |  |  |

|              | 0 = I2C2 mod |                                 |                       |                   |                |                |                      |  |  |

| bit 0        | AD2MD: AD2   | Module Disab                    | le bit <sup>(1)</sup> |                   |                |                |                      |  |  |

|              | 1 = AD2 modu |                                 |                       |                   |                |                |                      |  |  |

|              | 0 = AD2 modu | ile is enabled                  |                       |                   |                |                |                      |  |  |

**Note 1:** The PCFGx bits have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

NOTES:

| U-0                                                                | U-0                            | U-0                                                                                                                                                                                     | U-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|--------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|--|--|--|--|

| —                                                                  | —                              |                                                                                                                                                                                         | —             |                  | SEVOPS<3:0>      |                 |       |  |  |  |  |

| bit 15                                                             | ÷                              |                                                                                                                                                                                         |               | ·                |                  |                 | bit 8 |  |  |  |  |

|                                                                    |                                |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

| U-0                                                                | U-0                            | U-0                                                                                                                                                                                     | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| _                                                                  | —                              |                                                                                                                                                                                         | —             | —                | IUE              | OSYNC           | UDIS  |  |  |  |  |

| bit 7                                                              |                                |                                                                                                                                                                                         |               |                  |                  |                 | bit 0 |  |  |  |  |

|                                                                    |                                |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

| Legend:                                                            |                                |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

| -n = Value a                                                       | t POR                          | '1' = Bit is set                                                                                                                                                                        |               | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |  |  |  |  |

|                                                                    |                                |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

| bit 15-12                                                          | Unimplemer                     | nted: Read as '0                                                                                                                                                                        | )'            |                  |                  |                 |       |  |  |  |  |

| bit 11-8                                                           |                                | 0>: PWM Specia                                                                                                                                                                          | al Event Trig | ger Output Post  | tscale Select bi | ts              |       |  |  |  |  |

|                                                                    | 1111 = 1:16                    | postscale                                                                                                                                                                               |               |                  |                  |                 |       |  |  |  |  |

|                                                                    | •                              |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

|                                                                    | •<br>0001 = 1:2 p              |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

|                                                                    | 0001 = 1.2  p<br>0000 = 1.1  p |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

| bit 7-3                                                            | •                              | nted: Read as '0                                                                                                                                                                        | )'            |                  |                  |                 |       |  |  |  |  |

| bit 2                                                              | IUE: Immedia                   | ate Update Enal                                                                                                                                                                         | ole bit       |                  |                  |                 |       |  |  |  |  |

|                                                                    |                                | to the active PD                                                                                                                                                                        |               | are immediate    |                  |                 |       |  |  |  |  |

|                                                                    | 0 = Updates                    | to the active PD                                                                                                                                                                        | C registers   | are synchronize  | d to the PWM     | ime base        |       |  |  |  |  |

| bit 1                                                              |                                | put Override Sy                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

|                                                                    |                                | <ul> <li>1 = Output overrides via the OVDCON register are synchronized to the PWM time base</li> <li>0 = Output overrides via the OVDCON register occur on next Tcy boundary</li> </ul> |               |                  |                  |                 |       |  |  |  |  |

| <b>h</b> :+ 0                                                      | •                              |                                                                                                                                                                                         |               | gister occur on  | next ICY boun    | bary            |       |  |  |  |  |

| bit 0                                                              |                                | Update Disable                                                                                                                                                                          |               | Duffor registers | are disabled     |                 |       |  |  |  |  |

|                                                                    |                                | from Duty Cycle<br>from Duty Cycle                                                                                                                                                      |               |                  |                  |                 |       |  |  |  |  |

|                                                                    |                                |                                                                                                                                                                                         |               |                  |                  |                 |       |  |  |  |  |

#### REGISTER 16-6: PWMxCON2: PWMx CONTROL REGISTER 2

## 21.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

## 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

## 21.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set, and the TXREQ bit is cleared.

## 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

## 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

## 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = 111. In this mode, the data which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

## 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

### 26.1 DC Characteristics

#### TABLE 26-1: OPERATING MIPS vs. VOLTAGE

| Param | VDD Range Temp Range     |                 | Max MIPS                     |

|-------|--------------------------|-----------------|------------------------------|

| No.   | (in Volts)               | (in °C)         | dsPIC33FJXXXMCX06A/X08A/X10A |

|       | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C  | 40                           |

| _     | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C | 40                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 26-11 for the minimum and maximum BOR values.

#### TABLE 26-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min           | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| dsPIC33FJXXXMCX06A/X08A/X10A                                                                |        |               |     |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40           | —   | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40           | —   | +85  | °C   |

| Extended Temperature Devices                                                                |        |               |     |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40           | _   | +155 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40           | —   | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | PINT + PI/O   |     |      | W    |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |               |     |      |      |

| Maximum Allowed Power Dissipation                                                           | Pdmax  | (TJ — TA)/θJA |     |      | W    |

#### TABLE 26-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        |     | Тур | Max | Unit | Notes |

|-------------------------------------------------------|-----|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θJA | 40  |     | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θJA | 40  | -   | °C/W | 1     |

| Package Thermal Resistance, 80-pin TQFP (12x12x1 mm)  | θJA | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θJA | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θJA | 28  |     | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

## TABLE 26-39:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

|              |                       |                                                              | Standard Op<br>(unless othe<br>Operating ter | rwise st           | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|------------------------|----------|-----------------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                          | Тур <sup>(2)</sup> | Max                    | Units    | Conditions                                                      |

| SP70         | TscP                  | Maximum SCK Input Frequency                                  | _                                            |                    | 11                     | MHz      | See Note 3                                                      |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —                                            |                    |                        | ns       | See parameter DO32 and <b>Note 4</b>                            |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —                                            | _                  | _                      | ns       | See parameter DO31 and <b>Note 4</b>                            |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —                                            | _                  | _                      | ns       | See parameter DO32 and <b>Note 4</b>                            |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —                                            | _                  | _                      | ns       | See parameter DO31 and <b>Note 4</b>                            |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                            | 6                  | 20                     | ns       | —                                                               |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                           |                    |                        | ns       | —                                                               |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                           | _                  | _                      | ns       | —                                                               |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                           | _                  | _                      | ns       | —                                                               |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                          | _                  | _                      | ns       | _                                                               |

| SP51         | TssH2doZ              | SSx                                                          | 10                                           | —                  | 50                     | ns       | -                                                               |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                 |                    |                        | ns       | See Note 4                                                      |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specificiation.

4: Assumes 50 pF load on all SPIx pins.

| CHARA        | AC<br>CTERISTICS      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       | ,          |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                               | Min | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                   |     | _   | 35  | ns    | _          |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                  | 25  | —   | —   | ns    | _          |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                   | 25  | —   | —   | ns    | —          |

| HSP51        | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                      | 15  | —   | 55  | ns    | See Note 2 |

#### TABLE 27-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Assumes 50 pF load on all SPIx pins.

#### TABLE 27-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| -            | AC<br>TERISTICS       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       | -          |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                               | Min | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                   | _   |     | 35  | ns    | —          |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input<br>to SCKx Edge                                                                                                               | 25  | _   | _   | ns    | _          |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                                                                                                                | 25  |     |     | ns    | _          |

| HSP51        | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                      | 15  | _   | 55  | ns    | See Note 2 |

| HSP60        | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                                                                                                    | _   |     | 55  | ns    | —          |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Assumes 50 pF load on all SPIx pins.

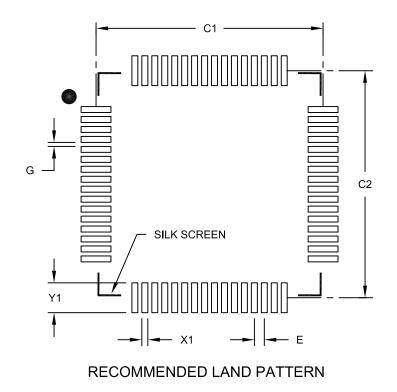

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |      | MILLIMETER | S    |

|--------------------------|-------|------|------------|------|

| Dimension Limits         |       | MIN  | NOM        | MAX  |

| Contact Pitch            | E     |      | 0.50 BSC   |      |

| Contact Pad Spacing      | C1    |      | 11.40      |      |

| Contact Pad Spacing      | C2    |      | 11.40      |      |

| Contact Pad Width (X64)  | X1    |      |            | 0.30 |

| Contact Pad Length (X64) | Y1    |      |            | 1.50 |

| Distance Between Pads    | G     | 0.20 |            |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

## **Revision C (March 2011)**

This revision includes typographical and formatting changes throughout the data sheet text. In addition, all instances of VDDCORE have been removed.

All other major changes are referenced by their respective section in the following table.

| TABLE D-2. WAJON SECTION OF DATES | TABLE B-2: | MAJOR SECTION UPDATES |

|-----------------------------------|------------|-----------------------|

|-----------------------------------|------------|-----------------------|

| Section Name                                                                        | Update Description                                                                                                                       |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Updated the title of Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)".                                                         |

|                                                                                     | The frequency limitation for device PLL start-up conditions was updated in Section 2.7 "Oscillator Value Conditions on Device Start-up". |

|                                                                                     | The second paragraph in Section 2.9 "Unused I/Os" was updated.                                                                           |

| Section 4.0 "Memory Organization"                                                   | The All Resets values for the following SFRs in the Timer Register<br>Map were changed (see Table 4-6):                                  |

|                                                                                     | • TMR1<br>• TMR2                                                                                                                         |

|                                                                                     | • TMR3                                                                                                                                   |

|                                                                                     | • TMR4                                                                                                                                   |

|                                                                                     | • TMR5                                                                                                                                   |

|                                                                                     | • TMR6                                                                                                                                   |

|                                                                                     | • TMR7                                                                                                                                   |

|                                                                                     | • TMR8                                                                                                                                   |

|                                                                                     | • TMR9                                                                                                                                   |

| Section 9.0 "Oscillator Configuration"                                              | Added Note 3 to the OSCCON: Oscillator Control Register (see Register 9-1).                                                              |

|                                                                                     | Added Note 2 to the CLKDIV: Clock Divisor Register (see Register 9-2).                                                                   |

|                                                                                     | Added Note 1 to the PLLFBD: PLL Feedback Divisor Register (see Register 9-3).                                                            |

|                                                                                     | Added Note 2 to the OSCTUN: FRC Oscillator Tuning Register (see Register 9-4).                                                           |

| Section 22.0 "10-bit/12-bit Analog-to-Digital Converter (ADC)"                      | Updated the VREFL references in the ADC1 module block diagram (see Figure 22-1).                                                         |

| Section 23.0 "Special Features"                                                     | Added a new paragraph and removed the third paragraph in <b>Section 23.1 "Configuration Bits"</b> .                                      |

|                                                                                     | Added the column "RTSP Effects" to the Configuration Bits Descriptions (see Table 23-2).                                                 |

| IPC13 (Interrupt Priority Control 13)      | 125 |

|--------------------------------------------|-----|

| IPC14 (Interrupt Priority Control 14)      |     |

| IPC15 (Interrupt Priority Control 15)      |     |

| IPC16 (Interrupt Priority Control 16)      |     |

| IPC17 (Interrupt Priority Control 17)      | 129 |

| IPC2 (Interrupt Priority Control 2)        |     |

| IPC3 (Interrupt Priority Control 3)        |     |

| IPC4 (Interrupt Priority Control 4)        |     |

| IPC5 (Interrupt Priority Control 5)        |     |

| IPC6 (Interrupt Priority Control 6)        | 118 |

| IPC7 (Interrupt Priority Control 7)        | 119 |

| IPC8 (Interrupt Priority Control 8)        |     |

| IPC9 (Interrupt Priority Control 9)        |     |

| NVMCOM (Flash Memory Control)              |     |

| OCxCON (Output Compare x Control)          |     |

| OSCCON (Oscillator Control)                |     |

| OSCTUN (FRC Oscillator Tuning)             |     |

| PLLFBD (PLL Feedback Divisor)              |     |

| PMD1 (Peripheral Module Disable Control 1) |     |

| PMD2 (Peripheral Module Disable Control 2) | 157 |

| PMD3 (Peripheral Module Disable Control 3) | 159 |

| PWMxCON1 (PWMx Control 1)                  | 184 |

| PWMxCON2 (PWMx Control 2)                  |     |

| PxDC1 (PWMx Duty Cycle 1)                  |     |

| PxDC2 (PWMx Duty Cycle 2)                  |     |

| PxDC3 (PWMx Duty Cycle 3)                  |     |

| PxDC4 (PWMx Duty Cycle 4)                  | 192 |

| PxDTCON1 (PWMx Dead-Time Control 1)        | 186 |

| PxDTCON2 (PWMx Dead-Time Control 2)        | 187 |

| PxFLTACON (PWMx Fault A Control)           | 188 |

| PxFLTBCON (PWMx Fault B Control)           | 189 |

| PxOVDCON (PWMx Override Control)           | 190 |

| PxSECMP (PWMx Special Event Compare)       |     |

| PxTCON (PWMx Time Base Control)            |     |

| PxTMR (PWMx Timer Count Value)             |     |

| PxTPER (PWMx Time Base Period)             |     |

| QEIxCON (QEIx Control)                     |     |

| RCON (Reset Control)                       |     |

| SPIxCON1 (SPIx Control 1)                  | 200 |

| SPIxCON2 (SPIx Control 2)                  |     |

| SPIxSTAT (SPIx Status and Control)         |     |

| SR (CPU STATUS)                            |     |

| SR (CPU Status)                            |     |

| T1CON (Timer1 Control)                     | 166 |

| TxCON (T2CON, T4CON, T6CON or              |     |

| T8CON Control)                             | 170 |

| TyCON (T3CON, T5CON, T7CON or              |     |

| T9CON Control)                             |     |

| UxMODE (UARTx Mode)                        |     |

| UxSTA (UARTx Status and Control)           | 215 |

| Reset                                      | 00  |

| Clock Source Selection                     |     |

| Special Function Register States           |     |

| Times                                      |     |

| Reset Sequence                             |     |

| Resets                                     |     |

| Revision History                           | 500 |

### S

| Serial Peripheral Interface (SPI)     | 197 |

|---------------------------------------|-----|

| Software Simulator (MPLAB SIM)        |     |

| Software Stack Pointer, Frame Pointer |     |

| CALL Stack Frame                      | 63  |

| Special Features of the CPU           | 259 |

| SPI Module                            |     |

| SPI1 Register Map                     | 51  |

| SPI2 Register Map                     | 51  |

| Symbols Used in Opcode Descriptions   |     |

| System Control                        |     |

| Register Map                          | 62  |

|                                       |     |

## т

| •                                                |     |

|--------------------------------------------------|-----|

| Temperature and Voltage Specifications           |     |

| AC                                               | 333 |

| Timer1                                           | 165 |

| Timer2/3, Timer4/5, Timer6/7 and Timer8/9        | 167 |

| Timing Characteristics                           |     |

| CLKO and I/O                                     | 293 |

| Timing Diagrams                                  |     |

| 10-Bit A/D Conversion (CHPS<1:0> = 01,           |     |

| SIMSAM = 0, ASAM = 0,                            |     |

| SSRC<2:0> = 000)                                 | 326 |

| 10-Bit A/D Conversion (CHPS<1:0> = 01,           |     |

| SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111,           |     |

| SAMC<4:0> = 00001)                               |     |

| 12-Bit A/D Conversion (ASAM = 0, SSRC = 000)     |     |

| CAN I/O                                          | 320 |

| External Clock                                   | 291 |

| I2Cx Bus Data (Master Mode)                      | 316 |

| I2Cx Bus Data (Slave Mode)                       | 318 |

| I2Cx Bus Start/Stop Bits (Master Mode)           |     |

| I2Cx Bus Start/Stop Bits (Slave Mode)            | 318 |

| Input Capture (CAPx)                             | 298 |

| Motor Control PWM                                |     |

| Motor Control PWM Fault                          | 300 |

| OC/PWM                                           | 299 |

| Output Compare (OCx)                             | 298 |

| QEA/QEB Input                                    | 301 |

| QEI Module Index Pulse                           | 302 |

| Reset, Watchdog Timer, Oscillator Start-up Timer |     |

| and Power-up Timer                               | 294 |

| Timer1, 2, 3, 4, 5, 6, 7, 8, 9 External Clock    |     |

| TimerQ (QEI Module) External Clock               | 303 |

| Timing Requirements                              |     |

| ADC Conversion (10-bit mode)                     |     |

| ADC Conversion (12-bit Mode)                     | 337 |

| CLKO and I/O                                     | 293 |

| External Clock                                   | 291 |

| Input Capture                                    |     |

| SPIx Master Mode (CKE = 0)                       |     |

| SPIx Module Master Mode (CKE = 1)                | 334 |

| SPIx Module Slave Mode (CKE = 0)                 | 335 |

| SPIx Module Slave Mode (CKE = 1)                 | 335 |