Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc710at-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

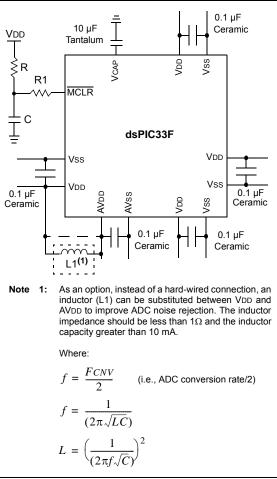

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

# 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 26.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 23.2 "On-Chip Voltage Regulator"** for details.

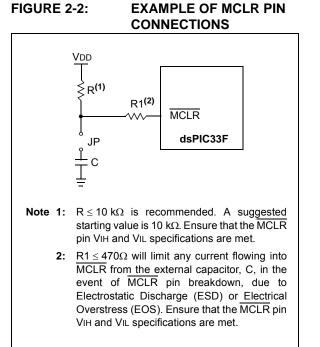

# 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### TABLE 4-25:ECAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1FOR dsPIC33FJXXXMC708A/710A DEVICES (CONTINUED)

| File Name  | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C2RXF11SID | 056C |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | -     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C2RXF11EID | 056E |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<  | <7:0> |       |       |       | xxxx          |

| C2RXF12SID | 0570 |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C2RXF12EID | 0572 |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<  | <7:0> |       |       |       | xxxx          |

| C2RXF13SID | 0574 |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | —     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C2RXF13EID | 0576 |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<  | <7:0> |       |       |       | xxxx          |

| C2RXF14SID | 0578 |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C2RXF14EID | 057A |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<  | <7:0> |       |       |       | xxxx          |

| C2RXF15SID | 057C |        |        |        | SID<   | 10:3>  |        |       |       |       | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C2RXF15EID | 057E |        |        |        | EID<   | 15:8>  |        |       |       |       |          |       | EID<  | <7:0> |       |       |       | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PORTA REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|--------|--------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISA               | 02C0 | TRISA15 | TRISA14 | _      | _      | _      | TRISA10 | TRISA9 | -     | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | C6FF          |

| PORTA               | 02C2 | RA15    | RA14    | _      | _      | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA                | 02C4 | LATA15  | LATA14  | _      | _      | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA <sup>(2)</sup> | 06C0 | ODCA15  | ODCA14  | —      | —      | -      |         | -      | -     | _      | _      | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-27: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for high pin count devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (e.g., [W7+W2]) is used, Modulo Address correction is performed but the contents of the register remain unchanged.

### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order; thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when the following conditions exist:

- The BWM bits (W register selection) in the MODCON register are any value other than 15 (the stack cannot be accessed using Bit-Reversed Addressing).

- 2. The BREN bit is set in the XBREV register.

- 3. The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is only executed for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data; normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed Addressing should not be enabled |

|-------|---------------------------------------------------------------------|

|       | together. In the event that the user                                |

|       | attempts to do so, Bit-Reversed Address-                            |

|       | ing will assume priority for the X WAGU,                            |

|       | and X WAGU Modulo Addressing will be                                |

|       | disabled. However, Modulo Addressing will                           |

|       | continue to function in the X RAGU.                                 |

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Set up NVMCO | N for row programming operations | 3     |                                       |

|----------------|----------------------------------|-------|---------------------------------------|

| MOV            | #0x4001, W0                      | ;     |                                       |

| MOV            | W0, NVMCON                       | ;     | Initialize NVMCON                     |

| ; Set up a poi | nter to the first program memory | / loc | ation to be written                   |

| ; program memo | ry selected, and writes enabled  |       |                                       |

| MOV            | #0x0000, W0                      | ;     |                                       |

| MOV            | W0, TBLPAG                       | ;     | Initialize PM Page Boundary SFR       |

| MOV            | #0x6000, W0                      | ;     | An example program memory address     |

| ; Perform the  | TBLWT instructions to write the  | latc  | hes                                   |

| ; 0th_program_ | word                             |       |                                       |

| MOV            | #LOW_WORD_0, W2                  | ;     |                                       |

| MOV            | #HIGH_BYTE_0, W3                 | ;     |                                       |

| TBLWTL         | W2, [W0]                         | ;     | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; 1st_program_ | word                             |       |                                       |

| MOV            | #LOW_WORD_1, W2                  | ;     |                                       |

| MOV            | #HIGH_BYTE_1, W3                 | ;     |                                       |

| TBLWTL         | W2, [W0]                         | ;     | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; 2nd_program  | _word                            |       |                                       |

|                | #LOW_WORD_2, W2                  | ;     |                                       |

|                | <pre>#HIGH_BYTE_2, W3</pre>      | ;     |                                       |

|                | W2, [W0]                         |       | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| •              |                                  |       |                                       |

| •              |                                  |       |                                       |

| •              |                                  |       |                                       |

| ; 63rd_program | —                                |       |                                       |

| MOV            | #LOW_WORD_31, W2                 | ;     |                                       |

| MOV            | #HIGH_BYTE_31, W3                | ;     |                                       |

|                | W2, [W0]                         |       | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

|                |                                  |       |                                       |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | ;                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ; Insert two NOPs after the             |

| NOP  |             | ; erase command is asserted             |

|      |             |                                         |

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                |

|------------------|--------------------------------------|-------------|--------------|---------------------------------|

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0     |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Capture 1           |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1          |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                     |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0            |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2           |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2          |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                     |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                     |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error              |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done       |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver           |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter        |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – ADC 1                    |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1            |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                        |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events       |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events      |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                        |

| 27               | 19                                   | 0x00003A    | 0x00013A     | Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1     |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – ADC 2                    |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7           |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8           |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2            |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3          |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4          |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                     |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                     |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2     |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver           |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter        |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error              |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done       |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3            |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3           |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4           |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5           |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6           |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5          |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6          |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7          |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8          |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                        |

#### TABLE 7-1: INTERRUPT VECTORS

© 2009-2012 Microchip Technology Inc.

| R/W-0         | R/W-0          | U-0                              | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |

|---------------|----------------|----------------------------------|------------------|----------------------|------------------|----------------|---------|

| T6IF          | DMA4IF         | _                                | OC8IF            | OC7IF                | OC6IF            | OC5IF          | IC6IF   |

| bit 15        |                |                                  |                  |                      |                  |                | bit 8   |

| R/W-0         | R/W-0          | R/W-0                            | R/W-0            | R/W-0                | R/W-0            | R/W-0          | R/W-0   |

| IC5IF         | IC4IF          | IC3IF                            | DMA3IF           | C1IF                 | C1RXIF           | SPI2IF         | SPI2EIF |

| bit 7         |                |                                  |                  |                      | I                |                | bit (   |

| Legend:       |                |                                  |                  |                      |                  |                |         |

| R = Readable  | e bit          | W = Writable                     | bit              | U = Unimple          | mented bit, read | l as '0'       |         |

| -n = Value at | POR            | '1' = Bit is set                 |                  | '0' = Bit is cle     | eared            | x = Bit is unk | nown    |

| bit 15        | T6IF: Timer6   | Interrupt Flag                   | Status bit       |                      |                  |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 14        |                | •                                |                  | Complete Interi      | rupt Flag Status | bit            |         |

|               |                | request has oc<br>request has no |                  | ·                    |                  |                |         |

| bit 13        |                | ted: Read as '                   |                  |                      |                  |                |         |

| bit 12        | OC8IF: Outpu   | ut Compare Ch                    | annel 8 Interr   | upt Flag Status      | s bit            |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 11        | OC7IF: Outpu   | ut Compare Ch                    | annel 7 Interr   | upt Flag Status      | s bit            |                |         |

|               |                | request has oc                   |                  |                      |                  |                |         |

|               |                | request has no                   |                  |                      |                  |                |         |

| bit 10        | •              | ut Compare Ch                    |                  | upt Flag Status      | s bit            |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 9         | -              | ut Compare Ch                    |                  | upt Flag Status      | s bit            |                |         |

|               |                | request has oc<br>request has no |                  |                      |                  |                |         |

| bit 8         | •              | Capture Chann                    |                  | -lag Status hit      |                  |                |         |

| bit o         | 1 = Interrupt  | request has oc<br>request has no | curred           | lag Status bit       |                  |                |         |

| bit 7         | •              | Capture Chann                    |                  | -lao Status bit      |                  |                |         |

|               | •              | request has oc                   | •                |                      |                  |                |         |

|               |                | request has no                   |                  |                      |                  |                |         |

| bit 6         | IC4IF: Input C | Capture Chann                    | el 4 Interrupt I | -lag Status bit      |                  |                |         |

|               |                | request has oc                   |                  |                      |                  |                |         |

| bit 5         | -              | request has no<br>Capture Chann  |                  | -<br>Elaa Status hit |                  |                |         |

| bit 5         | 1 = Interrupt  | request has oc<br>request has no | curred           | ay status bit        |                  |                |         |

| bit 4         | •              | •                                |                  | omnlete Inter        | rupt Flag Status | hit            |         |

|               | 1 = Interrupt  | request has oc<br>request has no | curred           |                      | apting Status    | JA             |         |

| bit 3         | -              | l Event Interrup                 |                  | bit                  |                  |                |         |

| Sit U         |                | request has oc                   | -                |                      |                  |                |         |

|               |                | request has no                   |                  |                      |                  |                |         |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

# 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJXXXMCX06A/X08A/X10A devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- · Software-controlled Doze mode

- · Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### 10.1 Clock Frequency and Clock Switching

dsPIC33FJXXXMCX06A/X08A/X10A devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

#### 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJXXXMCX06A/X08A/X10A devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode has the following features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports and peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of the following events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

### 10.2.2 IDLE MODE

Idle mode has the following features:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of the following events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

### 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 10.4 Peripheral Module Disable

The Peripheral Module Disable registers (PMD) provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

#### REGISTER 16-4: PxSECMP: PWMx SPECIAL EVENT COMPARE REGISTER

| R/W-0                  | R/W-0        | R/W-0                        | R/W-0          | R/W-0                        | R/W-0            | R/W-0           | R/W-0 |

|------------------------|--------------|------------------------------|----------------|------------------------------|------------------|-----------------|-------|

| SEVTDIR <sup>(1)</sup> |              |                              | S              | EVTCMP<14:8                  | >(2)             |                 |       |

| bit 15                 |              |                              |                |                              |                  |                 | bit 8 |

|                        |              |                              |                |                              |                  |                 |       |

| R/W-0                  | R/W-0        | R/W-0                        | R/W-0          | R/W-0                        | R/W-0            | R/W-0           | R/W-0 |

|                        |              |                              | SEVTCM         | /IP<7:0> <b>(2)</b>          |                  |                 |       |

| bit 7                  |              |                              |                |                              |                  |                 | bit 0 |

|                        |              |                              |                |                              |                  |                 |       |

| Legend:                |              |                              |                |                              |                  |                 |       |

| R = Readable           | bit          | W = Writable I               | bit            | U = Unimplen                 | nented bit, read | d as '0'        |       |

| -n = Value at F        | POR          | '1' = Bit is set             |                | '0' = Bit is clea            | ared             | x = Bit is unkr | nown  |

|                        |              |                              |                |                              |                  |                 |       |

| bit 15                 | SEVTDIR: S   | Special Event Trig           | gger Time Ba   | se Direction bit             | (1)              |                 |       |

|                        | 1 = A Specia | al Event Trigger v           | will occur whe | en the PWM tim               | ie base is cour  | ting downward   | S     |

|                        |              | al Event Trigger v           |                |                              | ie base is cour  | iting upwards   |       |

| bit 14-0               | SEVTCMP<     | : <b>14:0&gt;:</b> Special E | vent Compa     | re Value bits <sup>(2)</sup> |                  |                 |       |

|                        |              |                              |                |                              |                  |                 |       |

**Note 1:** SEVTDIR is compared with PTDIR (PTMR<15>) to generate the Special Event Trigger.

2: SEVTCMP<14:0> is compared with PTMR<14:0> to generate the Special Event Trigger.

| R/W-0                        | R/W-0                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                         | U-0                                                                                                                                                                       | U-0                          | U-0              | U-0              | U-0   |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|------------------|-------|

| FRMEN                        | SPIFSD                                                                                                                                                                                   | FRMPOL                                                                                                                                                                                                                        |                                                                                                                                                                           | _                            |                  |                  | _     |

| bit 15                       |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                  | bit 8 |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                  |       |

| U-0                          | U-0                                                                                                                                                                                      | U-0                                                                                                                                                                                                                           | U-0                                                                                                                                                                       | U-0                          | U-0              | R/W-0            | U-0   |

|                              | —                                                                                                                                                                                        | —                                                                                                                                                                                                                             |                                                                                                                                                                           | —                            |                  | FRMDLY           | —     |

| bit 7                        |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                  | bit C |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                  |       |

| Legend:                      |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                  |       |

| R = Readable                 | e bit                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                                  | bit                                                                                                                                                                       | U = Unimplen                 | nented bit, read | l as '0'         |       |

| -n = Value at I              | POR                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                              |                                                                                                                                                                           | '0' = Bit is clea            | ared             | x = Bit is unkno | own   |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                  |       |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                  |       |

| bit 15                       |                                                                                                                                                                                          | ned SPIx Supp                                                                                                                                                                                                                 |                                                                                                                                                                           |                              |                  |                  |       |

| bit 15                       | 1 = Framed S                                                                                                                                                                             | Plx support en                                                                                                                                                                                                                | abled (SSx p                                                                                                                                                              | in used as fram              | e Sync pulse ir  | nput/output)     |       |

|                              | 1 = Framed S<br>0 = Framed S                                                                                                                                                             | Plx support en<br>Plx support dis                                                                                                                                                                                             | abled ( <del>SSx</del> p<br>sabled                                                                                                                                        |                              | e Sync pulse ir  | nput/output)     |       |

| bit 15<br>bit 14             | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar                                                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse                                                                                                                                                                            | abled ( <del>SSx</del> p<br>sabled<br>Direction Cor                                                                                                                       |                              | e Sync pulse ir  | nput/output)     |       |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar<br>1 = Frame Sy                                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input                                                                                                                                                          | abled ( <del>SSx</del> p<br>sabled<br>Direction Cor<br>(slave)                                                                                                            |                              | e Sync pulse ir  | nput/output)     |       |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar<br>1 = Frame Sy<br>0 = Frame Sy                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse                                                                                                                                                                            | abled (SSx p<br>sabled<br>Direction Coi<br>(slave)<br>tt (master)                                                                                                         |                              | e Sync pulse ir  | nput/output)     |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra                                                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu                                                                                                                                        | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit                                                                                       |                              | e Sync pulse ir  | nput/output)     |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy                                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls                                                                                                                       | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high                                                                           |                              | e Sync pulse ir  | nput/output)     |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act                                                                                                    | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high<br>ive-low                                                                |                              | e Sync pulse ir  | nput/output)     |       |

| bit 14<br>bit 13             | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen                                                | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act                                                                                 | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'                                                          | ntrol bit                    | e Sync pulse ir  | nput/output)     |       |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy                                | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br>ted: Read as '<br>me Sync Pulse<br>nc pulse coinci                           | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first                      | trol bit<br>bit<br>bit clock | e Sync pulse ir  | nput/output)     |       |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy<br>0 = Frame Sy | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br><b>ted:</b> Read as 'u<br>me Sync Pulse<br>nc pulse coinci<br>nc pulse prece | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first<br>cdes first bit cl | trol bit<br>bit<br>bit clock |                  | nput/output)     |       |

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BWRP      | FBS      | Immediate      | Boot Segment Program Flash Write Protection bit<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BSS<2:0>  | FBS      | Immediate      | <ul> <li>Boot Segment Program Flash Code Protection Size bits</li> <li>x11 = No boot program Flash segment</li> <li>Boot space is 1K IW less VS:</li> <li>110 = Standard security; boot program Flash segment starts at end of VS, ends at 0007FEh</li> <li>010 = High security; boot program Flash segment starts at end of VS, ends at 0007FEh</li> <li>Boot space is 4K IW less VS:</li> <li>101 = Standard security; boot program Flash segment starts at end of VS, ends at 001FFEh</li> <li>001 = High security; boot program Flash segment starts at end of VS, ends at 001FFEh</li> <li>001 = High security; boot program Flash segment starts at end of VS, ends at 001FFEh</li> <li>001 = Standard security; boot program Flash segment starts at end of VS, ends at 001FFEh</li> <li>001 = Standard security; boot program Flash segment starts at end of VS, ends at 001FFEh</li> <li>001 = High security; boot program Flash segment starts at end of VS, ends at 003FFEh</li> <li>000 = High security; boot program Flash segment starts at end of VS, ends at 003FFEh</li> </ul> |

| RBS<1:0>  | FBS      | Immediate      | Boot Segment RAM Code Protection bits<br>11 = No boot RAM defined<br>10 = Boot RAM is 128 bytes<br>01 = Boot RAM is 256 bytes<br>00 = Boot RAM is 1024 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SWRP      | FSS      | Immediate      | Secure Segment Program Flash Write Protection bit<br>1 = Secure segment may be written<br>0 = Secure segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### TABLE 23-2: CONFIGURATION BITS DESCRIPTION

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                             |

|-----------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0>  | FSS      | Immediate      | Secure Segment Program Flash Code Protection Size bits                                                                                  |

|           |          |                | (FOR 128K and 256K DEVICES)                                                                                                             |

|           |          |                | x11 = No secure program Flash segment                                                                                                   |

|           |          |                | <u>Secure space is 8K IW less BS:</u><br>110 = Standard security; secure program Flash segment starts at end of<br>BS, ends at 0x003FFE |

|           |          |                | 010 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x003FFE                                              |

|           |          |                | Secure space is 16K IW less BS:                                                                                                         |

|           |          |                | 101 = Standard security; secure program Flash segment starts at end of BS, ends at 0x007FFE                                             |

|           |          |                | 001 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x007FFE                                              |

|           |          |                | Secure space is 32K IW less BS:                                                                                                         |

|           |          |                | 100 = Standard security; secure program Flash segment starts at end of<br>BS, ends at 0x00FFFE                                          |

|           |          |                | 000 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x00FFFE                                              |

|           |          |                | (FOR 64K DEVICES)                                                                                                                       |

|           |          |                | x11 = No Secure program Flash segment                                                                                                   |

|           |          |                | Secure space is 4K IW less BS:<br>110 = Standard security; secure program Flash segment starts at end of                                |

|           |          |                | BS, ends at 0x001FFE<br>010 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x001FFE                      |

|           |          |                | Secure space is 8K IW less BS:<br>101 = Standard security; secure program Flash segment starts at end of                                |

|           |          |                | BS, ends at 0x003FFE                                                                                                                    |

|           |          |                | 001 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x003FFE                                              |

|           |          |                | Secure space is 16K IW less BS:                                                                                                         |

|           |          |                | 100 = Standard security; secure program Flash segment starts at end of BS, ends at 007FFEh                                              |

|           |          |                | 000 = High security; secure program Flash segment starts at end of BS,<br>ends at 0x007FFE                                              |

| RSS<1:0>  | FSS      | Immediate      | Secure Segment RAM Code Protection bits<br>11 = No secure RAM defined                                                                   |

|           |          |                | 10 = Secure RAM is 256 bytes less BS RAM                                                                                                |

|           |          |                | 01 = Secure RAM is 2048 bytes less BS RAM<br>00 = Secure RAM is 4096 bytes less BS RAM                                                  |

| GSS<1:0>  | FGS      | Immediate      | General Segment Code-Protect bits<br>11 = User program memory is not code-protected                                                     |

|           |          |                | <ul> <li>10 = Standard security; general program Flash segment starts at end of<br/>SS, ends at EOM</li> </ul>                          |

|           |          |                | 0x = High security; general program Flash segment starts at end of SS,<br>ends at EOM                                                   |

#### TABLE 23-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

| DC CHARACTERISTICS |            |                                                                             |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |       |                |  |

|--------------------|------------|-----------------------------------------------------------------------------|------|------------------------------------------------------|-----|-------|----------------|--|

| Param<br>No.       | Symbol     | Characteristic                                                              | Min  | Тур <sup>(1)</sup>                                   | Max | Units | Conditions     |  |

| Operati            | ng Voltage | 9                                                                           |      |                                                      |     |       |                |  |

| DC10               | Supply V   | oltage                                                                      |      |                                                      |     |       |                |  |

|                    | Vdd        | —                                                                           | 3.0  |                                                      | 3.6 | V     | —              |  |

| DC12               | Vdr        | RAM Data Retention Voltage <sup>(2)</sup>                                   | 1.8  | _                                                    | _   | V     | —              |  |

| DC16               | VPOR       | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal            |      | _                                                    | Vss | V     | _              |  |

| DC17               | SVDD       | <b>V</b> DD <b>Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.03 | _                                                    | _   | V/ms  | 0-3.0V in 0.1s |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: This is the limit to which VDD can be lowered without losing RAM data.

# TABLE 26-38:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | Standard Op<br>(unless othe<br>Operating ter | erwise st | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|--------------------------------------------------------------|----------------------------------------------|-----------|------------------------|----------|-----------------------------------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min Typ <sup>(2)</sup> Max Units             |           |                        |          | Conditions                                                      |

| SP70               | TscP                  | Maximum SCK Input Frequency                                  | _                                            | _         | 15                     | MHz      | See Note 3                                                      |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                            | —         |                        | ns       | See parameter DO32 and <b>Note 4</b>                            |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                            | _         | _                      | ns       | See parameter DO31 and <b>Note 4</b>                            |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                            | _         | _                      | ns       | See parameter DO32 and <b>Note 4</b>                            |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | _                                            | _         | -                      | ns       | See parameter DO31 and <b>Note 4</b>                            |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | _                                            | 6         | 20                     | ns       | —                                                               |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                           | _         |                        | ns       | —                                                               |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                           | _         | _                      | ns       | —                                                               |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                           | _         | _                      | ns       | —                                                               |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                          | _         | _                      | ns       | —                                                               |

| SP51               | TssH2doZ              | SSx                                                          | 10                                           | —         | 50                     | ns       | —                                                               |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                 | —         |                        | ns       | See Note 4                                                      |