#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TC)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-VQFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ata6614q-plqw |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4. LIN System-basis-chip Block

# 4.1 Features

Master and slave operation possible

Supply voltage up to 40V

Operating voltage  $V_S = 5V$  to 27V

Typically 10 $\mu$ A supply current during sleep mode

Typically 35µA supply current in silent mode

Linear low-drop voltage regulator, 85mA current capability:

Normal, fail-safe, and silent mode

$V_{CC} = 5.0V \pm 2\%$

In sleep mode  $V_{CC}$  is switched off

VCC undervoltage detection (4ms reset time) and watchdog reset logical combined at open drain output NRES

Negative trigger input for watchdog

Adjustable watchdog time via external resistor

Boosting the voltage regulator possible with an external NPN transistor

LIN physical layer according to LIN 2.0, 2.1 and SAEJ2602-2

Wake-up capability via LIN-bus, wake pin, or KI\_15 pin

INH output to control an external voltage regulator or to switch off the master pull up resistor

TXD time-out timer

Bus pin is overtemperature and short-circuit protected versus GND and battery

Advanced EMC and ESD performance

Fulfills the OEM "Hardware Requirements for LIN in Automotive Applications Rev.1.1"

Interference and damage protection according to ISO7637

# 4.2 Description

The Atmel<sup>®</sup> ATA6630 is a fully integrated LIN transceiver, which complies with the LIN 2.0, 2.1 and SAEJ2602-2 specifications. It has a low-drop voltage regulator for 5V/85mA output and a window watchdog. The voltage regulator is able to source up to 85mA, but the output current can be boosted by using an external NPN transistor. The Atmel ATA6630 is designed to handle the low-speed data communication in vehicles, e.g., in convenience electronics. Improved slope control at the LIN-driver ensures secure data communication up to 20kBaud. Sleep Mode and Silent Mode guarantee very low current consumption.

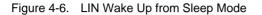

A falling edge at the LIN pin followed by a dominant bus level maintained for a certain time period ( $>t_{bus}$ ) and a rising edge at pin LIN result in a remote wake-up request. The device switches from Sleep Mode to Fail-safe Mode.

The VCC regulator is activated, and the internal LIN slave termination resistor is switched on. The remote wake-up re-quest is indicated by a low level at the RXD pin to interrupt the microcontroller (see Figure 4-6 on page 15).

EN high can be used to switch directly from Sleep/Silent to Fail-safe Mode. If EN is still high after VCC ramp up and undervoltage reset time, the IC switches to the Normal Mode.

# 5.6.5 Stack Pointer

The stack is mainly used for storing temporary data, for storing local variables and for storing return addresses after interrupts and subroutine calls. Note that the stack is implemented as growing from higher to lower memory locations. The stack pointer register always points to the top of the stack. The stack pointer points to the data SRAM stack area where the subroutine and interrupt stacks are located. A stack PUSH command will decrease the stack pointer.

The stack in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are enabled. Initial stack pointer value equals the last address of the internal SRAM and the stack pointer must be set to point above start of the SRAM, see Figure 5-8 on page 41.

See Table 5-1 for stack pointer details.

Table 5-1. Stack Pointer Instructions

| Instruction            | Stack pointer    | Description                                                                                  |

|------------------------|------------------|----------------------------------------------------------------------------------------------|

| PUSH                   | Decremented by 1 | Data is pushed onto the stack                                                                |

| CALL<br>ICALL<br>RCALL | Decremented by 2 | Return address is pushed onto the stack with a subroutine call or interrupt                  |

| POP                    | Incremented by 1 | Data is popped from the stack                                                                |

| RET<br>RETI            | Incremented by 2 | Return address is popped from the stack with return from subroutine or return from interrupt |

The AVR<sup>®</sup> stack pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is implementation dependent. Note that the data space in some implementations of the AVR architecture is so small that only SPL is needed. In this case, the SPH register will not be present.

5.6.5.1 SPH and SPL – Stack Pointer High and Stack Pointer Low Register

| Bit           | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

| 0x3E (0x5E)   | SP15   | SP14   | SP13   | SP12   | SP11   | SP10   | SP9    | SP8    | SPH |

| 0x3D (0x5D)   | SP7    | SP6    | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | SPL |

|               | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |     |

| Read/Write    | R/W    |     |

|               | R/W    |     |

| Initial Value | RAMEND |     |

|               | RAMEND |     |

EEPROM data corruption can easily be avoided by following this design recommendation:

Keep the AVR<sup>®</sup> RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal brown-out Detector (BOD). If the detection level of the internal BOD does not match the needed detection level, an external low  $V_{CC}$  reset protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

# 5.7.5 I/O Memory

The I/O space definition of the ATmega328P is shown in Section 5.30 "Register Summary" on page 294.

All ATmega328P I/Os and peripherals are placed in the I/O space. All I/O locations may be accessed by the LD/LDS/LDD and ST/STS/STD instructions, transferring data between the 32 general purpose working registers and the I/O space. I/O registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set section for more details. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega328P is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

The I/O and peripherals control registers are explained in later sections.

#### 5.7.5.1 General Purpose I/O Registers

The ATmega328P contains three general purpose I/O registers. These registers can be used for storing any information, and they are particularly useful for storing global variables and status flags. General purpose I/O registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI, CBI, SBIS, and SBIC instructions.

# 5.7.6 Register Description

# 5.7.6.1 EEARH and EEARL - The EEPROM Address Register

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |       |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x22 (0x42)   | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

| 0x21 (0x41)   | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

|               | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | Х     |       |

|               | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |       |

• Bits 15..9 - Res: Reserved Bits

These bits are reserved bits in the ATmega328P and will always read as zero.

#### • Bits 8..0 - EEAR8..0: EEPROM Address

The EEPROM address registers – EEARH and EEARL specify the EEPROM address in the 256/512/512/1K bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 255/511/511/1023. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

EEAR8 is an unused bit in ATmega328P and must always be written to zero.

# Atmel

# 5.13.4.4 PINB – The Port B Input Pins Address

|          | Bit           | 7         | 6         | 5         | 4       | 3      | 2      | 1      | 0      |       |

|----------|---------------|-----------|-----------|-----------|---------|--------|--------|--------|--------|-------|

|          | 0x03 (0x23)   | PINB7     | PINB6     | PINB5     | PINB4   | PINB3  | PINB2  | PINB1  | PINB0  | PINB  |

|          | Read/Write    | R         | R         | R         | R       | R      | R      | R      | R      |       |

|          | Initial Value | N/A       | N/A       | N/A       | N/A     | N/A    | N/A    | N/A    | N/A    |       |

| 5.13.4.5 | PORTC -       | The Port  | C Data R  | legister  |         |        |        |        |        |       |

|          | Bit           | 7         | 6         | 5         | 4       | 3      | 2      | 1      | 0      |       |

|          | 0x08 (0x28)   | -         | PORTC6    | PORTC5    | PORTC4  | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

|          | Read/Write    | R         | R/W       | R/W       | R/W     | R/W    | R/W    | R/W    | R/W    |       |

|          | Initial Value | 0         | 0         | 0         | 0       | 0      | 0      | 0      | 0      |       |

| 5.13.4.6 | DDRC – T      | he Port C | CData Di  | rection R | egister |        |        |        |        |       |

|          | Bit           | 7         | 6         | 5         | 4       | 3      | 2      | 1      | 0      |       |

|          | 0x07 (0x27)   | -         | DDC6      | DDC5      | DDC4    | DDC3   | DDC2   | DDC1   | DDC0   | DDRC  |

|          | Read/Write    | R         | R/W       | R/W       | R/W     | R/W    | R/W    | R/W    | R/W    |       |

|          | Initial Value | 0         | 0         | 0         | 0       | 0      | 0      | 0      | 0      |       |

| 5.13.4.7 | PINC – Th     | e Port C  | Input Pin | s Address | 3       |        |        |        |        |       |

|          | Bit           | 7         | 6         | 5         | 4       | 3      | 2      | 1      | 0      | -     |

|          | 0x06 (0x26)   | -         | PINC6     | PINC5     | PINC4   | PINC3  | PINC2  | PINC1  | PINC0  | PINC  |

|          | Read/Write    | R         | R         | R         | R       | R      | R      | R      | R      | _     |

|          | Initial Value | 0         | N/A       | N/A       | N/A     | N/A    | N/A    | N/A    | N/A    |       |

| 5.13.4.8 | PORTD -       | The Port  | D Data R  | legister  |         |        |        |        |        |       |

|          | Bit           | 7         | 6         | 5         | 4       | 3      | 2      | 1      | 0      |       |

|          | 0x0B (0x2B)   | PORTD7    | PORTD6    | PORTD5    | PORT D4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

|          | Read/Write    | R/W       | R/W       | R/W       | R/W     | R/W    | R/W    | R/W    | R/W    |       |

|          | Initial Value | 0         | 0         | 0         | 0       | 0      | 0      | 0      | 0      |       |

| 5.13.4.9 | DDRD – T      | he Port D | ) Data Di | rection R | egister |        |        |        |        |       |

|          | Bit           | 7         | 6         | 5         | 4       | 3      | 2      | 1      | 0      | _     |

|          | 0x0A (0x2A)   | DDD7      | DDD6      | DDD5      | DDD4    | DDD3   | DDD2   | DDD1   | DDD0   | DDRD  |

|          | Read/Write    | R/W       | R/W       | R/W       | R/W     | R/W    | R/W    | R/W    | R/W    |       |

|          | Initial Value | 0         | 0         | 0         | 0       | 0      | 0      | 0      | 0      |       |

| 5.13.4.1 | 0 PIND – Th   | e Port D  | Input Pin | s Address | 6       |        |        |        |        |       |

|          | Bit           | 7         | 6         | 5         | 4       | 3      | 2      | 1      | 0      |       |

|          | 0x09 (0x29)   | PIND7     | PIND6     | PIND5     | PIND4   | PIND3  | PIND2  | PIND1  | PIND0  | PIND  |

|          | Read/Write    | R         | R         | R         | R       | R      | R      | R      | R      |       |

|          | Initial Value | N/A       | N/A       | N/A       | N/A     | N/A    | N/A    | N/A    | N/A    |       |

When OC0A is connected to the pin, the function of the COM0A1:0 bits depends on the WGM02:0 bit setting. Table 5-41 shows the COM0A1:0 bit functionality when the WGM02:0 bits are set to a normal or CTC mode (non-PWM).

| COM0A1 | COM0A0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected. |

| 0      | 1      | Toggle OC0A on compare match              |

| 1      | 0      | Clear OC0A on compare match               |

| 1      | 1      | Set OC0A on compare match                 |

Table 5-41. Compare Output Mode, non-PWM Mode

Table 5-42 shows the COM0A1:0 bit functionality when the WGM01:0 bits are set to fast PWM mode.

Table 5-42. Compare Output Mode, Fast PWM Mode <sup>(1)</sup>

| COM0A1 | COM0A0 | Description                                                                                      |

|--------|--------|--------------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected.                                                        |

| 0      | 1      | WGM02 = 0: Normal port operation, OC0A disconnected.<br>WGM02 = 1: Toggle OC0A on compare match. |

| 1      | 0      | Clear OC0A on compare match, set OC0A at BOTTOM, (non-inverting mode).                           |

| 1      | 1      | Set OC0A on compare match, clear OC0A at BOTTOM, (inverting mode).                               |

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the compare match is ignored, but the set or clear is done at BOTTOM. See Section 5.14.7.3 "Fast PWM Mode" on page 104 for more details.

Table 5-43 shows the COM0A1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

| COM0A1 | COM0A0 | Description                                                                                      |

|--------|--------|--------------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected.                                                        |

| 0      | 1      | WGM02 = 0: Normal port operation, OC0A disconnected.<br>WGM02 = 1: Toggle OC0A on compare match. |

| 1      | 0      | Clear OC0A on compare match when up-counting. Set OC0A on compare match when down-counting.      |

| 1      | 1      | Set OC0A on compare match when up-counting. Clear OC0A on compare match when down-counting.      |

Table 5-43.

Compare Output Mode, Phase Correct PWM Mode

(1)

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the compare match is ignored, but the set or clear is done at TOP. See Section 5.15.9.4 "Phase Correct PWM Mode" on page 126 for more details.

• Bits 5:4 - COM0B1:0: Compare Match Output B Mode

These bits control the output compare pin (OC0B) behavior. If one or both of the COM0B1:0 bits are set, the OC0B output overrides the normal port functionality of the I/O pin it is connected to. However, note that the data direction register (DDR) bit corresponding to the OC0B pin must be set in order to enable the output driver.

When OC0B is connected to the pin, the function of the COM0B1:0 bits depends on the WGM02:0 bit setting. Table 5-44 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to a normal or CTC mode (non-PWM).

| COM0B1 | COM0B0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected. |

| 0      | 1      | Toggle OC0B on compare match              |

| 1      | 0      | Clear OC0B on compare match               |

| 1      | 1      | Set OC0B on compare match                 |

Table 5-44. Compare Output Mode, non-PWM Mode

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the compare registers. If the TOP value is lower than any of the compare registers, a compare match will never occur between the TCNT1 and the OCR1x. Note that when using fixed TOP values, the unused bits are masked to zero when any of the OCR1x registers are written. As the third period shown in Figure 5-45 illustrates, changing the TOP actively while the Timer/Counter is running in the phase correct mode can result in an unsymmetrical output. The reason for this can be found in the time of update of the OCR1x register. Since the OCR1x update occurs at TOP, the PWM period starts and ends at TOP. This implies that the length of the falling slope is determined by the previous TOP value, while the length of the rising slope is determined by the new TOP value. When these two values differ the two slopes of the period will differ in length. The difference in length gives the unsymmetrical result on the output.

It is recommended to use the phase and frequency correct mode instead of the phase correct mode when changing the TOP value while the Timer/Counter is running. When using a static TOP value there are practically no differences between the two modes of operation.

In phase correct PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM1x1:0 to three (See Table on page 132). The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x register at the compare match between OCR1x and TCNT1 when the counter increments, and clearing (or setting) the OC1x register at compare match between OCR1x and TCNT1 when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation:

$$f_{OCnxPCPWM} = \frac{f_{\text{clk\_I/O}}}{2 N TOP}$$

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x register represent special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCR1x is set equal to BOTTOM the output will be continuously low and if set equal to TOP the output will be continuously high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values. If OCR1A is used to define the TOP value (WGM13:0 = 11) and COM1A1:0 = 1, the OC1A output will toggle with a 50% duty cycle.

# 5.15.9.5 Phase and Frequency Correct PWM Mode

The phase and frequency correct pulse width modulation, or phase and frequency correct PWM mode (WGM13:0 = 8 or 9) provides a high resolution phase and frequency correct PWM waveform generation option. The phase and frequency correct PWM mode is, like the phase correct PWM mode, based on a dual-slope operation. The counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOTTOM. In non-inverting compare output mode, the output compare (OC1x) is cleared on the compare match between TCNT1 and OCR1x while upcounting, and set on the compare match while downcounting. In inverting compare output mode, the operation is inverted. The dual-slope operation gives a lower maximum operation frequency compared to the single-slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The main difference between the phase correct, and the phase and frequency correct PWM mode is the time the OCR1x register is updated by the OCR1x buffer register, (see Figure 5-45 and Figure 5-46).

The PWM resolution for the phase and frequency correct PWM mode can be defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM resolution in bits can be calculated using the following equation:

$$R_{PFCPWM} = \frac{\log TOP + 1}{\log 2}$$

In phase and frequency correct PWM mode the counter is incremented until the counter value matches either the value in ICR1 (WGM13:0 = 8), or the value in OCR1A (WGM13:0 = 9). The counter has then reached the TOP and changes the count direction. The TCNT1 value will be equal to TOP for one timer clock cycle. The timing diagram for the phase correct and frequency correct PWM mode is shown on Figure 5-46. The figure shows phase and frequency correct PWM mode when OCR1A or ICR1 is used to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a compare match occurs.

# Atmel

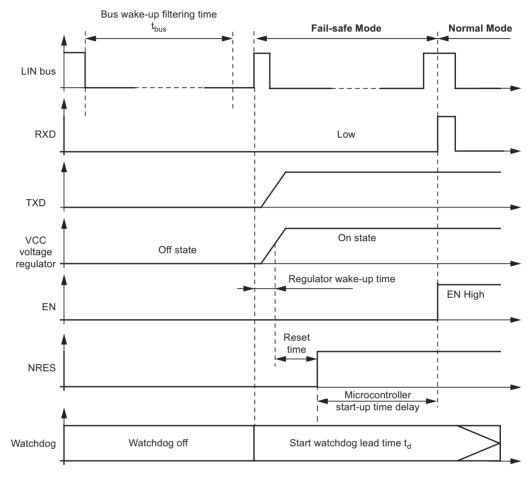

# 5.17.11.3 TCNT2 - Timer/Counter Register

The Timer/Counter register gives direct access, both for read and write operations, to the Timer/Counter unit 8-bit counter. Writing to the TCNT2 register blocks (removes) the compare match on the following timer clock. Modifying the counter (TCNT2) while the counter is running, introduces a risk of missing a compare match between TCNT2 and the OCR2x registers.

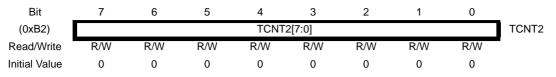

## 5.17.11.4 OCR2A - Output Compare Register A

The output compare register A contains an 8-bit value that is continuously compared with the counter value (TCNT2). A match can be used to generate an output compare interrupt, or to generate a waveform output on the OC2A pin.

#### 5.17.11.5 OCR2B – Output Compare Register B

| Bit           | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------------|-----|------------|-----|-----|-----|-----|-----|-----|--|

| (0xB4)        |     | OCR2B[7:0] |     |     |     |     |     |     |  |

| Read/Write    | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Initial Value | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |

The output compare register B contains an 8-bit value that is continuously compared with the counter value (TCNT2). A match can be used to generate an output compare interrupt, or to generate a waveform output on the OC2B pin.

## 5.17.11.6 TIMSK2 – Timer/Counter2 Interrupt Mask Register

| Bit           | 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0     | _      |

|---------------|---|---|---|---|---|--------|--------|-------|--------|

| (0x70)        | - | - | - | - | - | OCIE2B | OCIE2A | TOIE2 | TIMSK2 |

| Read/Write    | R | R | R | R | R | R/W    | R/W    | R/W   | -      |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0      | 0      | 0     |        |

#### • Bit 2 – OCIE2B: Timer/Counter2 Outp ut Compare Match B Interrupt Enable

When the OCIE2B bit is written to one and the I-bit in the status register is set (one), the Timer/Counter2 compare match B interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, i.e., when the OCF2B bit is set in the Timer/Counter 2 interrupt flag register – TIFR2.

• Bit 1 – OCIE2A: Timer/Counter2 Outp ut Compare Match A Interrupt Enable

When the OCIE2A bit is written to one and the I-bit in the status register is set (one), the Timer/Counter2 compare match A interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, i.e., when the OCF2A bit is set in the Timer/Counter 2 interrupt flag register – TIFR2.

• Bit 0 - TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is written to one and the I-bit in the status register is set (one), the Timer/Counter2 overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs, i.e., when the TOV2 bit is set in the Timer/Counter2 interrupt flag register – TIFR2.

• Bit 2 – OCR2BUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2B is written, this bit becomes set. When OCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2B is ready to be updated with a new value.

• Bit 1 – TCR2AUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2A is written, this bit becomes set. When TCCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2A is ready to be updated with a new value.

• Bit 0 - TCR2BUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2B is written, this bit becomes set. When TCCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2B is ready to be updated with a new value.

If a write is performed to any of the five Timer/Counter2 registers while its update busy flag is set, the updated value might get corrupted and cause an unintentional interrupt to occur.

The mechanisms for reading TCNT2, OCR2A, OCR2B, TCCR2A and TCCR2B are different. When reading TCNT2, the actual timer value is read. When reading OCR2A, OCR2B, TCCR2A and TCCR2B the value in the temporary storage register is read.

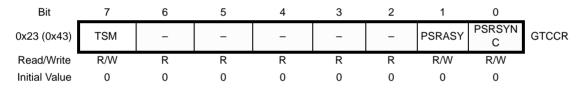

# 5.17.11.9 GTCCR – General Timer/Counter Control Register

• Bit 1 – PSRASY: Prescaler Reset Timer/Counter2

When this bit is one, the Timer/Counter2 prescaler will be reset. This bit is normally cleared immediately by hardware. If the bit is written when Timer/Counter2 is operating in asynchronous mode, the bit will remain one until the prescaler has been reset. The bit will not be cleared by hardware if the TSM bit is set. Refer to the description of the Section • "Bit 7 – TSM: Timer/Counter Synchronization Mode" on page 138 for a description of the Timer/Counter synchronization mode.

# 5.18.5 Register Description

## 5.18.5.1 SPCR - SPI Control Register

| Bit           | 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|-----|------|------|------|------|------|------|------|

| 0x2C (0x4C)   | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | SPCR |

| Read/Write    | R/W  | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | •    |

| Initial Value | 0    | 0   | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### • Bit 7 – SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR register is set and the if the global interrupt enable bit in SREG is set.

#### • Bit 6 – SPE: SPI Enable

When the SPE bit is written to one, the SPI is enabled. This bit must be set to enable any SPI operations.

#### • Bit 5 – DORD: Data Order

When the DORD bit is written to one, the LSB of the data word is transmitted first.

When the DORD bit is written to zero, the MSB of the data word is transmitted first.

## • Bit 4 - MSTR: Master/Slave Select

This bit selects master SPI mode when written to one, and Slave SPI mode when written logic zero. If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI Master mode.

#### • Bit 3 - CPOL: Clock Polarity

When this bit is written to one, SCK is high when idle. When CPOL is written to zero, SCK is low when idle. Refer to Figure 5-67 and Figure 5-68 for an example. The CPOL functionality is summarized below:

#### Table 5-66. CPOL Functionality

| CPOL | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Rising       | Falling       |

| 1    | Falling      | Rising        |

#### • Bit 2 - CPHA: Clock Phase

The settings of the clock phase bit (CPHA) determine if data is sampled on the leading (first) or trailing (last) edge of SCK. Refer to Figure 5-67 and Figure 5-68 for an example. The CPOL functionality is summarized below:

#### Table 5-67. CPHA Functionality

| СРНА | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Sample       | Setup         |

| 1    | Setup        | Sample        |

• Bits 1, 0 - SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a master. SPR1 and SPR0 have no effect on the slave.

# 5.21.2.1 TWI Terminology

The following definitions are frequently encountered in this section.

| Term        | Description                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------|

| Master      | The device that initiates and terminates a transmission. The master also generates the SCL clock. |

| Slave       | The device addressed by a master.                                                                 |

| Transmitter | The device placing data on the bus.                                                               |

| Receiver    | The device reading data from the bus.                                                             |

Table 5-85. TWI Terminology

The PRTWI bit in Section 5.9.10 "Minimizing Power Consumption" on page 60 must be written to zero to enable the 2-wire serial interface.

#### 5.21.2.2 Electrical Interconnection

As depicted in Figure 5-77, both bus lines are connected to the positive supply voltage through pull-up resistors. The bus drivers of all TWI-compliant devices are open-drain or open-collector. This implements a wired-AND function which is essential to the operation of the interface. A low level on a TWI bus line is generated when one or more TWI devices output a zero. A high level is output when all TWI devices tri-state their outputs, allowing the pull-up resistors to pull the line high. Note that all AVR<sup>®</sup> devices connected to the TWI bus must be powered in order to allow any bus operation.

The number of devices that can be connected to the bus is only limited by the bus capacitance limit of 400pF and the 7-bit slave address space. A detailed specification of the electrical characteristics of the TWI is given in Section 5.28.7 "2-wire Serial Interface Characteristics" on page 283. Two different sets of specifications are presented there, one relevant for bus speeds below 100 kHz, and one valid for bus speeds up to 400kHz.

# 5.21.3 Data Transfer and Frame Format

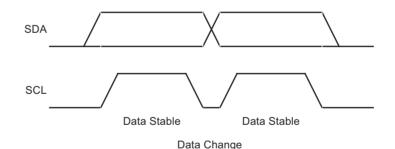

#### 5.21.3.1 Transferring Bits

Each data bit transferred on the TWI bus is accompanied by a pulse on the clock line. The level of the data line must be stable when the clock line is high. The only exception to this rule is for generating start and stop conditions.

Figure 5-78. Data Validity

Atmel

Table 5-88. Status codes for Master Receiver Mode

| Status Code                |                                                                            | Application Software Response |     |      |       |      |                                                                                                  |

|----------------------------|----------------------------------------------------------------------------|-------------------------------|-----|------|-------|------|--------------------------------------------------------------------------------------------------|

| (TWSR)                     | Otative of the O wine O wind                                               |                               |     | To T | WCR   |      |                                                                                                  |

| Prescaler<br>Bits<br>are 0 | Status of the 2-wire Serial<br>Bus and 2-wire Serial<br>Interface Hardware | To/from TWDR                  | STA | STO  | TWINT | TWEA | Next Action Taken by TWI Hardware                                                                |

| 0x08                       | A START condition has<br>been transmitted                                  | Load SLA+R                    | 0   | 0    | 1     | Х    | SLA+R will be transmitted<br>ACK or NOT ACK will be received                                     |

|                            | A repeated START condition                                                 | Load SLA+R or                 | 0   | 0    | 1     | Х    | SLA+R will be transmitted<br>ACK or NOT ACK will be received                                     |

| 0x10                       | has been transmitted                                                       | Load SLA+W                    | 0   | 0    | 1     | Х    | SLA+W will be transmitted<br>Logic will switch to master transmitter mode                        |

|                            | Arbitration lost in SLA+R or                                               | No TWDR action<br>or          | 0   | 0    | 1     | Х    | 2-wire serial bus will be released and not<br>addressed slave mode will be entered               |

| 0x38                       | NOT ACK bit                                                                | No TWDR action                | 1   | 0    | 1     | Х    | A START condition will be transmitted when the bus becomes free                                  |

| 0x40                       | SLA+R has been<br>transmitted:                                             | No TWDR action<br>or          | 0   | 0    | 1     | 0    | Data byte will be received and NOT ACK will be returned                                          |

| 0,40                       | ACK has been received                                                      | No TWDR action                | 0   | 0    | 1     | 1    | Data byte will be received and ACK will be returned                                              |

|                            |                                                                            | No TWDR action                |     |      |       |      |                                                                                                  |

|                            | SLA+R has been                                                             | or                            | 1   | 0    | 1     | X    | Repeated START will be transmitted                                                               |

| 0x48                       | transmitted;<br>NOT ACK has been                                           | No TWDR action<br>or          | 0   | 1    | 1     | Х    | STOP condition will be transmitted and TWSTO<br>Flag will be reset                               |

|                            | received                                                                   | No TWDR action                | 1   | 1    | 1     | Х    | STOP condition followed by a START condition<br>will be transmitted and TWSTO Flag will be reset |

| 0.50                       | Data byte has been received:                                               | Read data byte or             | 0   | 0    | 1     | 0    | Data byte will be received and NOT ACK will be returned                                          |

| 0x50                       | 0x50 received;<br>ACK has been returned                                    | Read data byte                | 0   | 0    | 1     | 1    | Data byte will be received and ACK will be returned                                              |

|                            | Data buta baa baan                                                         | Read data byte or             | 1   | 0    | 1     | Х    | Repeated START will be transmitted                                                               |

| 0x58                       | Data byte has been<br>received;                                            | Read data byte or             | 0   | 1    | 1     | Х    | STOP condition will be transmitted and TWSTO<br>Flag will be reset                               |

|                            | NOT ACK has been<br>returned                                               | Read data byte                | 1   | 1    | 1     | Х    | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset    |

# 5.21.9.3 TWSR - TWI Status Register

| Bit           | 7    | 6    | 5    | 4    | 3    | 2 | 1     | 0     | _    |

|---------------|------|------|------|------|------|---|-------|-------|------|

| (0xB9)        | TWS7 | TWS6 | TWS5 | TWS4 | TWS3 | - | TWPS1 | TWPS0 | TWSR |

| Read/Write    | R    | R    | R    | R    | R    | R | R/W   | R/W   |      |

| Initial Value | 1    | 1    | 1    | 1    | 1    | 0 | 0     | 0     |      |

## • Bits 7..3 – TWS: TWI Status

These 5 bits reflect the status of the TWI logic and the 2-wire serial bus. The different status codes are described later in this section. Note that the value read from TWSR contains both the 5-bit status value and the 2-bit prescaler value. The application designer should mask the prescaler bits to zero when checking the status bits. This makes status checking independent of prescaler setting. This approach is used in this datasheet, unless otherwise noted.

## • Bit 2 - Res: Reserved Bit

This bit is reserved and will always read as zero.

• Bits 1..0 - TWPS: TWI Prescaler Bits

These bits can be read and written, and control the bit rate prescaler.

| Table 5-92. | TWI Bit Rate Prescaler |

|-------------|------------------------|

|-------------|------------------------|

| TWPS1 | TWPS0 | Prescaler Value |

|-------|-------|-----------------|

| 0     | 0     | 1               |

| 0     | 1     | 4               |

| 1     | 0     | 16              |

| 1     | 1     | 64              |

To calculate bit rates, see Section 5.21.5.2 "Bit Rate Generator Unit" on page 200. The value of TWPS1..0 is used in the equation.

# 5.21.9.4 TWDR – TWI Data Register

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| (0xBB)        | TWD7 | TWD6 | TWD5 | TWD4 | TWD3 | TWD2 | TWD1 | TWD0 | TWDR |

| Read/Write    | R/W  |      |

| Initial Value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |      |

In transmit mode, TWDR contains the next byte to be transmitted. In receive mode, the TWDR contains the last byte received. It is writable while the TWI is not in the process of shifting a byte. This occurs when the TWI interrupt flag (TWINT) is set by hardware. Note that the data register cannot be initialized by the user before the first interrupt occurs. The data in TWDR remains stable as long as TWINT is set. While data is shifted out, data on the bus is simultaneously shifted in. TWDR always contains the last byte present on the bus, except after a wake up from a sleep mode by the TWI interrupt. In this case, the contents of TWDR is undefined.

In the case of a lost bus arbitration, no data is lost in the transition from master to slave. Handling of the ACK bit is controlled automatically by the TWI logic, the CPU cannot access the ACK bit directly.

# • Bits 7..0 - TWD: TWI Data Register

These eight bits constitute the next data byte to be transmitted, or the latest data byte received on the 2-wire serial bus.

This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the data registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

## 5.23.3 Starting a Conversion

A single conversion is started by disabling the power reduction ADC bit, PRADC, in Section 5.9.10 "Minimizing Power Consumption" on page 60 by writing a logical zero to it and writing a logical one to the ADC start conversion bit, ADSC. This bit stays high as long as the conversion is in progress and will be cleared by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

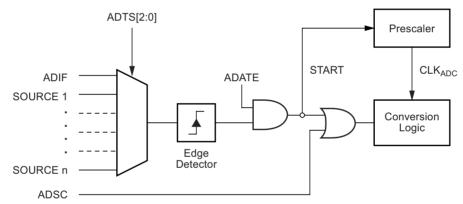

Alternatively, a conversion can be triggered automatically by various sources. Auto triggering is enabled by setting the ADC auto trigger enable bit, ADATE in ADCSRA. The trigger source is selected by setting the ADC trigger select bits, ADTS in ADCSRB (See description of the ADTS bits for a list of the trigger sources). When a positive edge occurs on the selected trigger signal, the ADC prescaler is reset and a conversion is started. This provides a method of starting conversions at fixed intervals. If the trigger signal still is set when the conversion completes, a new conversion will not be started. If another positive edge occurs on the trigger signal during conversion, the edge will be ignored. Note that an Interrupt flag will be set even if the specific interrupt is disabled or the global interrupt enable bit in SREG is cleared. A conversion can thus be triggered without causing an interrupt. However, the interrupt flag must be cleared in order to trigger a new conversion at the next interrupt event.

Using the ADC interrupt flag as a trigger source makes the ADC start a new conversion as soon as the ongoing conversion has finished. The ADC then operates in free running mode, constantly sampling and updating the ADC data register. The first conversion must be started by writing a logical one to the ADSC bit in ADCSRA. In this mode the ADC will perform successive conversions independently of whether the ADC Interrupt Flag, ADIF is cleared or not.

If auto triggering is enabled, single conversions can be started by writing ADSC in ADCSRA to one. ADSC can also be used to determine if a conversion is in progress. The ADSC bit will be read as one during a conversion, independently of how the conversion was started.

Atmel

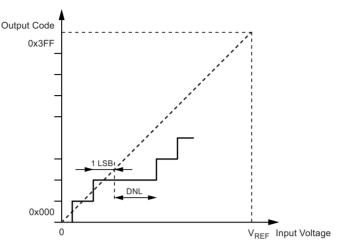

Differential non-linearity (DNL): The maximum deviation of the actual code width (the interval between two adjacent transitions) from the ideal code width (1 LSB). Ideal value: 0 LSB.

Figure 5-112. Differential Non-linearity (DNL)

Quantization error: Due to the quantization of the input voltage into a finite number of codes, a range of input voltages (1 LSB wide) will code to the same value. Always  $\pm 0.5$  LSB.

Absolute accuracy: The maximum deviation of an actual (unadjusted) transition compared to an ideal transition for any code. This is the compound effect of offset, gain error, differential error, non-linearity, and quantization error. Ideal value:  $\pm 0.5$  LSB.

# 5.23.7 ADC Conversion Result

After the conversion is complete (ADIF is high), the conversion result can be found in the ADC result registers (ADCL, ADCH).

For single ended conversion, the result is

$$ADC = \frac{V_{IN} \quad 1024}{V_{REF}}$$

where  $V_{IN}$  is the voltage on the selected input pin and  $V_{REF}$  the selected voltage reference (see Table 5-97 on page 238 and Table 5-98 on page 238). 0x000 represents analog ground, and 0x3FF represents the selected reference voltage minus one LSB.

#### 5.23.8 Temperature Measurement

The temperature measurement is based on an on-chip temperature sensor that is coupled to a single ended ADC input. MUX[4..0] bits in ADMUX register enables the temperature sensor. The internal 1.1V voltage reference must also be selected for the ADC voltage reference source in the temperature sensor measurement. When the temperature sensor is enabled, the ADC converter can be used in single conversion mode to measure the voltage over the temperature sensor.

The measured voltage has a linear relationship to the temperature as described in Table 5-96 on page 236.

The voltage sensitivity is approximately 1LSB/°C and the accuracy of the temperature measurement is ±10°C using manufacturing calibration values (TS\_GAIN, TS\_OFFSET).

The values described in Table 5-96 on page 236 are typical values. However, due to the process variation the temperature sensor output varies from one chip to another.

Table 5-96. Sensor output code vs Temperature (typical values)

| Temperature / °C | -40°C  | +25 °C | +125 °C |

|------------------|--------|--------|---------|

|                  | 0x010D | 0x0160 | 0x01E0  |

## Table 5-117. Fuse Low Byte

| Low Fuse Byte         | Bit No | Description          | Default Value                   |

|-----------------------|--------|----------------------|---------------------------------|

| CKDIV8 <sup>(4)</sup> | 7      | Divide clock by 8    | 0 (programmed)                  |

| CKOUT <sup>(3)</sup>  | 6      | Clock output         | 1 (unprogrammed)                |

| SUT1                  | 5      | Select start-up time | 1 (unprogrammed) <sup>(1)</sup> |

| SUT0                  | 4      | Select start-up time | 0 (programmed) <sup>(1)</sup>   |

| CKSEL3                | 3      | Select clock source  | 0 (programmed) <sup>(2)</sup>   |

| CKSEL2                | 2      | Select clock source  | 0 (programmed) <sup>(2)</sup>   |

| CKSEL1                | 1      | Select clock source  | 1 (unprogrammed) <sup>(2)</sup> |

| CKSEL0                | 0      | Select clock source  | 0 (programmed) <sup>(2)</sup>   |

Note: 1. The default value of SUT1..0 results in maximum start-up time for the default clock source. See Table 5-14 on page 54 for details.

- 2. The default setting of CKSEL3..0 results in internal RC oscillator at 8MHz. See Table 5-13 on page 54 for details.

- 3. The CKOUT fuse allows the system clock to be output on PORTB0. See Section 5.8.9 "Clock Output Buffer" on page 56 for details.

- 4. See Section 5.8.11 "System Clock Prescaler" on page 56 for details.

The status of the fuse bits is not affected by chip erase. Note that the fuse bits are locked if Lock bit1 (LB1) is programmed. Program the fuse bits before programming the lock bits.

## 5.27.2.1 Latching of Fuses

The fuse values are latched when the device enters programming mode and changes of the fuse values will have no effect until the part leaves programming mode. This does not apply to the EESAVE Fuse which will take effect once it is programmed. The fuses are also latched on power-up in normal mode.

## 5.27.3 Signature Bytes

All Atmel<sup>®</sup> microcontrollers have a three-byte signature code which identifies the device. This code can be read in both serial and parallel mode, also when the device is locked. The three bytes reside in a separate address space. For the ATmega328P the signature bytes are given in Table 5-118.

#### Table 5-118. Device ID

|            | Signature Bytes Address |       |       |  |  |  |

|------------|-------------------------|-------|-------|--|--|--|

| Part       | 0x000                   | 0x001 | 0x002 |  |  |  |

| ATmega328P | 0x1E                    | 0x95  | 0x0F  |  |  |  |

#### 5.27.4 Calibration Byte

The ATmega328P has a byte calibration value for the Internal RC oscillator. This byte resides in the high byte of address 0x000 in the signature address space. During reset, this byte is automatically written into the OSCCAL register to ensure correct frequency of the calibrated RC oscillator.

# 5.27.5 Page Size

Table 5-119. No. of Words in a Page and No. of Pages in the Flash

| Device     | Flash Size               | Page Size | PCWORD  | No. of Pages | PCPAGE   | PCMSB |

|------------|--------------------------|-----------|---------|--------------|----------|-------|

| ATmega328P | 16K words<br>(32K bytes) | 64 words  | PC[5:0] | 256          | PC[13:6] | 13    |

Table 5-120. No. of Words in a Page and No . of Pages in the EEPROM

| Device     | EEPROM Size | Page Size | PCWORD   | No. of Pages | PCPAGE   | EEAMSB |

|------------|-------------|-----------|----------|--------------|----------|--------|

| ATmega328P | 1K bytes    | 4 bytes   | EEA[1:0] | 256          | EEA[9:2] | 9      |

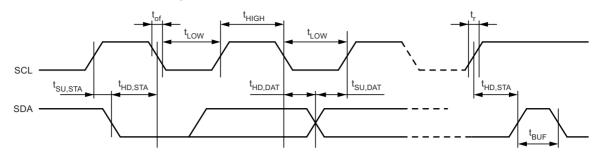

Figure 5-131. 2-wire Serial Bus Timing

# 5.28.8 ADC Characteristics

# Table 5-135. ADC Characteristics

| Parameter                  | Condition                                         | Symbol           | Min            | Тур | Max                  | Unit |

|----------------------------|---------------------------------------------------|------------------|----------------|-----|----------------------|------|

| Resolution                 | –40°C +125°C / 2.70 - 5.50V<br>ADC clock = 200kHz |                  |                | 10  |                      | bits |

| Absolute accuracy          | $V_{CC} = 4.0V, V_{Ref} = 4.0V$                   | TUE              |                | 2.2 | 3.5                  | LSB  |

| Integral non linearity     | $V_{CC} = 4.0V, V_{Ref} = 4.0V$                   | INL              |                | 0.6 | 1.5                  | LSB  |

| Differential non linearity | $V_{CC} = 4.0V, V_{Ref} = 4.0V$                   | DNL              |                | 0.3 | 0.7                  | LSB  |

| Gain error                 | $V_{CC} = 4.0V, V_{Ref} = 4.0V$                   |                  | -3.5           |     | 3.5                  | LSB  |

| Offset error               | $V_{CC} = 4.0V, V_{Ref} = 4.0V$                   |                  | -3.5           |     | 3.5                  | LSB  |

| Clock frequency            |                                                   |                  | 50             |     | 200                  | kHz  |

| Analog supply voltage      |                                                   | $AV_{CC}$        | $V_{CC} - 0.3$ |     | V <sub>CC</sub> +0.3 | V    |

| Reference voltage          |                                                   | V <sub>Ref</sub> | 1.0            |     | AV <sub>CC</sub>     | V    |

| Input voltage              |                                                   | V <sub>in</sub>  | GND            |     | V <sub>Ref</sub>     | V    |

| Internal voltage reference | $V_{CC} = 5v$                                     | V <sub>int</sub> | 1.0            | 1.1 | 1.2                  | V    |

| Reference input resistance |                                                   | R <sub>ref</sub> | 22.4           | 32  | 41.6                 | k    |

| Analog input resistance    |                                                   | $R_{ain}$        |                | 100 |                      | М    |

# 5.30 Register Summary (Continued)

| (0x8F) |          |         | Bit 6                      | Bit 5       | Bit 4            | Bit 3          | Bit 2         | Bit 1   | Bit 0   | Page |

|--------|----------|---------|----------------------------|-------------|------------------|----------------|---------------|---------|---------|------|

|        | Reserved | -       | -                          | -           | -                | -              | -             | -       | -       |      |

| (0x8E) | Reserved | -       | -                          | -           | -                | -              | -             | -       | -       |      |

| (0x8D) | Reserved | -       | -                          | -           | -                | -              | -             | -       | -       |      |

| (0x8C) | Reserved | -       | -                          | -           | -                | -              | -             | -       | -       |      |

| (0x8B) | OCR1BH   |         |                            | Timer/Count | er1 - Output c   | ompare regis   | ter B high by | rte     |         | 134  |

| (0x8A) | OCR1BL   |         |                            | Timer/Count | ter1 - Output c  | ompare regis   | ster B low by | te      |         | 134  |

| (0x89) | OCR1AH   |         |                            | Timer/Count | er1 - Output c   | ompare regis   | ter A high by | rte     |         | 134  |

| (0x88) | OCR1AL   |         |                            | Timer/Count | ter1 - Output c  | ompare regis   | ster A low by | te      |         | 134  |

| (0x87) | ICR1H    |         |                            | Timer/Cou   | unter1 - Input o | capture regis  | ter high byte |         |         | 135  |

| (0x86) | ICR1L    |         |                            | Timer/Co    | unter1 - Input   | capture regis  | ter low byte  |         |         | 135  |

| (0x85) | TCNT1H   |         |                            | Timer/C     | Counter1 - Cou   | Inter register | high byte     |         |         | 134  |

| (0x84) | TCNT1L   |         |                            | Timer/0     | Counter1 - Co    | unter register | r low byte    |         |         | 134  |

| (0x83) | Reserved | -       | -                          | -           | -                | -              | -             | -       | -       |      |

| (0x82) | TCCR1C   | FOC1A   | FOC1B                      | _           | -                | -              | -             | _       | -       | 134  |

| (0x81) | TCCR1B   | ICNC1   | ICES1                      | _           | WGM13            | WGM12          | CS12          | CS11    | CS10    | 133  |

| (0x80) | TCCR1A   | COM1A1  | COM1A0                     | COM1B1      | COM1B0           | -              | -             | WGM11   | WGM10   | 131  |

| (0x7F) | DIDR1    | _       | _                          | _           | -                | _              | _             | AIN1D   | AIN0D   | 225  |

| (0x7E) | DIDR0    | _       | _                          | ADC5D       | ADC4D            | ADC3D          | ADC2D         | ADC1D   | ADC0D   | 241  |

| (0x7D) | Reserved | _       | _                          | -           | -                | -              | -             | -       | -       |      |

| (0x7C) | ADMUX    | REFS1   | REFS0                      | ADLAR       | _                | MUX3           | MUX2          | MUX1    | MUX0    | 237  |

| (0x7B) | ADCSRB   | -       | ACME                       | _           | _                | _              | ADTS2         | ADTS1   | ADTS0   | 241  |

| (0x7A) | ADCSRA   | ADEN    | ADSC                       | ADATE       | ADIF             | ADIE           | ADPS2         | ADPS1   | ADPS0   | 239  |

| (0x79) | ADCH     |         |                            |             | ADC data reg     | lister high by | te            |         | L       | 240  |

| (0x78) | ADCL     |         | ADC data register low byte |             |                  |                | 240           |         |         |      |

| (0x77) | Reserved | _       | _                          | -           | -                | -              | -             | -       | -       |      |

| (0x76) | Reserved | _       | _                          | _           | -                | _              | _             | _       | _       |      |

| (0x75) | Reserved | _       | _                          | _           | _                | _              | _             | _       | _       |      |

| (0x74) | Reserved | _       | _                          | _           | _                | _              | _             | _       | _       |      |

| (0x73) | Reserved | _       | _                          | _           | _                | _              | _             | _       | _       |      |

| (0x72) | Reserved | _       | _                          | _           | _                | _              | _             | _       | _       |      |

| (0x71) | Reserved | _       | _                          | _           | _                | _              | _             | _       | _       |      |

| (0x70) | TIMSK2   | _       | _                          | _           | _                | _              | OCIE2B        | OCIE2A  | TOIE2   | 154  |

| (0x6F) | TIMSK1   | -       | _                          | ICIE1       | _                | -              | OCIE1B        | OCIE1A  | TOIE1   | 135  |

| (0x6E) | TIMSK0   | -       | -                          | -           | -                | -              | OCIE0B        | OCIE0A  | TOIE0   | 111  |

| (0x6D) | PCMSK2   | PCINT23 | PCINT22                    | PCINT21     | PCINT20          | PCINT19        | PCINT18       | PCINT17 | PCINT16 | 81   |

| (0x6C) | PCMSK1   | _       | PCINT14                    | PCINT13     | PCINT12          | PCINT11        | PCINT10       | PCINT9  | PCINT8  | 81   |

| (0x6B) | PCMSK0   | PCINT7  | PCINT6                     | PCINT5      | PCINT4           | PCINT3         | PCINT2        | PCINT1  | PCINT0  | 81   |

| (0x6A) | Reserved | -       | -                          | -           | -                | -              | -             | -       | _       |      |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

2. I/O registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVR<sup>®</sup>s, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega328P is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

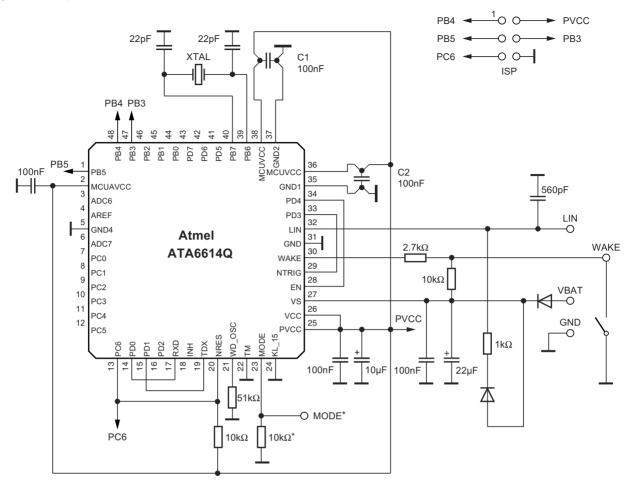

Figure 6-2. Typical LIN Master Application

\* The MODE pin can be connected directly to GND, if it is not needed to disable the Watchdog

Note:

All open pins of the SiP can be used for application-specific purposes.

AVR®: TXD, RXD, NRES and EN connected for LIN master. The connection between the LIN-SBC and the AVR requires the software being programmed correspondingly. Analog digital converter not active; system clock from external crystal.

LIN-SBC: Master application with 5V regulator and watchdog, 1k Master resistance connected via diode to VBAT, local wake up via pin WAKE.

RF emissions: Best results for RF emissions will be achieved by connecting the blocking capacitors of the microcontroller supply (C1 and C2) between the microcontroller pins and the GND/PVCC line. See also Figure 6-2.

| Ge | eneral F                 | eatures1                                                 |  |  |  |  |  |  |  |

|----|--------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|

| 1. | Description              |                                                          |  |  |  |  |  |  |  |

| 2. | Pin Configuration        |                                                          |  |  |  |  |  |  |  |

| 3. | Absolute Maximum Ratings |                                                          |  |  |  |  |  |  |  |

| 4. |                          | LIN System-basis-chip Block                              |  |  |  |  |  |  |  |

|    | 4.1                      | Features                                                 |  |  |  |  |  |  |  |

|    | 4.2                      | Description                                              |  |  |  |  |  |  |  |

|    | 4.3                      | Functional Description                                   |  |  |  |  |  |  |  |

|    | 4.4                      | Modes of Operation                                       |  |  |  |  |  |  |  |

|    | 4.5                      | Wake-up Scenarios from Silent or Sleep Mode              |  |  |  |  |  |  |  |

|    | 4.6                      | Voltage Regulator                                        |  |  |  |  |  |  |  |

|    | 4.7                      | Watchdog                                                 |  |  |  |  |  |  |  |

|    | 4.8                      | Electrical Characteristics                               |  |  |  |  |  |  |  |

| 5. | Mic                      | crocontroller Block                                      |  |  |  |  |  |  |  |

| 0. | 5.1                      | Features                                                 |  |  |  |  |  |  |  |

|    | 5.2                      | Overview                                                 |  |  |  |  |  |  |  |

|    | 5.3                      | Resources                                                |  |  |  |  |  |  |  |

|    | 5.4                      | Data Retention                                           |  |  |  |  |  |  |  |

|    | 5.5                      | About Code Examples                                      |  |  |  |  |  |  |  |

|    | 5.6                      | AVR CPU Core                                             |  |  |  |  |  |  |  |

|    | 5.7                      | AVR Memories                                             |  |  |  |  |  |  |  |

|    | 5.8                      | System Clock and Clock Options                           |  |  |  |  |  |  |  |

|    | 5.9                      | Power Management and Sleep Modes                         |  |  |  |  |  |  |  |

|    | 5.10                     | System Control and Reset                                 |  |  |  |  |  |  |  |

|    | 5.11                     | Interrupts                                               |  |  |  |  |  |  |  |

|    | 5.12                     | External Interrupts                                      |  |  |  |  |  |  |  |

|    | 5.13                     | I/O-Ports                                                |  |  |  |  |  |  |  |

|    | 5.14                     | 8-bit Timer/Counter0 with PWM                            |  |  |  |  |  |  |  |

|    | 5.15                     | 16-bit Timer/Counter1 with PWM                           |  |  |  |  |  |  |  |

|    | 5.16                     | Timer/Counter0 and Timer/Counter1 Prescalers             |  |  |  |  |  |  |  |

|    | 5.17                     | 8-bit Timer/Counter2 with PWM and Asynchronous Operation |  |  |  |  |  |  |  |

|    | 5.18                     | SPI – Serial Peripheral Interface                        |  |  |  |  |  |  |  |

|    | 5.19                     | USART0                                                   |  |  |  |  |  |  |  |

|    | 5.20                     | USART in SPI Mode                                        |  |  |  |  |  |  |  |

|    | 5.21                     | 2-wire Serial Interface                                  |  |  |  |  |  |  |  |

|    | 5.22                     | Analog Comparator                                        |  |  |  |  |  |  |  |

|    | 5.23                     | Analog-to-Digital Converter                              |  |  |  |  |  |  |  |

|    | 5.24                     | debugWIRE On-chip Debug System                           |  |  |  |  |  |  |  |

|    | 5.25                     | Self-programming the Flash, ATmega328P 243               |  |  |  |  |  |  |  |

|    | 5.26                     | Boot Loader Support – Read-while-write Self-programming  |  |  |  |  |  |  |  |

|    | 5.27                     | Memory Programming                                       |  |  |  |  |  |  |  |

|    | 5.28                     | Electrical Characteristics                               |  |  |  |  |  |  |  |

|    | 5.29                     | Typical Characteristics                                  |  |  |  |  |  |  |  |

|    | 5.30                     | Register Summary                                         |  |  |  |  |  |  |  |

|    | 5.31                     | Instruction Set Summary                                  |  |  |  |  |  |  |  |

| 6. | An                       | -<br>plication                                           |  |  |  |  |  |  |  |

| 7. |                          | dering Information                                       |  |  |  |  |  |  |  |

| 1. |                          | Jenny Information                                        |  |  |  |  |  |  |  |

Atmel