Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | 56800                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 60MHz                                                                  |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 11                                                                     |

| Program Memory Size        | 16KB (8K x 16)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 16                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                              |

| Data Converters            | A/D 8x12b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56f801fa60e |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Part 1 Overview

## 1.1 56F801 Features

### 1.1.1 Digital Signal Processing Core

- Efficient 16-bit 56800 family controller engine with dual Harvard architecture

- As many as 40 Million Instructions Per Second (MIPS) at 80MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Two 36-bit accumulators including extension bits

- 16-bit bidirectional barrel shifter

- Parallel instruction set with unique processor addressing modes

- Hardware DO and REP loops

- Three internal address buses and one external address bus

- Four internal data buses and one external data bus

- Instruction set supports both DSP and controller functions

- Controller style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/OnCE debug programming interface

### 1.1.2 Memory

- Harvard architecture permits as many as three simultaneous accesses to Program and Data memory

- On-chip memory including a low-cost, high-volume Flash solution

- 8K × 16 bit words of Program Flash

- 1K × 16-bit words of Program RAM

- 2K  $\times$  16-bit words of Data Flash

- $1K \times 16$ -bit words of Data RAM

- 2K × 16-bit words of Boot Flash

- Programmable Boot Flash supports customized boot code and field upgrades of stored code through a variety of interfaces (JTAG, SPI)

## 1.1.3 Peripheral Circuits for 56F801

- Pulse Width Modulator (PWM) with six PWM outputs, two Fault inputs, fault-tolerant design with deadtime insertion; supports both center- and edge-aligned modes

- Two 12-bit, Analog-to-Digital Converters (ADCs), which support two simultaneous conversions with two 4-multiplexed inputs; ADC and PWM modules can be synchronized

- General Purpose Quad Timer: Timer D with three pins (or three additional GPIO lines)

- Serial Communication Interface (SCI) with two pins (or two additional GPIO lines)

- Serial Peripheral Interface (SPI) with configurable four-pin port (or four additional GPIO lines)

A key application-specific feature of the 56F801 is the inclusion of a Pulse Width Modulator (PWM) module. This modules incorporates six complementary, individually programmable PWM signal outputs to enhance motor control functionality. Complementary operation permits programmable dead-time insertion, and separate top and bottom output polarity control. The up-counter value is programmable to support a continuously variable PWM frequency. Both edge- and center-aligned synchronous pulse width control (0% to 100% modulation) are supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors), both BDC and BLDC (Brush and Brushless DC motors), SRM and VRM (Switched and Variable Reluctance Motors), and stepper motors. The PWMs incorporate fault protection and cycle-by-cycle current limiting with sufficient output drive capability to directly drive standard opto-isolators. A "smoke-inhibit", write-once protection feature for key parameters is also included. The PWM is double-buffered and includes interrupt control to permit integral reload rates to be programmable from 1 to 16. The PWM modules provide a reference output to synchronize the Analog-to-Digital Converters.

The 56F801 incorporates an 8 input, 12-bit Analog-to-Digital Converter (ADC). A full set of standard programmable peripherals is provided that include a Serial Communications Interface (SCI), a Serial Peripheral Interface (SPI), and two Quad Timers. Any of these interfaces can be used as General-Purpose Input/Outputs (GPIO) if that function is not required. An on-chip relaxation oscillator provides flexibility in the choice of either on-chip or externally supplied frequency reference for chip timing operations. Application code is used to select which source is to be used.

## **1.3 State of the Art Development Environment**

- Processor Expert<sup>TM</sup> (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use component-based software application creation with an expert knowledge system.

- The Code Warrior Integrated Development Environment is a sophisticated tool for code navigation, compiling, and debugging. A complete set of evaluation modules (EVMs) and development system cards will support concurrent engineering. Together, PE, Code Warrior and EVMs create a complete, scalable tools solution for easy, fast, and efficient development.

## **1.4 Product Documentation**

The four documents listed in **Table 1-1** are required for a complete description and proper design with the 56F801. Documentation is available from local Freescale distributors, Freescale semiconductor sales offices, Freescale Literature Distribution Centers, or online at **www.freescale.com**.

| Торіс                                  | Description                                                                                              | Order Number |  |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------|--------------|--|--|

| 56800E<br>Family Manual                | Detailed description of the 56800 family architecture, and 16-bit core processor and the instruction set | 56800EFM     |  |  |

| DSP56F801/803/805/807<br>User's Manual |                                                                                                          |              |  |  |

| 56F801<br>Technical Data Sheet         | Electrical and timing specifications, pin descriptions, and package descriptions (this document)         | DSP56F801    |  |  |

| 56F801<br>Errata                       | Details any chip issues that might be present                                                            | 56F801E      |  |  |

Table 1-1 56F801 Chip Documentation

## 1.5 Data Sheet Conventions

This data sheet uses the following conventions:

| OVERBAR      | This is used to indicate a signal that is active when pulled low. For example, the $\overline{\text{RESET}}$ pin is active when low. |                                                                                    |            |                                  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------|----------------------------------|--|--|--|--|--|

| "asserted"   | A high true (active high) s                                                                                                          | A high true (active high) signal is high or a low true (active low) signal is low. |            |                                  |  |  |  |  |  |

| "deasserted" | A high true (active high) s                                                                                                          | A high true (active high) signal is low or a low true (active low) signal is high. |            |                                  |  |  |  |  |  |

| Examples:    | Signal/Symbol                                                                                                                        | Voltage <sup>1</sup>                                                               |            |                                  |  |  |  |  |  |

|              | PIN                                                                                                                                  | True                                                                               | Asserted   | V <sub>IL</sub> /V <sub>OL</sub> |  |  |  |  |  |

|              | PIN                                                                                                                                  | False                                                                              | Deasserted | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |  |  |

|              | PIN                                                                                                                                  | True                                                                               | Asserted   | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |  |  |

|              | PIN                                                                                                                                  | False                                                                              | Deasserted | V <sub>IL</sub> /V <sub>OL</sub> |  |  |  |  |  |

1. Values for V<sub>IL</sub>, V<sub>OL</sub>, V<sub>IH</sub>, and V<sub>OH</sub> are defined by individual product specifications.

# Part 2 Signal/Connection Descriptions

## 2.1 Introduction

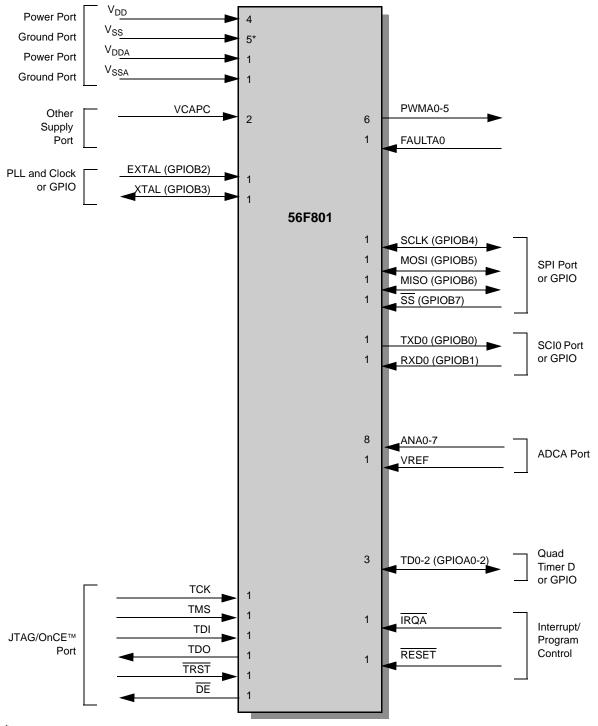

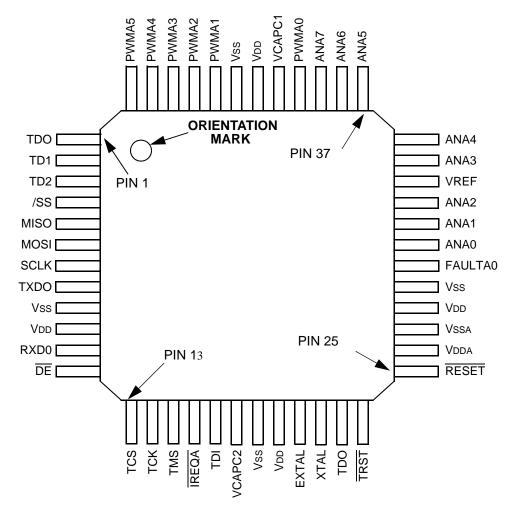

The input and output signals of the 56F801 are organized into functional groups, as shown in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 2-2** through **Table 2-12**, each table row describes the signal or signals present on a pin.

| Functional Group                                        | Number of<br>Pins | Detailed<br>Description |

|---------------------------------------------------------|-------------------|-------------------------|

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )            | 5                 | Table 2-2               |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )           | 6                 | Table 2-3               |

| Supply Capacitors                                       | 2                 | Table 2-4               |

| PLL and Clock                                           | 2                 | Table 2-5               |

| Interrupt and Program Control                           | 2                 | Table 2-6               |

| Pulse Width Modulator (PWM) Port                        | 7                 | Table 2-7               |

| Serial Peripheral Interface (SPI) Port <sup>1</sup>     | 4                 | Table 2-8               |

| Serial Communications Interface (SCI) Port <sup>1</sup> | 2                 | Table 2-9               |

| Analog-to-Digital Converter (ADC) Port                  | 9                 | Table 2-10              |

| Quad Timer Module Port                                  | 3                 | Table 2-11              |

| JTAG/On-Chip Emulation (OnCE)                           | 6                 | Table 2-12              |

**Table 2-1 Functional Group Pin Allocations**

1. Alternately, GPIO pins

\*includes TCS pin which is reserved for factory use and is tied to VSS

### Figure 2-1 56F801 Signals Identified by Functional Group<sup>1</sup>

<sup>1.</sup> Alternate pin functionality is shown in parenthesis.

| No. of<br>Pins | Signal<br>Name | Signal<br>Type   | State<br>During Reset | Signal Description                                                                                                                                                                                                                  |

|----------------|----------------|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | XTAL           | Output           | Chip-<br>driven       | <b>Crystal Oscillator Output</b> —This output should be connected to an 8MHz external crystal or ceramic resonator. For more information, please refer to <b>Section 3.5</b> .                                                      |

|                |                |                  |                       | This pin can also be connected to an external clock source. For more information, please refer to <b>Section 3.5.3</b> .                                                                                                            |

|                | GPIOB3         | Input/<br>Output | Input                 | <b>Port B GPIO</b> —This multiplexed pin is a General Purpose I/O (GPIO) pin that can be programmed as an input or output pin. This I/O can be utilized when using the on-chip relaxation oscillator so the XTAL pin is not needed. |

### Table 2-5 PLL and Clock (Continued)

## 2.4 Interrupt and Program Control Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type     | State<br>During Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------|--------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | ĪRQA           | Input<br>(Schmitt) | Input                 | <b>External Interrupt Request A</b> —The IRQA input is a synchronized external interrupt request that indicates that an external device is requesting service. It can be programmed to be level-sensitive or negative-edge- triggered.                                                                                                                                                                                                                    |

| 1              | RESET          | Input<br>(Schmitt) | Input                 | <b>Reset</b> —This input is a direct hardware reset on the processor. When RESET is asserted low, the controller is initialized and placed in the <u>Reset state</u> . A Schmitt trigger input is used for noise immunity. When the RESET pin is deasserted, the initial chip operating mode is latched from the EXTBOOT pin. The internal reset signal will be deasserted synchronous with the internal clocks, after a fixed number of internal clocks. |

|                |                |                    |                       | To ensure complete hardware reset, RESET and TRST should be asserted together. The only exception occurs in a debugging environment when a hardware device reset is required and it is necessary not to reset the OnCE/JTAG module. In this case, assert RESET, but do not assert TRST.                                                                                                                                                                   |

### **Table 2-6 Interrupt and Program Control Signals**

## 2.5 Pulse Width Modulator (PWM) Signals

| No. of<br>Pins | Signal<br>Name             | Signal<br>Type | State During<br>Reset | Signal Description                                                                                                                    |

|----------------|----------------------------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

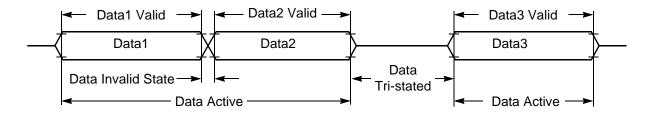

| 6              | PWMA0-5                    | Output         | Tri-stated            | <b>PWMA0-5</b> — These are six PWMA output pins.                                                                                      |

| 1              | FAULTA0 Input<br>(Schmitt) |                | Input                 | <b>FAULTA0</b> — This fault input pin is used for disabling selected PWMA outputs in cases where fault conditions originate off-chip. |

### Table 2-7 Pulse Width Modulator (PWMA) Signals

# 2.6 Serial Peripheral Interface (SPI) Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type | State During<br>Reset | Signal Description                                                                                                                                                                                                                                            |  |  |  |  |

|----------------|----------------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1              | MISO           | Input/Output   | Input                 | <b>SPI Master In/Slave Out (MISO)</b> —This serial data pin is an input to<br>a master device and an output from a slave device. The MISO line of<br>a slave device is placed in the high-impedance state if the slave<br>device is not selected.             |  |  |  |  |

|                | GPIOB6         | input Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as input or output pin.                                                                                                                                  |  |  |  |  |

|                |                |                |                       | After reset, the default state is MISO.                                                                                                                                                                                                                       |  |  |  |  |

| 1              | MOSI           | Input/Output   | Input                 | <b>SPI Master Out/Slave In (MOSI)</b> —This serial data pin is an output from a master device and an input to a slave device. The master device places data on the MOSI line a half-cycle before the clock edge that the slave device uses to latch the data. |  |  |  |  |

|                | GPIOB5         | Input/Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as input or output pin.                                                                                                                                  |  |  |  |  |

|                |                |                |                       | After reset, the default state is MOSI.                                                                                                                                                                                                                       |  |  |  |  |

| 1              | SCLK           | Input/Output   | Input                 | <b>SPI Serial Clock</b> —In master mode, this pin serves as an output, clocking slaved listeners. In slave mode, this pin serves as the data clock input.                                                                                                     |  |  |  |  |

|                | GPIOB4         | Input/Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as an input or output pin.<br>After reset, the default state is SCLK.                                                                                    |  |  |  |  |

| 1              | SS             | Input          | Input                 |                                                                                                                                                                                                                                                               |  |  |  |  |

|                | 33             | Input          | Input                 | SPI Slave Select—In master mode, this pin is used to arbitrate multiple masters. In slave mode, this pin is used to select the slave.                                                                                                                         |  |  |  |  |

|                | GPIOB7         | Input/Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as an input or output pin.                                                                                                                               |  |  |  |  |

|                |                |                |                       | After reset, the default state is $\overline{SS}$ .                                                                                                                                                                                                           |  |  |  |  |

### Table 2-8 Serial Peripheral Interface (SPI) Signals

## **3.2 DC Electrical Characteristics**

#### **Table 3-4 DC Electrical Characteristics**

Operating Conditions:  $V_{SS} = V_{SSA} = 0$  V,  $V_{DD} = V_{DDA} = 3.0-3.6$ V,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$ pF

| Characteristic                                                                     | Symbol                            | Min                   | Тур | Max  | Unit |

|------------------------------------------------------------------------------------|-----------------------------------|-----------------------|-----|------|------|

| Input high voltage (XTAL/EXTAL)                                                    | V <sub>IHC</sub>                  | 2.25                  | _   | 2.75 | V    |

| Input low voltage (XTAL/EXTAL)                                                     | V <sub>ILC</sub>                  | 0                     |     | 0.5  | V    |

| Input high voltage [GPIOB(2:3)] <sup>1</sup>                                       | V <sub>IH[GPIOB(2:3)]</sub>       | 2.0                   |     | 3.6  | V    |

| Input low voltage [GPIOB(2:3)] <sup>1</sup>                                        | V <sub>IL[GPIOB(2:3)]</sub>       | -0.3                  | _   | 0.8  | V    |

| Input high voltage (Schmitt trigger inputs) <sup>2</sup>                           | V <sub>IHS</sub>                  | 2.2                   |     | 5.5  | V    |

| Input low voltage (Schmitt trigger inputs) <sup>2</sup>                            | V <sub>ILS</sub>                  | -0.3                  |     | 0.8  | V    |

| Input high voltage (all other digital inputs)                                      | V <sub>IH</sub>                   | 2.0                   | —   | 5.5  | V    |

| Input low voltage (all other digital inputs)                                       | V <sub>IL</sub>                   | -0.3                  | —   | 0.8  | V    |

| Input current high (pullup/pulldown resistors disabled, $V_{IN}=V_{DD}$ )          | Ι <sub>ΙΗ</sub>                   | -1                    |     | 1    | μA   |

| Input current low (pullup/pulldown resistors disabled, $V_{IN}=V_{SS}$ )           | IIL                               | -1                    |     | 1    | μΑ   |

| Input current high (with pullup resistor, $V_{IN}=V_{DD}$ )                        | I <sub>IHPU</sub>                 | -1                    |     | 1    | μΑ   |

| Input current low (with pullup resistor, $V_{IN}=V_{SS}$ )                         | I <sub>ILPU</sub>                 | -210                  | —   | -50  | μA   |

| Input current high (with pulldown resistor, $V_{IN}=V_{DD}$ )                      | I <sub>IHPD</sub>                 | 20                    | _   | 180  | μΑ   |

| Input current low (with pulldown resistor, $V_{IN}=V_{SS}$ )                       | I <sub>ILPD</sub>                 | -1                    | _   | 1    | μΑ   |

| Nominal pullup or pulldown resistor value                                          | R <sub>PU</sub> , R <sub>PD</sub> |                       | 30  |      | KΩ   |

| Output tri-state current low                                                       | I <sub>OZL</sub>                  | -10                   | _   | 10   | μΑ   |

| Output tri-state current high                                                      | I <sub>OZH</sub>                  | -10                   | —   | 10   | μΑ   |

| Input current high (analog inputs, $V_{IN}=V_{DDA}$ ) <sup>3</sup>                 | I <sub>IHA</sub>                  | -15                   | —   | 15   | μA   |

| Input current low (analog inputs, V <sub>IN</sub> =V <sub>SSA</sub> ) <sup>3</sup> | I <sub>ILA</sub>                  | -15                   | —   | 15   | μA   |

| Output High Voltage (at I <sub>OH</sub> )                                          | V <sub>OH</sub>                   | V <sub>DD</sub> – 0.7 | —   |      | V    |

| Output Low Voltage (at I <sub>OL</sub> )                                           | V <sub>OL</sub>                   | _                     | —   | 0.4  | V    |

| Output source current                                                              | I <sub>OH</sub>                   | 4                     | —   |      | mA   |

| Output sink current                                                                | I <sub>OL</sub>                   | 4                     | —   |      | mA   |

| PWM pin output source current <sup>4</sup>                                         | I <sub>OHP</sub>                  | 10                    | —   | _    | mA   |

| PWM pin output sink current <sup>5</sup>                                           | I <sub>OLP</sub>                  | 16                    | —   | _    | mA   |

| Input capacitance                                                                  | C <sub>IN</sub>                   | —                     | 8   | _    | pF   |

| Output capacitance                                                                 | C <sub>OUT</sub>                  | _                     | 12  | _    | pF   |

#### Table 3-4 DC Electrical Characteristics (Continued)

Operating Conditions:  $V_{SS} = V_{SSA} = 0$  V,  $V_{DD} = V_{DDA} = 3.0-3.6$ V,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$ pF

| Characteristic                                             | Symbol                        | Min | Тур | Max | Unit |

|------------------------------------------------------------|-------------------------------|-----|-----|-----|------|

| V <sub>DD</sub> supply current                             | I <sub>DDT</sub> <sup>6</sup> |     |     |     |      |

| Run <sup>7</sup> (80MHz operation)                         |                               | —   | 120 | 130 | mA   |

| Run <sup>7</sup> (60MHz operation)                         |                               | —   | 102 | 111 | mA   |

| Wait <sup>8</sup>                                          |                               | —   | 96  | 102 | mA   |

| Stop                                                       |                               | —   | 62  | 70  | mA   |

| Low Voltage Interrupt, external power supply <sup>9</sup>  | V <sub>EIO</sub>              | 2.4 | 2.7 | 3.0 | V    |

| Low Voltage Interrupt, internal power supply <sup>10</sup> | V <sub>EIC</sub>              | 2.0 | 2.2 | 2.4 | V    |

| Power on Reset <sup>11</sup>                               | V <sub>POR</sub>              |     | 1.7 | 2.0 | V    |

1. Since the GPIOB[2:3] signals are shared with the XTAL/EXTAL function, these inputs are not 5.5 volt tolerant.

2. Schmitt Trigger inputs are: FAULTA0, IRQA, RESET, TCS, TCK, TMS, TDI, and TRST.

3. Analog inputs are: ANA[0:7], XTAL and EXTAL. Specification assumes ADC is not sampling.

4. PWM pin output source current measured with 50% duty cycle.

5. PWM pin output sink current measured with 50% duty cycle.

6.  $I_{DDT} = I_{DD} + I_{DDA}$  (Total supply current for  $V_{DD} + V_{DDA}$ )

7. Run (operating)  $I_{DD}$  measured using 8MHz clock source. All inputs 0.2V from rail; outputs unloaded. All ports configured as inputs; measured with all modules enabled.

8. Wait I<sub>DD</sub> measured using external square wave clock source ( $f_{osc}$  = 8MHz) into XTAL; all inputs 0.2V from rail; no DC loads; less than 50pF on all outputs. C<sub>L</sub> = 20pF on EXTAL; all ports configured as inputs; EXTAL capacitance linearly affects wait I<sub>DD</sub>; measured with PLL enabled.

9. This low voltage interrupt monitors the V<sub>DDA</sub> external power supply. V<sub>DDA</sub> is generally connected to the same potential as V<sub>DD</sub> via separate traces. If V<sub>DDA</sub> drops below V<sub>EIO</sub>, an interrupt is generated. Functionality of the device is guaranteed under transient conditions when V<sub>DDA</sub> $\geq$ V<sub>EIO</sub> (between the minimum specified V<sub>DD</sub> and the point when the V<sub>EIO</sub> interrupt is generated).

10. This low voltage interrupt monitors the internally regulated core power supply. If the output from the internal voltage is regulator drops below  $V_{EIC}$ , an interrupt is generated. Since the core logic supply is internally regulated, this interrupt will not be generated unless the external power supply drops below the minimum specified value (3.0V).

11. Power–on reset occurs whenever the internally regulated 2.5V digital supply drops below 1.5V typical. While power is ramping up, this signal remains active for as long as the internal 2.5V is below 1.5V typical no matter how long the ramp up rate is. The internally regulated voltage is typically 100 mV less than V<sub>DD</sub> during ramp up until 2.5V is reached, at which time it self regulates.

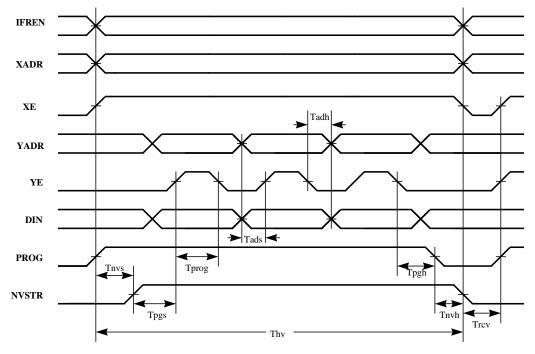

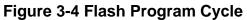

## 3.4 Flash Memory Characteristics

| I | able 3 | -5 Flash | Memory | Iruth | lable |  |

|---|--------|----------|--------|-------|-------|--|

|   |        |          |        |       |       |  |

| Mode         | XE <sup>1</sup> | YE <sup>2</sup> | SE <sup>3</sup> | OE <sup>4</sup> | PROG <sup>5</sup> | ERASE <sup>6</sup> | MAS1 <sup>7</sup> | NVSTR <sup>8</sup> |

|--------------|-----------------|-----------------|-----------------|-----------------|-------------------|--------------------|-------------------|--------------------|

| Standby      | L               | L               | L               | L               | L                 | L                  | L                 | L                  |

| Read         | Н               | Н               | Н               | Н               | L                 | L                  | L                 | L                  |

| Word Program | Н               | Н               | L               | L               | Н                 | L                  | L                 | Н                  |

| Page Erase   | Н               | L               | L               | L               | L                 | Н                  | L                 | Н                  |

| Mass Erase   | Н               | L               | L               | L               | L                 | Н                  | Н                 | Н                  |

1. X address enable, all rows are disabled when XE = 0

2. Y address enable, YMUX is disabled when YE = 0

3. Sense amplifier enable

4. Output enable, tri-state Flash data out bus when OE = 0

5. Defines program cycle

6. Defines erase cycle

7. Defines mass erase cycle, erase whole block

8. Defines non-volatile store cycle

#### **Table 3-6 IFREN Truth Table**

| Mode         | IFREN = 1                 | IFREN = 0                 |  |

|--------------|---------------------------|---------------------------|--|

| Read         | Read information block    | Read main memory block    |  |

| Word program | Program information block | Program main memory block |  |

| Page erase   | Erase information block   | Erase main memory block   |  |

| Mass erase   | Erase both block          | Erase main memory block   |  |

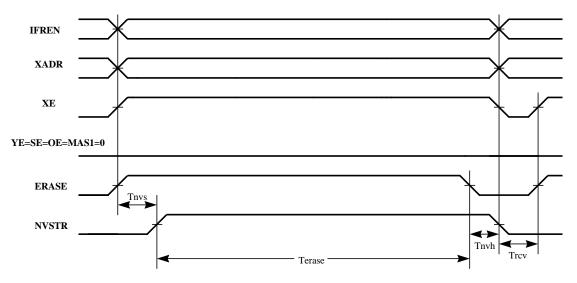

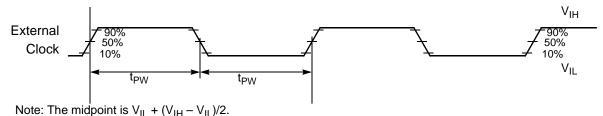

### 3.5.3 External Clock Source

The recommended method of connecting an external clock is given in **Figure 3-9**. The external clock source is connected to XTAL and the EXTAL pin is grounded.

#### Figure 3-9 Connecting an External Clock Signal

#### Table 3-8 External Clock Operation Timing Requirements<sup>3</sup>

Operating Conditions:  $V_{SS} = V_{SSA} = 0 V$ ,  $V_{DD} = V_{DDA} = 3.0-3.6 V$ ,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C

| Characteristic                                              | Symbol           | Min  | Тур | Max             | Unit |

|-------------------------------------------------------------|------------------|------|-----|-----------------|------|

| Frequency of operation (external clock driver) <sup>1</sup> | f <sub>osc</sub> | 0    | _   | 80 <sup>2</sup> | MHz  |

| Clock Pulse Width <sup>3, 4</sup>                           | t <sub>PW</sub>  | 6.25 | _   | _               | ns   |

1. See Figure 3-9 for details on using the recommended connection of an external clock driver.

2. May not exceed 60MHz for the DSP56F801FA60 device.

3. The high or low pulse width must be no smaller than 6.25ns or the chip will not function. However, the high pulse width does not have to be any particular percent of the low pulse width.

4. Parameters listed are guaranteed by design.

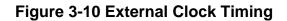

### 3.5.4 Use of On-Chip Relaxation Oscillator

An internal relaxation oscillator can supply the reference frequency when an external frequency source or crystal are not used. During a 56F801 boot or reset sequence, the relaxation oscillator is enabled by default, and the PRECS bit in the PLLCR word is set to 0 (Section 3.5). If an external oscillator is connected, the relaxation oscillator can be deselected instead by setting the PRECS bit in the PLLCR to 1. When this occurs, the PRECSS bit in the PLLSR (prescaler clock select status register) data word also sets to 1. If a changeover between internal and external oscillators is required at startup, internal device circuits

Temperature (<sup>o</sup>C)

Figure 3-11 Typical Relaxation Oscillator Frequency vs. Temperature (Trimmed to 8MHz @ 25°C)

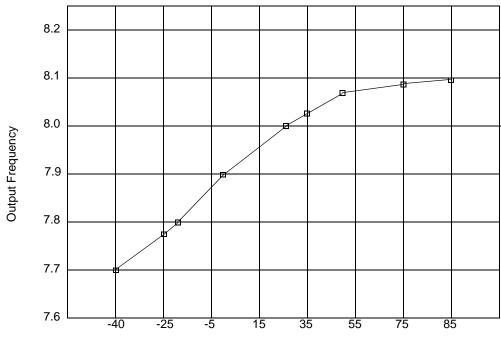

Figure 3-12 Typical Relaxation Oscillator Frequency vs. Trim Value @ 25°C

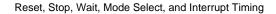

Figure 3-16 Interrupt from Wait State Timing

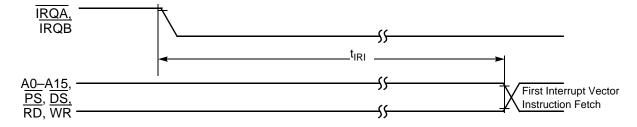

Figure 3-17 Recovery from Stop State Using Asynchronous Interrupt Timing

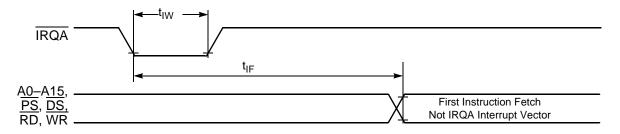

Figure 3-18 Recovery from Stop State Using IRQA Interrupt Service

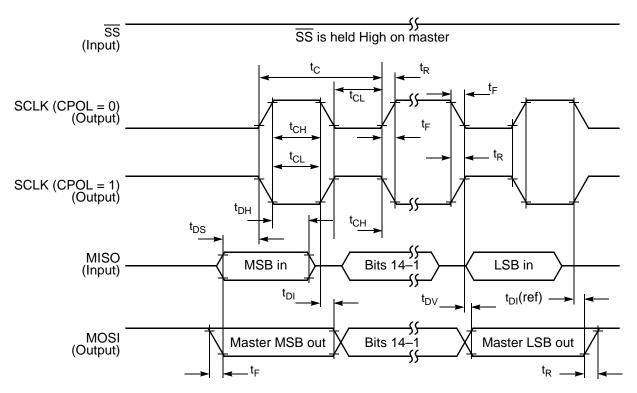

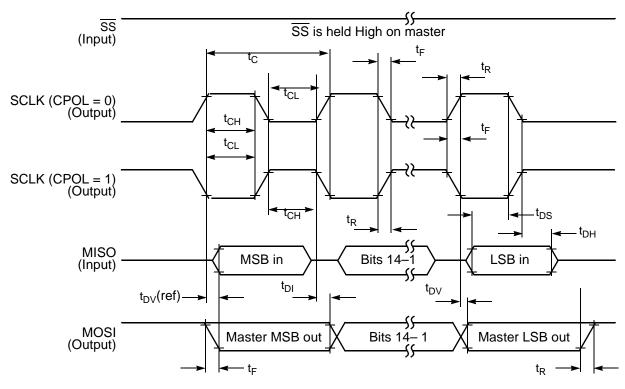

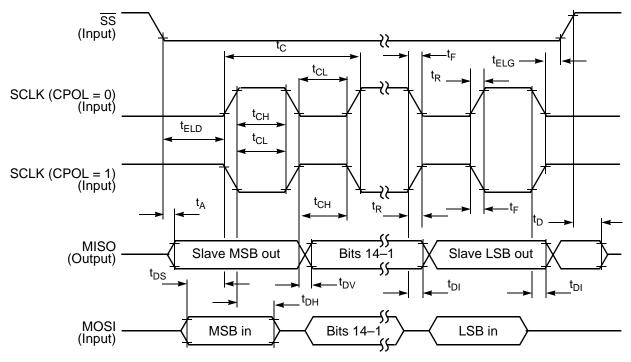

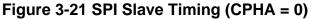

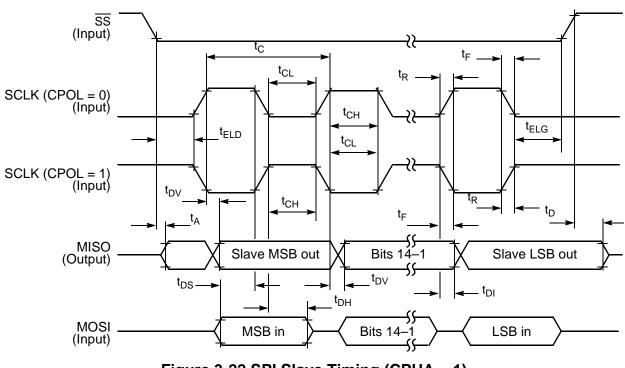

Figure 3-22 SPI Slave Timing (CPHA = 1)

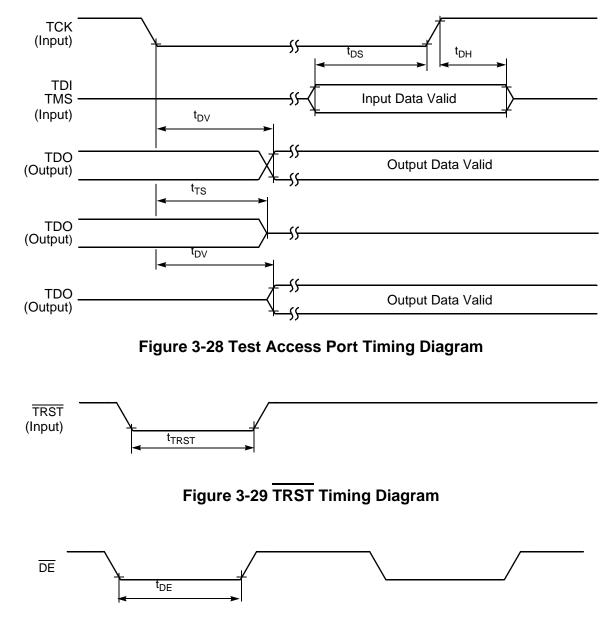

Figure 3-30 OnCE—Debug Event

# Part 4 Packaging

## 4.1 Package and Pin-Out Information 56F801

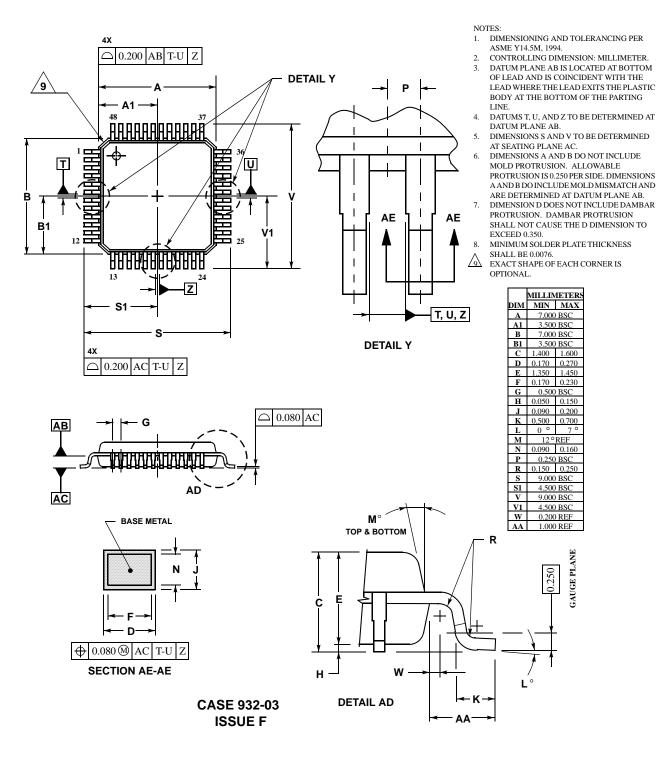

This section contains package and pin-out information for the 48-pin LQFP configuration of the 56F801.

Figure 4-1 Top View, 56F801 48-pin LQFP Package

Figure 4-2 48-pin LQFP Mechanical Information

Please see www.freescale.com for the most current case outline.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty. representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. This product incorporates SuperFlash® technology licensed from SST. © Freescale Semiconductor, Inc. 2005. All rights reserved.

DSP56F801 Rev. 17 09/2007