Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 56800                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 80MHz                                                                  |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 11                                                                     |

| Program Memory Size        | 16KB (8K x 16)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 16                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                              |

| Data Converters            | A/D 8x12b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56f801fa80e |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Document Revision History**

| Version History | Description of Change                                                                                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 17         | Added revision history.<br>Added this text to footnote 2 in <b>Table 3-8</b> : "However, the high pulse width does not have to<br>be any particular percent of the low pulse width." |

# Part 1 Overview

## 1.1 56F801 Features

## 1.1.1 Digital Signal Processing Core

- Efficient 16-bit 56800 family controller engine with dual Harvard architecture

- As many as 40 Million Instructions Per Second (MIPS) at 80MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Two 36-bit accumulators including extension bits

- 16-bit bidirectional barrel shifter

- Parallel instruction set with unique processor addressing modes

- Hardware DO and REP loops

- Three internal address buses and one external address bus

- Four internal data buses and one external data bus

- Instruction set supports both DSP and controller functions

- Controller style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/OnCE debug programming interface

## 1.1.2 Memory

- Harvard architecture permits as many as three simultaneous accesses to Program and Data memory

- On-chip memory including a low-cost, high-volume Flash solution

- 8K × 16 bit words of Program Flash

- 1K × 16-bit words of Program RAM

- 2K  $\times$  16-bit words of Data Flash

- $1K \times 16$ -bit words of Data RAM

- 2K × 16-bit words of Boot Flash

- Programmable Boot Flash supports customized boot code and field upgrades of stored code through a variety of interfaces (JTAG, SPI)

## 1.1.3 Peripheral Circuits for 56F801

- Pulse Width Modulator (PWM) with six PWM outputs, two Fault inputs, fault-tolerant design with deadtime insertion; supports both center- and edge-aligned modes

- Two 12-bit, Analog-to-Digital Converters (ADCs), which support two simultaneous conversions with two 4-multiplexed inputs; ADC and PWM modules can be synchronized

- General Purpose Quad Timer: Timer D with three pins (or three additional GPIO lines)

- Serial Communication Interface (SCI) with two pins (or two additional GPIO lines)

- Serial Peripheral Interface (SPI) with configurable four-pin port (or four additional GPIO lines)

## **1.4 Product Documentation**

The four documents listed in **Table 1-1** are required for a complete description and proper design with the 56F801. Documentation is available from local Freescale distributors, Freescale semiconductor sales offices, Freescale Literature Distribution Centers, or online at **www.freescale.com**.

| Торіс                                  | Topic Description                                                                                        |               |

|----------------------------------------|----------------------------------------------------------------------------------------------------------|---------------|

| 56800E<br>Family Manual                | Detailed description of the 56800 family architecture, and 16-bit core processor and the instruction set | 56800EFM      |

| DSP56F801/803/805/807<br>User's Manual | Detailed description of memory, peripherals, and interfaces of the 56F801, 56F803, 56F805, and 56F807    | DSP56F801-7UM |

| 56F801<br>Technical Data Sheet         | Electrical and timing specifications, pin descriptions, and package descriptions (this document)         | DSP56F801     |

| 56F801<br>Errata                       | Details any chip issues that might be present                                                            | 56F801E       |

Table 1-1 56F801 Chip Documentation

## 1.5 Data Sheet Conventions

This data sheet uses the following conventions:

| OVERBAR      | This is used to indicate a signal that is active when pulled low. For example, the $\overline{\text{RESET}}$ pin is active when low. |                                                                                    |                                |                                  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------|----------------------------------|--|--|--|--|

| "asserted"   | A high true (active high) s                                                                                                          | A high true (active high) signal is high or a low true (active low) signal is low. |                                |                                  |  |  |  |  |

| "deasserted" | A high true (active high) s                                                                                                          | ignal is low or a low tru                                                          | ue (active low) signal is higl | h.                               |  |  |  |  |

| Examples:    | Signal/Symbol                                                                                                                        | Signal/Symbol Logic State Signal State Voltage <sup>1</sup>                        |                                |                                  |  |  |  |  |

|              | PIN                                                                                                                                  | True                                                                               | Asserted                       | V <sub>IL</sub> /V <sub>OL</sub> |  |  |  |  |

|              | PIN                                                                                                                                  | False                                                                              | Deasserted                     | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |  |

|              | PIN                                                                                                                                  | True                                                                               | Asserted                       | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |  |

|              | PIN                                                                                                                                  | False                                                                              | Deasserted                     | V <sub>IL</sub> /V <sub>OL</sub> |  |  |  |  |

1. Values for V<sub>IL</sub>, V<sub>OL</sub>, V<sub>IH</sub>, and V<sub>OH</sub> are defined by individual product specifications.

# Part 2 Signal/Connection Descriptions

## 2.1 Introduction

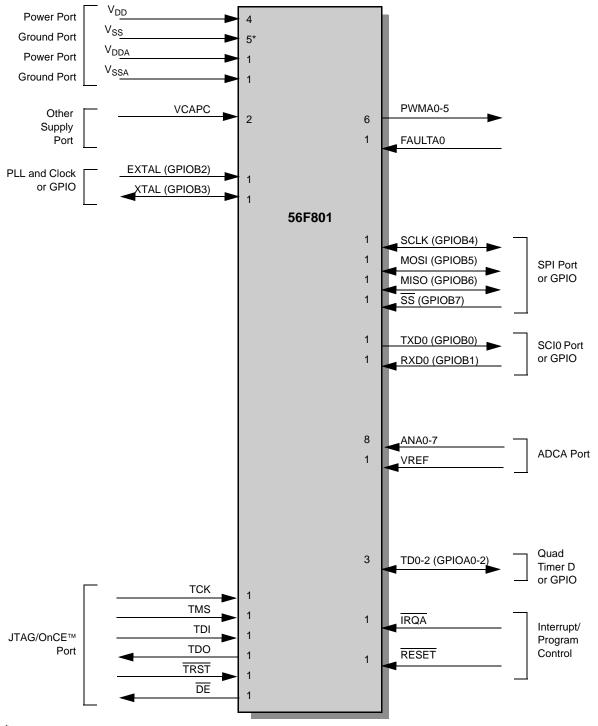

The input and output signals of the 56F801 are organized into functional groups, as shown in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 2-2** through **Table 2-12**, each table row describes the signal or signals present on a pin.

| Functional Group                                        | Number of<br>Pins | Detailed<br>Description |

|---------------------------------------------------------|-------------------|-------------------------|

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )            | 5                 | Table 2-2               |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )           | 6                 | Table 2-3               |

| Supply Capacitors                                       | 2                 | Table 2-4               |

| PLL and Clock                                           | 2                 | Table 2-5               |

| Interrupt and Program Control                           | 2                 | Table 2-6               |

| Pulse Width Modulator (PWM) Port                        | 7                 | Table 2-7               |

| Serial Peripheral Interface (SPI) Port <sup>1</sup>     | 4                 | Table 2-8               |

| Serial Communications Interface (SCI) Port <sup>1</sup> | 2                 | Table 2-9               |

| Analog-to-Digital Converter (ADC) Port                  | 9                 | Table 2-10              |

| Quad Timer Module Port                                  | 3                 | Table 2-11              |

| JTAG/On-Chip Emulation (OnCE)                           | 6                 | Table 2-12              |

**Table 2-1 Functional Group Pin Allocations**

1. Alternately, GPIO pins

\*includes TCS pin which is reserved for factory use and is tied to VSS

## Figure 2-1 56F801 Signals Identified by Functional Group<sup>1</sup>

56F801 Technical Data, Rev. 17

<sup>1.</sup> Alternate pin functionality is shown in parenthesis.

# 2.6 Serial Peripheral Interface (SPI) Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type | State During<br>Reset | Signal Description                                                                                                                                                                                                                                            |  |  |

|----------------|----------------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1              | MISO           | Input/Output   | Input                 | <b>SPI Master In/Slave Out (MISO)</b> —This serial data pin is an input to<br>a master device and an output from a slave device. The MISO line of<br>a slave device is placed in the high-impedance state if the slave<br>device is not selected.             |  |  |

|                | GPIOB6         | input Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as input or output pin.                                                                                                                                  |  |  |

|                |                |                |                       | After reset, the default state is MISO.                                                                                                                                                                                                                       |  |  |

| 1              | MOSI           | Input/Output   | Input                 | <b>SPI Master Out/Slave In (MOSI)</b> —This serial data pin is an output from a master device and an input to a slave device. The master device places data on the MOSI line a half-cycle before the clock edge that the slave device uses to latch the data. |  |  |

|                | GPIOB5         | Input/Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that car be individually programmed as input or output pin.                                                                                                                                  |  |  |

|                |                |                |                       | After reset, the default state is MOSI.                                                                                                                                                                                                                       |  |  |

| 1              | SCLK           | Input/Output   | Input                 | <b>SPI Serial Clock</b> —In master mode, this pin serves as an output, clocking slaved listeners. In slave mode, this pin serves as the data clock input.                                                                                                     |  |  |

|                | GPIOB4         | Input/Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as an input or output pin.<br>After reset, the default state is SCLK.                                                                                    |  |  |

| 1              | SS             | Input          | Input                 |                                                                                                                                                                                                                                                               |  |  |

|                | 33             | Input          | Input                 | SPI Slave Select—In master mode, this pin is used to arbitrate multiple masters. In slave mode, this pin is used to select the slave.                                                                                                                         |  |  |

|                | GPIOB7         | Input/Output   | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as an input or output pin.                                                                                                                               |  |  |

|                |                |                |                       | After reset, the default state is $\overline{SS}$ .                                                                                                                                                                                                           |  |  |

## Table 2-8 Serial Peripheral Interface (SPI) Signals

## 2.7 Serial Communications Interface (SCI) Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type | State During<br>Reset | Signal Description                                                                                                              |  |

|----------------|----------------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 1              | TXD0           | Output         | Input                 | Transmit Data (TXD0)—SCI0 transmit data output                                                                                  |  |

|                | GPIOB0         | Input/Output   | Input                 | <b>Port B GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as an input or output pin. |  |

|                |                |                |                       | After reset, the default state is SCI output.                                                                                   |  |

| 1              | RXD0           | Input          | Input                 | Receive Data (RXD0)—SCI0 receive data input                                                                                     |  |

|                | GPIOB1         | Input/Output   | Input                 | <b>Port B GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as an input or output pin. |  |

|                |                |                |                       | After reset, the default state is SCI input.                                                                                    |  |

Table 2-9 Serial Communications Interface (SCI0) Signals

## 2.8 Analog-to-Digital Converter (ADC) Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type | State During<br>Reset | Signal Description                                                                                     |  |  |  |

|----------------|----------------|----------------|-----------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| 4              | ANA0-3         | Input          | Input                 | ut ANA0-3—Analog inputs to ADC, channel 1                                                              |  |  |  |

| 4              | ANA4-7         | Input          | Input                 | ANA4-7—Analog inputs to ADC, channel 2                                                                 |  |  |  |

| 1              | VREF           | Input          | Input                 | <b>VREF</b> —Analog reference voltage for ADC. Must be set to $V_{DDA}$ -0.3V for optimal performance. |  |  |  |

# 2.9 Quad Timer Module Signals

#### Table 2-11 Quad Timer Module Signals

| No. of<br>Pins | Signal<br>Name | Signal Type  | State During<br>Reset | Signal Description                                                                                                                                                                      |

|----------------|----------------|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3              | TD0-2          | Input/Output | Input                 | TD0-2—Timer D Channel 0-2                                                                                                                                                               |

|                | GPIOA0-2       | Input/Output | Input                 | <b>Port A GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can be individually programmed as an input or output pin. After reset, the default state is the quad timer input. |

The 56F801 DC and AC electrical specifications are preliminary and are from design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications will be published after complete characterization and device qualifications have been completed.

#### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

| Characteristic                                                     | Symbol          | Min                   | Max                    | Unit |

|--------------------------------------------------------------------|-----------------|-----------------------|------------------------|------|

| Supply voltage                                                     | V <sub>DD</sub> | V <sub>SS</sub> – 0.3 | V <sub>SS</sub> + 4.0  | V    |

| All other input voltages, excluding Analog inputs                  | V <sub>IN</sub> | V <sub>SS</sub> – 0.3 | V <sub>SS</sub> + 5.5V | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>             | $\Delta V_{DD}$ | - 0.3                 | 0.3                    | V    |

| Voltage difference $V_{SS}$ to $V_{SSA}$                           | $\Delta V_{SS}$ | - 0.3                 | 0.3                    | V    |

| Analog inputs ANA0-7 and VREF                                      | V <sub>IN</sub> | V <sub>SSA</sub> -0.3 | V <sub>DDA</sub> + 0.3 | V    |

| Analog inputs EXTAL, XTAL                                          | V <sub>IN</sub> | V <sub>SSA</sub> -0.3 | V <sub>SSA</sub> + 3.0 | V    |

| Current drain per pin excluding $V_{DD}$ , $V_{SS}$ , & PWM ouputs | I               | —                     | 10                     | mA   |

#### Table 3-1 Absolute Maximum Ratings

#### **Table 3-2 Recommended Operating Conditions**

| Characteristic                                   | Symbol           | Min  | Тур | Мах  | Unit |

|--------------------------------------------------|------------------|------|-----|------|------|

| Supply voltage, digital                          | V <sub>DD</sub>  | 3.0  | 3.3 | 3.6  | V    |

| Supply Voltage, analog                           | V <sub>DDA</sub> | 3.0  | 3.3 | 3.6  | V    |

| Voltage difference $V_{DD}$ to $V_{DDA}$         | $\Delta V_{DD}$  | -0.1 | -   | 0.1  | V    |

| Voltage difference $\rm V_{SS}$ to $\rm V_{SSA}$ | $\Delta V_{SS}$  | -0.1 | -   | 0.1  | V    |

| ADC reference voltage <sup>1</sup>               | VREF             | 2.7  | -   | 3.3V | V    |

| Ambient operating temperature                    | T <sub>A</sub>   | -40  | _   | 85   | °C   |

1. VREF must be 0.3 below  $\mathrm{V}_{\mathrm{DDA}}.$

| Characteristic                            | Comments                | Symbol                      | Value Symbol                       |      | Notes  |  |

|-------------------------------------------|-------------------------|-----------------------------|------------------------------------|------|--------|--|

| Unaracteristic                            | Comments                | Oymbol                      | 48-pin LQFP                        | Unit | 110185 |  |

| Junction to ambient<br>Natural convection |                         | R <sub>θJA</sub>            | 50.6                               | °C/W | 2      |  |

| Junction to ambient (@1m/sec)             |                         | $R_{	ext{	heta}JMA}$        | 47.4                               | °C/W | 2      |  |

| Junction to ambient<br>Natural convection | Four layer board (2s2p) | R <sub>θJMA</sub><br>(2s2p) | 39.1                               | °C/W | 1,2    |  |

| Junction to ambient (@1m/sec)             | Four layer board (2s2p) | $R_{	ext{	heta}JMA}$        | 37.9                               | °C/W | 1,2    |  |

| Junction to case                          |                         | $R_{	ext{	heta}JC}$         | 17.3                               | °C/W | 3      |  |

| Junction to center of case                |                         | $\Psi_{JT}$                 | 1.2                                | °C/W | 4, 5   |  |

| I/O pin power dissipation                 |                         | P <sub>I/O</sub>            | User Determined                    | W    |        |  |

| Power dissipation                         |                         | Ρ <sub>D</sub>              | $P_D = (I_DD \times V_DD + P_I/O)$ | W    |        |  |

| Junction to center of case                |                         | P <sub>DMAX</sub>           | (TJ - TA) /RθJA                    | W    | 7      |  |

### Table 3-3 Thermal Characteristics<sup>6</sup>

#### Notes:

- 1. Theta-JA determined on 2s2p test boards is frequently lower than would be observed in an application. Determined on 2s2p thermal test board.

- 2. Junction to ambient thermal resistance, Theta-JA ( $R_{\theta JA}$ ) was simulated to be equivalent to the JEDEC specification JESD51-2 in a horizontal configuration in natural convection. Theta-JA was also simulated on a thermal test board with two internal planes (2s2p where s is the number of signal layers and p is the number of planes) per JESD51-6 and JESD51-7. The correct name for Theta-JA for forced convection or with the non-single layer boards is Theta-JMA.

- 3. Junction to case thermal resistance, Theta-JC ( $R_{\theta JC}$ ), was simulated to be equivalent to the measured values using the cold plate technique with the cold plate temperature used as the "case" temperature. The basic cold plate measurement technique is described by MIL-STD 883D, Method 1012.1. This is the correct thermal metric to use to calculate thermal performance when the package is being used with a heat sink.

- 4. Thermal Characterization Parameter, Psi-JT ( $\Psi_{JT}$ ), is the "resistance" from junction to reference point thermocouple on top center of case as defined in JESD51-2.  $\Psi_{JT}$  is a useful value to use to estimate junction temperature in steady state customer environments.

- 5. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 6. See Section 5.1 from more details on thermal design considerations.

- 7. TJ = Junction Temperature TA = Ambient Temperature

## **3.2 DC Electrical Characteristics**

#### **Table 3-4 DC Electrical Characteristics**

Operating Conditions:  $V_{SS} = V_{SSA} = 0$  V,  $V_{DD} = V_{DDA} = 3.0-3.6$ V,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$ pF

| Characteristic                                                                     | Symbol                            | Min                   | Тур | Max  | Unit |

|------------------------------------------------------------------------------------|-----------------------------------|-----------------------|-----|------|------|

| Input high voltage (XTAL/EXTAL)                                                    | V <sub>IHC</sub>                  | 2.25                  |     | 2.75 | V    |

| Input low voltage (XTAL/EXTAL)                                                     | V <sub>ILC</sub>                  | 0                     |     | 0.5  | V    |

| Input high voltage [GPIOB(2:3)] <sup>1</sup>                                       | V <sub>IH[GPIOB(2:3)]</sub>       | 2.0                   |     | 3.6  | V    |

| Input low voltage [GPIOB(2:3)] <sup>1</sup>                                        | V <sub>IL[GPIOB(2:3)]</sub>       | -0.3                  |     | 0.8  | V    |

| Input high voltage (Schmitt trigger inputs) <sup>2</sup>                           | V <sub>IHS</sub>                  | 2.2                   |     | 5.5  | V    |

| Input low voltage (Schmitt trigger inputs) <sup>2</sup>                            | V <sub>ILS</sub>                  | -0.3                  |     | 0.8  | V    |

| Input high voltage (all other digital inputs)                                      | V <sub>IH</sub>                   | 2.0                   | —   | 5.5  | V    |

| Input low voltage (all other digital inputs)                                       | V <sub>IL</sub>                   | -0.3                  |     | 0.8  | V    |

| Input current high (pullup/pulldown resistors disabled, $V_{IN}=V_{DD}$ )          | I <sub>IH</sub>                   | -1                    |     | 1    | μΑ   |

| Input current low (pullup/pulldown resistors disabled, $V_{IN}=V_{SS}$ )           | ۱ <sub>IL</sub>                   | -1                    |     | 1    | μΑ   |

| Input current high (with pullup resistor, $V_{IN}=V_{DD}$ )                        | I <sub>IHPU</sub>                 | -1                    |     | 1    | μΑ   |

| Input current low (with pullup resistor, $V_{IN}=V_{SS}$ )                         | I <sub>ILPU</sub>                 | -210                  | _   | -50  | μΑ   |

| Input current high (with pulldown resistor, $V_{IN}=V_{DD}$ )                      | I <sub>IHPD</sub>                 | 20                    |     | 180  | μΑ   |

| Input current low (with pulldown resistor, $V_{IN}=V_{SS}$ )                       | I <sub>ILPD</sub>                 | -1                    |     | 1    | μΑ   |

| Nominal pullup or pulldown resistor value                                          | R <sub>PU</sub> , R <sub>PD</sub> |                       | 30  |      | KΩ   |

| Output tri-state current low                                                       | I <sub>OZL</sub>                  | -10                   |     | 10   | μΑ   |

| Output tri-state current high                                                      | I <sub>OZH</sub>                  | -10                   | _   | 10   | μA   |

| Input current high (analog inputs, $V_{IN}=V_{DDA}$ ) <sup>3</sup>                 | I <sub>IHA</sub>                  | -15                   | _   | 15   | μA   |

| Input current low (analog inputs, V <sub>IN</sub> =V <sub>SSA</sub> ) <sup>3</sup> | I <sub>ILA</sub>                  | -15                   | _   | 15   | μA   |

| Output High Voltage (at I <sub>OH</sub> )                                          | V <sub>OH</sub>                   | V <sub>DD</sub> – 0.7 |     | _    | V    |

| Output Low Voltage (at I <sub>OL</sub> )                                           | V <sub>OL</sub>                   | _                     | —   | 0.4  | V    |

| Output source current                                                              | I <sub>ОН</sub>                   | 4                     | —   |      | mA   |

| Output sink current                                                                | I <sub>OL</sub>                   | 4                     |     | _    | mA   |

| PWM pin output source current <sup>4</sup>                                         | I <sub>OHP</sub>                  | 10                    |     | _    | mA   |

| PWM pin output sink current <sup>5</sup>                                           | I <sub>OLP</sub>                  | 16                    | —   | —    | mA   |

| Input capacitance                                                                  | C <sub>IN</sub>                   | —                     | 8   | —    | pF   |

| Output capacitance                                                                 | C <sub>OUT</sub>                  | —                     | 12  | _    | pF   |

Temperature (<sup>o</sup>C)

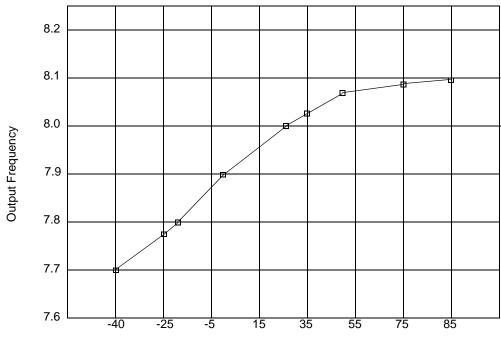

Figure 3-11 Typical Relaxation Oscillator Frequency vs. Temperature (Trimmed to 8MHz @ 25°C)

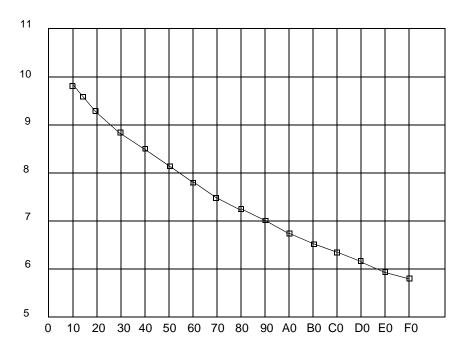

Figure 3-12 Typical Relaxation Oscillator Frequency vs. Trim Value @ 25°C

#### 3.5.5 **Phase Locked Loop Timing**

Table 3-10 PLL Timing Operating Conditions:  $V_{SS} = V_{SSA} = 0 V$ ,  $V_{DD} = V_{DDA} = 3.0-3.6 V$ ,  $T_A = -40^{\circ}$  to  $+85^{\circ}C$

| Characteristic                                                           | Symbol              | Min | Тур | Мах             | Unit |

|--------------------------------------------------------------------------|---------------------|-----|-----|-----------------|------|

| External reference crystal frequency for the PLL <sup>1</sup>            | f <sub>osc</sub>    | 4   | 8   | 10              | MHz  |

| PLL output frequency <sup>2</sup>                                        | f <sub>out</sub> /2 | 40  | _   | 80 <sup>3</sup> | MHz  |

| PLL stabilization time <sup>4</sup> 0° to +85°C                          | t <sub>plls</sub>   | _   | 10  | _               | ms   |

| PLL stabilization time <sup>4</sup> -40 <sup>o</sup> to 0 <sup>o</sup> C | t <sub>plls</sub>   | _   | 100 | 200             | ms   |

1. An externally supplied reference clock should be as free as possible from any phase jitter for the PLL to work correctly. The PLL is optimized for 8MHz input crystal.

2. ZCLK may not exceed 80MHz. For additional information on ZCLK and fout/2, please refer to the OCCS chapter in the User Manual. ZCLK = f<sub>op</sub>

3. Will not exceed 60MHz for the DSP56F801FA60 device.

4. This is the minimum time required after the PLL setup is changed to ensure reliable operation.

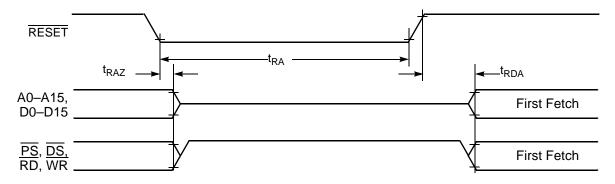

Figure 3-13 Asynchronous Reset Timing

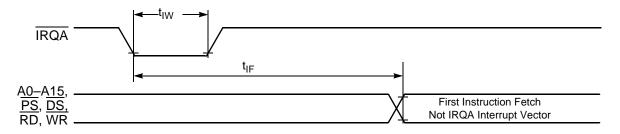

Figure 3-14 External Interrupt Timing (Negative-Edge-Sensitive)

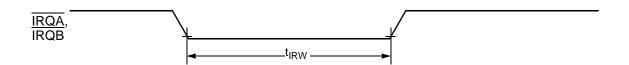

Figure 3-15 External Level-Sensitive Interrupt Timing

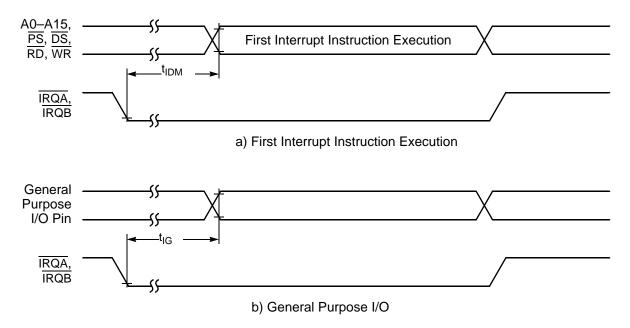

Figure 3-16 Interrupt from Wait State Timing

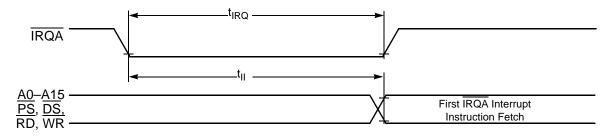

Figure 3-17 Recovery from Stop State Using Asynchronous Interrupt Timing

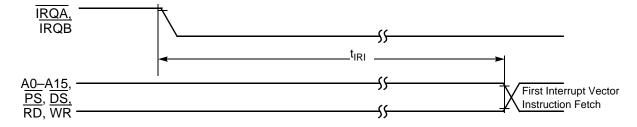

Figure 3-18 Recovery from Stop State Using IRQA Interrupt Service

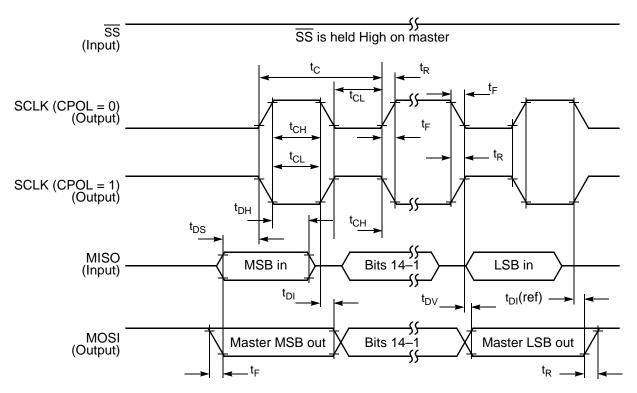

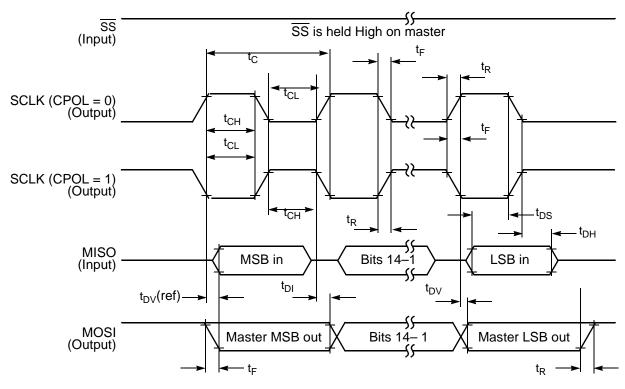

# 3.7 Serial Peripheral Interface (SPI) Timing

Table 3-12 SPI Timing<sup>1</sup> Operating Conditions:  $V_{SS} = V_{SSA} = 0 V$ ,  $V_{DD} = V_{DDA} = 3.0-3.6 V$ ,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$ pF

| Characteristic                                                          | Symbol           | Min          | Max          | Unit     | See Figure                                                       |

|-------------------------------------------------------------------------|------------------|--------------|--------------|----------|------------------------------------------------------------------|

| Cycle time<br>Master<br>Slave                                           | t <sub>C</sub>   | 50<br>25     |              | ns<br>ns | Figures <b>3-19, 3-20</b> ,<br><b>3-21, 3-22</b>                 |

| Enable lead time<br>Master<br>Slave                                     | t <sub>ELD</sub> | <br>25       |              | ns<br>ns | Figure 3-22                                                      |

| Enable lag time<br>Master<br>Slave                                      | t <sub>ELG</sub> | <br>100      |              | ns<br>ns | Figure 3-22                                                      |

| Clock (SCK) high time<br>Master<br>Slave                                | t <sub>CH</sub>  | 17.6<br>12.5 |              | ns<br>ns | Figures <b>3-19</b> , <b>3-20</b> ,<br><b>3-21</b> , <b>3-22</b> |

| Clock (SCK) low time<br>Master<br>Slave                                 | t <sub>CL</sub>  | 24.1<br>25   |              | ns<br>ns | Figures <b>3-19, 3-20</b> ,<br><b>3-21, 3-22</b>                 |

| Data setup time required for inputs<br>Master<br>Slave                  | t <sub>DS</sub>  | 20<br>0      |              | ns<br>ns | Figures <b>3-19</b> , <b>3-20</b> ,<br><b>3-21</b> , <b>3-22</b> |

| Data hold time required for inputs<br>Master<br>Slave                   | t <sub>DH</sub>  | 0<br>2       |              | ns<br>ns | Figures <b>3-19, 3-20</b> ,<br><b>3-21, 3-22</b>                 |

| Access time (time to data active from<br>high-impedance state)<br>Slave | t <sub>A</sub>   | 4.8          | 15           | ns       | Figure 3-22                                                      |

| Disable time (hold time to high-impedance state)<br>Slave               | t <sub>D</sub>   | 3.7          | 15.2         | ns       | Figure 3-22                                                      |

| Data Valid for outputs<br>Master<br>Slave (after enable edge)           | t <sub>DV</sub>  |              | 4.5<br>20.4  | ns<br>ns | Figures <b>3-19</b> , <b>3-20</b> ,<br><b>3-21</b> , <b>3-22</b> |

| Data invalid<br>Master<br>Slave                                         | t <sub>DI</sub>  | 0<br>0       |              | ns<br>ns | Figures <b>3-19</b> , <b>3-20</b> ,<br><b>3-21</b> , <b>3-22</b> |

| Rise time<br>Master<br>Slave                                            | t <sub>R</sub>   | _            | 11.5<br>10.0 | ns<br>ns | Figures <b>3-19</b> , <b>3-20</b> ,<br><b>3-21</b> , <b>3-22</b> |

| Fall time<br>Master<br>Slave                                            | t <sub>F</sub>   |              | 9.7<br>9.0   | ns<br>ns | Figures <b>3-19</b> , <b>3-20</b> ,<br><b>3-21</b> , <b>3-22</b> |

1. Parameters listed are guaranteed by design.

56F801 Technical Data, Rev. 17

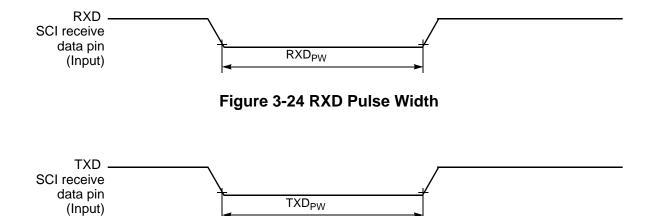

Figure 3-25 TXD Pulse Width

# 3.10 Analog-to-Digital Converter (ADC) Characteristics

| Characteristic                          | Symbol              | Min              | Тур     | Мах              | Unit                                 |

|-----------------------------------------|---------------------|------------------|---------|------------------|--------------------------------------|

| ADC input voltages                      | V <sub>ADCIN</sub>  | 0 <sup>1</sup>   | _       | $V_{REF}^2$      | V                                    |

| Resolution                              | R <sub>ES</sub>     | 12               | —       | 12               | Bits                                 |

| Integral Non-Linearity <sup>3</sup>     | INL                 | —                | +/- 4   | +/- 5            | LSB <sup>4</sup>                     |

| Differential Non-Linearity              | DNL                 | —                | +/- 0.9 | +/- 1            | LSB <sup>4</sup>                     |

| Monotonicity                            | GUARANTEED          |                  |         |                  |                                      |

| ADC internal clock <sup>5</sup>         | f <sub>ADIC</sub>   | 0.5              | _       | 5                | MHz                                  |

| Conversion range                        | R <sub>AD</sub>     | V <sub>SSA</sub> | _       | V <sub>DDA</sub> | V                                    |

| Conversion time                         | t <sub>ADC</sub>    | —                | 6       | —                | t <sub>AIC</sub> cycles <sup>6</sup> |

| Sample time                             | t <sub>ADS</sub>    | _                | 1       | _                | t <sub>AIC</sub> cycles <sup>6</sup> |

| Input capacitance                       | C <sub>ADI</sub>    | —                | 5       | _                | pF <sup>6</sup>                      |

| Gain Error (transfer gain) <sup>5</sup> | E <sub>GAIN</sub>   | 1.00             | 1.10    | 1.15             | _                                    |

| Offset Voltage <sup>5</sup>             | V <sub>OFFSET</sub> | +10              | +230    | +325             | mV                                   |

## Table 3-15 ADC Characteristics

- Bypass the  $V_{DD}$  and  $V_{SS}$  layers of the PCB with approximately 100  $\mu$ F, preferably with a high-grade capacitor such as a tantalum capacitor.

- Because the controller's output signals have fast rise and fall times, PCB trace lengths should be minimal.

- Consider all device loads as well as parasitic capacitance due to PCB traces when calculating capacitance. This is especially critical in systems with higher capacitive loads that could create higher transient currents in the V<sub>DD</sub> and GND circuits.

- Take special care to minimize noise levels on the VREF,  $V_{DDA}$  and  $V_{SSA}$  pins.

- Designs that utilize the TRST pin for JTAG port or OnCE module functionality (such as development or debugging systems) should allow a means to assert TRST whenever RESET is asserted, as well as a means to assert TRST independently of RESET. TRST must be asserted at power up for proper operation. Designs that do not require debugging functionality, such as consumer products, TRST should be tied low.

- Because the Flash memory is programmed through the JTAG/OnCE port, designers should provide an interface to this port to allow in-circuit Flash programming.

# Part 6 Ordering Information

**Table 6-1** lists the pertinent information needed to place an order. Consult a Freescale Semiconductor sales office or authorized distributor to determine availability and to order parts.

| Part   | Supply<br>Voltage | Package Type                              | Pin<br>Count | Ambient<br>Frequency<br>(MHz) | Order Number    |

|--------|-------------------|-------------------------------------------|--------------|-------------------------------|-----------------|

| 56F801 | 3.0–3.6 V         | Low Profile Plastic Quad Flat Pack (LQFP) | 48           | 80                            | DSP56F801FA80   |

| 56F801 | 3.0–3.6 V         | Low Profile Plastic Quad Flat Pack (LQFP) | 48           | 60                            | DSP56F801FA60   |

|        |                   |                                           |              |                               |                 |

| 56F801 | 3.0–3.6 V         | Low Profile Plastic Quad Flat Pack (LQFP) | 48           | 80                            | DSP56F801FA80E* |

| 56F801 | 3.0–3.6 V         | Low Profile Plastic Quad Flat Pack (LQFP) | 48           | 60                            | DSP56F801FA60E* |

## Table 6-1 56F801 Ordering Information

\*This package is RoHS compliant.