Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12xeg128mal |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Port | Pin Name | Pin Function<br>& Priority <sup>(1)</sup> | I/O | Description                                                                                            | Pin Function<br>after Reset |

|------|----------|-------------------------------------------|-----|--------------------------------------------------------------------------------------------------------|-----------------------------|

| Р    | PP7      | PWM7                                      | I/O | Pulse Width Modulator input/output channel 7                                                           | GPIO                        |

|      | Ī        | SCK2                                      | I/O | Serial Peripheral Interface 2 serial clock pin                                                         |                             |

|      | Ī        | (TIMIOC7)                                 | I/O | Timer Channel 7 input/output                                                                           |                             |

|      |          | GPIO/KWP7                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

|      | PP6      | PWM6                                      | 0   | Pulse Width Modulator output channel 6                                                                 |                             |

|      | -        | SS2                                       | I/O | Serial Peripheral Interface 2 slave select output in master mode, input for slave mode or master mode. |                             |

|      |          | (TIMIOC6)                                 | I/O | Timer Channel 6 input/output                                                                           |                             |

|      |          | GPIO/KWP6                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

|      | PP5      | PWM5                                      | 0   | Pulse Width Modulator output channel 5                                                                 |                             |

|      |          | MOSI2                                     | I/O | Serial Peripheral Interface 2 master out/slave in pin                                                  |                             |

|      |          | (TIMIOC5)                                 | I/O | Timer Channel 5 input/output                                                                           |                             |

|      |          | GPIO/KWP5                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

|      | PP4      | PWM4                                      | 0   | Pulse Width Modulator output channel 4                                                                 |                             |

|      |          | MISO2                                     | I/O | Serial Peripheral Interface 2 master in/slave out pin                                                  |                             |

|      |          | (TIMIOC4)                                 | I/O | Timer Channel 4 input/output                                                                           |                             |

|      |          | GPIO/KWP4                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

|      | PP3      | Pulse Width Modulator output channel 3    |     |                                                                                                        |                             |

|      |          | SS1                                       | I/O | Serial Peripheral Interface 1 slave select output in master mode, input for slave mode or master mode. |                             |

|      |          | (TIMIOC3)                                 | I/O | Timer Channel 3 input/output                                                                           |                             |

|      |          | GPIO/KWP3                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

|      | PP2      | PWM2                                      | 0   | Pulse Width Modulator output channel 2                                                                 |                             |

|      |          | SCK1                                      | I/O | Serial Peripheral Interface 1 serial clock pin                                                         |                             |

|      |          | (TIMIOC2)                                 | I/O | Timer Channel 2 input/output                                                                           |                             |

|      |          | GPIO/KWP2                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

|      | PP1      | PWM1                                      | 0   | Pulse Width Modulator output channel 1                                                                 |                             |

|      |          | MOSI1                                     | I/O | Serial Peripheral Interface 1 master out/slave in pin                                                  |                             |

|      |          | (TIMIOC1)                                 | I/O | Timer Channel 1 input/output                                                                           |                             |

|      |          | GPIO/KWP1                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

|      | PP0      | PWM0                                      | 0   | Pulse Width Modulator output channel 0                                                                 |                             |

|      | Ī        | MISO1                                     | I/O | Serial Peripheral Interface 1 master in/slave out pin                                                  |                             |

|      |          | (TIMIOC0)                                 | I/O | Timer Channel 0 input/output                                                                           |                             |

|      |          | GPIO/KWP0                                 | I/O | General-purpose I/O with interrupt                                                                     |                             |

#### Table 2-42. PTIP Register Field Descriptions

| Field | Description                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0   | <b>Port P input data</b> —                                                                                                                                      |

| PTIP  | This register always reads back the buffered state of the associated pins. This can also be used to detect overload or short circuit conditions on output pins. |

## 2.3.47 Port P Data Direction Register (DDRP)

Address 0x025A

Access: User read/write<sup>(1)</sup>

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | DDRP7 | DDRP6 | DDRP5 | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 2-45. Port P Data Direction Register (DDRP)

1. Read: Anytime. Write: Anytime.

#### Table 2-43. DDRP Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DDRP   | Port P data direction—<br>This register controls the data direction of pin 7.<br>The enabled PWM channel 7 forces the I/O state to be an output. If the PWM shutdown feature is enabled this pin<br>is forced to be an input. In these cases the data direction bit will not change.<br>1 Associated pin is configured as output.<br>0 Associated pin is configured as input. |

| 6-0<br>DDRP | Port P data direction—<br>The PWM forces the I/O state to be an output for each port line associated with an enabled PWM6-0 channel. In this case the data direction bit will not change.<br>1 Associated pin is configured as output.<br>0 Associated pin is configured as input.                                                                                            |

#### NOTE

Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read on PTP or PTIP registers, when changing the DDRP register.

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7–6<br>CS3E[1:0] | Chip Select 3 Enables — These bits enable the external chip select $\overline{CS3}$ output which is asserted during accesses to specific external addresses. The associated global address range is shown in Table 3-7 and Figure 3-17.         Chip select 3 is only active if enabled in Normal Expanded mode, Emulation Expanded mode.         The function disabled in all other operating modes.         00       Chip select 3 is disabled         01.10.11       Chip select 3 is enabled |  |  |  |  |  |

| 5–4<br>CS2E[1:0] | Chip Select 2 Enables — These bits enable the external chip select $\overline{CS2}$ output which is asserted during accesses to specific external addresses. The associated global address range is shown in Table 3-7 and Figure 3-17.<br>Chip select 2 is only active if enabled in Normal Expanded mode, Emulation Expanded mode.<br>The function disabled in all other operating modes.<br>00 Chip select 2 is disabled<br>01,10,11 Chip select 2 is enabled                                 |  |  |  |  |  |

| 3–2<br>CS1E[1:0] | Chip Select 1 Enables — These bits enable the external chip select $\overline{CS1}$ output which is asserted during accesses to specific external addresses. The associated global address range is shown in Table 3-7 and Figure 3-17.         Chip select 1 is only active if enabled in Normal Expanded mode, Emulation Expanded mode.         The function disabled in all other operating modes.         00       Chip select 1 is disabled         01,10,11 Chip select 1 is enabled       |  |  |  |  |  |

| 1–0<br>CS0E[1:0] | Chip Select 0 Enables — These bits enable the external chip select $\overline{CS0}$ output which is asserted during accesses to specific external addresses. The associated global address range is shown in Table 3-7 and Figure 3-17.         Chip select 0 is only active if enabled in Normal Expanded mode, Emulation Expanded mode.         The function disabled in all other operating modes.         00       Chip select 0 is disabled         01,10,11 Chip select 0 is enabled       |  |  |  |  |  |

#### Table 3-6. MMCCTL0 Field Descriptions

Table 3-7 shows the address boundaries of each chip select and the relationship with the implemented resources (internal) parameters.

Table 3-7. Global Chip Selects Memory Space

| Chip Selects       | Bottom Address | Top Address                              |

|--------------------|----------------|------------------------------------------|

| CS3                | 0x00_0800      | 0x0F_FFFF minus RAMSIZE <sup>(1)</sup>   |

| CS2 <sup>(2)</sup> | 0x14_0000      | 0x1F_FFFF                                |

| CS1                | 0x20_0000      | 0x3F_FFFF                                |

| CS0 <sup>(3)</sup> | 0x40_0000      | 0x7F_FFFF minus FLASHSIZE <sup>(4)</sup> |

1. External RPAGE accesses in (NX, EX)

2. When ROMHM is set (see ROMHM in Table 3-16) the CS2 is asserted in the space occupied by this onchip memory block.

3. When the internal NVM is enabled (see ROMON in Section 3.3.2.5, "MMC Control Register (MMCCTL1)) the CS0 is not asserted in the space occupied by this on-chip memory block.

4. External PPAGE accesses in (NX, EX)

## BHS

## Branch if Higher or Same (Same as BCC)

# BHS

## Operation

If C = 0, then PC +  $0002 + (REL9 \le 1) \Rightarrow PC$

Branch instruction to compare unsigned numbers.

#### Branch if $RS1 \ge RS2$ :

SUB R0,RS1,RS2 BHS REL9

## **CCR Effects**

- N: Not affected.

- Z: Not affected.

- V: Not affected.

- C: Not affected.

## **Code and CPU Cycles**

| Source Form | Address<br>Mode | Machine Code       | Cycles |

|-------------|-----------------|--------------------|--------|

| BHS REL9    | REL9            | 0 0 1 0 0 0 0 REL9 | PP/P   |

## Subtract with Carry

#### Operation

RS1 - RS2 - C  $\Rightarrow$  RD

Subtracts the content of register RS2 and the value of the Carry bit from the content of register RS1 using binary subtraction and stores the result in the destination register RD. Also the zero flag is carried forward from the previous operation allowing 32 and more bit subtractions.

Example:

| SUB | R6,R4,R2 |                                            |

|-----|----------|--------------------------------------------|

| SBC | R7,R5,R3 | ; R7:R6 = R5:R4 - R3:R2                    |

| BCC |          | ; conditional branch on 32 bit subtraction |

#### **CCR Effects**

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000 and Z was set before this operation; cleared otherwise.

- V: Set if a two's complement overflow resulted from the operation; cleared otherwise. RS1[15] & RS2[15] & RD[15]<sub>new</sub> | RS1[15] & RS2[15] & RD[15]<sub>new</sub>

- C: Set if there is a carry from bit 15 of the result; cleared otherwise. RS1[15] & RS2[15] | RS1[15] & RD[15]<sub>new</sub> | RS2[15] & RD[15]<sub>new</sub>

## Code and CPU Cycles

| Source Form      | Address<br>Mode |   | Machine Code |   |   |   |    |     | Cycles |   |   |   |

|------------------|-----------------|---|--------------|---|---|---|----|-----|--------|---|---|---|

| SBC RD, RS1, RS2 | TRI             | 0 | 0            | 0 | 1 | 1 | RD | RS1 | RS2    | 0 | 1 | Р |

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PLLSEL | PLL Select BitWrite: Anytime.Writing a one when LOCK=0 has no effect. This prevents the selection of an unstable PLLCLK as SYSCLK.PLLSEL bit is cleared when the MCU enters Self Clock Mode, Stop Mode or Wait Mode with PLLWAI bit set.It is recommended to read back the PLLSEL bit to make sure PLLCLK has really been selected asSYSCLK, as LOCK status bit could theoretically change at the very moment writing the PLLSEL bit.00System clocks are derived from OSCCLK (f <sub>BUS</sub> = f <sub>OSC</sub> / 2).11System clocks are derived from PLLCLK (f <sub>BUS</sub> = f <sub>PLL</sub> / 2). |

| 6<br>PSTP   | <ul> <li>Pseudo Stop Bit</li> <li>Write: Anytime</li> <li>This bit controls the functionality of the oscillator during Stop Mode.</li> <li>0 Oscillator is disabled in Stop Mode.</li> <li>1 Oscillator continues to run in Stop Mode (Pseudo Stop).</li> <li>Note: Pseudo Stop Mode allows for faster STOP recovery and reduces the mechanical stress and aging of the resonator in case of frequent STOP conditions at the expense of a slightly increased power consumption.</li> </ul>                                                                                                                |

| 5<br>XCLKS  | <ul> <li>Oscillator Configuration Status Bit — This read-only bit shows the oscillator configuration status.</li> <li>0 Loop controlled Pierce Oscillator is selected.</li> <li>1 External clock / full swing Pierce Oscillator is selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |

| 3<br>PLLWAI | PLL Stops in Wait Mode Bit         Write: Anytime         If PLLWAI is set, the S12XECRG will clear the PLLSEL bit before entering Wait Mode. The PLLON bit remains set during Wait Mode but the IPLL is powered down. Upon exiting Wait Mode, the PLLSEL bit has to be set manually if PLL clock is required.         0       IPLL keeps running in Wait Mode.         1       IPLL stops in Wait Mode.                                                                                                                                                                                                  |

| 1<br>RTIWAI | <b>RTI Stops in Wait Mode Bit</b> Write: Anytime         0       RTI keeps running in Wait Mode.         1       RTI stops and initializes the RTI dividers whenever the part goes into Wait Mode.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0<br>COPWAI | <ul> <li>COP Stops in Wait Mode Bit</li> <li>Normal modes: Write once</li> <li>Special modes: Write anytime</li> <li>0 COP keeps running in Wait Mode.</li> <li>1 COP stops and initializes the COP counter whenever the part goes into Wait Mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

#### Table 11-6. CLKSEL Field Descriptions

## 11.3.2.7 S12XECRG IPLL Control Register (PLLCTL)

This register controls the IPLL functionality.

Module Base + 0x0006

| _      | 7   | 6     | 5   | 4   | 3      | 2   | 1   | 0    |

|--------|-----|-------|-----|-----|--------|-----|-----|------|

| R<br>W | CME | PLLON | FM1 | FM0 | FSTWKP | PRE | PCE | SCME |

| Reset  | 1   | 1     | 0   | 0   | 0      | 0   | 0   | 1    |

## Read: Anytime

### Write: Refer to each bit for individual write conditions

#### Table 11-7. PLLCTL Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>CME         | <ul> <li>Clock Monitor Enable Bit — CME enables the clock monitor. Write anytime except when SCM = 1.</li> <li>Clock monitor is disabled.</li> <li>Clock monitor is enabled. Slow or stopped clocks will cause a clock monitor reset sequence or Self Clock Mode.</li> <li>Note: Operating with CME=0 will not detect any loss of clock. In case of poor clock quality this could cause unpredictable operation of the MCU!</li> <li>In Stop Mode (PSTP=0) the clock monitor is disabled independently of the CME bit setting and any loss of external clock will not be detected.</li> <li>Also after wake-up from stop mode (PSTP = 0) with fast wake-up enabled (FSTWKP = 1) the clock monitor is disabled independently of the CME bit setting and any loss of external clock will not be detected.</li> </ul>                                                                                 |  |  |  |  |

| 6<br>PLLON       | <ul> <li>Phase Lock Loop On Bit — PLLON turns on the IPLL circuitry. In Self Clock Mode, the IPLL is turned on, but the PLLON bit reads the last written value. Write anytime except when PLLSEL = 1.</li> <li>0 IPLL is turned off.</li> <li>1 IPLL is turned on.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 5, 4<br>FM1, FM0 | IPLL <b>Frequency Modulation Enable Bit</b> — FM1 and FM0 enable additional frequency modulation on the VCOCLK. This is to reduce noise emission. The modulation frequency is $f_{ref}$ divided by 16. Write anytime except when PLLSEL = 1. See Table 11-8 for coding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 3<br>FSTWKP      | <ul> <li>Fast Wake-up from Full Stop Bit — FSTWKP enables fast wake-up from full stop mode. Write anytime. If Self-Clock Mode is disabled (SCME = 0) this bit has no effect.</li> <li>Fast wake-up from full stop mode is disabled.</li> <li>Fast wake-up from full stop mode is enabled. When waking up from full stop mode the system will immediately resume operation in Self-Clock Mode (see Section 11.4.1.4, "Clock Quality Checker"). The SCMIF flag will not be set. The system will remain in Self-Clock Mode with oscillator and clock monitor disabled until FSTWKP bit is cleared. The clearing of FSTWKP will start the oscillator, the clock monitor and the clock quality check. If the clock quality check is successful, the S12XECRG will switch all system clocks to OSCCLK. The SCMIF flag will be set. See application examples in Figure 11-19 and Figure 11-20.</li> </ul> |  |  |  |  |

| 2<br>PRE         | <ul> <li>RTI Enable During Pseudo Stop Bit — PRE enables the RTI during Pseudo Stop Mode.</li> <li>Write anytime.</li> <li>0 RTI stops running during Pseudo Stop Mode.</li> <li>1 RTI continues running during Pseudo Stop Mode.</li> <li>Note: If the PRE bit is cleared the RTI dividers will go static while Pseudo Stop Mode is active. The RTI dividers will not initialize like in Wait Mode with RTIWAI bit set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 1<br>PCE         | <ul> <li>COP Enable During Pseudo Stop Bit — PCE enables the COP during Pseudo Stop Mode.</li> <li>Write anytime.</li> <li>0 COP stops running during Pseudo Stop Mode</li> <li>1 COP continues running during Pseudo Stop Mode</li> <li>Note: If the PCE bit is cleared the COP dividers will go static while Pseudo Stop Mode is active. The COP dividers will not initialize like in Wait Mode with COPWAI bit set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 0<br>SCME        | Self Clock Mode Enable Bit         Normal modes: Write once         Special modes: Write anytime         SCME can not be cleared while operating in Self Clock Mode (SCM = 1).         0 Detection of crystal clock failure causes clock monitor reset (see Section 11.5.1.1, "Clock Monitor Reset").         1 Detection of crystal clock failure forces the MCU in Self Clock Mode (see Section 11.4.2.2, "Self Clock Mode").                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

All bits reset to zero.

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:4<br>SHxy | <ul> <li>Share Input action of Input Capture Channels x and y</li> <li>0 Normal operation</li> <li>1 The channel input 'x' causes the same action on the channel 'y'. The port pin 'x' and the corresponding edge detector is used to be active on the channel 'y'.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 3<br>TFMOD  | <ul> <li>Timer Flag Setting Mode — Use of the TFMOD bit in conjunction with the use of the ICOVW register allows a timer interrupt to be generated after capturing two values in the capture and holding registers instead of generating an interrupt for every capture.</li> <li>By setting TFMOD in queue mode, when NOVWx bit is set and the corresponding capture and holding registers are emptied, an input capture event will first update the related input capture register with the main timer contents. At the next event, the TCx data is transferred to the TCxH register, the TCx is updated and the CxF interrupt flag is set. In all other input capture cases the interrupt flag is set by a valid external event on ICx.</li> <li>The timer flags C3F–C0F in TFLG1 are set when a valid input capture transition on the corresponding port pin occurs.</li> <li>If in queue mode (BUFEN = 1 and LATQ = 0), the timer flags C3F–C0F in TFLG1 are set only when a latch on the corresponding holding register occurs. If the queue mode is not engaged, the timer flags C3F–C0F are set the same way as for TFMOD = 0.</li> </ul> |  |  |  |  |  |

| 2<br>PACMX  | <ul> <li>8-Bit Pulse Accumulators Maximum Count</li> <li>0 Normal operation. When the 8-bit pulse accumulator has reached the value 0x00FF, with the next active edge, it will be incremented to 0x0000.</li> <li>1 When the 8-bit pulse accumulator has reached the value 0x00FF, it will not be incremented further. The value 0x00FF indicates a count of 255 or more.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 1<br>BUFFEN | <ul> <li>IC Buffer Enable</li> <li>0 Input capture and pulse accumulator holding registers are disabled.</li> <li>1 Input capture and pulse accumulator holding registers are enabled. The latching mode is defined by LATQ control bit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 0<br>LATQ   | <ul> <li>Input Control Latch or Queue Mode Enable — The BUFEN control bit should be set in order to enable the IC and pulse accumulators holding registers. Otherwise LATQ latching modes are disabled.</li> <li>Write one into ICLAT bit in MCCTL, when LATQ and BUFEN are set will produce latching of input capture and pulse accumulators registers into their holding registers.</li> <li>Queue mode of Input Capture is enabled. The main timer value is memorized in the IC register by a valid input pin transition. With a new occurrence of a capture, the value of the IC register will be transferred to its holding register and the IC register memorizes the new timer value.</li> <li>Latch mode is enabled. Latching function occurs when modulus down-counter reaches zero or a zero is written into the count register MCCNT (see Section 14.4.1.1.2, "Buffered IC Channels"). With a latching event the contents of IC registers and 8-bit pulse accumulators are transferred to their holding registers. 8-bit pulse accumulators are cleared.</li> </ul>                                                                    |  |  |  |  |  |

#### Table 14-31. ICSYS Field Descriptions

| PTMPS7 | PTMPS6 | PTMPS5 | PTMPS4 | PTMPS3 | PTMPS2 | PTMPS1 | PTMPS0 | Prescaler<br>Division<br>Rate |

|--------|--------|--------|--------|--------|--------|--------|--------|-------------------------------|

| 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1                             |

| 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 2                             |

| 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 3                             |

| 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 4                             |

| 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 5                             |

| 0      | 0      | 0      | 0      | 0      | 1      | 0      | 1      | 6                             |

| 0      | 0      | 0      | 0      | 0      | 1      | 1      | 0      | 7                             |

| 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      | 8                             |

| 0      | 0      | 0      | 0      | 1      | 1      | 1      | 1      | 16                            |

| 0      | 0      | 0      | 1      | 1      | 1      | 1      | 1      | 32                            |

| 0      | 0      | 1      | 1      | 1      | 1      | 1      | 1      | 64                            |

| 0      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 128                           |

| 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 256                           |

#### Table 14-36. Precision Timer Modulus Counter Prescaler Select Examples when PRNT = 1

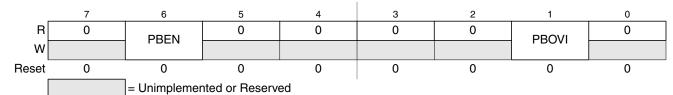

## 14.3.2.28 16-Bit Pulse Accumulator B Control Register (PBCTL)

Module Base + 0x0030

#### Figure 14-51. 16-Bit Pulse Accumulator B Control Register (PBCTL)

Read: Anytime

Write: Anytime

All bits reset to zero.

- 3. Input pulses with a duration between  $(DLY_CNT 1)$  and  $DLY_CNT$  cycles may be rejected or accepted, depending on their relative alignment with the sample points.

- 4. Input pulses with a duration of DLY\_CNT or longer are accepted.

## 14.4.1.2 OC Channel Initialization

An internal compare channel whose output drives OCx may be programmed before the timer drives the output compare state (OCx). The required output of the compare logic can be disconnected from the pin, leaving it driven by the GP IO port, by setting the appropriate OCPDx bit before enabling the output compare channel (by default the OCPD bits are cleared which would enable the output compare logic to drive the pin as soon as the timer output compare channel is enabled). The desired initial state can then be configured in the internal output compare logic by forcing a compare action with the logic disconnected from the IO (by writing a one to CFORCx bit with TIOSx, OCPDx and TEN bits set to one). Clearing the output compare disconnect bit (OCPDx) will then allow the internal compare logic to drive the programmed state to OCx. This allows a glitch free switching between general purpose I/O and timer output functionality.

## 14.4.1.3 Pulse Accumulators

There are four 8-bit pulse accumulators with four 8-bit holding registers associated with the four IC buffered channels 3–0. A pulse accumulator counts the number of active edges at the input of its channel.

The minimum pulse width for the PAI input is greater than two bus clocks. The maximum input frequency on the pulse accumulator channel is one half the bus frequency or Eclk.

The user can prevent the 8-bit pulse accumulators from counting further than 0x00FF by utilizing the PACMX control bit in the ICSYS register. In this case, a value of 0x00FF means that 255 counts or more have occurred.

Each pair of pulse accumulators can be used as a 16-bit pulse accumulator (see Figure 14-72).

Pulse accumulator B operates only as an event counter, it does not feature gated time accumulation mode. The edge control for pulse accumulator B as a 16-bit pulse accumulator is defined by TCTL4[1:0].

To operate the 16-bit pulse accumulators A and B (PACA and PACB) independently of input capture or output compare 7 and 0 respectively, the user must set the corresponding bits: IOSx = 1, OMx = 0, and OLx = 0. OC7M7 or OC7M0 in the OC7M register must also be cleared.

There are two modes of operation for the pulse accumulators:

• Pulse accumulator latch mode

The value of the pulse accumulator is transferred to its holding register when the modulus downcounter reaches zero, a write 0x0000 to the modulus counter or when the force latch control bit ICLAT is written.

At the same time the pulse accumulator is cleared.

• Pulse accumulator queue mode

When queue mode is enabled, reads of an input capture holding register will transfer the contents of the associated pulse accumulator to its holding register.

#### ter 19 Pulse-Width Modulator (S12PWM8B8CV1)

2 registers become the high order bytes of the double byte channel. When channels 0 and 1 are concatenated, channel 0 registers become the high order bytes of the double byte channel.

See Section 19.4.2.7, "PWM 16-Bit Functions" for a more detailed description of the concatenation PWM Function.

#### NOTE

Change these bits only when both corresponding channels are disabled.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CON67 | <ul> <li>Concatenate Channels 6 and 7</li> <li>Channels 6 and 7 are separate 8-bit PWMs.</li> <li>Channels 6 and 7 are concatenated to create one 16-bit PWM channel. Channel 6 becomes the high order byte and channel 7 becomes the low order byte. Channel 7 output pin is used as the output for this 16-bit PWM (bit 7 of port PWMP). Channel 7 clock select control-bit determines the clock source, channel 7 polarity bit determines the polarity, channel 7 enable bit enables the output and channel 7 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 6<br>CON45 | <ul> <li>Concatenate Channels 4 and 5</li> <li>Channels 4 and 5 are separate 8-bit PWMs.</li> <li>Channels 4 and 5 are concatenated to create one 16-bit PWM channel. Channel 4 becomes the high order byte and channel 5 becomes the low order byte. Channel 5 output pin is used as the output for this 16-bit PWM (bit 5 of port PWMP). Channel 5 clock select control-bit determines the clock source, channel 5 polarity bit determines the polarity, channel 5 enable bit enables the output and channel 5 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 5<br>CON23 | <ul> <li>Concatenate Channels 2 and 3</li> <li>Channels 2 and 3 are separate 8-bit PWMs.</li> <li>Channels 2 and 3 are concatenated to create one 16-bit PWM channel. Channel 2 becomes the high order byte and channel 3 becomes the low order byte. Channel 3 output pin is used as the output for this 16-bit PWM (bit 3 of port PWMP). Channel 3 clock select control-bit determines the clock source, channel 3 polarity bit determines the polarity, channel 3 enable bit enables the output and channel 3 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 4<br>CON01 | <ul> <li>Concatenate Channels 0 and 1</li> <li>Channels 0 and 1 are separate 8-bit PWMs.</li> <li>Channels 0 and 1 are concatenated to create one 16-bit PWM channel. Channel 0 becomes the high order byte and channel 1 becomes the low order byte. Channel 1 output pin is used as the output for this 16-bit PWM (bit 1 of port PWMP). Channel 1 clock select control-bit determines the clock source, channel 1 polarity bit determines the polarity, channel 1 enable bit enables the output and channel 1 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 3<br>PSWAI | <ul> <li>PWM Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling the input clock to the prescaler.</li> <li>0 Allow the clock to the prescaler to continue while in wait mode.</li> <li>1 Stop the input clock to the prescaler whenever the MCU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2<br>PFREZ | <ul> <li>PWM Counters Stop in Freeze Mode — In freeze mode, there is an option to disable the input clock to the prescaler by setting the PFRZ bit in the PWMCTL register. If this bit is set, whenever the MCU is in freeze mode, the input clock to the prescaler is disabled. This feature is useful during emulation as it allows the PWM function to be suspended. In this way, the counters of the PWM can be stopped while in freeze mode so that once normal program flow is continued, the counters are re-enabled to simulate real-time operations. Since the registers can still be accessed in this mode, to re-enable the prescaler clock, either disable the PFRZ bit or exit freeze mode.</li> <li>O Allow PWM to continue while in freeze mode.</li> <li>I Disable PWM input clock to the prescaler whenever the part is in freeze mode. This is useful for emulation.</li> </ul> |

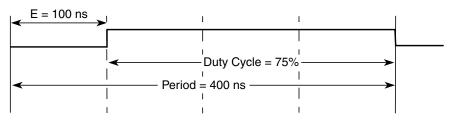

Figure 19-21. PWM Left Aligned Output Example Waveform

## 19.4.2.6 Center Aligned Outputs

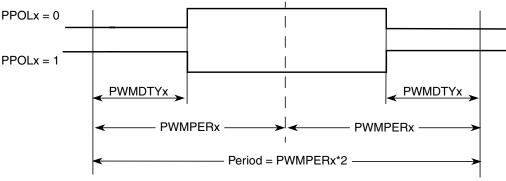

For center aligned output mode selection, set the CAEx bit (CAEx = 1) in the PWMCAE register and the corresponding PWM output will be center aligned.

The 8-bit counter operates as an up/down counter in this mode and is set to up whenever the counter is equal to \$00. The counter compares to two registers, a duty register and a period register as shown in the block diagram in Figure 19-19. When the PWM counter matches the duty register, the output flip-flop changes state, causing the PWM waveform to also change state. A match between the PWM counter and the period register changes the counter direction from an up-count to a down-count. When the PWM counter decrements and matches the duty register again, the output flip-flop changes state causing the PWM output to also change state. When the PWM counter decrements and reaches zero, the counter direction changes from a down-count back to an up-count and a load from the double buffer period and duty registers to the associated registers is performed, as described in Section 19.4.2.3, "PWM Period and Duty". The counter counts from 0 up to the value in the period register and then back down to 0. Thus the effective period is PWMPERx\*2.

#### NOTE

Changing the PWM output mode from left aligned to center aligned output (or vice versa) while channels are operating can cause irregularities in the PWM output. It is recommended to program the output mode before enabling the PWM channel.

Figure 19-22. PWM Center Aligned Output Waveform

#### Table 22-6. TSCR1 Field Descriptions (continued)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>TFFCA | <ul> <li>Timer Fast Flag Clear All</li> <li>Allows the timer flag clearing to function normally.</li> <li>For TFLG1(0x000E), a read from an input capture or a write to the output compare channel (0x0010–0x001F) causes the corresponding channel flag, CnF, to be cleared. For TFLG2 (0x000F), any access to the TCNT register (0x0004, 0x0005) clears the TOF flag. Any access to the PACNT registers (0x0022, 0x0023) clears the PAOVF and PAIF flags in the PAFLG register (0x0021). This has the advantage of eliminating software overhead in a separate clear sequence. Extra care is required to avoid accidental flag clearing due to unintended accesses.</li> </ul> |

| 3<br>PRNT  | <ul> <li>Precision Timer</li> <li>0 Enables legacy timer. PR0, PR1, and PR2 bits of the TSCR2 register are used for timer counter prescaler selection.</li> <li>1 Enables precision timer. All bits of the PTPSR register are used for Precision Timer Prescaler Selection, and all bits.</li> <li>This bit is writable only once out of reset.</li> </ul>                                                                                                                                                                                                                                                                                                                       |

## 22.3.2.7 Timer Toggle On Overflow Register 1 (TTOV)

Module Base + 0x0007

|        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| R<br>W | TOV7 | TOV6 | TOV5 | TOV4 | TOV3 | TOV2 | TOV1 | TOV0 |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Figure 22-13. Timer Toggle On Overflow Register 1 (TTOV)

Read: Anytime

Write: Anytime

#### Table 22-7. TTOV Field Descriptions

| Field    | Description                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------|

| 7:0      | Toggle On Overflow Bits — TOVx toggles output compare pin on overflow. This feature only takes effect when          |

| TOV[7:0] | in output compare mode. When set, it takes precedence over forced output compare but not channel 7 override events. |

|          | 0 Toggle output compare pin on overflow feature disabled.                                                           |

|          | 1 Toggle output compare pin on overflow feature enabled.                                                            |

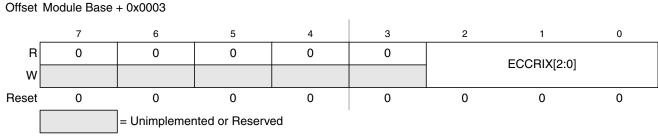

#### Table 26-14. FECCRIX Field Descriptions

| Field | Description                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>ECC Error Register Index</b> — The ECCRIX bits are used to select which word of the FECCR register array is being read. See Section 26.3.2.13, "Flash ECC Error Results Register (FECCR)," for more details. |

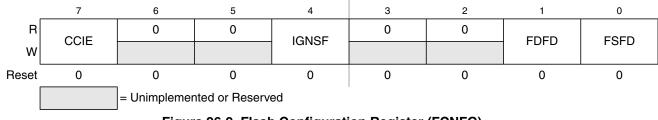

## 26.3.2.5 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU or XGATE.

Offset Module Base + 0x0004

Figure 26-9. Flash Configuration Register (FCNFG)

CCIE, IGNSF, FDFD, and FSFD bits are readable and writable while remaining bits read 0 and are not writable.

| Table 26-15. | FCNFG Field | Descriptions |

|--------------|-------------|--------------|

|--------------|-------------|--------------|

| Field      | Description                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIE  | <ul> <li>Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.</li> <li>0 Command complete interrupt disabled</li> <li>1 An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 26.3.2.7)</li> </ul>                                               |

| 4<br>IGNSF | <ul> <li>Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 26.3.2.8).</li> <li>0 All single bit faults detected during array reads are reported</li> <li>1 Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated</li> </ul> |

| Status of Security     |

|------------------------|

| SECURED                |

| SECURED <sup>(1)</sup> |

| UNSECURED              |

| SECURED                |

|                        |

#### Table 28-12. Flash Security States

1. Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 28.5.

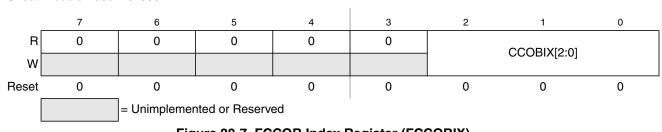

## 28.3.2.3 Flash CCOB Index Register (FCCOBIX)

Offset Module Base + 0x0002

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Figure 28-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

Table 28-13. FCCOBIX Field Descriptions

| Field       | Description                                                                                                                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See Section 28.3.2.11, "Flash Common Command Object Register (FCCOB)," for more details. |

## 28.3.2.4 Flash ECCR Index Register (FECCRIX)

The FECCRIX register is used to index the FECCR register for ECC fault reporting.

#### Figure 28-8. FECCR Index Register (FECCRIX)

ECCRIX bits are readable and writable while remaining bits read 0 and are not writable.

ter 28 768 KByte Flash Module (S12XFTM768K4V2)

| Global Address<br>(EEEIFRON) | Size<br>(Bytes) | Description                                                                                       |

|------------------------------|-----------------|---------------------------------------------------------------------------------------------------|

| 0x12_0000 - 0x12_0001        | 2               | D-Flash User Partition (DFPART)<br>Refer to Section 29.4.2.15, "Full Partition D-Flash Command"   |

| 0x12_0002 - 0x12_0003        | 2               | D-Flash User Partition (duplicate <sup>(1)</sup> )                                                |

| 0x12_0004 - 0x12_0005        | 2               | Buffer RAM EEE Partition (ERPART)<br>Refer to Section 29.4.2.15, "Full Partition D-Flash Command" |

| 0x12_0006 - 0x12_0007        | 2               | Buffer RAM EEE Partition (duplicate <sup>1</sup> )                                                |

| 0x12 0008-0x12 007F          | 120             | Reserved                                                                                          |

Table 29-7. EEE Nonvolatile Information Register Fields

1. Duplicate value used if primary value generates a double bit fault when read during the reset sequence.

#### 29.3.2 **Register Descriptions**

The Flash module contains a set of 20 control and status registers located between Flash module base + 0x0000 and 0x0013. A summary of the Flash module registers is given in Figure 29-4 with detailed descriptions in the following subsections.

#### CAUTION

Writes to any Flash register must be avoided while a Flash command is active (CCIF=0) to prevent corruption of Flash register contents and Memory Controller behavior.

| Address<br>& Name |        | 7       | 6       | 5     | 4        | 3       | 2       | 1       | 0       |

|-------------------|--------|---------|---------|-------|----------|---------|---------|---------|---------|

| 0x0000<br>FCLKDIV | R<br>W | FDIVLD  | FDIV6   | FDIV5 | FDIV4    | FDIV3   | FDIV2   | FDIV1   | FDIV0   |

| 0x0001<br>FSEC    | R<br>W | KEYEN1  | KEYEN0  | RNV5  | RNV4     | RNV3    | RNV2    | SEC1    | SEC0    |

| 0x0002<br>FCCOBIX | R<br>W | 0       | 0       | 0     | 0        | 0       | CCOBIX2 | CCOBIX1 | CCOBIX0 |

| 0x0003<br>FECCRIX | R<br>W | 0       | 0       | 0     | 0        | 0       | ECCRIX2 | ECCRIX1 | ECCRIX0 |

| 0x0004<br>FCNFG   | R<br>W | CCIE    | 0       | 0     | IGNSF    | 0       | 0       | FDFD    | FSFD    |

| 0x0005<br>FERCNFG | R<br>W | ERSERIE | PGMERIE | 0     | EPVIOLIE | ERSVIE1 | ERSVIE0 | DFDIE   | SFDIE   |

#### Figure 29-4. FTM1024K5 Register Summary

## 0x02F0–0x02F7 Voltage Regulator (VREG\_3V3) Map

| Address     | Name       |          | Bit 7  | Bit 6  | Bit 5  | Bit 4    | Bit 3  | Bit 2  | Bit 1 | Bit 0 |     |      |      |      |      |

|-------------|------------|----------|--------|--------|--------|----------|--------|--------|-------|-------|-----|------|------|------|------|

| 0x02F0 VREG | VREGHTCL   | VRECHTCI | VECUTO | VECUTO | VECUTO | VRECHTCI | R      | 0      | 0     | VSEL  | VAE | HTEN | HTDS | HTIE | HTIF |

| 07021 0     | VILLOITIOL | W        |        |        | VOLL   | VAL      |        |        |       |       |     |      |      |      |      |

| 0x02F1      | VREGCTRL   | R        | 0      | 0      | 0      | 0        | 0      | LVDS   | LVIE  | LVIF  |     |      |      |      |      |

|             | VILLOOTTLE | W        |        |        |        |          |        |        |       |       |     |      |      |      |      |

| 0x02F2      | VREGAPICL  | R        | APICLK | 0      | 0      | APIFES   | APIEA  | APIFE  | APIE  | APIF  |     |      |      |      |      |

| ONOL! L     |            | W        | / 1021 |        |        | /        | /      | /      |       |       |     |      |      |      |      |

| 0x02F3      | VREGAPITR  | R        | APITR5 | APITR4 | APITR3 | APITR2   | APITR1 | APITR0 | 0     | 0     |     |      |      |      |      |

|             | -          | W        |        |        |        |          |        |        |       |       |     |      |      |      |      |

| 0x02F4      | VREGAPIRH  | R        | APIR15 | APIR14 | APIR13 | APIR12   | APIR11 | APIR10 | APIR9 | APIR8 |     |      |      |      |      |

|             |            | W        |        |        |        |          |        |        |       |       |     |      |      |      |      |

| 0x02F5      | VREGAPIRL  | R        | APIR7  | APIR6  | APIR5  | APIR4    | APIR3  | APIR2  | APIR1 | APIR0 |     |      |      |      |      |

|             |            | W        |        |        |        |          |        |        |       |       |     |      |      |      |      |

| 0x02F6      | Reserved   | Reserved | R      | 0      | 0      | 0        | 0      | 0      | 0     | 0     | 0   |      |      |      |      |

|             |            | W        |        |        |        |          |        |        |       |       |     |      |      |      |      |

| 0x02F7      | VREGHTTR   | R        | HTOEN  | 0      | 0      | 0        | HTTR3  | HTTR2  | HTTR1 | HTTR0 |     |      |      |      |      |

|             |            | W        |        |        |        |          |        |        |       |       |     |      |      |      |      |

## 0x02F8–0x02FF Reserved

| Address | Name |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x02F8- |      | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x02FF  |      | w |       |       |       |       |       |       |       |       |

### 0x0300–0x0327 Pulse Width Modulator 8-Bit 8-Channel (PWM) Map (Sheet 1 of 3)

| Address | Name      |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0300  | PWME      | R<br>W | PWME7 | PWME6 | PWME5 | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |

| 0x0301  | PWMPOL    | R<br>W | PPOL7 | PPOL6 | PPOL5 | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |

| 0x0302  | PWMCLK    | R<br>W | PCLK7 | PCLK6 | PCLK5 | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |

| 0x0303  | PWMPRCLK  | R<br>W | 0     | PCKB2 | PCKB1 | PCKB0 | 0     | PCKA2 | PCKA1 | PCKA0 |

| 0x0304  | PWMCAE    | R<br>W | CAE7  | CAE6  | CAE5  | CAE4  | CAE3  | CAE2  | CAE1  | CAE0  |

| 0x0305  | PWMCTL    | R<br>W | CON67 | CON45 | CON23 | CON01 | PSWAI | PFRZ  | 0     | 0     |

| 0x0306  | PWMTST    | R      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0300  | Test Only | W      |       |       |       |       |       |       |       |       |

| 0x0307  | PWMPRSC   | R      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0,0007  |           | W      |       |       |       |       |       |       |       |       |

| 0x0308  | PWMSCLA   | R<br>W | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0309  | PWMSCLB   | R<br>W | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |