Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HCS12X                                                       |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 50MHz                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI            |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 119                                                          |

| Program Memory Size        | 384KB (384K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 4K x 8                                                       |

| RAM Size                   | 24K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                 |

| Data Converters            | A/D 24x12b                                                   |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 144-LQFP                                                     |

| Supplier Device Package    | 144-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12xeq384cag |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.7 ADC0 Configuration

# 1.7.1 External Trigger Input Connection

The ADC module includes four external trigger inputs ETRIG0, ETRIG1, ETRIG2, and ETRIG3. The external trigger allows the user to synchronize ADC conversion to external trigger events. Table 1-17 shows the connection of the external trigger inputs.

| External Trigger<br>Input | Connectivity                                |  |  |  |

|---------------------------|---------------------------------------------|--|--|--|

| ETRIG0                    | Pulse width modulator channel 1             |  |  |  |

| ETRIG1                    | Pulse width modulator channel 3             |  |  |  |

| ETRIG2                    | Periodic interrupt timer hardware trigger 0 |  |  |  |

| ETRIG3                    | Periodic interrupt timer hardware trigger 1 |  |  |  |

Table 1-17. ATD0 External Trigger Sources

Consult the ATD block description for information about the analog-to-digital converter module. ATD block description references to freeze mode are equivalent to active BDM mode.

# 1.7.2 ADC0 Channel[17] Connection

Further to the 16 externally available channels, ADC0 features an extra channel[17] that is connected to the internal temperature sensor at device level. To access this channel ADC0 must use the channel encoding SC:CD:CC:CB:CA = 1:0:0:0:1 in ATDCTL5. For more temperature sensor information, please refer to 1.10.1 Temperature Sensor Configuration

# **1.8 ADC1 External Trigger Input Connection**

The ADC module includes four external trigger inputs ETRIG0, ETRIG1, ETRIG2, and ETRIG3. The external trigger feature allows the user to synchronize ADC conversion to external trigger events. Table 1-18 shows the connection of the external trigger inputs.

| External Trigger<br>Input | Connectivity                                |  |  |  |

|---------------------------|---------------------------------------------|--|--|--|

| ETRIG0                    | Pulse width modulator channel 1             |  |  |  |

| ETRIG1                    | Pulse width modulator channel 3             |  |  |  |

| ETRIG2                    | Periodic interrupt timer hardware trigger 0 |  |  |  |

| ETRIG3                    | Periodic interrupt timer hardware trigger 1 |  |  |  |

Consult the ADC block description for information about the analog-to-digital converter module. ADC block description references to freeze mode are equivalent to active BDM mode.

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>DDRB | Port B Data Direction—<br>This register controls the data direction of pins 7 through 0.<br>The external bus function forces the I/O state to be outputs for all associated pins. In this case the data direction bits<br>will not change.<br>When operating a pin as a general purpose I/O, the associated data direction bit determines whether it is an input<br>or output.<br>1 Associated pin is configured as output.<br>0 Associated pin is configured as high-impedance input. |

#### Table 2-7. DDRB Register Field Descriptions

#### 2.3.7 Port C Data Register (PORTC)

Address 0x0004 (PRR)

Access: User read/write<sup>(1)</sup>

| _                   | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|---------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| R<br>W              | PC7    | PC6    | PC5    | PC4    | PC3    | PC2    | PC1   | PC0   |

| Altern.<br>Function | DATA15 | DATA14 | DATA13 | DATA12 | DATA11 | DATA10 | DATA9 | DATA8 |

| Reset               | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

Figure 2-5. Port C Data Register (PORTC) 1. Read: Anytime. In emulation modes, read operations will return the data from the external bus, in all other modes the data source is depending on the data direction value.

Write: Anytime. In emulation modes, write operations will also be directed to the external bus.

#### **Table 2-8. PORTC Register Field Descriptions**

| Field | Description                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0   | Port C general purpose input/output data—Data Register                                                                                                                                                                                                                                                                                                                      |

| PC    | Port C pins 7 through 0 are associated with data I/O lines DATA[15:8] respectively in expanded modes.<br>When not used with the alternative function, these pins can be used as general purpose I/O.<br>If the associated data direction bits of these pins are set to 1, a read returns the value of the port register, otherwise<br>the buffered pin input state is read. |

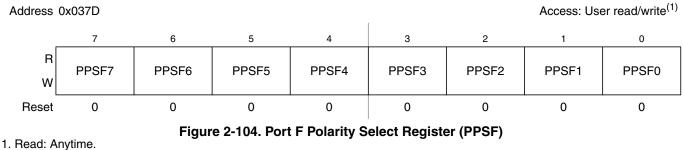

# 2.3.106 Port F Polarity Select Register (PPSF)

Write: Anytime.

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PPSF | <ul> <li>Port F pull device select—Determine pull device polarity on input pins</li> <li>This register selects whether a pull-down or a pull-up device is connected to the pin.</li> <li>1 A pull-down device is connected to the associated pin, if enabled and if the pin is used as input.</li> <li>0 A pull-up device is connected to the associated pin, if enabled and if the pin is used as input.</li> </ul> |

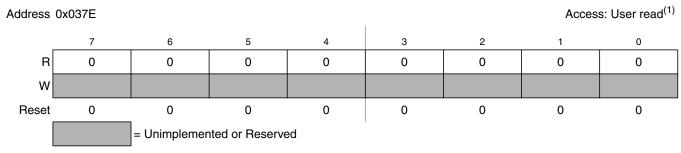

# 2.3.107 PIM Reserved Register

Figure 2-105. PIM Reserved Register

1. Read: Always reads 0x00 Write: Unimplemented

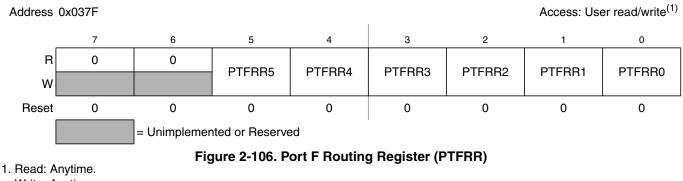

# 2.3.108 Port F Routing Register (PTFRR)

Write: Anytime.

#### **CPU12X Information Byte**

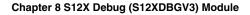

Figure 8-25. CPU12X Information Byte CINF

#### Table 8-45. CINF Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CSD | <ul> <li>Source Destination Indicator — This bit indicates if the corresponding stored address is a source or destination address. This is only used in Normal and Loop1 mode tracing.</li> <li>0 Source address</li> <li>1 Destination address</li> </ul>                                                                                                                                      |

| 6<br>CVA | Vector Indicator — This bit indicates if the corresponding stored address is a vector address. Vector addresses are destination addresses, thus if CVA is set, then the corresponding CSD is also set. This is only used in Normal and Loop1 mode tracing. This bit has no meaning in Pure PC mode.         0       Indexed jump destination address         1       Vector destination address |

| 4<br>CDV | Data Invalid Indicator — This bit indicates if the trace buffer entry is invalid. It is only used when tracing from<br>both sources in Normal, Loop1 and Pure PC modes, to indicate that the CPU12X trace buffer entry is valid.0Trace buffer entry is invalid<br>11Trace buffer entry is valid                                                                                                 |

#### **CXINF Information Byte**

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CFREE | CSZ   | CRW   | COCF  | XACK  | XSZ   | XRW   | XOCF  |

#### Figure 8-26. Information Byte CXINF

This describes the format of the information byte used only when tracing in Detail Mode. When tracing from the CPU12X in Detail Mode, information is stored to the trace buffer on all cycles except opcode fetch and free cycles. The XGATE entry stored on the same line is a snapshot of the XGATE program counter. In this case the CSZ and CRW bits indicate the type of access being made by the CPU12X, whilst the XACK and XOCF bits indicate if the simultaneous XGATE cycle is a free cycle (no bus acknowledge) or opcode fetch cycle. Similarly when tracing from the XGATE in Detail Mode, information is stored to the trace buffer on all cycles except opcode fetch and free cycles. The CPU12X entry stored on the same line is a snapshot of the CPU12X program counter. In this case the XSZ and XRW bits indicate the type of access being made by the XGATE, whilst the CFREE and COCF bits indicate if the simultaneous CPU12X cycle is a free cycle or opcode fetch cycle.

#### Table 8-46. CXINF Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CFREE | <ul> <li>CPU12X Free Cycle Indicator — This bit indicates if the stored CPU12X address corresponds to a free cycle.</li> <li>This bit only contains valid information when tracing the XGATE accesses in Detail Mode.</li> <li>O Stored information corresponds to free cycle</li> <li>1 Stored information does not correspond to free cycle</li> </ul> |

| Field               | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–8<br>XGSWTM[7:0] | Software Trigger Mask — These bits control the write access to the XGSWT bits. Each XGSWT bit can only be written if a "1" is written to the corresponding XGSWTM bit in the same access.<br>Read:<br>These bits will always read "0".<br>Write:<br>0 Disable write access to the XGSWT in the same bus cycle<br>1 Enable write access to the corresponding XGSWT bit in the same bus cycle |

| 7–0<br>XGSWT[7:0]   | <ul> <li>Software Trigger Bits — These bits act as interrupt flags that are able to trigger XGATE software channels. They can only be set and cleared by software. Read:</li> <li>0 No software trigger pending</li> <li>1 Software trigger pending if the XGIE bit is set</li> <li>Write:</li> <li>0 Clear Software Trigger</li> <li>1 Set Software Trigger</li> </ul>                     |

#### Table 10-11. XGSWT Field Descriptions

#### NOTE

The XGATE channel IDs that are associated with the eight software triggers are determined on chip integration level. (see Section "Interrupts" of the **device overview**)

XGATE software triggers work like any peripheral interrupt. They can be used as XGATE requests as well as S12X\_CPU interrupts. The target of the software trigger must be selected in the S12X\_INT module.

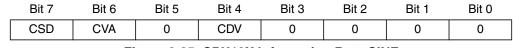

# 10.3.1.10 XGATE Semaphore Register (XGSEM)

The XGATE provides a set of eight hardware semaphores that can be shared between the S12X\_CPU and the XGATE RISC core. Each semaphore can either be unlocked, locked by the S12X\_CPU or locked by the RISC core. The RISC core is able to lock and unlock a semaphore through its SSEM and CSEM instructions. The S12X\_CPU has access to the semaphores through the XGATE Semaphore Register (Figure 10-12). Refer to section Section 10.4.4, "Semaphores" for details.

Module Base +0x0001A

Read: Anytime

Write: Anytime (see Section 10.4.4, "Semaphores")

| DLY7 | DLY6 | DLY5 | DLY4 | DLY3 | DLY2 | DLY1 | DLY0 | Delay                 |

|------|------|------|------|------|------|------|------|-----------------------|

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 32 bus clock cycles   |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 64 bus clock cycles   |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 128 bus clock cycles  |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 256 bus clock cycles  |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 512 bus clock cycles  |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1024 bus clock cycles |

Table 14-29. Delay Counter Select Examples when PRNT = 1

# 14.3.2.23 Input Control Overwrite Register (ICOVW)

Module Base + 0x002A

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | NOVW7 | NOVW6 | NOVW5 | NOVW4 | NOVW3 | NOVW2 | NOVW1 | NOVW0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 14-46. Input Control Overwrite Register (ICOVW)

Read: Anytime

Write: Anytime

All bits reset to zero.

| Table 14-30. ICOVW Field Descriptions | Table 14-30. | ICOVW | Field | Descriptions |

|---------------------------------------|--------------|-------|-------|--------------|

|---------------------------------------|--------------|-------|-------|--------------|

| Field     | Description                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0       | No Input Capture Overwrite                                                                                                                                                                                                                                |

| NOVW[7:0] | 0 The contents of the related capture register or holding register can be overwritten when a new input capture or latch occurs.                                                                                                                           |

|           | 1 The related capture register or holding register cannot be written by an event unless they are empty (see Section 14.4.1.1, "IC Channels"). This will prevent the captured value being overwritten until it is read or latched in the holding register. |

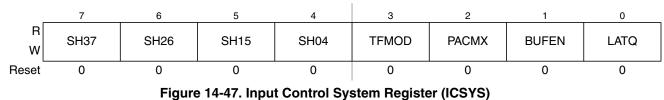

# 14.3.2.24 Input Control System Control Register (ICSYS)

Module Base + 0x002B

Read: Anytime

Write: Once in normal modes

| PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 | Prescale<br>Factor |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 2                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 3                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 4                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 5                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 6                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 7                  |

| 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 8                  |

| 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 16                 |

| 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 32                 |

| 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 64                 |

| 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 128                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 256                |

Table 14-34. Precision Timer Prescaler Selection Examples when PRNT = 1

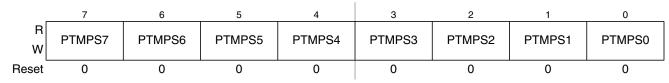

# 14.3.2.27 Precision Timer Modulus Counter Prescaler Select Register (PTMCPSR)

Module Base + 0x002F

#### Figure 14-50. Precision Timer Modulus Counter Prescaler Select Register (PTMCPSR)

Read: Anytime

#### Write: Anytime

All bits reset to zero.

#### Table 14-35. PTMCPSR Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTMPS[7:0] | <b>Precision Timer Modulus Counter Prescaler Select Bits</b> — These eight bits specify the division rate of the modulus counter prescaler. These are effective only when the PRNT bit of TSCR1 is set to 1. Table 14-36 shows some possible division rates. |

|                   | The newly selected prescaler division rate will not be effective until a load of the load register into the modulus counter count register occurs.                                                                                                           |

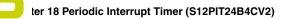

# 18.3.0.3 PIT Channel Enable Register (PITCE)

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PCE[3:0] | <ul> <li>PIT Enable Bits for Timer Channel 3:0 — These bits enable the PIT channels 3-0. If PCE is cleared, the PIT channel is disabled and the corresponding flag bit in the PITTF register is cleared. When PCE is set, and if the PIT module is enabled (PITE = 1) the 16-bit timer counter is loaded with the start count value and starts down-counting.</li> <li>0 The corresponding PIT channel is disabled.</li> <li>1 The corresponding PIT channel is enabled.</li> </ul> |

## 20.4.6.6.1 Idle Input line Wakeup (WAKE = 0)

In this wakeup method, an idle condition on the RXD pin clears the RWU bit and wakes up the SCI. The initial frame or frames of every message contain addressing information. All receivers evaluate the addressing information, and receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another idle character appears on the RXD pin.

Idle line wakeup requires that messages be separated by at least one idle character and that no message contains idle characters.

The idle character that wakes a receiver does not set the receiver idle bit, IDLE, or the receive data register full flag, RDRF.

The idle line type bit, ILT, determines whether the receiver begins counting logic 1s as idle character bits after the start bit or after the stop bit. ILT is in SCI control register 1 (SCICR1).

#### 20.4.6.6.2 Address Mark Wakeup (WAKE = 1)

In this wakeup method, a logic 1 in the most significant bit (MSB) position of a frame clears the RWU bit and wakes up the SCI. The logic 1 in the MSB position marks a frame as an address frame that contains addressing information. All receivers evaluate the addressing information, and the receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another address frame appears on the RXD pin.

The logic 1 MSB of an address frame clears the receiver's RWU bit before the stop bit is received and sets the RDRF flag.

Address mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames.

#### NOTE

With the WAKE bit clear, setting the RWU bit after the RXD pin has been idle can cause the receiver to wake up immediately.

# 20.4.7 Single-Wire Operation

Normally, the SCI uses two pins for transmitting and receiving. In single-wire operation, the RXD pin is disconnected from the SCI. The SCI uses the TXD pin for both receiving and transmitting.

Figure 20-30. Single-Wire Operation (LOOPS = 1, RSRC = 1)

| Field    | Description                                                                                                                                                                                                                                                                 |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>TOF | <b>Timer Overflow Flag</b> — Set when 16-bit free-running timer overflows from 0xFFFF to 0x0000. Clearing this bit requires writing a one to bit 7 of TFLG2 register while the TEN bit of TSCR1 or PAEN bit of PACTL is set to one (See also TCRE control bit explanation.) |  |

#### Table 22-17. TRLG2 Field Descriptions

# 22.3.2.14 Timer Input Capture/Output Compare Registers High and Low 0–7 (TCxH and TCxL)

|        | 0x0010 = TC0<br>0x0012 = TC<br>0x0014 = TC2<br>0x0016 = TC3 | 1H<br>2H | 0x0018 = TC4<br>0x001A = TC4<br>0x001C = TC4<br>0x001C = TC4<br>0x001E = TC4 | 5H<br>6H    |             |             |        |       |

|--------|-------------------------------------------------------------|----------|------------------------------------------------------------------------------|-------------|-------------|-------------|--------|-------|

| _      | 15                                                          | 14       | 13                                                                           | 12          | 11          | 10          | 9      | 0     |

| R<br>W | Bit 15                                                      | Bit 14   | Bit 13                                                                       | Bit 12      | Bit 11      | Bit 10      | Bit 9  | Bit 8 |

| Reset  | 0                                                           | 0        | 0                                                                            | 0           | 0           | 0           | 0      | 0     |

|        | Figure 22-22. Time                                          |          |                                                                              | e/Output Co | ompare Regi | ster x High | (TCxH) |       |

|        | 0x0011 = TC<br>0x0013 = TC<br>0x0015 = TC<br>0x0017 = TC    | 1L<br>2L | 0x0019 = TC4<br>0x001B = TC3<br>0x001D = TC<br>0x001F = TC3                  | 5L<br>6L    |             |             |        |       |

|        | 7                                                           | 6        | 5                                                                            | 4           | 3           | 2           | 1      | 0     |

| R<br>W | Bit 7                                                       | Bit 6    | Bit 5                                                                        | Bit 4       | Bit 3       | Bit 2       | Bit 1  | Bit 0 |

| Reset  | 0                                                           | 0        | 0                                                                            | 0           | 0           | 0           | 0      | 0     |

Figure 22-23. Timer Input Capture/Output Compare Register x Low (TCxL)

Depending on the TIOS bit for the corresponding channel, these registers are used to latch the value of the free-running counter when a defined transition is sensed by the corresponding input capture edge detector or to trigger an output action for output compare.

Read: Anytime

Write: Anytime for output compare function. Writes to these registers have no meaning or effect during input capture. All timer input capture/output compare registers are reset to 0x0000.

#### NOTE

Read/Write access in byte mode for high byte should takes place before low byte otherwise it will give a different result.

# 25.4.2.11 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and D-Flash memory space and, if the erase is successful, will release security.

| CCOBIX[2:0] | FCCOB P | arameters    |  |  |

|-------------|---------|--------------|--|--|

| 000         | 0x0B    | Not required |  |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and D-Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

|          |           | 5                                                                                   |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|

| Register | Error Bit | Error Condition                                                                     |  |

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                         |  |

|          |           | Set if a Load Data Field command sequence is currently active                       |  |

|          |           | Set if command not available in current mode (see Table 25-30)                      |  |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash memory is protected                                  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |

Table 25-54. Unsecure Flash Command Error Handling

# 25.4.2.12 Verify Backdoor Access Key Command

**EPVIOLIF**

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 25-11). The Verify Backdoor Access Key command releases security if usersupplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 25-3). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

Set if any area of the buffer RAM EEE partition is protected

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0C             | Not required |

| 001         | Key              | / 0          |

| 010         | Key              | / 1          |

| 011         | Key 2            |              |

| 100         | Key              | / 3          |

Table 25-55. Verify Backdoor Access Key Command FCCOB Requirements

FERSTAT

ter 26 384 KByte Flash Module (S12XFTM384K2V1)

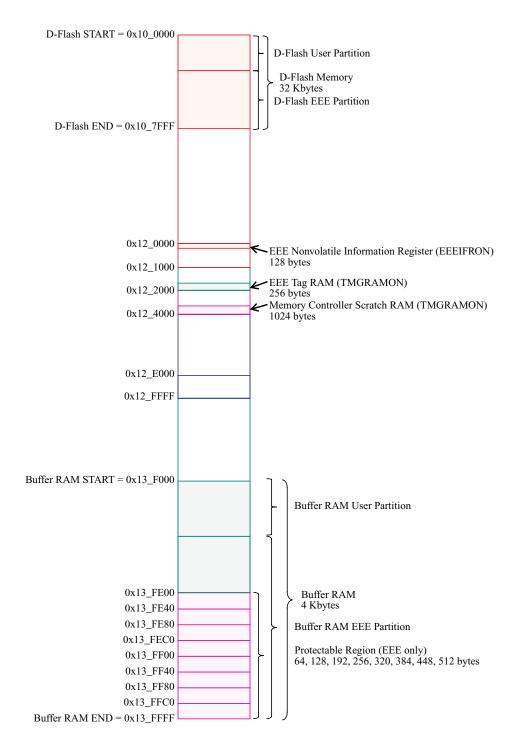

Figure 26-3. EEE Resource Memory Map

The Full Partition D-Flash command (see Section 26.4.2.15) is used to program the EEE nonvolatile information register fields where address  $0x12\_0000$  defines the D-Flash partition for user access and address  $0x12\_0004$  defines the buffer RAM partition for EEE operations.

# Chapter 28 768 KByte Flash Module (S12XFTM768K4V2)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                                                                                                                                                                                                                                         | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V02.09             | 29 Nov 2007      |                                                                                                                                                                                                                                                                                              | - Cleanup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V02.10             | 19 Dec 2007      | 28.4.2/28-1113<br>28.4.2/28-1113<br>28.3.1/28-1082                                                                                                                                                                                                                                           | <ul> <li>Updated Command Error Handling tables based on parent-child relationship<br/>with FTM1024K5</li> <li>Corrected Error Handling table for Full Partition D-Flash, Partition D-Flash,<br/>and EEPROM Emulation Query commands</li> <li>Corrected P-Flash Memory Addressing table</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V02.11             | 25 Sep 2009      | 28.1/28-1077<br>28.3.2.1/28-<br>1089<br>28.4.2.4/28-<br>1116<br>28.4.2.7/28-<br>1119<br>28.4.2.12/28-<br>1123<br>28.4.2.12/28-<br>1123<br>28.4.2.12/28-<br>1123<br>28.4.2.20/28-<br>1132<br>28.3.2/28-1087<br>28.3.2/28-1087<br>28.3.2.1/28-<br>1089<br>28.4.1.2/28-<br>1108<br>28.6/28-1138 | <ul> <li>Clarify single bit fault correction for P-Flash phrase</li> <li>Expand FDIV vs OSCCLK Frequency table</li> <li>Add statement concerning code runaway when executing Read Once command from Flash block containing associated fields</li> <li>Add statement concerning code runaway when executing Program Once command from Flash block containing associated fields</li> <li>Add statement concerning code runaway when executing Verify Backdoor Access Key command from Flash block containing associated fields</li> <li>Relate Key 0 to associated Backdoor Comparison Key address</li> <li>Change "power down reset" to "reset"</li> <li>Add ACCERR condition for Disable EEPROM Emulation command The following changes were made to clarify module behavior related to Flash register access during register writes while command is active</li> <li>Writes to FCLKDIV are allowed during reset sequence while CCIF is clear</li> <li>Add caution concerning register writes while command is active</li> <li>Writes to FCCOBIX, FCCOBHI, FCCOBLO registers are ignored during reset sequence</li> </ul> |

#### Table 28-1. Revision History

# 28.1 Introduction

The FTM768K4 module implements the following:

• 768 Kbytes of P-Flash (Program Flash) memory, consisting of 4 physical Flash blocks, intended primarily for nonvolatile code storage

• Ability to program up to four words in a burst sequence

# 28.1.2.3 Emulated EEPROM Features

- Up to 4 Kbytes of emulated EEPROM (EEE) accessible as 4 Kbytes of RAM

- Flexible protection scheme to prevent accidental program or erase of data

- Automatic EEE file handling using an internal Memory Controller

- Automatic transfer of valid EEE data from D-Flash memory to buffer RAM on reset

- Ability to monitor the number of outstanding EEE related buffer RAM words left to be programmed into D-Flash memory

- Ability to disable EEE operation and allow priority access to the D-Flash memory

- Ability to cancel all pending EEE operations and allow priority access to the D-Flash memory

#### 28.1.2.4 User Buffer RAM Features

• Up to 4 Kbytes of RAM for user access

## 28.1.2.5 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

# 28.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 28-1.

| Register | Error Bit | Error Condition                                                                      |  |

|----------|-----------|--------------------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                          |  |

|          |           | Set if a Load Data Field command sequence is currently active                        |  |

| FSTAT    |           | Set if an invalid global address [22:16] is supplied <sup>(1)</sup>                  |  |

| FSTAI    | FPVIOL    | None                                                                                 |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read <sup>(2)</sup>               |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read <sup>2</sup> |  |

| FERSTAT  | EPVIOLIF  | None                                                                                 |  |

1. As defined by the memory map for FTM1024K5.

2. As found in the memory map for FTM1024K5.

#### 28.4.2.3 **Erase Verify P-Flash Section Command**

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases. The section to be verified cannot cross a 256 Kbyte boundary in the P-Flash memory space.

Table 28-37. Erase Verify P-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |

|-------------|----------------------------------------------------------|----------------------------------------------|

| 000         | 0x03                                                     | Global address [22:16] of<br>a P-Flash block |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |

| 010         | Number of phrases to be verified                         |                                              |

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                                                                                                              |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                                                                                                  |

|          |           | Set if command not available in current mode (see Table 28-30)                                                                                               |

|          |           | Set if an invalid global address [22:0] is supplied <sup>(1)</sup>                                                                                           |

|          |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                                                                                 |

| FSTAT    |           | Set if a Load Data Field command sequence is currently active and the selected block has previously been selected in the same command sequence               |

|          |           | Set if a Load Data Field command sequence is currently active and global address [17:0] does not match that previously supplied in the same command sequence |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                                                                                                  |

|          | MGSTAT1   | None                                                                                                                                                         |

|          | MGSTAT0   | None                                                                                                                                                         |

| FERSTAT  | EPVIOLIF  | None                                                                                                                                                         |

1. As defined by the memory map for FTM1024K5.

# 28.4.2.6 Program P-Flash Command

The Program P-Flash operation will program a previously erased phrase in the P-Flash memory using an embedded algorithm.

#### CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

Table 28-43. Program P-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                         |                                                     |

|-------------|--------------------------------------------------------------------------|-----------------------------------------------------|

| 000         | 0x06                                                                     | Global address [22:16] to<br>identify P-Flash block |

| 001         | Global address [15:0] of phrase location to be programmed <sup>(1)</sup> |                                                     |

| 010         | Word 0 program value                                                     |                                                     |

| 011         | Word 1 program value                                                     |                                                     |

| 100         | Word 2 program value                                                     |                                                     |

| 101         | Word 3 program value                                                     |                                                     |

1. Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

# CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

Table 29-43. Program P-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                         |                                                     |

|-------------|--------------------------------------------------------------------------|-----------------------------------------------------|

| 000         | 0x06                                                                     | Global address [22:16] to<br>identify P-Flash block |

| 001         | Global address [15:0] of phrase location to be programmed <sup>(1)</sup> |                                                     |

| 010         | Word 0 program value                                                     |                                                     |

| 011         | Word 1 program value                                                     |                                                     |

| 100         | Word 2 program value                                                     |                                                     |

| 101         | Word 3 program value                                                     |                                                     |

1. Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

| Register | Error Bit | Error Condition                                                                                                                                              |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 101 at command launch                                                                                                                  |

|          |           | Set if command not available in current mode (see Table 29-30)                                                                                               |

|          |           | Set if an invalid global address [22:0] is supplied                                                                                                          |

|          |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                                                                                 |

|          |           | Set if a Load Data Field command sequence is currently active and the selected block has previously been selected in the same command sequence               |

| FSTAT    |           | Set if a Load Data Field command sequence is currently active and global address [17:0] does not match that previously supplied in the same command sequence |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                                                                                                  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                                                                          |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                                                                          |

| FERSTAT  | EPVIOLIF  | None                                                                                                                                                         |

#### Table 29-44. Program P-Flash Command Error Handling

# 29.4.2.7 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 29.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program

# 29.4.2.20 Disable EEPROM Emulation Command

The Disable EEPROM Emulation command causes the Memory Controller to suspend current EEE activity.

#### Table 29-73. Disable EEPROM Emulation Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x14             | Not required |

Upon clearing CCIF to launch the Disable EEPROM Emulation command, the Memory Controller will halt EEE operations at the next convenient point without clearing the EEE tag RAM or tag counter before setting the CCIF flag.

Table 29-74. Disable EEPROM Emulation Command Error Handling

| Register | Error Bit | Error Condition                                                               |

|----------|-----------|-------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 000 at command launch                                   |

|          | ACCERR    | Set if a Load Data Field command sequence is currently active                 |

| FSTAT    |           | Set if Full Partition D-Flash or Partition D-Flash command not previously run |

| FSTAL    | FPVIOL    | None                                                                          |

|          | MGSTAT1   | None                                                                          |

|          | MGSTAT0   | None                                                                          |

| FERSTAT  | EPVIOLIF  | None                                                                          |

## 29.4.2.21 EEPROM Emulation Query Command

The EEPROM Emulation Query command returns EEE partition and status variables.

Table 29-75. EEPROM Emulation Query Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters         |                           |  |  |  |  |

|-------------|--------------------------|---------------------------|--|--|--|--|

| 000         | 0x15 Not required        |                           |  |  |  |  |

| 001         | Return DFPART            |                           |  |  |  |  |

| 010         | Return ERPART            |                           |  |  |  |  |

| 011         | Return E                 | COUNT <sup>(1)</sup>      |  |  |  |  |

| 100         | Return Dead Sector Count | Return Ready Sector Count |  |  |  |  |

Indicates sector erase count

Upon clearing CCIF to launch the EEPROM Emulation Query command, the CCIF flag will set after the EEE partition and status variables are stored in the FCCOBIX register. If the Emulation Query command is executed prior to partitioning (Partition D-Flash Command Section 29.4.2.15), the following reset values are returned: DFPART =  $0x_FFFF$ , ERPART =  $0x_FFFF$ , ECOUNT =  $0x_FFFF$ , Dead Sector Count =  $0x \ 00$ , Ready Sector Count =  $0x \ 00$ .

#### 0x01C0-0x01FF MSCAN (CAN2) Map (Sheet 3 of 3)

| Address           | Name      |        | Bit 7 | Bit 6                                                              | Bit 5                                                                          | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|-----------|--------|-------|--------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|-------|

| 0x01DF            | CAN2IDMR7 | R<br>W | AM7   | AM6                                                                | AM5                                                                            | AM4   | AM3   | AM2   | AM1   | AM0   |

| 0x01E0–<br>0x01EF | CAN2RXFG  | R      |       | (See Detaile                                                       | FOREGROUND RECEIVE BUFFER<br>See Detailed MSCAN Foreground Receive and Transmi |       |       |       |       |       |

| 0x01F0-           | CAN2TXFG  | W<br>R |       | ( <b>0 D i</b> i i                                                 |                                                                                |       |       |       |       |       |

| 0x01FF            |           | w      |       | (See Detailed MSCAN Foreground Receive and Transmit Buffer Layout) |                                                                                |       |       |       |       |       |

ndix E Detailed Register Address Map

# 0x0380–0x03BF XGATE Map (Sheet 1 of 3)

| Address | Name     |             | Bit 7   | Bit 6       | Bit 5   | Bit 4   | Bit 3       | Bit 2   | Bit 1       | Bit 0    |  |

|---------|----------|-------------|---------|-------------|---------|---------|-------------|---------|-------------|----------|--|

|         |          | R           | 0       | 0           | 0       | 0       | 0           | 0       | 0           |          |  |

| 0x0380  | XGMCTL   | W           | XGEM    | XGFRZM      | XGDBGM  | XGSSM   | XGFACTM     |         | XGS<br>WEFM | XGIEM    |  |

| 0x0381  | XGMCTL   | R<br>W      | XGE     | XGFRZ       | XGDBG   | XGSS    | XGFACT      | 0       | XGSWEF      | XGIE     |  |

| 0x0382  | XGCHID   | R           | 0       |             |         | 2       | XGCHID[6:0] | ]       |             |          |  |

| 0x0383  | XGCHPL   | W<br>R<br>W | 0       | 0           | 0       | 0       | 0           | XGCHPL  | 0           | 0        |  |

| 0x0384  | Reserved |             |         |             |         |         |             |         |             |          |  |

| 0x0385  | XGISPSEL | R<br>W      | 0       | 0           | 0       | 0       | 0           | 0       | XGISPS      | SEL[1:0] |  |

| 0x0386  | XGVBR    | R<br>W      |         | XGVBR[15:8] |         |         |             |         |             |          |  |

| 0x0387  | XGVBR    | R<br>W      |         | XGVBR[7:1]  |         |         |             |         |             |          |  |

| 0x0388  | XGIF     | R<br>W      | 0       | 0           | 0       | 0       | 0           | 0       | 0           | XGIF_78  |  |

| 0x0389  | XGIF     | R<br>W      | XGIF_77 | XGIF_76     | XGIF_75 | XGIF_74 | XGIF_73     | XGIF_72 | XGIF_71     | XGIF_70  |  |

| 0x038A  | XGIF     | R<br>W      | XGIF_6F | XGIF_6E     | XGIF_6D | XGIF_6C | XGIF_6B     | XGIF_6A | XGIF_69     | XGIF_68  |  |

| 0x023B  | XGIF     | R<br>W      | XGIF_67 | XGIF_66     | XGIF_65 | XGIF_64 | XGIF_63     | XGIF_62 | XGIF_61     | XGIF_60  |  |

| 0x023C  | XGIF     | R<br>W      | XGIF_5F | XGIF_5E     | XGIF_5D | XGIF_5C | XGIF_5B     | XGIF_5A | XGIF_59     | XGIF_58  |  |

| 0x038D  | XGIF     | R<br>W      | XGIF_57 | XGIF_56     | XGIF_55 | XGIF_54 | XGIF_53     | XGIF_52 | XGIF_51     | XGIF_50  |  |

| 0x038E  | XGIF     | R<br>W      | XGIF_4F | XGIF_4E     | XGIF_4D | XGIF_4C | XGIF_4B     | XGIF_4A | XGIF_49     | XGIF_48  |  |

| 0x038F  | XGIF     | R<br>W      | XGIF_47 | XGIF_46     | XGIF_45 | XGIF_44 | XGIF_43     | XGIF_42 | XGIF_41     | XGIF_40  |  |

| 0x0390  | XGIF     | R<br>W      | XGIF_3F | XGIF_3E     | XGIF_3D | XGIF_3C | XGIF_3B     | XGIF_3A | XGIF_39     | XGIF_38  |  |

| 0x0391  | XGIF     | R<br>W      | XGIF_37 | XGIF_36     | XGIF_35 | XGIF_34 | XGIF_33     | XGIF_32 | XGIF_31     | XGIF_30  |  |

| 0x0392  | XGIF     | R<br>W      | XGIF_2F | XGIF_2E     | XGIF_2D | XGIF_2C | XGIF_2B     | XGIF_2A | XGIF_29     | XGIF_28  |  |

| 0x0393  | XGIF     | R<br>W      | XGIF_27 | XGIF_26     | XGIF_25 | XGIF_24 | XGIF_23     | XGIF_22 | XGIF_21     | XGIF_20  |  |

| 0x0394  | XGIF     | R<br>W      | XGIF_1F | XGIF_1E     | XGIF_1D | XGIF_1C | XGIF_1B     | XGIF_1A | XGIF_19     | XGIF_18  |  |

| 0x0395  | XGIF     | R<br>W      | XGIF_17 | XGIF_16     | XGIF_15 | XGIF_14 | XGIF_13     | XGIF_12 | XGIF_11     | XGIF_10  |  |