Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2014110                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | HCS12X                                                       |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 50MHz                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI            |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 119                                                          |

| Program Memory Size        | 384KB (384K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 4K x 8                                                       |

| RAM Size                   | 24K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                 |

| Data Converters            | A/D 24x12b                                                   |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 144-LQFP                                                     |

| Supplier Device Package    | 144-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12xeq384vag |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | CANO | <b>CAN1</b> | CAN2 | CAN3 | CAN4 | SCI0 | SCI1 | SCI2 | SC13 | SCI4 | SCI5 | SCI6 | SCI7 | SP10 | SPI1 | SP12 | IIC0 | llC1 | <u>cso</u> | <u>CS1</u> | <u>CS2</u> | <u>CS3</u> | TIM |

|---------|------|-------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------------|------------|------------|------------|-----|

| PS[1:0] |      |             |      |      |      | 0    |      |      |      |      |      |      |      |      |      |      |      |      |            |            |            |            |     |

| PS[3:2] |      |             |      |      |      |      | 0    |      |      |      |      |      |      |      |      |      |      |      |            |            |            |            |     |

| PS[7:4] |      |             |      |      |      |      |      |      |      |      |      |      |      | 0    |      |      |      |      |            |            |            |            |     |

# Table 1-8. Peripheral - Port Routing Options<sup>(1)</sup> (continued)

sible rerouting er software control n, denotes a p

| 208<br>MAPBGA | LQFP<br>144 | LQFP<br>112 | QFP <sup>(1)</sup><br>80 | Pin   | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func. | 5th<br>Func. |

|---------------|-------------|-------------|--------------------------|-------|--------------|--------------|--------------|--------------|

| D4            | 1           | 1           | 1                        | PP3   | KWP3         | PWM3         | SS1          | TIMIOC3      |

| B2            | 2           | 2           | 2                        | PP2   | KWP2         | PWM2         | SCK1         | TIMIOC2      |

| C2            | 3           | 3           | 3                        | PP1   | KWP1         | PWM1         | MOSI1        | TIMIOC1      |

| D3            | 4           | 4           | 4                        | PP0   | KWP0         | PWM0         | MISO1        | TIMIOC0      |

| D2            |             |             |                          | PJ3   | KWJ3         |              |              |              |

| C1            | 5           |             |                          | PJ2   | KWJ2         | CS1          |              |              |

| E4            | 6           |             |                          | PK6   | ADDR22       | ACC2         |              |              |

| E2            | 7           | 5           |                          | РК3   | ADDR19       | IQSTAT3      |              |              |

| E3            | 8           | 6           |                          | PK2   | ADDR18       | IQSTAT2      |              |              |

| D1            | 9           | 7           |                          | PK1   | ADDR17       | IQSTAT1      |              |              |

| E1            | 10          | 8           |                          | PK0   | ADDR16       | IQSTAT0      |              |              |

| VDDX          |             |             |                          | VDDX7 |              |              |              |              |

| VSSX          |             |             |                          | VSSX7 |              |              |              |              |

| F3            | 11          | 9           | 5                        | PT0   | IOC0         |              |              |              |

| F2            |             |             |                          | PR0   | TIMIOC0      |              |              |              |

| G4            | 12          | 10          | 6                        | PT1   | IOC1         |              |              |              |

| F1            |             |             |                          | PR1   | TIMIOC1      |              |              |              |

| G1            | 13          | 11          | 7                        | PT2   | IOC2         |              |              |              |

| G3            |             |             |                          | PR2   | TIMIOC2      |              |              |              |

| G2            | 14          | 12          | 8                        | PT3   | IOC3         |              |              |              |

| H1            |             |             |                          | PR3   | TIMIOC3      |              |              |              |

| H4            | 15          | 13          | 9                        | VDDF  |              |              |              |              |

### Table 1-9. Pin-Out Summary (Sheet 1 of 7)

The ECLKCTL register is used to control the availability of the free-running clocks and the free-running clock divider.

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>NECLK  | <b>No ECLK</b> —Disable ECLK output<br>This bit controls the availability of a free-running clock on the ECLK pin.<br>Clock output is always active in emulation modes and if enabled in all other operating modes.<br>1 ECLK disabled<br>0 ECLK enabled                                                                                                                                                                   |

| 6<br>NCLKX2 | No ECLKX2—Disable ECLKX2 output<br>This bit controls the availability of a free-running clock on the ECLKX2 pin. This clock has a fixed rate of twice the<br>internal Bus Clock.<br>Clock output is always active in emulation modes and if enabled in all other operating modes.<br>1 ECLKX2 disabled<br>0 ECLKX2 enabled                                                                                                 |

| 5<br>DIV16  | Free-running ECLK predivider—Divide by 16<br>This bit enables a divide-by-16 stage on the selected EDIV rate.<br>1 Divider enabled: ECLK rate = EDIV rate divided by 16<br>0 Divider disabled: ECLK rate = EDIV rate                                                                                                                                                                                                       |

| 4-0<br>EDIV | Free-running ECLK Divider—Configure ECLK rate<br>These bits determine the rate of the free-running clock on the ECLK pin. Divider is always disabled in emulation<br>modes and active as programmed in all other operating modes.<br>00000 ECLK rate = Bus Clock rate<br>00001 ECLK rate = Bus Clock rate divided by 2<br>00010 ECLK rate = Bus Clock rate divided by 3,<br>11111 ECLK rate = Bus Clock rate divided by 32 |

### Table 2-16. ECLKCTL Register Field Descriptions

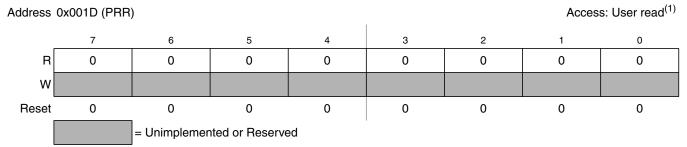

# 2.3.16 PIM Reserved Register

1. Read: Always reads 0x00 Write: Unimplemented

### Figure 2-14. PIM Reserved Register

#### 3.3 **Memory Map and Registers**

#### 3.3.1 **Module Memory Map**

A summary of the registers associated with the MMC block is shown in Figure 3-2. Detailed descriptions of the registers and bits are given in the subsections that follow.

| Address          | Register<br>Name |        | Bit 7       | 6           | 5           | 4           | 3           | 2           | 1           | Bit 0       |

|------------------|------------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0x000A           | MMCCTL0          | R<br>W | CS3E1       | CS3E0       | CS2E1       | CS2E0       | CS1E1       | CS1E0       | CS0E1       | CS0E0       |

| 0x000B           | MODE             | R<br>W | MODC        | MODB        | MODA        | 0           | 0           | 0           | 0           | 0           |

| 0x0010           | GPAGE            | R<br>W | 0           | GP6         | GP5         | GP4         | GP3         | GP2         | GP1         | GP0         |

| 0x0011           | DIRECT           | R<br>W | DP15        | DP14        | DP13        | DP12        | DP11        | DP10        | DP9         | DP8         |

| 0x0012           | Reserved         | R<br>W | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| 0x0013           | MMCCTL1          | R<br>W | TGMRAMON    | 0           | EEEIFRON    | PGMIFRON    | RAMHM       | EROMON      | ROMHM       | ROMON       |

| 0x0014           | Reserved         | R<br>W | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| 0x0015           |                  |        |             |             |             |             |             |             |             |             |

|                  | PPAGE            | R<br>W | PIX7        | PIX6        | PIX5        | PIX4        | PIX3        | PIX2        | PIX1        | PIX0        |

| 0x0016           | PPAGE<br>RPAGE   |        | PIX7<br>RP7 | PIX6<br>RP6 | PIX5<br>RP5 | PIX4<br>RP4 | PIX3<br>RP3 | PIX2<br>RP2 | PIX1<br>RP1 | PIX0<br>RP0 |

| 0x0016<br>0x0017 |                  | W<br>R |             |             |             |             |             |             |             |             |

Figure 3-2. MMC Register Summary

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>EROMON | <ul> <li>Enables emulated Flash or ROM memory in the memory map</li> <li>Write: Never</li> <li>This bit is used in some modes to define the placement of the Emulated Flash or ROM (Refer to Table 3-12)</li> <li>0 Disables the emulated Flash or ROM in the memory map.</li> <li>1 Enables the emulated Flash or ROM in the memory map.</li> </ul>                                                                                                                                                                                                                                                                                                |

| 1<br>ROMHM  | <ul> <li>FLASH or ROM only in higher Half of Memory Map</li> <li>Write: Once in normal and emulation modes and anytime in special modes</li> <li>0 The fixed page of Flash or ROM can be accessed in the lower half of the memory map. Accesses to 0x4000–0x7FFF will be mapped to 0x7F_4000-0x7F_7FFF in the global memory space.</li> <li>1 Disables access to the Flash or ROM in the lower half of the memory map. These physical locations of the Flash or ROM can still be accessed through the program page window. Accesses to 0x4000–0x7FFF will be mapped to 0x14_4000-0x14_7FFF in the global memory space (external access).</li> </ul> |

| 0<br>ROMON  | <ul> <li>Enable FLASH or ROM in the memory map</li> <li>Write: Once in normal and emulation modes and anytime in special modes.</li> <li>This bit is used in some modes to define the placement of the ROM (Refer to Table 3-12)</li> <li>0 Disables the Flash or ROM from the memory map.</li> <li>1 Enables the Flash or ROM in the memory map.</li> </ul>                                                                                                                                                                                                                                                                                        |

EROMON and ROMON control the visibility of the Flash in the memory map for CPU or BDM (not for XGATE). Both local and global memory maps are affected.

| Chip Modes            | ROMON | EROMON | DATA SOURCE <sup>(1)</sup> | Stretch <sup>(2)</sup> |

|-----------------------|-------|--------|----------------------------|------------------------|

| Normal Single Chip    | Х     | Х      | Internal Flash             | N                      |

| Special Single Chip   |       |        |                            |                        |

| Emulation Single Chip | Х     | 0      | Emulation Memory           | N                      |

|                       | Х     | 1      | Internal Flash             |                        |

| Normal Expanded       | 0     | Х      | External Application       | Y                      |

|                       | 1     | Х      | Internal Flash             | N                      |

| Emulation Expanded    | 0     | Х      | External Application       | Y                      |

|                       | 1     | 0      | Emulation Memory           | N                      |

|                       | 1     | 1      | Internal Flash             | -                      |

| Special Test          | 0     | Х      | External Application       | N                      |

|                       | 1     | Х      | Internal Flash             | 1                      |

Table 3-12. Data Sources when CPU or BDM is Accessing Flash Area

1. Internal Flash means Flash resources inside the MCU are read/written.

Emulation memory means resources inside the emulator are read/written (PRU registers, flash replacement, RAM, EEPROM and register space are always considered internal). External application means resources residing outside the MCU are read/written.

2. The external access stretch mechanism is part of the EBI module (refer to EBI Block Guide for details).

### ter 3 Memory Mapping Control (S12XMMCV4)

The fixed 16K page from 0x4000-0x7FFF (when ROMHM = 0) is the page number 0xFD.

The reset value of 0xFE ensures that there is linear Flash space available between addresses 0x4000 and 0xFFFF out of reset.

The fixed 16K page from 0xC000-0xFFFF is the page number 0xFF.

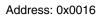

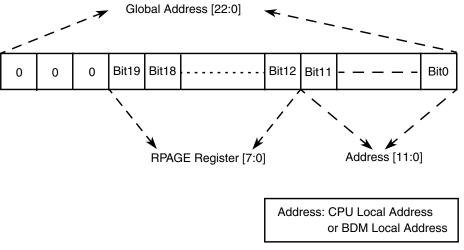

# 3.3.2.7 RAM Page Index Register (RPAGE)

Figure 3-13. RAM Page Index Register (RPAGE)

Read: Anytime

Write: Anytime

These eight index bits are used to page 4 KByte blocks into the RAM page window located in the local (CPU or BDM) memory map from address 0x1000 to address 0x1FFF (see Figure 3-14). This supports accessing up to 1022 KByte of RAM (in the Global map) within the 64 KByte Local map. The RAM page index register is effectively used to construct paged RAM addresses in the Local map format.

## CAUTION

XGATE write access to this register during an CPU access which makes use of this register could lead to unexpected results.

Figure 3-14. RPAGE Address Mapping

# NOTE

Because RAM page 0 has the same global address as the register space, it is possible to write to registers through the RAM space when RPAGE = 0x00.

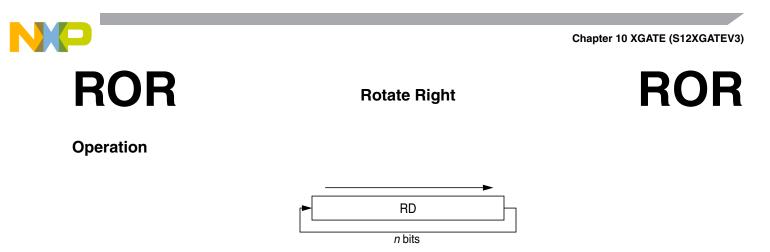

### n = RS or IMM4

Rotates the bits in register RD n positions to the right. The upper n bits of the register RD are filled with the lower n bits. Two source forms are available. In the first form, the parameter n is contained in the instruction code as an immediate operand. In the second form, the parameter is contained in the lower bits of the source register RS[3:0]. All other bits in RS are ignored. If n is zero no shift will take place and the register RD will be unaffected; however, the condition code flags will be updated.

### **CCR Effects**

| Ν | Z | V | С |

|---|---|---|---|

| Δ | Δ | 0 | — |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: 0; cleared.

- C: Not affected.

### **Code and CPU Cycles**

| Source Form   | Address<br>Mode |   | Machine Code |   |   |   |    |      |   |   | Cycles |   |   |   |

|---------------|-----------------|---|--------------|---|---|---|----|------|---|---|--------|---|---|---|

| ROR RD, #IMM4 | IMM4            | 0 | 0            | 0 | 0 | 1 | RD | IMM4 |   | 1 | 1      | 1 | 1 | Р |

| ROR RD, RS    | DYA             | 0 | 0            | 0 | 0 | 1 | RD | RS   | 1 | 0 | 1      | 1 | 1 | Р |

| Register<br>Name      |        | Bit 7  | 6      | 5             | 4      | 3      | 2      | 1     | Bit 0 |

|-----------------------|--------|--------|--------|---------------|--------|--------|--------|-------|-------|

| 0x0000<br>TIOS        | R<br>W | IOS7   | IOS6   | IOS5          | IOS4   | IOS3   | IOS2   | IOS1  | IOS0  |

| 0x0001                | R      | 0      | 0      | 0             | 0      | 0      | 0      | 0     | 0     |

| CFORC                 | w      | FOC7   | FOC6   | FOC5          | FOC4   | FOC3   | FOC2   | FOC1  | FOC0  |

| 0x0002<br>OC7M        | R<br>W | OC7M7  | OC7M6  | OC7M5         | OC7M4  | OC7M3  | OC7M2  | OC7M1 | OC7M0 |

| 0x0003<br>OC7D        | R<br>W | OC7D7  | OC7D6  | OC7D5         | OC7D4  | OC7D3  | OC7D2  | OC7D1 | OC7D0 |

| 0x0004<br>TCNT (High) | R<br>W | TCNT15 | TCNT14 | TCNT13        | TCNT12 | TCNT11 | TCNT10 | TCNT9 | TCNT8 |

| 0x0005<br>TCNT (Low)  | R<br>W | TCNT7  | TCNT6  | TCNT5         | TCNT4  | TCNT3  | TCNT2  | TCNT1 | TCNT0 |

| 0x0006                | R      | TEN    | TOMAL  | TOFDZ         | TEEOA  | DDNT   | 0      | 0     | 0     |

| TSCR1                 | w      | TEN    | TSWAI  | TSFRZ         | TFFCA  | PRNT   |        |       |       |

| 0x0007<br>TTOF        | R<br>W | TOV7   | TOV6   | TOV5          | TOV4   | TOV3   | TOV2   | TOV1  | TOV0  |

| 0x0008<br>TCTL1       | R<br>W | OM7    | OL7    | OM6           | OL6    | OM5    | OL5    | OM4   | OL4   |

| 0x0009<br>TCTL2       | R<br>W | OM3    | OL3    | OM2           | OL2    | OM1    | OL1    | OM0   | OL0   |

| 0x000A<br>TCTL3       | R<br>W | EDG7B  | EDG7A  | EDG6B         | EDG6A  | EDG5B  | EDG5A  | EDG4B | EDG4A |

| 0x000B<br>TCTL4       | R<br>W | EDG3B  | EDG3A  | EDG2B         | EDG2A  | EDG1B  | EDG1A  | EDG0B | EDG0A |

| 0x000C<br>TIE         | R<br>W | C7I    | C6I    | C5I           | C4I    | C3I    | C2I    | C1I   | COI   |

|                       | ſ      |        |        | ented or Rese | rved   |        |        |       |       |

= Unimplemented or Reserved

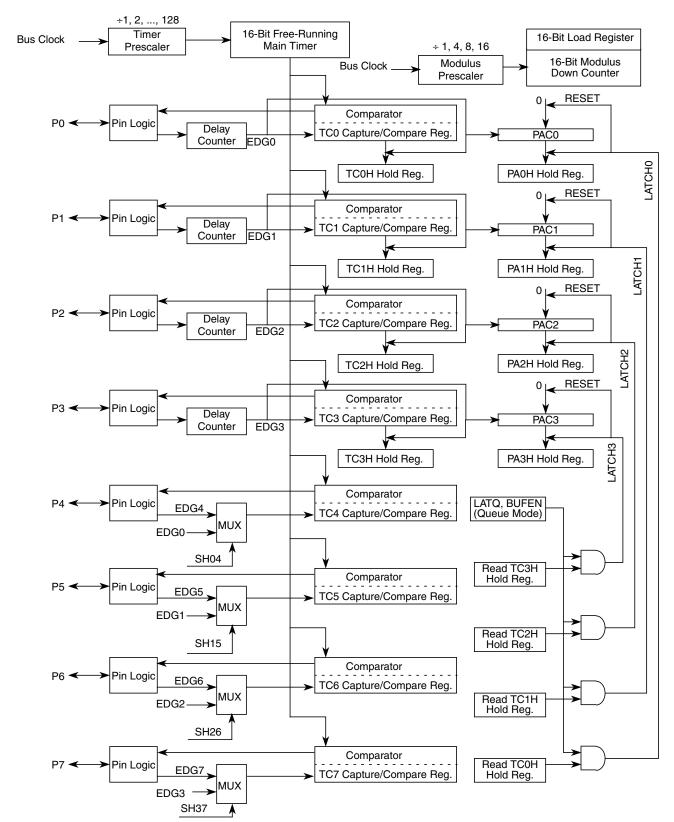

Figure 14-2. ECT Register Summary (Sheet 1 of 5)

MC9S12XE-Family Reference Manual Rev. 1.25

| Register<br>Name | Bit 7 | 6             | 5             | 4    | 3    | 2    | 1   | Bit 0 |

|------------------|-------|---------------|---------------|------|------|------|-----|-------|

| 0x003A R         | TC15  | TC14          | TC13          | TC12 | TC11 | TC10 | TC9 | TC8   |

| TC1H (High) W    |       |               |               |      |      |      |     |       |

| 0x003B R         | TC7   | TC6           | TC5           | TC4  | TC3  | TC2  | TC1 | TC0   |

| TC1H (Low) W     |       |               |               |      |      |      |     |       |

| 0x003C R         | TC15  | TC14          | TC13          | TC12 | TC11 | TC10 | TC9 | TC8   |

| TC2H (High) W    |       |               |               |      |      |      |     |       |

| 0x003D R         | TC7   | TC6           | TC5           | TC4  | TC3  | TC2  | TC1 | TC0   |

| TC2H (Low) W     |       |               |               |      |      |      |     |       |

| 0x003E R         | TC15  | TC14          | TC13          | TC12 | TC11 | TC10 | TC9 | TC8   |

| TC3H (High) W    |       |               |               |      |      |      |     |       |

| 0x003F R         | TC7   | TC6           | TC5           | TC4  | TC3  | TC2  | TC1 | TC0   |

| TC3H (Low) W     |       |               |               |      |      |      |     |       |

| [                |       | ] = Unimpleme | ented or Rese | rved |      |      |     |       |

Figure 14-2. ECT Register Summary (Sheet 5 of 5)

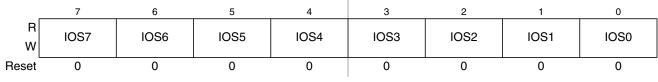

## 14.3.2.1 Timer Input Capture/Output Compare Select Register (TIOS)

Module Base + 0x0000

Figure 14-3. Timer Input Capture/Output Compare Register (TIOS)

Read or write: Anytime

All bits reset to zero.

### Table 14-2. TIOS Field Descriptions

| Field    | Description                                                                                                                           |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0      | nput Capture or Output Compare Channel Configuration                                                                                  |  |  |  |

| IOS[7:0] | <ul> <li>The corresponding channel acts as an input capture.</li> <li>The corresponding channel acts as an output compare.</li> </ul> |  |  |  |

If it were the case that the IBSWAI bit was cleared when the WAI instruction was executed, the IIC internal clocks and interface would remain alive, continuing the operation which was currently underway. It is also possible to configure the IIC such that it will wake up the CPU via an interrupt at the conclusion of the current operation. See the discussion on the IBIF and IBIE bits in the IBSR and IBCR, respectively.

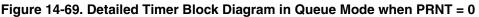

# 15.3.1.4 IIC Status Register (IBSR)

This status register is read-only with exception of bit 1 (IBIF) and bit 4 (IBAL), which are software clearable.

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>TCF      | <ul> <li>Data Transferring Bit — While one byte of data is being transferred, this bit is cleared. It is set by the falling edge of the 9th clock of a byte transfer. Note that this bit is only valid during or immediately following a transfer to the IIC module or from the IIC module.</li> <li>0 Transfer in progress</li> <li>1 Transfer complete</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 6<br>IAAS     | Addressed as a Slave Bit — When its own specific address (I-bus address register) is matched with the calling address or it receives the general call address with GCEN== 1,this bit is set. The CPU is interrupted provided the IBIE is set. Then the CPU needs to check the SRW bit and set its $Tx/Rx$ mode accordingly. Writing to the I-bus control register clears this bit.<br>0 Not addressed<br>1 Addressed as a slave                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 5<br>IBB      | <ul> <li>Bus Busy Bit</li> <li>0 This bit indicates the status of the bus. When a START signal is detected, the IBB is set. If a STOP signal is detected, IBB is cleared and the bus enters idle state.</li> <li>1 Bus is busy</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 4<br>IBAL     | <ul> <li>Arbitration Lost — The arbitration lost bit (IBAL) is set by hardware when the arbitration procedure is lost. Arbitration is lost in the following circumstances: <ol> <li>SDA sampled low when the master drives a high during an address or data transmit cycle.</li> <li>SDA sampled low when the master drives a high during the acknowledge bit of a data receive cycle.</li> <li>A start cycle is attempted when the bus is busy.</li> <li>A repeated start cycle is requested in slave mode.</li> <li>A stop condition is detected when the master did not request it.</li> </ol> </li> <li>This bit must be cleared by software, by writing a one to it. A write of 0 has no effect on this bit.</li> </ul> |  |  |  |  |

| 3<br>RESERVED | <b>Reserved</b> — Bit 3 of IBSR is reserved for future use. A read operation on this bit will return 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

### Table 15-9. IBSR Field Descriptions

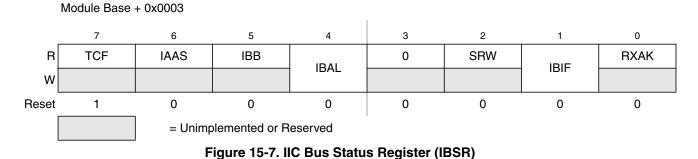

# 16.1.1 Glossary

| ACK              | Acknowledge of CAN message            |  |  |

|------------------|---------------------------------------|--|--|

| CAN              | Controller Area Network               |  |  |

| CRC              | Cyclic Redundancy Code                |  |  |

| EOF              | End of Frame                          |  |  |

| FIFO             | First-In-First-Out Memory             |  |  |

| IFS              | Inter-Frame Sequence                  |  |  |

| SOF              | Start of Frame                        |  |  |

| CPU bus          | CPU related read/write data bus       |  |  |

| CAN bus          | CAN protocol related serial bus       |  |  |

| oscillator clock | Direct clock from external oscillator |  |  |

| bus clock        | CPU bus related clock                 |  |  |

| CAN clock        | CAN protocol related clock            |  |  |

#### Table 16-2. Terminology

# 16.1.2 Block Diagram

Figure 16-1. MSCAN Block Diagram

### Table 20-4. SCICR1 Field Descriptions (continued)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2<br>ILT | Idle Line Type Bit — ILT determines when the receiver starts counting logic 1s as idle character bits. The counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of logic 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the stop bit avoids false idle character recognition, but requires properly synchronized transmissions.         0       Idle character bit count begins after start bit         1       Idle character bit count begins after stop bit |  |  |  |  |

| 1<br>PE  | <ul> <li>Parity Enable Bit — PE enables the parity function. When enabled, the parity function inserts a parity bit in the most significant bit position.</li> <li>0 Parity function disabled</li> <li>1 Parity function enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 0<br>PT  | <ul> <li>Parity Type Bit — PT determines whether the SCI generates and checks for even parity or odd parity. With even parity, an even number of 1s clears the parity bit and an odd number of 1s sets the parity bit. With odd parity, an odd number of 1s clears the parity bit and an even number of 1s sets the parity bit.</li> <li>0 Even parity</li> <li>1 Odd parity</li> </ul>                                                                                                                                                                                                   |  |  |  |  |

### Table 20-5. Loop Functions

| LOOPS | RSRC | Function                                                                 |  |

|-------|------|--------------------------------------------------------------------------|--|

| 0     | х    | Normal operation                                                         |  |

| 1     | 0    | Loop mode with transmitter output internally connected to receiver input |  |

| 1     | 1    | Single-wire mode with TXD pin connected to receiver input                |  |

When all bits are clear (the default condition), the SPI module clock is divided by 2. When the selection bits (SPR2–SPR0) are 001 and the preselection bits (SPPR2–SPPR0) are 000, the module clock divisor becomes 4. When the selection bits are 010, the module clock divisor becomes 8, etc.

When the preselection bits are 001, the divisor determined by the selection bits is multiplied by 2. When the preselection bits are 010, the divisor is multiplied by 3, etc. See Table 21-7 for baud rate calculations for all bit conditions, based on a 25 MHz bus clock. The two sets of selects allows the clock to be divided by a non-power of two to achieve other baud rates such as divide by 6, divide by 10, etc.

The baud rate generator is activated only when the SPI is in master mode and a serial transfer is taking place. In the other cases, the divider is disabled to decrease  $I_{DD}$  current.

### NOTE

For maximum allowed baud rates, please refer to the SPI Electrical Specification in the Electricals chapter of this data sheet.

# 21.4.5 Special Features

# 21.4.5.1 **SS** Output

The  $\overline{SS}$  output feature automatically drives the  $\overline{SS}$  pin low during transmission to select external devices and drives it high during idle to deselect external devices. When  $\overline{SS}$  output is selected, the  $\overline{SS}$  output pin is connected to the  $\overline{SS}$  input pin of the external device.

The  $\overline{SS}$  output is available only in master mode during normal SPI operation by asserting SSOE and MODFEN bit as shown in Table 21-3.

The mode fault feature is disabled while  $\overline{SS}$  output is enabled.

## NOTE

Care must be taken when using the  $\overline{SS}$  output feature in a multimaster system because the mode fault feature is not available for detecting system errors between masters.

# 21.4.5.2 Bidirectional Mode (MOMI or SISO)

The bidirectional mode is selected when the SPC0 bit is set in SPI control register 2 (see Table 21-11). In this mode, the SPI uses only one serial data pin for the interface with external device(s). The MSTR bit decides which pin to use. The MOSI pin becomes the serial data I/O (MOMI) pin for the master mode, and the MISO pin becomes serial data I/O (SISO) pin for the slave mode. The MISO pin in master mode and MOSI pin in slave mode are not used by the SPI.

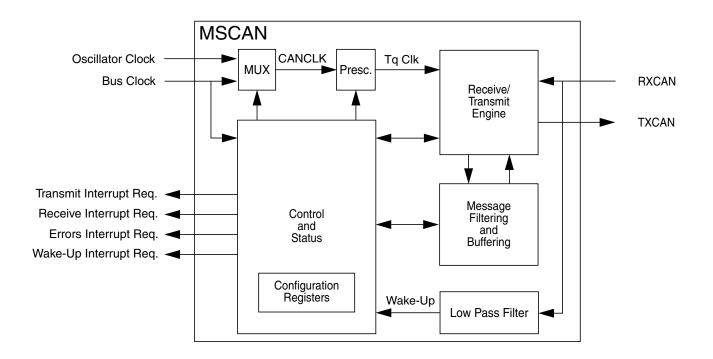

# 22.3.2.8 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Write: Anytime

Module Base + 0x0008

### Table 22-8. TCTL1/TCTL2 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0<br>OMx | <ul> <li>Output Mode — These eight pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx.</li> <li>Note: To enable output action by OMx bits on timer port, the corresponding bit in OC7M should be cleared. For an output line to be driven by an OCx the OCPDx must be cleared.</li> </ul>  |  |  |  |  |

| 7:0<br>OLx | <ul> <li>Output Level — These eight pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx.</li> <li>Note: To enable output action by OLx bits on timer port, the corresponding bit in OC7M should be cleared. For an output line to be driven by an OCx the OCPDx must be cleared.</li> </ul> |  |  |  |  |

#### Table 22-9. Compare Result Output Action

| OMx | OLx | Action                                                 |

|-----|-----|--------------------------------------------------------|

| 0   | 0   | No output compare<br>action on the timer output signal |

| 0   | 1   | Toggle OCx output line                                 |

| 1   | 0   | Clear OCx output line to zero                          |

| 1   | 1   | Set OCx output line to one                             |

Figure 25-4. FTM256K2 Register Summary (continued)

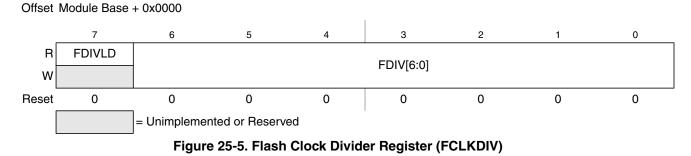

# 25.3.2.1 Flash Clock Divider Register (FCLKDIV)

The FCLKDIV register is used to control timed events in program and erase algorithms.

All bits in the FCLKDIV register are readable, bits 6–0 are write once and bit 7 is not writable.

### Table 25-8. FCLKDIV Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                                                                                                                             |  |  |

| 6–0<br>FDIV[6:0] | <b>Clock Divider Bits</b> — FDIV[6:0] must be set to effectively divide OSCCLK down to generate an internal Flash clock, FCLK, with a target frequency of 1 MHz for use by the Flash module to control timed events during program and erase algorithms. Table 25-9 shows recommended values for FDIV[6:0] based on OSCCLK frequency. Please refer to Section 25.4.1, "Flash Command Operations," for more information. |  |  |

## CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0). The FCLKDIV register is writable during the Flash reset sequence even though CCIF is clear.

| FCMD | Command                          | and Function on D-Flash Memory                                                                                                                                                                                                                            |  |

|------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x08 | Erase All Blocks                 | Erase all D-Flash (and P-Flash) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the EPDIS and EPOPEN bits in the EPROT register are<br>set prior to launching the command. |  |

| 0x0B | Unsecure Flash                   | Supports a method of releasing MCU security by erasing all D-Flash (and P-Flash) blocks and verifying that all D-Flash (and P-Flash) blocks are erased.                                                                                                   |  |

| 0x0D | Set User Margin<br>Level         | Specifies a user margin read level for the D-Flash block.                                                                                                                                                                                                 |  |

| 0x0E | Set Field Margin<br>Level        | Specifies a field margin read level for the D-Flash block (special modes only).                                                                                                                                                                           |  |

| 0x0F | Full Partition D-<br>Flash       | Erase the D-Flash block and partition an area of the D-Flash block for user access.                                                                                                                                                                       |  |

| 0x10 | Erase Verify D-<br>Flash Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                                          |  |

| 0x11 | Program D-Flash                  | Program up to four words in the D-Flash block.                                                                                                                                                                                                            |  |

| 0x12 | Erase D-Flash<br>Sector          | Erase all bytes in a sector of the D-Flash block.                                                                                                                                                                                                         |  |

| 0x13 | Enable EEPROM<br>Emulation       | Enable EEPROM emulation where writes to the buffer RAM EEE partition will be copied to the D-Flash EEE partition.                                                                                                                                         |  |

| 0x14 | Disable EEPROM<br>Emulation      | Suspend all current erase and program activity related to EEPROM emulation but leave current EEE tags set.                                                                                                                                                |  |

| 0x15 | EEPROM<br>Emulation Query        | Returns EEE partition and status variables.                                                                                                                                                                                                               |  |

| 0x20 | Partition D-Flash                | Partition an area of the D-Flash block for user access.                                                                                                                                                                                                   |  |

### Table 25-32. D-Flash Commands

# 25.4.2 Flash Command Description

This section provides details of all available Flash commands launched by a command write sequence. The ACCERR bit in the FSTAT register will be set during the command write sequence if any of the following illegal steps are performed, causing the command not to be processed by the Memory Controller:

- Starting any command write sequence that programs or erases Flash memory before initializing the FCLKDIV register

- Writing an invalid command as part of the command write sequence

- For additional possible errors, refer to the error handling table provided for each command

If a Flash block is read during execution of an algorithm (CCIF = 0) on that same block, the read operation will return invalid data. If the SFDIF or DFDIF flags were not previously set when the invalid read operation occurred, both the SFDIF and DFDIF flags will be set and the FECCR registers will be loaded with the global address used in the invalid read operation with the data and parity fields set to all 0.

If the ACCERR or FPVIOL bits are set in the FSTAT register, the user must clear these bits before starting any command write sequence (see Section 25.3.2.7).

### Table 27-4. Program IFR Fields

| Global Address<br>(PGMIFRON) | Size<br>(Bytes) | Field Description                                                       |

|------------------------------|-----------------|-------------------------------------------------------------------------|

| 0x40_0000 - 0x40_0007        | 8               | Device ID                                                               |

| 0x40_0008 - 0x40_00E7        | 224             | Reserved                                                                |

| 0x40_00E8 - 0x40_00E9        | 2               | Version ID                                                              |

| 0x40_00EA - 0x40_00FF        | 22              | Reserved                                                                |

| 0x40_0100 - 0x40_013F        | 64              | Program Once Field<br>Refer to Section 27.4.2.7, "Program Once Command" |

| 0x40_0140 - 0x40_01FF        | 192             | Reserved                                                                |

#### Table 27-5. P-Flash IFR Accessibility

| Global Address<br>(PGMIFRON) | Size<br>(Bytes) | Accessed From                 |

|------------------------------|-----------------|-------------------------------|

| 0x40_0000 - 0x40_01FF        | 512             | XBUS0 (PBLK0S) <sup>(1)</sup> |

| 0x40_0200 - 0x40_03FF        | 512             | Unimplemented                 |

| 0x40_0400 - 0x40_05FF        | 512             | XBUS0 (PBLK1N)                |

| 0x40_0600 - 0x40_07FF        | 512             | XBUS1 (PBLK1S)                |

1. Refer to Table 27-4 for more details.

#### Table 27-6. EEE Resource Fields

| Global Address          | Size<br>(Bytes) | Description                                                        |  |

|-------------------------|-----------------|--------------------------------------------------------------------|--|

| 0x10_0000 - 0x10_7FFF   | 32,768          | D-Flash Memory (User and EEE)                                      |  |

| 0x10_8000 - 0x11_FFFF   | 98,304          | Reserved                                                           |  |

| 0x12_0000 - 0x12_007F   | 128             | EEE Nonvolatile Information Register (EEEIFRON <sup>(1)</sup> = 1) |  |

| 0x12_0080 - 0x12_0FFF   | 3,968           | Reserved                                                           |  |

| 0x12_1000 - 0x12_1EFF   | 3,840           | Reserved                                                           |  |

| 0x12_1F00 - 0x12_1FFF   | 256             | EEE Tag RAM (TMGRAMON <sup>1</sup> = 1)                            |  |

| 0x12_2000 - 0x12_3BFF   | 7,168           | Reserved                                                           |  |

| 0x12_3C00 - 0x12_3FFF   | 1,024           | Memory Controller Scratch RAM (TMGRAMON <sup>1</sup> = 1)          |  |

| 0x12_4000 - 0x12_DFFF   | 40,960          | Reserved                                                           |  |

| 0x12_E000 - 0x12_FFFF   | 8,192           | Reserved                                                           |  |

| 0x13_0000 - 0x13_EFFF   | 61,440          | Reserved                                                           |  |

| 0x13_F000 - 0x13_FFFF   | 4,096           | Buffer RAM (User and EEE)                                          |  |

| 1. MMCCTL1 register bit |                 |                                                                    |  |

# 28.4.2.10 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| 000         | 0x0A                                                                                                                     | Global address [22:16] to identify<br>P-Flash block to be erased |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 28.1.2.1 for the P-Flash sector size. |                                                                  |  |  |

Table 28-51. Erase P-Flash Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                       |  |  |

|          |           | Set if command not available in current mode (see Table 28-30)                      |  |  |

|          |           | Set if an invalid global address [22:16] is supplied <sup>(1)</sup>                 |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |  |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                |  |  |

Table 28-52. Erase P-Flash Sector Command Error Handling

1. As defined by the memory map for FTM1024K5.

# 28.4.2.11 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and D-Flash memory space and, if the erase is successful, will release security.

### Table 28-53. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |

|-------------|------------------|--------------|--|--|

| 000         | 0x0B             | Not required |  |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and D-Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security

| Num | 6 |       | Doting                      | Gumbel                | N/1:         | T      | Max  | Unit |

|-----|---|-------|-----------------------------|-----------------------|--------------|--------|------|------|

| Num | С |       | Rating                      | Symbol                | Min          | Тур    | Max  | Unit |

|     |   | Ps    | eudo stop current (API, RTI | , and COP disabled) I | PLL off, LCI | o mode |      |      |

| 10  | C | -40°C |                             | I <sub>DDPS</sub>     | —            | 175    | —    | μA   |

|     | P | 27°C  |                             | _                     | —            | 185    | 255  |      |

|     | C | 70°C  |                             |                       | —            | 255    | —    |      |

|     | C | 85°C  |                             |                       | —            | 305    | —    |      |

|     | C | 105°C |                             |                       | —            | 455    | —    |      |

|     | P | 110°C |                             |                       | —            | 505    | 2155 |      |

|     | Р | 130°C |                             |                       | —            | 805    | 3655 |      |

|     | P | 150°C |                             |                       | —            | 1555   | 7655 |      |

|     |   | Ps    | eudo stop current (API, RTI | , and COP enabled) F  | PLL off, LCF | o mode |      |      |

| 11  | С | 27°C  |                             | I <sub>DDPS</sub>     | —            | 205    | —    | μA   |

|     | С | 70°C  |                             |                       | —            | 275    |      |      |

|     | С | 85°C  |                             |                       | —            | 325    | —    |      |

|     | С | 105°C |                             |                       | —            | 475    | —    |      |

|     | С | 125°C |                             |                       | —            | 810    | —    |      |

|     | С | 150°C |                             |                       | —            | 1575   | —    |      |

|     |   |       | Si                          | top Current           |              |        |      |      |

| 12  | С | -40°C |                             | I <sub>DDS</sub>      | —            | 20     | —    | μA   |

|     | Р | 27°C  |                             |                       | —            | 30     | 100  |      |

|     | С | 70°C  |                             |                       | —            | 100    |      |      |

|     | С | 85°C  |                             |                       | —            | 150    | —    |      |

|     | С | 105°C |                             |                       | —            | 300    | —    |      |

|     | Р | 110°C |                             |                       | —            | 350    | 2000 |      |

|     | C | 125°C |                             |                       | —            | 550    | —    |      |

|     | P | 130°C |                             |                       | —            | 650    | 3500 |      |

|     | Р | 150°C |                             |                       | —            | 1400   | 7500 |      |

|     |   |       | Stop Cu                     | rrent (API active)    |              |        |      |      |

| 13  | Т | –40°C |                             | I <sub>DDS</sub>      | _            | 32     |      | μA   |

|     | Т | 27°C  |                             |                       | —            | 42     |      |      |

|     | Т | 85°C  |                             |                       | —            | 162    | —    |      |

|     | Т | 110°C |                             |                       | —            | 362    | _    |      |

|     | Т | 130°C |                             |                       | —            | 662    | _    |      |

|     |   |       | Stop Curre                  | ent (one ATD active)  |              |        |      |      |

| 14  | Т | 27°C  |                             | I <sub>DDS</sub>      | _            | 300    | _    | μΑ   |

|     | Т | 85°C  |                             |                       | —            | 420    | —    |      |

|     | Т | 125°C |                             |                       |              | 820    |      |      |

### Table A-14. Pseudo Stop and Full Stop Current