Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HCS12X                                                       |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 50MHz                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI            |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 119                                                          |

| Program Memory Size        | 512KB (512K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 4K x 8                                                       |

| RAM Size                   | 32K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                 |

| Data Converters            | A/D 24x12b                                                   |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 144-LQFP                                                     |

| Supplier Device Package    | 144-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12xeq512cag |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Mnemonic | Nominal<br>Voltage | Description                                                                                                                                                         |

|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDPLL   | 1.8 V              | Provides operating voltage and ground for                                                                                                                           |

| VSSPLL   | 0 V                | the phased-locked loop. This allows the<br>supply voltage to the PLL to be bypassed<br>independently. Internal power and ground<br>generated by internal regulator. |

Table 1-11. Power and Ground Connection Summary (continued)

ter 2 Port Integration Module (S12XEPIMV1)

| Register<br>Name                                 |        | Bit 7    | 6           | 5              | 4          | 3           | 2        | 1        | Bit 0    |  |

|--------------------------------------------------|--------|----------|-------------|----------------|------------|-------------|----------|----------|----------|--|

| 0x0272<br>DDR0AD0                                | R<br>W | DDR0AD07 | DDR0AD06    | DDR0AD05       | DDR0AD04   | DDR0AD03    | DDR0AD02 | DDR0AD01 | DDR0AD00 |  |

| 0x0273<br>DDR1AD0                                | R<br>W | DDR1AD07 | DDR1AD06    | DDR1AD05       | DDR1AD04   | DDR1AD03    | DDR1AD02 | DDR1AD01 | DDR1AD00 |  |

| 0x0274<br>RDR0AD0                                | R<br>W | RDR0AD07 | RDR0AD06    | RDR0AD05       | RDR0AD04   | RDR0AD03    | RDR0AD02 | RDR0AD01 | RDR0AD00 |  |

| 0x0275<br>RDR1AD0                                | R<br>W | RDR1AD07 | RDR1AD06    | RDR1AD05       | RDR1AD04   | RDR1AD03    | RDR1AD02 | RDR1AD01 | RDR1AD00 |  |

| 0x0276<br>PER0AD0                                | R<br>W | PER0AD07 | PER0AD06    | PER0AD05       | PER0AD04   | PER0AD03    | PER0AD02 | PER0AD01 | PER0AD00 |  |

| 0x0277<br>PER1AD0                                | R<br>W | PER1AD07 | PER1AD06    | PER1AD05       | PER1AD04   | PER1AD03    | PER1AD02 | PER1AD01 | PER1AD00 |  |

| 0x0278<br>PT0AD1                                 | R<br>W | PT0AD17  | PT0AD16     | PT0AD15        | PT0AD14    | PT0AD13     | PT0AD12  | PT0AD11  | PT0AD10  |  |

| 0x0279<br>PT1AD1                                 | R<br>W | PT1AD17  | PT1AD16     | PT1AD15        | PT1AD14    | PT1AD13     | PT1AD12  | PT1AD11  | PT1AD10  |  |

| 0x027A<br>DDR0AD1                                | R<br>W | DDR0AD17 | DDR0AD16    | DDR0AD15       | DDR0AD14   | DDR0AD13    | DDR0AD12 | DDR0AD11 | DDR0AD10 |  |

| 0x027B<br>DDR1AD1                                | R<br>W | DDR1AD17 | DDR1AD16    | DDR1AD15       | DDR1AD14   | DDR1AD13    | DDR1AD12 | DDR1AD11 | DDR1AD10 |  |

| 0x027C<br>RDR0AD1                                | R<br>W | RDR0AD17 | RDR0AD16    | RDR0AD15       | RDR0AD14   | RDR0AD13    | RDR0AD12 | RDR0AD11 | RDR0AD10 |  |

| 0x027D<br>RDR1AD1                                | R<br>W | RDR1AD17 | RDR1AD16    | RDR1AD15       | RDR1AD14   | RDR1AD13    | RDR1AD12 | RDR1AD11 | RDR1AD10 |  |

| 0x027E<br>PER0AD1                                | R<br>W | PER0AD17 | PER0AD16    | PER0AD15       | PER0AD14   | PER0AD13    | PER0AD12 | PER0AD1' | PER0AD10 |  |

| 0x027F<br>PER1AD1                                | R<br>W | PER1AD17 | PER1AD16    | PER1AD15       | PER1AD14   | PER1AD13    | PER1AD12 | PER1AD11 | PER1AD10 |  |

| 0x0280–<br>0x0267<br>Non-PIM<br>Address<br>Range | R<br>W |          |             |                | Non-PIM Ad | dress Range |          |          |          |  |

|                                                  | [      |          | = Unimpleme | ented or Reser | ved        |             |          |          |          |  |

| PRR Name | PRR Local Address | PRR Location |

|----------|-------------------|--------------|

| PORTA    | 0x0000            | PIM          |

| PORTB    | 0x0001            | PIM          |

| DDRA     | 0x0002            | PIM          |

| DDRB     | 0x0003            | PIM          |

| PORTC    | 0x0004            | PIM          |

| PORTD    | 0x0005            | PIM          |

| DDRC     | 0x0006            | PIM          |

| DDRD     | 0x0007            | PIM          |

| PORTE    | 0x0008            | PIM          |

| DDRE     | 0x0009            | PIM          |

| MMCCTL0  | 0x000A            | MMC          |

| MODE     | 0x000B            | MMC          |

| PUCR     | 0x000C            | PIM          |

| RDRIV    | 0x000D            | PIM          |

| EBICTL0  | 0x000E            | EBI          |

| EBICTL1  | 0x000F            | EBI          |

| Reserved | 0x0012            | MMC          |

| MMCCTL1  | 0x0013            | MMC          |

| ECLKCTL  | 0x001C            | PIM          |

| Reserved | 0x001D            | PIM          |

| PORTK    | 0x0032            | PIM          |

| DDRK     | 0x0033            | PIM          |

## Table 3-21. PRR Listing

# 3.5.3 On-Chip ROM Control

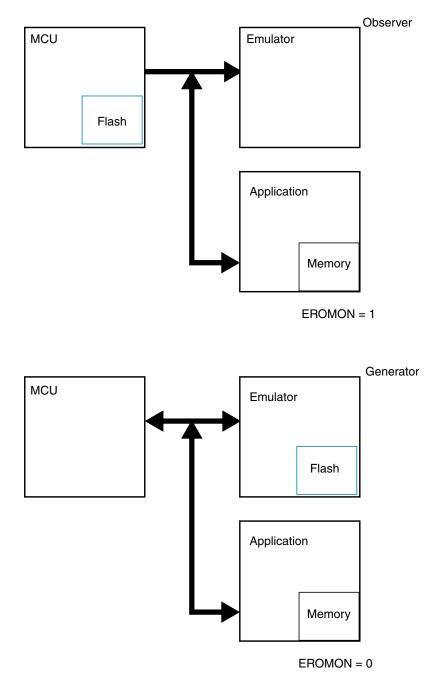

The MCU offers two modes to support emulation. In the first mode (called generator) the emulator provides the data instead of the internal FLASH and traces the CPU actions. In the other mode (called observer) the internal FLASH provides the data and all internal actions are made visible to the emulator.

# 3.5.3.1 ROM Control in Single-Chip Modes

In single-chip modes the MCU has no external bus. All memory accesses and program fetches are internal (see Figure 3-24).

# 3.5.3.4 ROM Control in Emulation Expanded Mode

In emulation expanded mode the external bus will be connected to the emulator and to the application. If the ROMON bit is set, the internal FLASH provides the data. If the EROMON bit is set as well the emulator observes all CPU internal actions, otherwise the emulator provides the data and traces all CPU actions (see Figure 3-27). When the ROMON bit is cleared, the application memory provides the data and the emulator will observe the CPU internal actions (see Figure 3-28).

Figure 3-27. ROMON = 1 in Emulation Expanded Mode

- Hardware handshake protocol to increase the performance of the serial communication

- Active out of reset in special single chip mode

- Nine hardware commands using free cycles, if available, for minimal CPU intervention

- Hardware commands not requiring active BDM

- 14 firmware commands execute from the standard BDM firmware lookup table

- Software control of BDM operation during wait mode

- Software selectable clocks

- Global page access functionality

- Enabled but not active out of reset in emulation modes (if modes available)

- CLKSW bit set out of reset in emulation modes (if modes available).

- When secured, hardware commands are allowed to access the register space in special single chip mode, if the non-volatile memory erase test fail.

- Family ID readable from firmware ROM at global address 0x7FFF0F (value for HCS12X devices is 0xC1)

- BDM hardware commands are operational until system stop mode is entered (all bus masters are in stop mode)

# 7.1.2 Modes of Operation

BDM is available in all operating modes but must be enabled before firmware commands are executed. Some systems may have a control bit that allows suspending thefunction during background debug mode.

# 7.1.2.1 Regular Run Modes

All of these operations refer to the part in run mode and not being secured. The BDM does not provide controls to conserve power during run mode.

- Normal modes General operation of the BDM is available and operates the same in all normal modes.

- Special single chip mode

In special single chip mode, background operation is enabled and active out of reset. This allows programming a system with blank memory.

• Emulation modes (if modes available)

In emulation mode, background operation is enabled but not active out of reset. This allows debugging and programming a system in this mode more easily.

# 7.1.2.2 Secure Mode Operation

If the device is in secure mode, the operation of the BDM is reduced to a small subset of its regular run mode operation. Secure operation prevents BDM and CPU accesses to non-volatile memory (Flash and/or EEPROM) other than allowing erasure. For more information please see Section 7.4.1, "Security".

### ter 7 Background Debug Module (S12XBDMV2)

16-bit misaligned reads and writes are generally not allowed. If attempted by BDM hardware command, the BDM will ignore the least significant bit of the address and will assume an even address from the remaining bits.

For devices with external bus:

The following cycle count information is only valid when the external wait function is not used (see wait bit of EBI sub-block). During an external wait the BDM can not steal a cycle. Hence be careful with the external wait function if the BDM serial interface is much faster than the bus, because of the BDM soft-reset after time-out (see Section 7.4.11, "Serial Communication Time Out").

For hardware data read commands, the external host must wait at least 150 bus clock cycles after sending the address before attempting to obtain the read data. This is to be certain that valid data is available in the BDM shift register, ready to be shifted out. For hardware write commands, the external host must wait 150 bus clock cycles after sending the data to be written before attempting to send a new command. This is to avoid disturbing the BDM shift register before the write has been completed. The 150 bus clock cycle delay in both cases includes the maximum 128 cycle delay that can be incurred as the BDM waits for a free cycle before stealing a cycle.

For firmware read commands, the external host should wait at least 48 bus clock cycles after sending the command opcode and before attempting to obtain the read data. This includes the potential of extra cycles when the access is external and stretched (+1 to maximum +7 cycles) or to registers of the PRU (port replacement unit) in emulation modes (if modes available). The 48 cycle wait allows enough time for the requested data to be made available in the BDM shift register, ready to be shifted out.

## NOTE

This timing has increased from previous BDM modules due to the new capability in which the BDM serial interface can potentially run faster than the bus. On previous BDM modules this extra time could be hidden within the serial time.

For firmware write commands, the external host must wait 36 bus clock cycles after sending the data to be written before attempting to send a new command. This is to avoid disturbing the BDM shift register before the write has been completed.

The external host should wait at least for 76 bus clock cycles after a TRACE1 or GO command before starting any new serial command. This is to allow the CPU to exit gracefully from the standard BDM firmware lookup table and resume execution of the user code. Disturbing the BDM shift register prematurely may adversely affect the exit from the standard BDM firmware lookup table.

## NOTE

If the bus rate of the target processor is unknown or could be changing or the external wait function is used, it is recommended that the ACK (acknowledge function) is used to indicate when an operation is complete. When using ACK, the delay times are automated.

Figure 7-7 represents the BDM command structure. The command blocks illustrate a series of eight bit times starting with a falling edge. The bar across the top of the blocks indicates that the BKGD line idles in the high state. The time for an 8-bit command is  $8 \times 16$  target clock cycles.<sup>1</sup>

| TRANGE | Tracing Range                                             |

|--------|-----------------------------------------------------------|

| 00     | Trace from all addresses (No filter)                      |

| 01     | Trace only in address range from \$00000 to Comparator D  |

| 10     | Trace only in address range from Comparator C to \$7FFFFF |

| 11     | Trace only in range from Comparator C to Comparator D     |

## Table 8-12. TRANGE Trace Range Encoding

### Table 8-13. TRCMOD Trace Mode Bit Encoding

| TRCMOD | Description |

|--------|-------------|

| 00     | Normal      |

| 01     | Loop1       |

| 10     | Detail      |

| 11     | Pure PC     |

### Table 8-14. TALIGN Trace Alignment Encoding

| TALIGN | Description                                   |

|--------|-----------------------------------------------|

| 00     | Trigger at end of stored data                 |

| 01     | Trigger before storing data                   |

| 10     | Trace buffer entries before and after trigger |

| 11     | Reserved                                      |

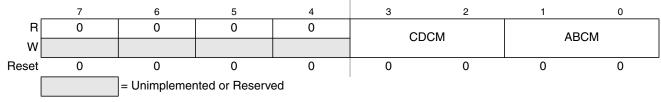

## 8.3.2.4 Debug Control Register2 (DBGC2)

Address: 0x0023

## Figure 8-6. Debug Control Register2 (DBGC2)

Read: Anytime

Write: Anytime the module is disarmed.

This register configures the comparators for range matching.

#### Table 8-15. DBGC2 Field Descriptions

| Field            | Description                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 3–2<br>CDCM[1:0] | <b>C and D Comparator Match Control</b> — These bits determine the C and D comparator match mapping as described in Table 8-16. |

| 1–0<br>ABCM[1:0] | A and B Comparator Match Control — These bits determine the A and B comparator match mapping as described in Table 8-17.        |

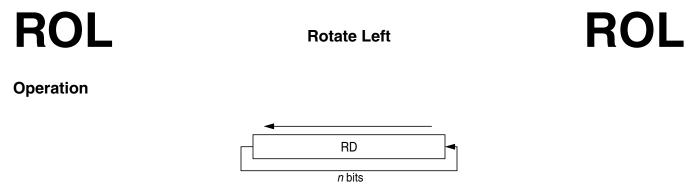

### n = RS or IMM4

Rotates the bits in register RD n positions to the left. The lower n bits of the register RD are filled with the upper n bits. Two source forms are available. In the first form, the parameter n is contained in the instruction code as an immediate operand. In the second form, the parameter is contained in the lower bits of the source register RS[3:0]. All other bits in RS are ignored. If n is zero, no shift will take place and the register RD will be unaffected; however, the condition code flags will be updated.

## **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | 0 | — |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: 0; cleared.

- C: Not affected.

## **Code and CPU Cycles**

| Source Form   | Address<br>Mode | Machine Code |   |   |   |   |    | Cycles |   |   |   |   |   |   |

|---------------|-----------------|--------------|---|---|---|---|----|--------|---|---|---|---|---|---|

| ROL RD, #IMM4 | IMM4            | 0            | 0 | 0 | 0 | 1 | RD | IMM4   |   | 1 | 1 | 1 | 0 | Р |

| ROL RD, RS    | DYA             | 0            | 0 | 0 | 0 | 1 | RD | RS     | 1 | 0 | 1 | 1 | 0 | Р |

## Table 14-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare Mask Action for Channel 7:0</li> <li>A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>0 The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>1 The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 andOCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

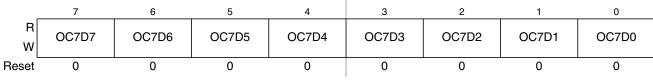

## 14.3.2.4 Output Compare 7 Data Register (OC7D)

Module Base + 0x0003

Figure 14-6. Output Compare 7 Data Register (OC7D)

Read or write: Anytime

All bits reset to zero.

### Table 14-5. OC7D Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Output Compare 7 Data Bits</b> — A channel 7 event, which can be a counter overflow when TTOV[7] is set or A channel 7 output compare can cause bits in the output compare 7 data register to transfer to the timer port data register depending on the output compare 7 mask register. |

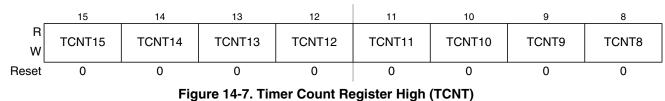

# 14.3.2.5 Timer Count Register (TCNT)

Module Base + 0x0004

| IBC[7:0]<br>(hex) | SCL Divider<br>(clocks) | SDA Hold<br>(clocks) | SCL Hold<br>(start) | SCL Hold<br>(stop) |

|-------------------|-------------------------|----------------------|---------------------|--------------------|

| AC                | 2304                    | 388                  | 1144                | 1156               |

| AD                | 2560                    | 388                  | 1272                | 1284               |

| AE                | 3072                    | 516                  | 1528                | 1540               |

| AF                | 3840                    | 516                  | 1912                | 1924               |

| B0                | 2560                    | 260                  | 1272                | 1284               |

| B1                | 3072                    | 260                  | 1528                | 1540               |

| B2                | 3584                    | 516                  | 1784                | 1796               |

| B3                | 4096                    | 516                  | 2040                | 2052               |

| B4                | 4608                    | 772                  | 2296                | 2308               |

| B5                | 5120                    | 772                  | 2552                | 2564               |

| B6                | 6144                    | 1028                 | 3064                | 3076               |

| B7                | 7680                    | 1028                 | 3832                | 3844               |

| B8                | 5120                    | 516                  | 2552                | 2564               |

| B9                | 6144                    | 516                  | 3064                | 3076               |

| BA                | 7168                    | 1028                 | 3576                | 3588               |

| BB                | 8192                    | 1028                 | 4088                | 4100               |

| BC                | 9216                    | 1540                 | 4600                | 4612               |

| BD                | 10240                   | 1540                 | 5112                | 5124               |

| BE                | 12288                   | 2052                 | 6136                | 6148               |

| BF                | 15360                   | 2052                 | 7672                | 7684               |

### Table 15-7. IIC Divider and Hold Values (Sheet 6 of 6)

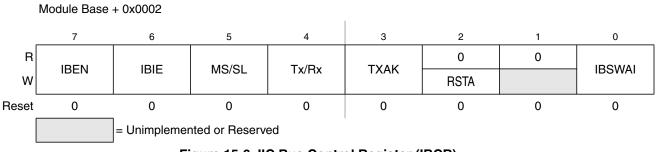

# 15.3.1.3 IIC Control Register (IBCR)

Figure 15-6. IIC Bus Control Register (IBCR)

Read and write anytime

| Register<br>Name |   | Bit 7  | 6                                                           | 5             | 4            | 3             | 2           | 1      | Bit 0  |  |  |

|------------------|---|--------|-------------------------------------------------------------|---------------|--------------|---------------|-------------|--------|--------|--|--|

| 0x000F           | R | TXERR7 | TXERR6                                                      | TXERR5        | TXERR4       | TXERR3        | TXERR2      | TXERR1 | TXERR0 |  |  |

| CANTXERR         | W |        |                                                             |               |              |               |             |        |        |  |  |

| 0x0010-0x0013    | R | AC7    | AC6                                                         | AC5           | AC4          | AC3           | AC2         | AC1    | AC0    |  |  |

| CANIDAR0-3       | W | 707    | 700                                                         | 703           | 704          | 700           | 702         | ACT    | 700    |  |  |

| 0x0014-0x0017    | R | AM7    | AM6                                                         | AM5           | AM4          | АМЗ           | AM2         | AM1    | AMO    |  |  |

| CANIDMRx         | W |        | Alvio                                                       | AIVIS         | Alvi4        | Alvio         | Alviz       | AIVIT  | AIVIO  |  |  |

| 0x0018-0x001B    | R | AC7    | AC6                                                         | AC5           | AC4          | AC3           | AC2         | AC1    | AC0    |  |  |

| CANIDAR4-7       | W | AU7    | ACO                                                         | A05           | A04          | A03           | A02         | ACT    | ACU    |  |  |

| 0x001C-0x001F    | R | AM7    | AM6                                                         | AM5           | AM4          | АМЗ           | AM2         | AM1    | AMO    |  |  |

| CANIDMR4-7       | w | Alvi7  | Alvio                                                       | CIVIA         | Alvi4        | Alvið         | Alviz       | AIVIT  | Alviu  |  |  |

| 0x0020-0x002F    | R |        | 0                                                           |               | "D           |               | Manage Ob   |        |        |  |  |

| CANRXFG          | w |        | See S                                                       | ection 16.3.3 | s, "Programm | er's Model of | Message Sto | brage  |        |  |  |

| 0x0030-0x003F    | R |        |                                                             |               |              |               |             |        |        |  |  |

| CANTXFG          | w |        | See Section 16.3.3, "Programmer's Model of Message Storage" |               |              |               |             |        |        |  |  |

|                  |   |        | = Unimplemented or Reserved                                 |               |              |               |             |        |        |  |  |

Figure 16-3. MSCAN Register Summary (continued)

# 16.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the MSCAN module. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. All bits of all registers in this module are completely synchronous to internal clocks during a register read.

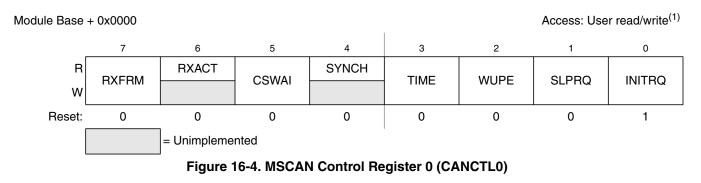

# 16.3.2.1 MSCAN Control Register 0 (CANCTL0)

The CANCTL0 register provides various control bits of the MSCAN module as described below.

## Table 18-8. PITMTLD0–1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMTLD[7:0] | <b>PIT Micro Timer Load Bits 7:0</b> — These bits set the 8-bit modulus down-counter load value of the micro timers. Writing a new value into the PITMTLD register will not restart the timer. When the micro timer has counted down to zero, the PMTLD register value will be loaded. The PFLMT bits in the PITCFLMT register can be used to immediately update the count register with the new value if an immediate load is desired. |

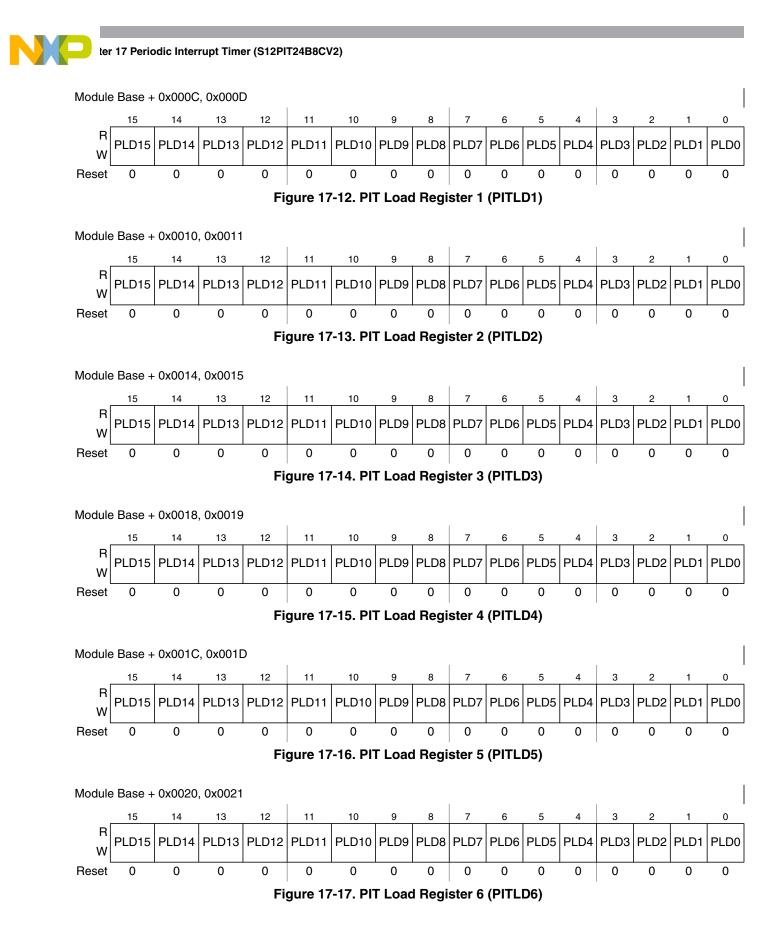

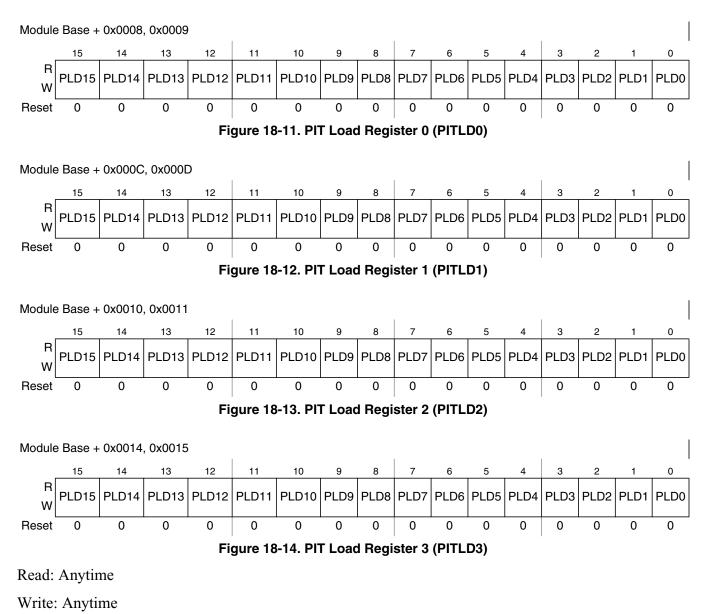

# 18.3.0.8 PIT Load Register 0 to 3 (PITLD0–3)

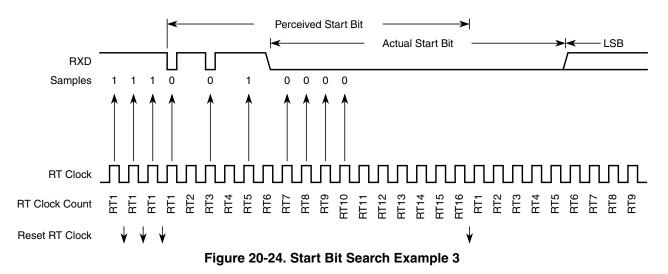

In Figure 20-24, a large burst of noise is perceived as the beginning of a start bit, although the test sample at RT5 is high. The RT5 sample sets the noise flag. Although this is a worst-case misalignment of perceived bit time, the data samples RT8, RT9, and RT10 are within the bit time and data recovery is successful.

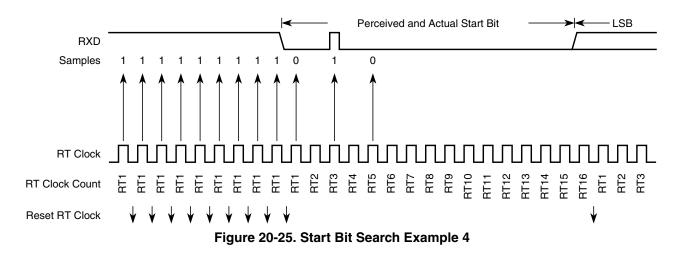

Figure 20-25 shows the effect of noise early in the start bit time. Although this noise does not affect proper synchronization with the start bit time, it does set the noise flag.

ter 21 Serial Peripheral Interface (S12SPIV5)

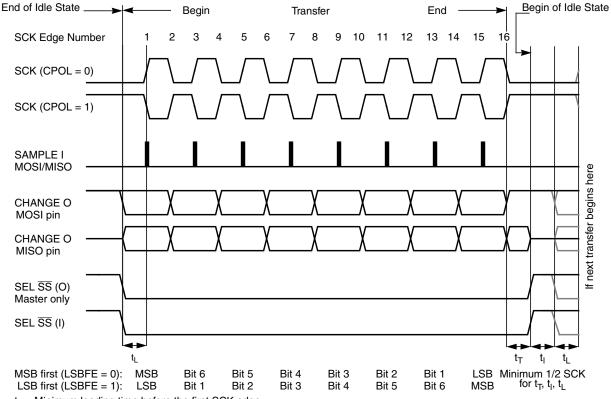

$t_{\text{L}}$  = Minimum leading time before the first SCK edge

$t_{T}^{-}$  = Minimum trailing time after the last SCK edge

$t_{I}$  = Minimum idling time between transfers (minimum  $\overline{SS}$  high time)

$t_L$ ,  $t_T$ , and  $t_I$  are guaranteed for the master mode and required for the slave mode.

Figure 21-12. SPI Clock Format 0 (CPHA = 0), with 8-bit Transfer Width selected (XFRW = 0)

| CCOBIX[2:0] | FCCOB Parameters                                                   |  |  |  |  |

|-------------|--------------------------------------------------------------------|--|--|--|--|

| 000         | 0x0F Not required                                                  |  |  |  |  |

| 001         | Number of 256 byte sectors for the D-Flash user partition (DFPART) |  |  |  |  |

| 010         | Number of 256 byte sectors for buffer RAM EEE partition (ERPART)   |  |  |  |  |

## Table 25-63. Full Partition D-Flash Command FCCOB Requirements

Upon clearing CCIF to launch the Full Partition D-Flash command, the following actions are taken to define a partition within the D-Flash block for direct access (DFPART) and a partition within the buffer RAM for EEE use (ERPART):

- Validate the DFPART and ERPART values provided:

- DFPART <= 128 (maximum number of 256 byte sectors in D-Flash block)

- ERPART <= 16 (maximum number of 256 byte sectors in buffer RAM)

- If ERPART > 0, 128 DFPART >= 12 (minimum number of 256 byte sectors in the D-Flash block required to support EEE)

- If ERPART > 0, ((128-DFPART)/ERPART) >= 8 (minimum ratio of D-Flash EEE space to buffer RAM EEE space to support EEE)

- Erase the D-Flash block and the EEE nonvolatile information register

- Program DFPART to the EEE nonvolatile information register at global address 0x12\_0000 (see Table 25-7)

- Program a duplicate DFPART to the EEE nonvolatile information register at global address 0x12\_0002 (see Table 25-7)

- Program ERPART to the EEE nonvolatile information register at global address 0x12\_0004 (see Table 25-7)

- Program a duplicate ERPART to the EEE nonvolatile information register at global address 0x12\_0006 (see Table 25-7)

The D-Flash user partition will start at global address  $0x10_{0000}$ . The buffer RAM EEE partition will end at global address  $0x13_{FFFF}$ . After the Full Partition D-Flash operation has completed, the CCIF flag will set.

Running the Full Partition D-Flash command a second time will result in the previous partition values and the entire D-Flash memory being erased. The data value written corresponds to the number of 256 byte sectors allocated for either direct D-Flash access (DFPART) or buffer RAM EEE access (ERPART).

ter 26 384 KByte Flash Module (S12XFTM384K2V1)

Offset Module Base + 0x0008

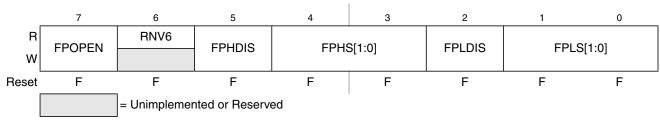

The (unreserved) bits of the FPROT register are writable with the restriction that the size of the protected region can only be increased (see Section 26.3.2.9.1, "P-Flash Protection Restrictions," and Table 26-23).

During the reset sequence, the FPROT register is loaded with the contents of the P-Flash protection byte in the Flash configuration field at global address 0x7F\_FF0C located in P-Flash memory (see Table 26-3) as indicated by reset condition 'F' in Figure 26-13. To change the P-Flash protection that will be loaded during the reset sequence, the upper sector of the P-Flash memory must be unprotected, then the P-Flash protection byte must be reprogrammed. If a double bit fault is detected while reading the P-Flash phrase containing the P-Flash protection byte during the reset sequence, the FPOPEN bit will be cleared and remaining bits in the FPROT register will be set to leave the P-Flash memory fully protected.

Trying to alter data in any protected area in the P-Flash memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. The block erase of a P-Flash block is not possible if any of the P-Flash sectors contained in the same P-Flash block are protected.

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FPOPEN      | <ul> <li>Flash Protection Operation Enable — The FPOPEN bit determines the protection function for program or erase operations as shown in Table 26-20 for the P-Flash block.</li> <li>When FPOPEN is clear, the FPHDIS and FPLDIS bits define unprotected address ranges as specified by the corresponding FPHS and FPLS bits</li> <li>When FPOPEN is set, the FPHDIS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS and FPLS bits</li> </ul> |

| 6<br>RNV[6]      | <b>Reserved Nonvolatile Bit</b> — The RNV bit should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory ending with global address 0x7F_FFF.<br>0 Protection/Unprotection enabled<br>1 Protection/Unprotection disabled                                                                                                                                                                                                                                                                                                      |

| 4–3<br>FPHS[1:0] | <b>Flash Protection Higher Address Size</b> — The FPHS bits determine the size of the protected/unprotected area in P-Flash memory as shown inTable 26-21. The FPHS bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                                                                                                                                                                                            |

| 2<br>FPLDIS      | Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x7F_8000.         0       Protection/Unprotection enabled         1       Protection/Unprotection disabled                                                                                                                                                                                                                                                                             |

| 1–0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 26-22. The FPLS bits can only be written to while the FPLDIS bit is set.                                                                                                                                                                                                                                                                                                                                                                   |

# 27.4.1.4 P-Flash Commands

Table 27-31 summarizes the valid P-Flash commands along with the effects of the commands on the P-Flash block and other resources within the Flash module.

| FCMD | Command                          | Function on P-Flash Memory                                                                                                                                                                                                                                |

|------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks       | Verify that all P-Flash (and D-Flash) blocks are erased.                                                                                                                                                                                                  |

| 0x02 | Erase Verify Block               | Verify that a P-Flash block is erased.                                                                                                                                                                                                                    |

| 0x03 | Erase Verify P-<br>Flash Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                                          |

| 0x04 | Read Once                        | Read a dedicated 64 byte field in the nonvolatile information register in P-Flash block 0 that was previously programmed using the Program Once command.                                                                                                  |

| 0x05 | Load Data Field                  | Load data for simultaneous multiple P-Flash block operations.                                                                                                                                                                                             |

| 0x06 | Program P-Flash                  | Program a phrase in a P-Flash block and any previously loaded phrases for any other P-<br>Flash block (see Load Data Field command).                                                                                                                      |

| 0x07 | Program Once                     | Program a dedicated 64 byte field in the nonvolatile information register in P-Flash block 0 that is allowed to be programmed only once.                                                                                                                  |

| 0x08 | Erase All Blocks                 | Erase all P-Flash (and D-Flash) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the EPDIS and EPOPEN bits in the EPROT register are<br>set prior to launching the command. |

| 0x09 | Erase P-Flash<br>Block           | Erase a single P-Flash block.<br>An erase of the full P-Flash block is only possible when FPLDIS, FPHDIS and FPOPEN<br>bits in the FPROT register are set prior to launching the command.                                                                 |

| 0x0A | Erase P-Flash<br>Sector          | Erase all bytes in a P-Flash sector.                                                                                                                                                                                                                      |

| 0x0B | Unsecure Flash                   | Supports a method of releasing MCU security by erasing all P-Flash (and D-Flash) blocks and verifying that all P-Flash (and D-Flash) blocks are erased.                                                                                                   |

| 0x0C | Verify Backdoor<br>Access Key    | Supports a method of releasing MCU security by verifying a set of security keys.                                                                                                                                                                          |

| 0x0D | Set User Margin<br>Level         | Specifies a user margin read level for all P-Flash blocks.                                                                                                                                                                                                |

| 0x0E | Set Field Margin<br>Level        | Specifies a field margin read level for all P-Flash blocks (special modes only).                                                                                                                                                                          |

| Table 27-31. P-Flash Comm | nands |

|---------------------------|-------|

|---------------------------|-------|

# 27.4.1.5 D-Flash and EEE Commands

Table 27-32 summarizes the valid D-Flash and EEE commands along with the effects of the commands on the D-Flash block and EEE operation.

| FCMD | Command                    | Function on D-Flash Memory                               |

|------|----------------------------|----------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all D-Flash (and P-Flash) blocks are erased. |

| 0x02 | Erase Verify Block         | Verify that the D-Flash block is erased.                 |

Table 27-32. D-Flash Commands

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                             |

|          | ACCERR    | Set if a Load Data Field command sequence is currently active           |

|          |           | Set if command not available in current mode (see Table 28-30)          |

| FSTAT    |           | Set if an invalid DFPART or ERPART selection is supplied                |

|          | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

| FERSTAT  | EPVIOLIF  | None                                                                    |

### Table 28-64. Full Partition D-Flash Command Error Handling

## 28.4.2.16 Erase Verify D-Flash Section Command

The Erase Verify D-Flash Section command will verify that a section of code in the D-Flash user partition is erased. The Erase Verify D-Flash Section command defines the starting point of the data to be verified and the number of words.

Table 28-65. Erase Verify D-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                       |                                                      |  |  |  |  |

|-------------|--------------------------------------------------------|------------------------------------------------------|--|--|--|--|

| 000         | 0x10                                                   | Global address [22:16] to identify the D-Flash block |  |  |  |  |

| 001         | Global address [15:0] of the first word to be verified |                                                      |  |  |  |  |

| 010         | Number of words to be verified                         |                                                      |  |  |  |  |

Upon clearing CCIF to launch the Erase Verify D-Flash Section command, the Memory Controller will verify the selected section of D-Flash memory is erased. The CCIF flag will set after the Erase Verify D-Flash Section operation has completed.

ndix E Detailed Register Address Map

## 0x0030–0x0031 Reserved Register Space

| 0x0030 Reserved | Reserved | R | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|-----------------|----------|---|---|---|---|---|---|---|---|---|

|                 | neserveu | W |   |   |   |   |   |   |   |   |

| 0x0031          | Reserved | R | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|                 |          | W |   |   |   |   |   |   |   |   |

# 0x0032–0x0033 Port Integration Module (PIM) Map 4 of 6

| Address | Name  |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0032  | PORTK | R<br>W | PK7   | PK6   | PK5   | PK4   | PK3   | PK2   | PK1   | PK0   |

| 0x0033  | DDRK  | R<br>W | DDRK7 | DDRK6 | DDRK5 | DDRK4 | DDRK3 | DDRK2 | DDRK1 | DDRK0 |

## 0x0034–0x003F Clock and Reset Generator (CRG) Map

| Address | Name    |        | Bit 7                     | Bit 6 | Bit 5        | Bit 4         | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |

|---------|---------|--------|---------------------------|-------|--------------|---------------|---------|---------|---------|---------|--|

| 0x0034  | SYNR    | R<br>W |                           |       | SYNDIV5      | SYNDIV4       | SYNDIV3 | SYNDIV2 | SYNDIV1 | SYNDIV0 |  |

| 0x0035  | REFDV   | R<br>W |                           |       | REFDIV5      | REFDIV4       | REFDIV3 | REFDIV2 | REFDIV1 | REFDIV0 |  |

| 0x0036  | POSTDIV | R<br>W | 0                         | 0     | 0            | POSTDIV[4:0]] |         |         |         |         |  |

| 0x0037  | CRGFLG  | R<br>W | RTIF                      | PORF  | LVRF         | LOCKIF        | LOCK    | ILAF    | SCMIF   | SCM     |  |

| 0x0038  | CRGINT  | R<br>W | RTIE                      | 0     | 0            | LOCKIE        | 0       | 0       | SCMIE   | 0       |  |

| 0x0039  | CLKSEL  | R<br>W | PLLSEL                    | PSTP  | XCLKS        | 0             | PLLWAI  | 0       | RTIWAI  | COPWAI  |  |

| 0x003A  | PLLCTL  | R<br>W | CME                       | PLLON | FM1          | FM0           | FSTWKP  | PRE     | PCE     | SCME    |  |

| 0x003B  | RTICTL  | R<br>W | RTDEC                     | RTR6  | RTR5         | RTR4          | RTR3    | RTR2    | RTR1    | RTR0    |  |

| 0x003C  | COPCTL  | R<br>W | WCOP                      | RSBCK | 0<br>WRTMASK | 0             | 0       | CR2     | CR1     | CR0     |  |

| 0x003D  | FORBYP  | R      | 0                         | 0     | 0            | 0             | 0       | 0       | 0       | 0       |  |

|         |         | W      | Reserved For Factory Test |       |              |               |         |         |         |         |  |

| 0x003E  | CTCTL   | R      | 0                         | 0     | 0            | 0             | <b></b> | 0       | 0       | 0       |  |

|         |         | W      | Reserved For Factory Test |       |              |               |         |         |         |         |  |

| 0x003F  | ARMCOP  | R      | 0                         | 0     | 0            | 0             | 0       | 0       | 0       | 0       |  |

|         |         | W      | Bit 7                     | 6     | 5            | 4             | 3       | 2       | 1       | Bit 0   |  |