Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HCS12X                                                       |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 50MHz                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI            |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 119                                                          |

| Program Memory Size        | 256КВ (256К х 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 4K x 8                                                       |

| RAM Size                   | 16K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                 |

| Data Converters            | A/D 24x12b                                                   |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 144-LQFP                                                     |

| Supplier Device Package    | 144-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12xet256cag |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | 9    | 5    | 42   | 13   | 4    | 0    | -    | 2    | <i>m</i> | 4    | 10   | 6    | ~    |      | _    | 2    |                  |    |            |            |            |            |     |

|---------|------|------|------|------|------|------|------|------|----------|------|------|------|------|------|------|------|------------------|----|------------|------------|------------|------------|-----|

|         | CANO | CAN1 | CAN2 | CAN3 | CAN4 | SCIO | SCI1 | SCI2 | SC13     | SCI4 | SCI5 | SCI6 | SCI7 | SP10 | SPI1 | SPI2 | E<br>I<br>C<br>0 | l⊡ | <u>cso</u> | <u>CS1</u> | <u>CS2</u> | <u>CS3</u> | TIM |

| PF[0]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    | Х          |            |            |            |     |

| PF[1]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            | Х          |            |            |     |

| PF[2]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            | Х          |            |     |

| PF[3]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            | Х          |     |

| PF[5:4] |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      | Х                |    |            |            |            |            |     |

| PF[7:6] |      |      |      |      |      |      |      |      | Х        |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PH[1:0] |      |      |      |      |      |      |      |      |          |      |      | 0    |      |      | Х    |      |                  |    |            |            |            |            |     |

| PH[3:2] |      |      |      |      |      |      |      |      |          |      |      |      | 0    |      | Х    |      |                  |    |            |            |            |            |     |

| PH[5:4] |      |      |      |      |      |      |      |      |          | 0    |      |      |      |      |      | Х    |                  |    |            |            |            |            |     |

| PH[7:6] |      |      |      |      |      |      |      |      |          |      | 0    |      |      |      |      | Х    |                  |    |            |            |            |            |     |

| PJ[0]   |      |      |      |      |      |      |      | 0    |          |      |      |      |      |      |      |      |                  |    |            |            |            | 0          |     |

| PJ[1]   |      |      |      |      |      |      |      | 0    |          |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PJ[2]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            | 0          |            |            |     |

| PJ[3]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PJ[4]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  | 0  | 0          |            |            |            |     |

| PJ[5]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  | 0  |            |            | 0          |            |     |

| PJ[7:6] | X    |      |      |      | 0    |      |      |      |          |      |      |      |      |      |      |      | 0                |    |            |            |            |            |     |

| PL[1:0] |      |      |      |      |      |      |      |      |          | Х    |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PL[3:2] |      |      |      |      |      |      |      |      |          |      | Х    |      |      |      |      |      |                  |    |            |            |            |            |     |

| PL[5:4] |      |      |      |      |      |      |      |      |          |      |      | Х    |      |      |      |      |                  |    |            |            |            |            |     |

| PL[7:6] |      |      |      |      |      |      |      |      |          |      |      |      | Х    |      |      |      |                  |    |            |            |            |            |     |

| PM[1:0] | 0    |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PM[3:2] | X    | 0    |      |      |      |      |      |      |          |      |      |      |      | х    |      |      |                  |    |            |            |            |            |     |

| PM[5:4] | X    |      | 0    |      | х    |      |      |      |          |      |      |      |      | х    |      |      |                  |    |            |            |            |            |     |

| PM[7:6] |      |      |      | 0    | х    |      |      |      | 0        |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PP[3:0] |      |      |      |      |      |      |      |      |          |      |      |      |      |      | 0    |      |                  |    |            |            |            |            | Х   |

| PP[7:4] |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      | 0    |                  |    |            |            |            |            | х   |

| PR[7:0] |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            |            | 0   |

# Table 1-8. Peripheral - Port Routing Options<sup>(1)</sup>

# Chapter 2 Port Integration Module (S12XEPIMV1)

| Revision<br>Number | Revision Date | Sections<br>Affected      | Description of Changes                                                                                                               |

|--------------------|---------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| V01.17             | 02 Apr 2008   |                           | <ul> <li>Corrected reduced drive strength to 1/5</li> <li>Separated PE1,0 bit descriptions from other PE GPIO</li> </ul>             |

| V01.18             | 25 Nov 2008   | 2.3.19/120<br>2.4.3.4/181 | <ul> <li>Corrected alternative functions on Port K (ACC[2:0])</li> <li>Corrected functions on PE[5] (MODB) and PE[2] (WE)</li> </ul> |

| V01.19             | 18 Dec 2009   |                           | <ul> <li>Added function independency to reduced drive and wired-or bit descriptions</li> <li>Minor corrections</li> </ul>            |

Table 2-1. Revision History

## 2.1 Introduction

### 2.1.1 Overview

The S12XE Family Port Integration Module establishes the interface between the peripheral modules including the non-multiplexed External Bus Interface module (S12X\_EBI) and the I/O pins for all ports. It controls the electrical pin properties as well as the signal prioritization and multiplexing on shared pins.

This document covers:

- Port A and B used as address output of the S12X\_EBI

- Port C and D used as data I/O of the S12X\_EBI

- Port E associated with the S12X\_EBI control signals and the  $\overline{IRQ}$ ,  $\overline{XIRQ}$  interrupt inputs

- Port K associated with address output and control signals of the S12X\_EBI

- Port T associated with 1 ECT module

- Port S associated with 2 SCI and 1 SPI modules

- Port M associated with 4 MSCAN and 1 SCI module

- Port P connected to the PWM and 2 SPI modules inputs can be used as an external interrupt source

- Port H associated with 4 SCI modules inputs can be used as an external interrupt source

- Port J associated with 1 MSCAN, 1 SCI, 2 IIC modules and chip select outputs inputs can be used as an external interrupt source

- Port AD0 and AD1 associated with two 16-channel ATD modules

- Port R associated with 1 standard timer (TIM) module

- Port L associated with 4 SCI modules

# 2.3.37 Port M Data Register (PTM)

Address 0x0250

#### Access: User read/write<sup>(1)</sup>

|          | 7        | 6        | 5        | 4        | 3                  | 2        | 1      | 0      |

|----------|----------|----------|----------|----------|--------------------|----------|--------|--------|

| R<br>W   | PTM7     | PTM6     | PTM5     | PTM4     | РТМ3               | PTM2     | PTM1   | PTM0   |

| Altern.  | TXCAN3   | RXCAN3   | TXCAN2   | RXCAN2   | TXCAN1             | RXCAN1   | TXCAN0 | RXCAN0 |

| Function | —        | _        | (TXCAN0) | (RXCAN0) | (TXCAN0)           | (RXCAN0) | —      | _      |

|          | (TXCAN4) | (RXCAN4) | (TXCAN4) | (RXCAN4) | —                  | —        | —      | _      |

| -        | _        | —        | (SCK0)   | (MOSI0)  | ( <del>SSO</del> ) | (MISO0)  | _      | _      |

|          | TXD3     | RXD3     | —        | —        | _                  | —        | _      | _      |

| Reset    | 0        | 0        | 0        | 0        | 0                  | 0        | 0      | 0      |

Figure 2-35. Port M Data Register (PTM)

1. Read: Anytime.

Write: Anytime.

#### Table 2-33. PTM Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6<br>PTM | Port M general purpose input/output data—Data Register<br>Port M pins 7 and 6 are associated with TXCAN and RXCAN signals of CAN3 and the routed CAN4, as well as with<br>TXD and RXD signals of SCI3, respectively.<br>The CAN3 function takes precedence over the CAN4, SCI3 and the general purpose I/O function if the CAN3 module<br>is enabled. The CAN4 function takes precedence over the SCI3 and the general purpose I/O function if the CAN4<br>module is enabled. The SCI3 function takes precedence over the general purpose I/O function if the SCI3 module<br>is enabled. When not used with the alternative function, this pin can be used as general purpose I/O.<br>If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the<br>buffered pin input state is read.                                                                                                                                                                                                                                                                                                           |

| 5<br>PTM   | Port M general purpose input/output data—Data Register<br>Port M pin 5 is associated with the TXCAN signal of CAN2 and the routed CAN4 and CAN0, as well as with SCK<br>signals of SPI0.<br>The CAN2 function takes precedence over the routed CAN0, routed CAN4, the routed SPI0 and the general purpose<br>I/O function if the CAN2 module is enabled. The routed CAN0 function takes precedence over the routed CAN4, the<br>routed SPI0 and the general purpose I/O function if the routed CAN0 module is enabled. The routed CAN4 function<br>takes precedence over the routed SPI0 and general purpose I/O function if the routed CAN4 module is enabled. The<br>routed SPI0 function takes precedence of the general purpose I/O function if the routed SPI0 is enabled. The<br>routed SPI0 function takes precedence of the general purpose I/O function if the routed SPI0 is enabled.<br>When not used with the alternative function, this pin can be used as general purpose I/O.<br>If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the<br>buffered pin input state is read. |

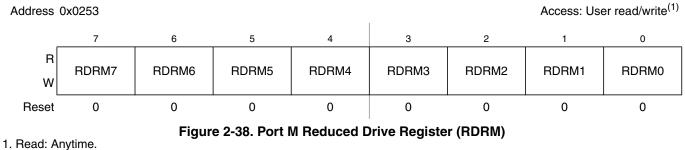

# 2.3.40 Port M Reduced Drive Register (RDRM)

Write: Anytime.

#### Table 2-36. RDRM Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>RDRM | <ul> <li>Port M reduced drive—Select reduced drive for outputs</li> <li>This register configures the drive strength of Port M output pins 7 through 0 as either full or reduced independent of the function used on the pins. If a pin is used as input this bit has no effect.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength).</li> <li>0 Full drive strength enabled.</li> </ul> |

## 2.3.41 Port M Pull Device Enable Register (PERM)

Address 0x0254

Access: User read/write<sup>(1)</sup>

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | PERM7 | PERM6 | PERM5 | PERM4 | PERM3 | PERM2 | PERM1 | PERM0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Figure 2-39. Port M Pull Device Enable Register (PERM)

1. Read: Anytime. Write: Anytime.

#### Table 2-37. PERM Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PERM | <ul> <li>Port M pull device enable—Enable pull-up devices on input pins</li> <li>These bits configure whether a pull device is activated, if the associated pin is used as an input or wired-or output.</li> <li>This bit has no effect if the pin is used as push-pull output. Out of reset no pull device is enabled.</li> <li>1 Pull device enabled.</li> <li>0 Pull device disabled.</li> </ul> |

#### Iter 8 S12X Debug (S12XDBGV3) Module

S12X tagging is disabled when the BDM becomes active. XGATE tagging is possible when the BDM is active.

## 8.4.6.1 External Tagging using TAGHI and TAGLO

External tagging using the external TAGHI and TAGLO pins can only be used to tag CPU12X opcodes; tagging of XGATE code using these pins is not possible. An external tag triggers the state sequencer into state0 when the tagged opcode reaches the execution stage of the instruction queue.

The pins operate independently, thus the state of one pin does not affect the function of the other. External tagging is possible in emulation modes only. The presence of logic level 0 on either pin at the rising edge of the external clock (ECLK) performs the function indicated in the Table 8-47. It is possible to tag both bytes of an instruction word. If a taghit occurs, a breakpoint can be generated as defined by the DBGBRK and BDM bits in DBGC1. Each time TAGHI or TAGLO are low on the rising edge of ECLK, the old tag is replaced by a new one.

| TAGHI | TAGLO | Tag        |  |  |  |

|-------|-------|------------|--|--|--|

| 1     | 1     | No tag     |  |  |  |

| 1     | 0     | Low byte   |  |  |  |

| 0     | 1     | High byte  |  |  |  |

| 0     | 0     | Both bytes |  |  |  |

Table 8-47. Tag Pin Function

### 8.4.6.2 Unconditional Tagging Function

In emulation modes a low assertion of PE5/TAGLO/MODA in the 7th or 8th bus cycle after reset enables the unconditional tagging function, allowing immediate tagging via TAGHI/TAGLO with breakpoint to BDM independent of the ARM, BDM and DBGBRK bits. Conversely these bits are not affected by unconditional tagging. The unconditional tagging function remains enabled until the next reset. This function allows an immediate entry to BDM in emulation modes before user code execution. The TAGLO assertion must be in the 7th or 8th bus cycle following the end of reset, whereby the prior RESET pin assertion lasts the full 192 bus cycles.

## 8.4.7 Breakpoints

Breakpoints can be generated as follows.

- Through XGATE software breakpoint requests.

- From comparator channel triggers to final state.

- Using software to write to the TRIG bit in the DBGC1 register.

- From taghits generated using the external TAGHI and TAGLO pins.

Breakpoints generated by the XGATE module or via the BDM BACKGROUND command have no affect on the CPU12X in STOP or WAIT mode.

### Add Immediate 8 bit Constant (High Byte)

#### Operation

RD + IMM8:\$00  $\Rightarrow RD$

ADDH

Adds the content of high byte of register RD and a signed immediate 8 bit constant using binary addition and stores the result in the high byte of the destination register RD. This instruction can be used after an ADDL for a 16 bit immediate addition.

Example:

| ADDL | R2,#LOWBYTE  |   |    |   |    |   |    |     |           |

|------|--------------|---|----|---|----|---|----|-----|-----------|

| ADDH | R2,#HIGHBYTE | ; | R2 | = | R2 | + | 16 | bit | immediate |

#### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | Δ | Δ |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: Set if a two's complement overflow resulted from the operation; cleared otherwise. RD[15]<sub>old</sub> & IMM8[7] & RD[15]<sub>new</sub> | RD[15]<sub>old</sub> & IMM8[7] & RD[15]<sub>new</sub>

- C: Set if there is a carry from the bit 15 of the result; cleared otherwise. RD[15]<sub>old</sub> & IMM8[7] | RD[15]<sub>old</sub> & RD[15]<sub>new</sub> | IMM8[7] & RD[15]<sub>new</sub>

#### Code and CPU Cycles

| Source Form    | Address<br>Mode |   |                   |  |  |  | Machin | e Code | Cycles |

|----------------|-----------------|---|-------------------|--|--|--|--------|--------|--------|

| ADDH RD, #IMM8 | IMM8            | 1 | 1 1 1 0 1 RD IMM8 |  |  |  |        |        | Р      |

Logical AND Immediate 8 bit Constant (High Byte)

### Operation

$RD.H \& IMM8 \Rightarrow RD.H$

Performs a bit wise logical AND between the high byte of register RD and an immediate 8 bit constant and stores the result in the destination register RD.H. The low byte of RD is not affected.

### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | 0 |   |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the 8 bit result is \$00; cleared otherwise.

- V: 0; cleared.

- C: Not affected.

### Code and CPU Cycles

| Source Form    | Address<br>Mode | Machine Code |   | e Code | Cycles |   |    |      |   |

|----------------|-----------------|--------------|---|--------|--------|---|----|------|---|

| ANDH RD, #IMM8 | IMM8            | 1            | 0 | 0      | 0      | 1 | RD | IMM8 | Р |

### 11.4.1.3 Clock Monitor (CM)

If no OSCCLK edges are detected within a certain time, the clock monitor within the oscillator block generates a clock monitor fail event. The S12XECRG then asserts self clock mode or generates a system reset depending on the state of SCME bit. If the clock monitor is disabled or the presence of clocks is detected no failure is indicated by the oscillator block. The clock monitor function is enabled/disabled by the CME control bit.

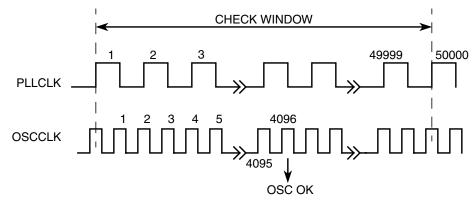

### 11.4.1.4 Clock Quality Checker

The clock monitor performs a coarse check on the incoming clock signal. The clock quality checker provides a more accurate check in addition to the clock monitor.

A clock quality check is triggered by any of the following events:

- Power on reset (*POR*)

- Low voltage reset (*LVR*)

- Wake-up from Full Stop Mode (*exit full stop*)

- Clock Monitor fail indication (CM fail)

A time window of 50000 PLLCLK cycles<sup>1</sup> is called *check window*.

A number greater equal than 4096 rising OSCCLK edges within a *check window* is called *osc ok*. Note that *osc ok* immediately terminates the current *check window*. See Figure 11-17 as an example.

Figure 11-17. Check Window Example

1. IPLL is running at self clock mode frequency  $\mathrm{f}_{\mathrm{SCM}}.$

ter 13 Analog-to-Di

ter 13 Analog-to-Digital Converter (ADC12B16CV1)

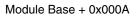

## 13.3.2.9 ATD Status Register 2 (ATDSTAT2)

This read-only register contains the Conversion Complete Flags CCF[15:0].

#### Read: Anytime

Write: Anytime, no effect

| Table 13-19. | ATDSTAT2 | Field | Descriptions |

|--------------|----------|-------|--------------|

| 14010 10 101 |          |       |              |

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>CCF[15:0] | <b>Conversion Complete Flag</b> <i>n</i> ( <i>n</i> = 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — A conversion complete flag is set at the end of each conversion in a sequence. The flags are associated with the conversion position in a sequence (and also the result register number). Therefore in non-fifo mode, CCF[8] is set when the ninth conversion in a sequence is complete and the result is available in result register ATDDR8; CCF[9] is set when the tenth conversion in a sequence is complete and the result is available in ATDDR9, and so forth.                                                                                                                                                                              |

|                   | If automatic compare of conversion results is enabled (CMPE[ <i>n</i> ]=1 in ATDCMPE), the conversion complete flag<br>is only set if comparison with ATDDR <i>n</i> is true and if ACMPIE=1 a compare interrupt will be requested. In this<br>case, as the ATDDR <i>n</i> result register is used to hold the compare value, the result will not be stored there at the<br>end of the conversion but is lost.<br>A flag CCF[ <i>n</i> ] is cleared when one of the following occurs:<br>A) Write to ATDCTL5 (a new conversion sequence is started)<br>B) If AFFC=0, write "1" to CCF[ <i>n</i> ]<br>C) If AFFC=1 and CMPE[ <i>n</i> ]=0, read of result register ATDDR <i>n</i><br>D) If AFFC=1 and CMPE[ <i>n</i> ]=1, write to result register ATDDR <i>n</i> |

|                   | <ul> <li>In case of a concurrent set and clear on CCF[n]: The clearing by method A) will overwrite the set. The clearing by methods B) or C) or D) will be overwritten by the set.</li> <li>0 Conversion number n not completed or successfully compared</li> <li>1 If (CMPE[n]=0): Conversion number n has completed. Result is ready in ATDDRn.<br/>If (CMPE[n]=1): Compare for conversion result number n with compare value in ATDDRn, using compare operator CMPGT[n] is true. (No result available in ATDDRn)</li> </ul>                                                                                                                                                                                                                                   |

## 14.4.3.5 Pulse Accumulator A Overflow Interrupt

This active high output will be asserted by the module to request a timer pulse accumulator A overflow interrupt to be serviced by the system controller.

## 14.4.3.6 Timer Overflow Interrupt

This active high output will be asserted by the module to request a timer overflow interrupt to be serviced by the system controller.

| Register | Error Bit | Error Condition |

|----------|-----------|-----------------|

| FERSTAT  | EPVIOLIF  | None            |

#### Table 25-38. Erase Verify P-Flash Section Command Error Handling

### 25.4.2.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash block 0. The Read Once field is programmed using the Program Once command described in Section 25.4.2.7. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                         |  |  |

|-------------|------------------------------------------|--|--|

| 000         | 0x04 Not Required                        |  |  |

| 001         | Read Once phrase index (0x0000 - 0x0007) |  |  |

| 010         | Read Once word 0 value                   |  |  |

| 011         | Read Once word 1 value                   |  |  |

| 100         | Read Once word 2 value                   |  |  |

| 101         | Read Once word 3 value                   |  |  |

Table 25-39. Read Once Command FCCOB Requirements

Upon clearing CCIF to launch the Read Once command, a Read Once phrase is fetched and stored in the FCCOB indexed register. The CCIF flag will set after the Read Once operation has completed. Valid phrase index values for the Read Once command range from 0x0000 to 0x0007. During execution of the Read Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

| Register | Error Bit | Error Condition                                                         |  |

|----------|-----------|-------------------------------------------------------------------------|--|

|          | 100500    | Set if CCOBIX[2:0] != 001 at command launch                             |  |

|          |           | Set if a Load Data Field command sequence is currently active           |  |

|          | ACCERR    | Set if command not available in current mode (see Table 25-30)          |  |

| FSTAT    |           | Set if an invalid phrase index is supplied                              |  |

|          | FPVIOL    | None                                                                    |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |

| FERSTAT  | EPVIOLIF  | None                                                                    |  |

Table 25-40. Read Once Command Error Handling

### 25.4.2.5 Load Data Field Command

The Load Data Field command is executed to provide FCCOB parameters for multiple P-Flash blocks for a future simultaneous program operation in the P-Flash memory space.

ter 26 384 KByte Flash Module (S12XFTM384K2V1)

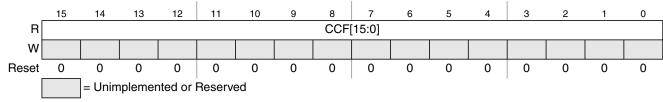

Figure 26-3. EEE Resource Memory Map

The Full Partition D-Flash command (see Section 26.4.2.15) is used to program the EEE nonvolatile information register fields where address  $0x12\_0000$  defines the D-Flash partition for user access and address  $0x12\_0004$  defines the buffer RAM partition for EEE operations.

## 28.4.1.4 P-Flash Commands

Table 28-31 summarizes the valid P-Flash commands along with the effects of the commands on the P-Flash block and other resources within the Flash module.

| FCMD | Command                          | Function on P-Flash Memory                                                                                                                                                                                                                                |

|------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks       | Verify that all P-Flash (and D-Flash) blocks are erased.                                                                                                                                                                                                  |

| 0x02 | Erase Verify Block               | Verify that a P-Flash block is erased.                                                                                                                                                                                                                    |

| 0x03 | Erase Verify P-<br>Flash Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                                          |

| 0x04 | Read Once                        | Read a dedicated 64 byte field in the nonvolatile information register in P-Flash block 0 that was previously programmed using the Program Once command.                                                                                                  |

| 0x05 | Load Data Field                  | Load data for simultaneous multiple P-Flash block operations.                                                                                                                                                                                             |

| 0x06 | Program P-Flash                  | Program a phrase in a P-Flash block and any previously loaded phrases for any other P-<br>Flash block (see Load Data Field command).                                                                                                                      |

| 0x07 | Program Once                     | Program a dedicated 64 byte field in the nonvolatile information register in P-Flash block 0 that is allowed to be programmed only once.                                                                                                                  |

| 0x08 | Erase All Blocks                 | Erase all P-Flash (and D-Flash) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the EPDIS and EPOPEN bits in the EPROT register are<br>set prior to launching the command. |

| 0x09 | Erase P-Flash<br>Block           | Erase a single P-Flash block.<br>An erase of the full P-Flash block is only possible when FPLDIS, FPHDIS and FPOPEN<br>bits in the FPROT register are set prior to launching the command.                                                                 |

| 0x0A | Erase P-Flash<br>Sector          | Erase all bytes in a P-Flash sector.                                                                                                                                                                                                                      |

| 0x0B | Unsecure Flash                   | Supports a method of releasing MCU security by erasing all P-Flash (and D-Flash) blocks and verifying that all P-Flash (and D-Flash) blocks are erased.                                                                                                   |

| 0x0C | Verify Backdoor<br>Access Key    | Supports a method of releasing MCU security by verifying a set of security keys.                                                                                                                                                                          |

| 0x0D | Set User Margin<br>Level         | Specifies a user margin read level for all P-Flash blocks.                                                                                                                                                                                                |

| 0x0E | Set Field Margin<br>Level        | Specifies a field margin read level for all P-Flash blocks (special modes only).                                                                                                                                                                          |

| Table 28- | 31. P-Flash | Commands |

|-----------|-------------|----------|

|-----------|-------------|----------|

## 28.4.1.5 D-Flash and EEE Commands

Table 28-32 summarizes the valid D-Flash and EEE commands along with the effects of the commands on the D-Flash block and EEE operation.

| FCMD | Command                    | Function on D-Flash Memory                               |

|------|----------------------------|----------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all D-Flash (and P-Flash) blocks are erased. |

| 0x02 | Erase Verify Block         | Verify that the D-Flash block is erased.                 |

# 29.2 External Signal Description

The Flash module contains no signals that connect off-chip.

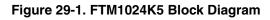

Figure 29-2. P-Flash Memory Map

MC9S12XE-Family Reference Manual Rev. 1.25

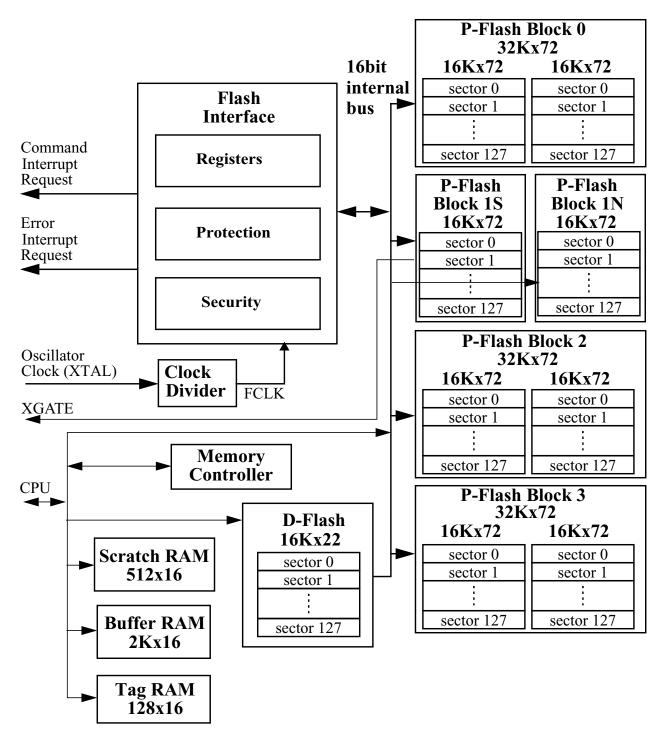

ter 29 1024 KByte Flash Module (S12XFTM1024K5V2)

- Program a duplicate DFPART to the EEE nonvolatile information register at global address 0x12\_0002 (see Table 29-7)

- Program ERPART to the EEE nonvolatile information register at global address 0x12\_0004 (see Table 29-7)

- Program a duplicate ERPART to the EEE nonvolatile information register at global address 0x12\_0006 (see Table 29-7)

The D-Flash user partition will start at global address  $0x10_{0000}$ . The buffer RAM EEE partition will end at global address  $0x13_{FFF}$ . After the Partition D-Flash operation has completed, the CCIF flag will set.

Running the Partition D-Flash command a second time will result in the ACCERR bit within the FSTAT register being set. The data value written corresponds to the number of 256 byte sectors allocated for either direct D-Flash access (DFPART) or buffer RAM EEE access (ERPART).

| Register | Error Bit | Error Condition                                                         |  |

|----------|-----------|-------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                             |  |

|          |           | Set if a Load Data Field command sequence is currently active           |  |

|          |           | Set if command not available in current mode (see Table 29-30)          |  |

| FSTAT    |           | Set if partitions have already been defined                             |  |

| FSTAI    |           | Set if an invalid DFPART or ERPART selection is supplied                |  |

|          | FPVIOL    | None                                                                    |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |

| FERSTAT  | EPVIOLIF  | None                                                                    |  |

Table 29-78. Partition D-Flash Command Error Handling

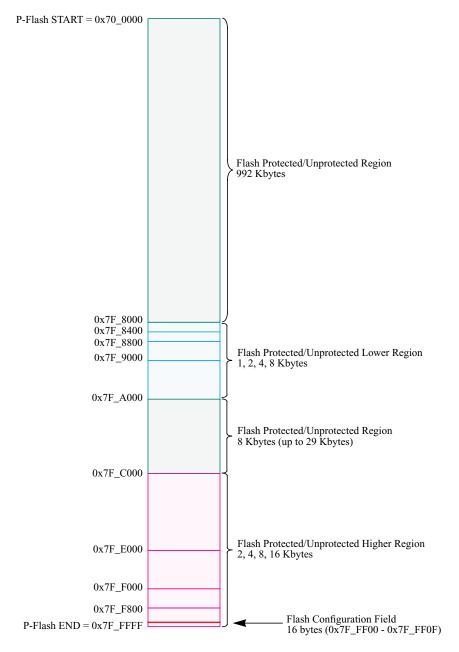

Figure 29-27. Flash Module Interrupts Implementation

### 29.4.4 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 29.4.3, "Interrupts").

### 29.4.5 Stop Mode

If a Flash command is active (CCIF = 0) or an EE-Emulation operation is pending when the MCU requests stop mode, the current Flash operation will be completed before the CPU is allowed to enter stop mode.

## 29.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 29-12). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x7F\_FF0F.

#### Table A-8. 5V I/O Characteristics

| Conditions are 4.5 V < $V_{DD35}$ < 5.5 V temperature from -40°C to +150°C, unless otherwise noted I/O Characteristics for all I/O pins except EXTAL, XTAL, TEST and supply pins. |   |                                                                                   |                   |   |   |   |      |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------|-------------------|---|---|---|------|--|--|

| 16                                                                                                                                                                                | D | Port H, J, P interrupt input pulse passed (STOP) t <sub>PULSE</sub> 4 — —         |                   |   |   |   |      |  |  |

| 17                                                                                                                                                                                | D | IRQ pulse width, edge-sensitive mode (STOP)                                       | PW <sub>IRQ</sub> | 1 | _ | _ | tcyc |  |  |

| 18                                                                                                                                                                                |   | D     XIRQ pulse width with X-bit set (STOP)     PW <sub>XIRQ</sub> 4     -     - |                   |   |   |   |      |  |  |

Maximum leakage current occurs at maximum operating temperature.

Refer to Section A.1.4, "Current Injection" for more details

Parameter only applies in stop or pseudo stop mode.

ndix E Detailed Register Address Map

# 0x0380–0x03BF XGATE Map (Sheet 1 of 3)

| Address | Name     |             | Bit 7   | Bit 6       | Bit 5   | Bit 4   | Bit 3       | Bit 2   | Bit 1       | Bit 0    |  |  |

|---------|----------|-------------|---------|-------------|---------|---------|-------------|---------|-------------|----------|--|--|

|         |          | R           | 0       | 0           | 0       | 0       | 0           | 0       | 0           |          |  |  |

| 0x0380  | XGMCTL   | W           | XGEM    | XGFRZM      | XGDBGM  | XGSSM   | XGFACTM     |         | XGS<br>WEFM | XGIEM    |  |  |

| 0x0381  | XGMCTL   | R<br>W      | XGE     | XGFRZ       | XGDBG   | XGSS    | XGFACT      | 0       | XGSWEF      | XGIE     |  |  |

| 0x0382  | XGCHID   | R           | 0       |             |         | 2       | XGCHID[6:0] | ]       |             |          |  |  |

| 0x0383  | XGCHPL   | W<br>R<br>W | 0       | 0           | 0       | 0       | 0           | XGCHPL  | 0           | 0        |  |  |

| 0x0384  | Reserved |             |         |             |         |         |             |         |             |          |  |  |

| 0x0385  | XGISPSEL | R<br>W      | 0       | 0           | 0       | 0       | 0           | 0       | XGISPS      | SEL[1:0] |  |  |

| 0x0386  | XGVBR    | R<br>W      |         | XGVBR[15:8] |         |         |             |         |             |          |  |  |

| 0x0387  | XGVBR    | R<br>W      |         | XGVBR[7:1]  |         |         |             |         |             |          |  |  |

| 0x0388  | XGIF     | R<br>W      | 0       | 0           | 0       | 0       | 0           | 0       | 0           | XGIF_78  |  |  |

| 0x0389  | XGIF     | R<br>W      | XGIF_77 | XGIF_76     | XGIF_75 | XGIF_74 | XGIF_73     | XGIF_72 | XGIF_71     | XGIF_70  |  |  |

| 0x038A  | XGIF     | R<br>W      | XGIF_6F | XGIF_6E     | XGIF_6D | XGIF_6C | XGIF_6B     | XGIF_6A | XGIF_69     | XGIF_68  |  |  |

| 0x023B  | XGIF     | R<br>W      | XGIF_67 | XGIF_66     | XGIF_65 | XGIF_64 | XGIF_63     | XGIF_62 | XGIF_61     | XGIF_60  |  |  |

| 0x023C  | XGIF     | R<br>W      | XGIF_5F | XGIF_5E     | XGIF_5D | XGIF_5C | XGIF_5B     | XGIF_5A | XGIF_59     | XGIF_58  |  |  |

| 0x038D  | XGIF     | R<br>W      | XGIF_57 | XGIF_56     | XGIF_55 | XGIF_54 | XGIF_53     | XGIF_52 | XGIF_51     | XGIF_50  |  |  |

| 0x038E  | XGIF     | R<br>W      | XGIF_4F | XGIF_4E     | XGIF_4D | XGIF_4C | XGIF_4B     | XGIF_4A | XGIF_49     | XGIF_48  |  |  |

| 0x038F  | XGIF     | R<br>W      | XGIF_47 | XGIF_46     | XGIF_45 | XGIF_44 | XGIF_43     | XGIF_42 | XGIF_41     | XGIF_40  |  |  |

| 0x0390  | XGIF     | R<br>W      | XGIF_3F | XGIF_3E     | XGIF_3D | XGIF_3C | XGIF_3B     | XGIF_3A | XGIF_39     | XGIF_38  |  |  |

| 0x0391  | XGIF     | R<br>W      | XGIF_37 | XGIF_36     | XGIF_35 | XGIF_34 | XGIF_33     | XGIF_32 | XGIF_31     | XGIF_30  |  |  |

| 0x0392  | XGIF     | R<br>W      | XGIF_2F | XGIF_2E     | XGIF_2D | XGIF_2C | XGIF_2B     | XGIF_2A | XGIF_29     | XGIF_28  |  |  |

| 0x0393  | XGIF     | R<br>W      | XGIF_27 | XGIF_26     | XGIF_25 | XGIF_24 | XGIF_23     | XGIF_22 | XGIF_21     | XGIF_20  |  |  |

| 0x0394  | XGIF     | R<br>W      | XGIF_1F | XGIF_1E     | XGIF_1D | XGIF_1C | XGIF_1B     | XGIF_1A | XGIF_19     | XGIF_18  |  |  |

| 0x0395  | XGIF     | R<br>W      | XGIF_17 | XGIF_16     | XGIF_15 | XGIF_14 | XGIF_13     | XGIF_12 | XGIF_11     | XGIF_10  |  |  |

MC9S12XE-Family Reference Manual Rev. 1.25

### 0x03D0–0x03FF Timer Module (TIM) Map (Sheet 2 of 2)

| Address           | Name     |        | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|-------------------|----------|--------|---------|---------|---------|---------|---------|---------|--------|--------|

| 0x03E4            | TC2H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03E5            | TC2L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03E6            | тсзн     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03E7            | TC3L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03E8            | TC4H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03E9            | TC4L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03EA            | TC5H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03EB            | TC5L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03EC            | TC6H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03ED            | TC6L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03EE            | TC7H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03EF            | TC7L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03F0            | PACTL    | R<br>W | 0       | PAEN    | PAMOD   | PEDGE   | CLK1    | CLK0    | PAOVI  | PAI    |

| 0x03F1            | PAFLG    | R<br>W | 0       | 0       | 0       | 0       | 0       | 0       | PAOVF  | PAIF   |

| 0x03F2            | PACNTH   | R<br>W | PACNT15 | PACNT14 | PACNT13 | PACNT12 | PACNT11 | PACNT10 | PACNT9 | PACNT8 |

| 0x03F3            | PACNTL   | R<br>W | PACNT7  | PACNT6  | PACNT5  | PACNT4  | PACNT3  | PACNT2  | PACNT1 | PACNT0 |

| 0x03F4–<br>0x03FB | Reserved | R<br>W |         | 0       | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x03FC            | OCPD     | R<br>W | OCPD7   | OCPD6   | OCPD5   | OCPD4   | OCPD3   | OCPD2   | OCPD1  | OCPD0  |

| 0x03FD            | Reserved | R<br>W |         |         |         |         |         |         |        |        |

| 0x03FE            | PTPSR    | R<br>W | PTPSR7  | PTPSR6  | PTPSR5  | PTPSR4  | PTPSR3  | PTPSR2  | PTPSR1 | PTPSR0 |

| 0x03FF            | Reserved | R<br>W |         |         |         |         |         |         |        |        |