Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xea128j2caa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2.3.7 PA[7:0] / ADDR[15:8] / IVD[15:8] — Port A I/O Pins

PA[7:0] are general-purpose input or output pins. In MCU expanded modes of operation, these pins are used for the external address bus. In MCU emulation modes of operation, these pins are used for external address bus and internal visibility read data.

## 1.2.3.8 PB[7:1] / ADDR[7:1] / IVD[7:1] — Port B I/O Pins

PB[7:1] are general-purpose input or output pins. In MCU expanded modes of operation, these pins are used for the external address bus. In MCU emulation modes of operation, these pins are used for external address bus and internal visibility read data.

## 1.2.3.9 PB0 / ADDR0 / UDS / IVD[0] — Port B I/O Pin 0

PB0 is a general-purpose input or output pin. In MCU expanded modes of operation, this pin is used for the external address bus ADDR0 or as upper data strobe signal. In MCU emulation modes of operation, this pin is used for external address bus ADDR0 and internal visibility read data IVD0.

## 1.2.3.10 PC[7:0] / DATA [15:8] — Port C I/O Pins

PC[7:0] are general-purpose input or output pins. In MCU expanded modes of operation, these pins are used for the external data bus.

The input voltage thresholds for PC[7:0] can be configured to reduced levels, to allow data from an external 3.3-V peripheral to be read by the MCU operating at 5.0 V. The input voltage thresholds for PC[7:0] are configured to reduced levels out of reset in expanded and emulation modes. The input voltage thresholds for PC[7:0] are configured to 5-V levels out of reset in normal modes.

## 1.2.3.11 PD[7:0] / DATA [7:0] — Port D I/O Pins

PD[7:0] are general-purpose input or output pins. In MCU expanded modes of operation, these pins are used for the external data bus.

The input voltage thresholds for PD[7:0] can be configured to reduced levels, to allow data from an external 3.3-V peripheral to be read by the MCU operating at 5.0 V. The input voltage thresholds for PD[7:0] are configured to reduced levels out of reset in expanded and emulation modes. The input voltage thresholds for PC[7:0] are configured to 5-V levels out of reset in normal modes.

## 1.2.3.12 PE7 / ECLKX2 / XCLKS — Port E I/O Pin 7

PE7 is a general-purpose input or output pin. ECLKX2 is a free running clock of twice the internal bus frequency, available by default in emulation modes and when enabled in other modes. The  $\overline{\text{XCLKS}}$  is an input signal which controls whether a crystal in combination with the internal loop controlled Pierce oscillator is used or whether full swing Pierce oscillator/external clock circuitry is used (refer to Oscillator Configuration). An internal pullup is enabled during reset.

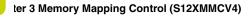

Figure 3-17. Expansion of the Local Address Map

ter 4 Memory Protection Unit (S12XMPUV1)

## 4.3.1 Register Descriptions

This section describes in address order all the MPU module registers and their individual bits.

| Register<br>Name                        |                    | Bit 7           | 6     | 5     | 4       | 3           | 2       | 1           | Bit 0 |  |

|-----------------------------------------|--------------------|-----------------|-------|-------|---------|-------------|---------|-------------|-------|--|

| 0x0000                                  | R                  | AEF             | WPF   | NEXF  | 0       | 0           | 0       | 0           | SVSF  |  |

| MPUFLG                                  | w                  |                 |       |       |         |             |         |             |       |  |

| 0x0001                                  | R                  | 0               |       |       |         | ADDR[22:16] |         |             |       |  |

| MPUASTAT0                               | w                  |                 |       |       |         |             |         |             |       |  |

| 0x0002                                  | R                  |                 |       |       | ADDR    | [15:8]      |         |             |       |  |

| MPUASTAT1                               | w                  |                 |       |       |         |             |         |             |       |  |

| 0x0003                                  | R                  |                 |       |       | ADDF    | R[7:0]      |         |             |       |  |

| MPUASTAT2                               | w                  |                 |       |       |         |             |         |             |       |  |

| 0x0004                                  | R                  | 0               | 0     | 0     | 0       | 0           | 0       | 0           | 0     |  |

| Reserved                                | w                  |                 |       |       |         |             |         |             |       |  |

| 0x0005                                  | R<br>W             | SVSEN           | 0     | 0     | 0       | 0           |         | SEI [2:0]   |       |  |

| MPUSEL                                  |                    | SVSEN           |       |       |         | SEL[2:0]    |         |             |       |  |

| 0x0006                                  | R                  | MSTR0           | MSTR1 | MSTR2 | MSTR3   |             | LOW_AD  |             |       |  |

| MPUDESC0 <sup>(1)</sup>                 | w                  | Morrio          | WOTT  | MOTTE | MOTIO   |             |         | טוונצב. וטן |       |  |

| 0x0007                                  | R                  | LOW_ADDR[18:11] |       |       |         |             |         |             |       |  |

| MPUDESC1 <sup>1</sup>                   | w                  |                 |       |       |         |             |         |             |       |  |

| 0x0008<br>MPUDESC2 <sup>1</sup>         | R                  |                 |       |       | LOW_AD  | DB[10:3]    |         |             |       |  |

| MPUDE502                                | w                  |                 |       |       |         |             |         |             |       |  |

| 0x0009                                  | R                  | WP              | NEX   | 0     | 0       |             | HIGH_AD | DR[22:19]   |       |  |

| MPUDESC3 <sup>1</sup>                   | w                  |                 |       |       |         |             |         |             |       |  |

| 0x000A                                  | R HIGH_ADDR[18:11] |                 |       |       |         |             |         |             |       |  |

| MPUDESC4 <sup>1</sup>                   | w                  |                 |       |       |         |             |         |             |       |  |

| 0x000B                                  | R                  |                 |       |       | HIGH_AD | DR[10:3]    |         |             |       |  |

| MPUDESC5 <sup>1</sup> W HIGH_ADDR[10:3] |                    |                 |       |       |         |             |         |             |       |  |

|                                         |                    |                 |       |       |         |             |         |             |       |  |

= Unimplemented or Reserved 1. The module addresses 0x0006–0x000B represent a window in the register map through which different descriptor registers are visible.

#### Figure 4-2. MPU Register Summary

ter 6 Interrupt (S12XINTV2)

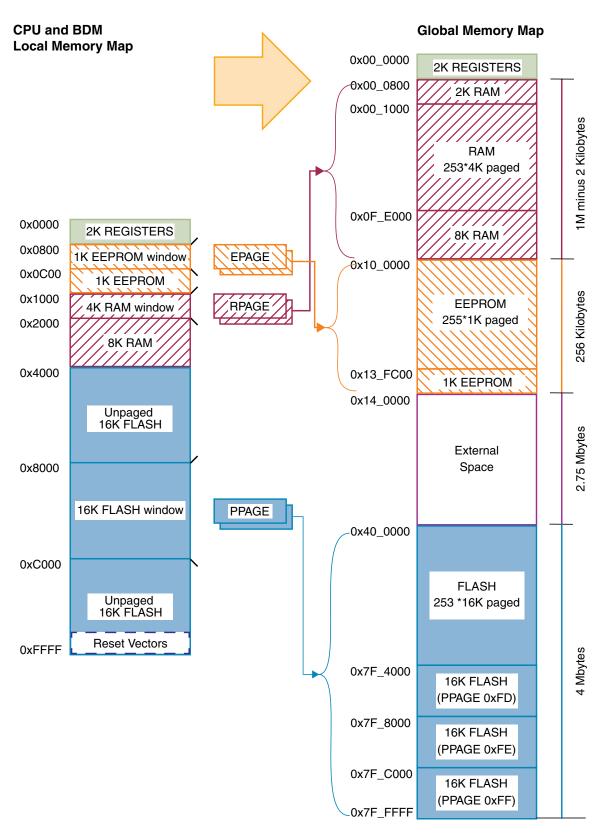

## 6.1.4 Block Diagram

Figure 6-1 shows a block diagram of the XINT module.

## 6.2 External Signal Description

The XINT module has no external signals.

# Chapter 8 S12X Debug (S12XDBGV3) Module

| Revision<br>Number | Revision Date | Sections<br>Affected           | Description of Changes                                                                                                                              |

|--------------------|---------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| V03.20             | 14 Sep 2007   | 8.3.2.7/8-317                  | - Clarified reserved State Sequencer encodings.                                                                                                     |

| V03.21             | 23 Oct 2007   | 8.4.2.2/8-329<br>8.4.2.4/8-330 | <ul> <li>Added single databyte comparison limitation information</li> <li>Added statement about interrupt vector fetches whilst tagging.</li> </ul> |

| V03.22             | 12 Nov 2007   | 8.4.5.2/8-334<br>8.4.5.5/8-341 | <ul> <li>Removed LOOP1 tracing restriction NOTE.</li> <li>Added pin reset effect NOTE.</li> </ul>                                                   |

| V03.23             | 13 Nov 2007   | General                        | - Text readability improved, typo removed.                                                                                                          |

| V03.24             | 04 Jan 2008   | 8.4.5.3/8-336                  | - Corrected bit name.                                                                                                                               |

| V03.25             | 14 May 2008   | General                        | - Updated Revision History Table format. Corrected other paragraph formats.                                                                         |

| V03.26             | 12 Sep 2012   | General                        | - Added missing full stops. Removed redundant quotation marks.                                                                                      |

### Table 8-1. Revision History

## 8.1 Introduction

The S12XDBG module provides an on-chip trace buffer with flexible triggering capability to allow nonintrusive debug of application software. The S12XDBG module is optimized for the S12X 16-bit architecture and allows debugging of CPU12Xand XGATE module operations.

Typically the S12XDBG module is used in conjunction with the S12XBDM module, whereby the user configures the S12XDBG module for a debugging session over the BDM interface. Once configured the S12XDBG module is armed and the device leaves BDM Mode returning control to the user program, which is then monitored by the S12XDBG module. Alternatively the S12XDBG module can be configured over a serial interface using SWI routines.

## 8.1.1 Glossary

| Term                    | Definition                                                                                           |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| COF                     | Change Of Flow.<br>Change in the program flow due to a conditional branch, indexed jump or interrupt |  |  |  |

| BDM                     | Background Debug Mode                                                                                |  |  |  |

| DUG                     | Device User Guide, describing the features of the device into which the DBG is integrated            |  |  |  |

| WORD 16-bit data entity |                                                                                                      |  |  |  |

### Table 8-2. Glossary Of Terms

Logical AND Immediate 8 bit Constant (High Byte)

### Operation

$RD.H \& IMM8 \Rightarrow RD.H$

Performs a bit wise logical AND between the high byte of register RD and an immediate 8 bit constant and stores the result in the destination register RD.H. The low byte of RD is not affected.

### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | 0 |   |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the 8 bit result is \$00; cleared otherwise.

- V: 0; cleared.

- C: Not affected.

### Code and CPU Cycles

| Source Form    | Address<br>Mode |   | Machine Code |   |   |   | Cycles |      |   |

|----------------|-----------------|---|--------------|---|---|---|--------|------|---|

| ANDH RD, #IMM8 | IMM8            | 1 | 0            | 0 | 0 | 1 | RD     | IMM8 | Р |

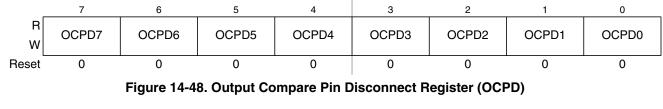

## 14.3.2.25 Output Compare Pin Disconnect Register (OCPD)

Module Base + 0x002C

Read: Anytime

Write: Anytime

All bits reset to zero.

#### Table 14-32. OCPD Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0       | Output Compare Pin Disconnect Bits                                                                                                                                                                                                                                                                                                                                        |

| OCPD[7:0] | <ul> <li>0 Enables the timer channel IO port. Output Compare actions will occur on the channel pin. These bits do not affect the input capture or pulse accumulator functions.</li> <li>1 Disables the timer channel IO port. Output Compare actions will not affect on the channel pin; the output compare flag will still be set on an Output Compare event.</li> </ul> |

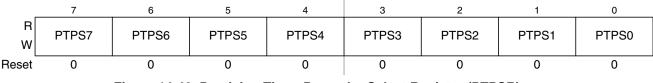

### 14.3.2.26 Precision Timer Prescaler Select Register (PTPSR)

Module Base + 0x002E

Figure 14-49. Precision Timer Prescaler Select Register (PTPSR)

Read: Anytime

Write: Anytime

All bits reset to zero.

#### Table 14-33. PTPSR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:0<br>PTPS[7:0] | <b>Precision Timer Prescaler Select Bits</b> — These eight bits specify the division rate of the main Timer prescaler. These are effective only when the PRNT bit of TSCR1 is set to 1. Table 14-34 shows some selection examples in this case. |  |  |  |  |  |  |  |

|                  | The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero.                                                                                                          |  |  |  |  |  |  |  |

| IBC[7:0]<br>(hex) | SCL Divider<br>(clocks) | SDA Hold<br>(clocks) | SCL Hold<br>(start) | SCL Hold<br>(stop) |

|-------------------|-------------------------|----------------------|---------------------|--------------------|

| 82                | 88                      | 32                   | 32                  | 52                 |

| 83                | 96                      | 32                   | 36                  | 56                 |

| 84                | 104                     | 36                   | 40                  | 60                 |

| 85                | 112                     | 36                   | 44                  | 64                 |

| 86                | 128                     | 40                   | 52                  | 72                 |

| 87                | 152                     | 40                   | 64                  | 84                 |

| 88                | 112                     | 28                   | 40                  | 60                 |

| 89                | 128                     | 28                   | 48                  | 68                 |

| 8A                | 144                     | 36                   | 56                  | 76                 |

| 8B                | 160                     | 36                   | 64                  | 84                 |

| 8C                | 176                     | 44                   | 72                  | 92                 |

| 8D                | 192                     | 44                   | 80                  | 100                |

| 8E                | 224                     | 52                   | 96                  | 116                |

| 8F                | 272                     | 52                   | 120                 | 140                |

| 90                | 192                     | 36                   | 72                  | 100                |

| 91                | 224                     | 36                   | 88                  | 116                |

| 92                | 256                     | 52                   | 104                 | 132                |

| 93                | 288                     | 52                   | 120                 | 148                |

| 94                | 320                     | 68                   | 136                 | 164                |

| 95                | 352                     | 68                   | 152                 | 180                |

| 96                | 416                     | 84                   | 184                 | 212                |

| 97                | 512                     | 84                   | 232                 | 260                |

| 98                | 320                     | 36                   | 152                 | 164                |

| 99                | 384                     | 36                   | 184                 | 196                |

| 9A                | 448                     | 68                   | 216                 | 228                |

| 9B                | 512                     | 68                   | 248                 | 260                |

| 9C                | 576                     | 100                  | 280                 | 292                |

| 9D                | 640                     | 100                  | 312                 | 324                |

| 9E                | 768                     | 132                  | 376                 | 388                |

| 9F                | 960                     | 132                  | 472                 | 484                |

| A0                | 640                     | 68                   | 312                 | 324                |

| A1                | 768                     | 68                   | 376                 | 388                |

| A2                | 896                     | 132                  | 440                 | 452                |

| A3                | 1024                    | 132                  | 504                 | 516                |

| A4                | 1152                    | 196                  | 568                 | 580                |

| A5                | 1280                    | 196                  | 632                 | 644                |

| A6                | 1536                    | 260                  | 760                 | 772                |

| A7                | 1920                    | 260                  | 952                 | 964                |

| A8                | 1280                    | 132                  | 632                 | 644                |

| A9                | 1536                    | 132                  | 760                 | 772                |

| AA                | 1792                    | 260                  | 888                 | 900                |

| AB                | 2048                    | 260                  | 1016                | 1028               |

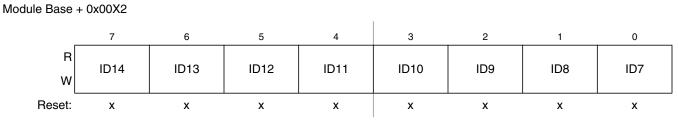

### Figure 16-28. Identifier Register 2 (IDR2) — Extended Identifier Mapping

| Field           | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>ID[14:7] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

#### Table 16-29. IDR2 Register Field Descriptions — Extended

#### Module Base + 0x00X3

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R      |     | IDE |     | 201 | ססו |     |     | ото |

| w      | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | RTR |

| Reset: | х   | х   | х   | х   | х   | х   | х   | x   |

#### Figure 16-29. Identifier Register 3 (IDR3) — Extended Identifier Mapping

#### Table 16-30. IDR3 Register Field Descriptions — Extended

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1<br>ID[6:0] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                                      |

| 0<br>RTR       | <ul> <li>Remote Transmission Request — This flag reflects the status of the remote transmission request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.</li> <li>0 Data frame</li> <li>1 Remote frame</li> </ul> |

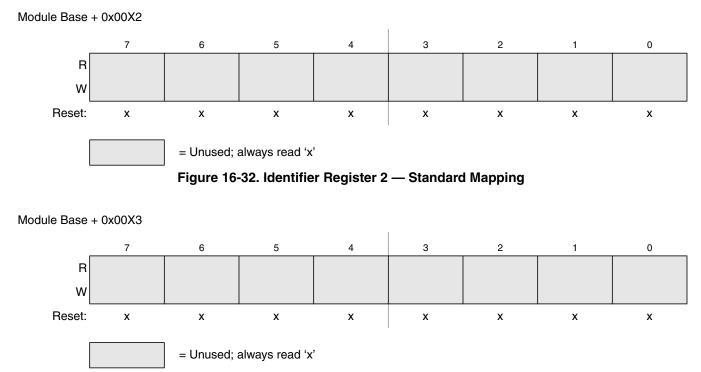

#### Figure 16-33. Identifier Register 3 — Standard Mapping

### 16.3.3.2 Data Segment Registers (DSR0-7)

The eight data segment registers, each with bits DB[7:0], contain the data to be transmitted or received. The number of bytes to be transmitted or received is determined by the data length code in the corresponding DLR register.

Module Base + 0x00X4 to Module Base + 0x00XB

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| Reset: | х   | x   | x   | x   | x   | x   | x   | х   |

Figure 16-34. Data Segment Registers (DSR0–DSR7) — Extended Identifier Mapping

| Table 16-33. DSR0–DSR7 Register Field Descriptions | Table 16-33. | DSR0-DSR7 | <b>Register Fiel</b> | Id Descriptions |

|----------------------------------------------------|--------------|-----------|----------------------|-----------------|

|----------------------------------------------------|--------------|-----------|----------------------|-----------------|

| Field          | Description   |

|----------------|---------------|

| 7-0<br>DB[7:0] | Data bits 7-0 |

### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

## 19.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the PWM module.

| Register<br>Name                |        | Bit 7 | 6                           | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|---------------------------------|--------|-------|-----------------------------|-------|-------|-------|-------|-------|-------|

| 0x0000<br>PWME                  | R<br>W | PWME7 | PWME6                       | PWME5 | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |

| 0x0001<br>PWMPOL                | R<br>W | PPOL7 | PPOL6                       | PPOL5 | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |

| 0x0002<br>PWMCLK                | R<br>W | PCLK7 | PCLKL6                      | PCLK5 | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |

| 0x0003<br>PWMPRCLK              | R<br>W | 0     | PCKB2                       | PCKB1 | PCKB0 | 0     | PCKA2 | PCKA1 | PCKA0 |

| 0x0004<br>PWMCAE                | R<br>W | CAE7  | CAE6                        | CAE5  | CAE4  | CAE3  | CAE2  | CAE1  | CAE0  |

| 0x0005<br>PWMCTL                | R<br>W | CON67 | CON45                       | CON23 | CON01 | PSWAI | PFRZ  | 0     | 0     |

| 0x0006<br>PWMTST <sup>(1)</sup> | R<br>W | 0     | 0                           | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0007<br>PWMPRSC <sup>1</sup>  | R<br>W | 0     | 0                           | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0008<br>PWMSCLA               | R<br>W | Bit 7 | 6                           | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0009<br>PWMSCLB               | R<br>W | Bit 7 | 6                           | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x000A<br>PWMSCNTA<br>1         | R<br>W | 0     | 0                           | 0     | 0     | 0     | 0     | 0     | 0     |

|                                 |        |       | = Unimplemented or Reserved |       |       |       |       |       |       |

## NOTE

Care must be taken when expecting data from a master while the slave is in wait or stop mode. Even though the shift register will continue to operate, the rest of the SPI is shut down (i.e., a SPIF interrupt will **not** be generated until exiting stop or wait mode). Also, the byte from the shift register will not be copied into the SPIDR register until after the slave SPI has exited wait or stop mode. In slave mode, a received byte pending in the receive shift register will be lost when entering wait or stop mode. An SPIF flag and SPIDR copy is generated only if wait mode is entered or exited during a transision. If the slave enters wait mode in idle mode and exits wait mode in idle mode, neither a SPIF nor a SPIDR copy will occur.

## 21.4.7.3 SPI in Stop Mode

Stop mode is dependent on the system. The SPI enters stop mode when the module clock is disabled (held high or low). If the SPI is in master mode and exchanging data when the CPU enters stop mode, the transmission is frozen until the CPU exits stop mode. After stop, data to and from the external SPI is exchanged correctly. In slave mode, the SPI will stay synchronized with the master.

The stop mode is not dependent on the SPISWAI bit.

### 21.4.7.4 Reset

The reset values of registers and signals are described in Section 21.3, "Memory Map and Register Definition", which details the registers and their bit fields.

- If a data transmission occurs in slave mode after reset without a write to SPIDR, it will transmit garbage, or the data last received from the master before the reset.

- Reading from the SPIDR after reset will always read zeros.

### 21.4.7.5 Interrupts

The SPI only originates interrupt requests when SPI is enabled (SPE bit in SPICR1 set). The following is a description of how the SPI makes a request and how the MCU should acknowledge that request. The interrupt vector offset and interrupt priority are chip dependent.

The interrupt flags MODF, SPIF, and SPTEF are logically ORed to generate an interrupt request.

### 21.4.7.5.1 MODF

MODF occurs when the master detects an error on the  $\overline{SS}$  pin. The master SPI must be configured for the MODF feature (see Table 21-3). After MODF is set, the current transfer is aborted and the following bit is changed:

• MSTR = 0, The master bit in SPICR1 resets.

The MODF interrupt is reflected in the status register MODF flag. Clearing the flag will also clear the interrupt. This interrupt will stay active while the MODF flag is set. MODF has an automatic clearing process which is described in Section 21.3.2.4, "SPI Status Register (SPISR)".

#### ter 24 128 KByte Flash Module (S12XFTM128K2V1)

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Ability to program up to four words in a burst sequence

## 24.1.2.3 Emulated EEPROM Features

- Up to 2 Kbytes of emulated EEPROM (EEE) accessible as 2 Kbytes of RAM

- Flexible protection scheme to prevent accidental program or erase of data

- Automatic EEE file handling using an internal Memory Controller

- Automatic transfer of valid EEE data from D-Flash memory to buffer RAM on reset

- Ability to monitor the number of outstanding EEE related buffer RAM words left to be programmed into D-Flash memory

- Ability to disable EEE operation and allow priority access to the D-Flash memory

- Ability to cancel all pending EEE operations and allow priority access to the D-Flash memory

## 24.1.2.4 User Buffer RAM Features

• Up to 2 Kbytes of RAM for user access

## 24.1.2.5 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

## 24.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 24-1.

## 25.1.2.3 Emulated EEPROM Features

- Up to 4 Kbytes of emulated EEPROM (EEE) accessible as 4 Kbytes of RAM

- Flexible protection scheme to prevent accidental program or erase of data

- Automatic EEE file handling using an internal Memory Controller

- Automatic transfer of valid EEE data from D-Flash memory to buffer RAM on reset

- Ability to monitor the number of outstanding EEE related buffer RAM words left to be programmed into D-Flash memory

- Ability to disable EEE operation and allow priority access to the D-Flash memory

- Ability to cancel all pending EEE operations and allow priority access to the D-Flash memory

## 25.1.2.4 User Buffer RAM Features

• Up to 4 Kbytes of RAM for user access

## 25.1.2.5 Other Flash Module Features

- No external high-voltage power supply required for Flash memory program and erase operations

- Interrupt generation on Flash command completion and Flash error detection

- Security mechanism to prevent unauthorized access to the Flash memory

## 25.1.3 Block Diagram

The block diagram of the Flash module is shown in Figure 25-1.

| Register | Error Bit | Error Condition                                                                                           |  |  |

|----------|-----------|-----------------------------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                                                               |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                                             |  |  |

|          |           | Set if command not available in current mode (see Table 25-30)                                            |  |  |

|          | ACCERR    | Set if an invalid global address [22:0] is supplied                                                       |  |  |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)                                    |  |  |

| FSTAT    |           | Set if the global address [22:0] points to an area of the D-Flash EEE partition                           |  |  |

|          |           | Set if the requested section breaches the end of the D-Flash block or goes into the D-Flash EEE partition |  |  |

|          | FPVIOL    | None                                                                                                      |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                                                   |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read                                   |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                                      |  |  |

#### Table 25-66. Erase Verify D-Flash Section Command Error Handling

### 25.4.2.17 Program D-Flash Command

The Program D-Flash operation programs one to four previously erased words in the D-Flash user partition. The Program D-Flash operation will confirm that the targeted location(s) were successfully programmed upon completion.

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

| CCOBIX[2:0] | FCCOB Parameters                                          |                   |  |  |  |

|-------------|-----------------------------------------------------------|-------------------|--|--|--|

| 000         | 0x11 Global address [22:16] to identify the D-Flash block |                   |  |  |  |

| 001         | Global address [15:0] of word to be programmed            |                   |  |  |  |

| 010         | Word 0 program value                                      |                   |  |  |  |

| 011         | Word 1 program value, if desired                          |                   |  |  |  |

| 100         | Word 2 program value, if desired                          |                   |  |  |  |

| 101         | Word 3 program                                            | value, if desired |  |  |  |

Table 25-67. Program D-Flash Command FCCOB Requirements

Upon clearing CCIF to launch the Program D-Flash command, the user-supplied words will be transferred to the Memory Controller and be programmed. The CCOBIX index value at Program D-Flash command launch determines how many words will be programmed in the D-Flash block. No protection checks are made in the Program D-Flash operation on the D-Flash block, only access error checks. The CCIF flag is set when the operation has completed.

## 28.4.2.10 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| 000         | 0x0A                                                                                                                     | Global address [22:16] to identify<br>P-Flash block to be erased |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 28.1.2.1 for the P-Flash sector size. |                                                                  |  |  |

Table 28-51. Erase P-Flash Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |

|          |           | Set if a Load Data Field command sequence is currently active                       |  |

|          | ACCERR    | Set if command not available in current mode (see Table 28-30)                      |  |

|          |           | Set if an invalid global address [22:16] is supplied <sup>(1)</sup>                 |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |

| FERSTAT  | EPVIOLIF  | None                                                                                |  |

Table 28-52. Erase P-Flash Sector Command Error Handling

1. As defined by the memory map for FTM1024K5.

### 28.4.2.11 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and D-Flash memory space and, if the erase is successful, will release security.

### Table 28-53. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |

|-------------|------------------|--------------|

| 000         | 0x0B             | Not required |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and D-Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security

| Register | Error Bit | Error Condition                                                                                                  |  |  |

|----------|-----------|------------------------------------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                                                       |  |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                                                       |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                                                    |  |  |

|          |           | Set if command not available in current mode (see Table 28-30)                                                   |  |  |

|          | ACCERR    | Set if an invalid global address [22:0] is supplied                                                              |  |  |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)                                           |  |  |

| FSTAT    |           | Set if the global address [22:0] points to an area in the D-Flash EEE partition                                  |  |  |

|          |           | Set if the requested group of words breaches the end of the D-Flash block or goes into the D-Flash EEE partition |  |  |

|          | FPVIOL    | None                                                                                                             |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                              |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                              |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                                             |  |  |

### Table 28-68. Program D-Flash Command Error Handling

## 28.4.2.18 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash user partition.

Table 28-69. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                |                                                     |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| 000         | 0x12                                                                                                            | Global address [22:16] to identify<br>D-Flash block |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 28.1.2.2 for D-Flash sector size. |                                                     |  |  |

Upon clearing CCIF to launch the Erase D-Flash Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase D-Flash Sector operation has completed.

## A.6.3 Phase Locked Loop

### A.6.3.1 Jitter Information

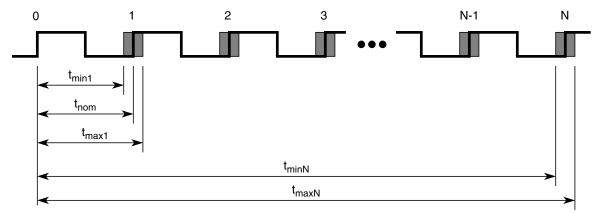

With each transition of the clock  $f_{cmp}$ , the deviation from the reference clock  $f_{ref}$  is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the clock output frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure A-5.

### Figure A-5. Jitter Definitions

The relative deviation of  $t_{nom}$  is at its maximum for one clock period, and decreases towards zero for larger number of clock periods (N).

ndix E Detailed Register Address Map

| 0x00C0-0x00C7 As | ynchronous Serial I | Interface (SCI3 | ) Map |

|------------------|---------------------|-----------------|-------|

|------------------|---------------------|-----------------|-------|

| Address       | Name                          |                             | Bit 7                        | Bit 6                     | Bit 5         | Bit 4         | Bit 3 | Bit 2   | Bit 1  | Bit 0  |       |  |       |

|---------------|-------------------------------|-----------------------------|------------------------------|---------------------------|---------------|---------------|-------|---------|--------|--------|-------|--|-------|

| 0x00C0        | SCI3BDH <sup>(1)</sup>        | R<br>W                      | IREN                         | TNP1                      | TNP0          | SBR12         | SBR11 | SBR10   | SBR9   | SBR8   |       |  |       |

| 0x00C1        | SCI3BDL <sup>1</sup>          | R<br>W                      | SBR7                         | SBR6                      | SBR5          | SBR4          | SBR3  | SBR2    | SBR1   | SBR0   |       |  |       |

| 0x00C2        | SCI3CR1 <sup>1</sup>          | R<br>W                      | LOOPS                        | SCISWAI                   | RSRC          | М             | WAKE  | ILT     | PE     | PT     |       |  |       |

| 0x00C0 S      | x00C0 SCI3ASR1 <sup>(2)</sup> | 0C0 SCI3ASR1 <sup>(2)</sup> | 00C0 SCI3ASR1 <sup>(2)</sup> | 0 SCI3ASR1 <sup>(2)</sup> | R             | RXEDGIF       | 0     | 0       | 0      | 0      |       |  | DKDIE |

|               |                               |                             |                              |                           | JUCU SCIBASRI | UUCU SCIJASKI | W     | RAEDGIF |        |        |       |  | BERRV |

| 0x00C1 S0     | 00C1 SCI3ACR1 <sup>2</sup>    |                             |                              | F                         | R             | RXEDGIE       | 0     | 0       | 0      | 0      | 0     |  | BKDIE |

|               |                               | W                           | RAEDGIE                      |                           |               |               |       |         | BERRIE | DRUIE  |       |  |       |

| 0x00C2 SCI3   | SCI3ACR2 <sup>2</sup>         | SCI2ACD2                    | R                            | 0                         | 0             | 0             | 0     | 0       | BERRM1 | BERRM0 | BKDFE |  |       |

|               |                               | W                           |                              |                           |               |               |       |         |        |        |       |  |       |

| 0x00C3        | SCI3CR2                       | R<br>W                      | TIE                          | TCIE                      | RIE           | ILIE          | TE    | RE      | RWU    | SBK    |       |  |       |

| 0x00C4 SCI3SR | 6C126D1                       | R                           | TDRE                         | TC                        | RDRF          | IDLE          | OR    | NF      | FE     | PF     |       |  |       |

|               | 3013301                       | W                           |                              |                           |               |               |       |         |        |        |       |  |       |

| 0x00C5        | SCI3SR2                       | C5 SCI3SR2 <mark>R</mark> A |                              | AMAP                      | 0             | 0             | TXPOL | RXPOL   | BRK13  | TXDIR  | RAF   |  |       |

|               |                               |                             |                              |                           |               | TAFUL         | NAFUL |         |        |        |       |  |       |

| 0x00C6        | SCI3DRH                       | R                           | R8                           | Т8                        | 0             | 0             | 0     | 0       | 0      | 0      |       |  |       |

|               |                               | 001001111                   | W                            |                           | 10            |               |       |         |        |        |       |  |       |

| 0x00C7        | SCI3DRL                       | R                           | R7                           | R6                        | R5            | R4            | R3    | R2      | R1     | R0     |       |  |       |

|               |                               | W                           | T7                           | T6                        | T5            | T4            | Т3    | T2      | T1     | Т0     |       |  |       |

1. Those registers are accessible if the AMAP bit in the SCI3SR2 register is set to zero 2. Those registers are accessible if the AMAP bit in the SCI3SR2 register is set to one

### 0x03D0–0x03FF Timer Module (TIM) Map (Sheet 2 of 2)

| Address           | Name     |        | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|-------------------|----------|--------|---------|---------|---------|---------|---------|---------|--------|--------|

| 0x03E4            | TC2H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03E5            | TC2L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03E6            | тсзн     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03E7            | TC3L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03E8            | TC4H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03E9            | TC4L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03EA            | TC5H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03EB            | TC5L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03EC            | TC6H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03ED            | TC6L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03EE            | TC7H     | R<br>W | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  |

| 0x03EF            | TC7L     | R<br>W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x03F0            | PACTL    | R<br>W | 0       | PAEN    | PAMOD   | PEDGE   | CLK1    | CLK0    | PAOVI  | PAI    |

| 0x03F1            | PAFLG    | R<br>W | 0       | 0       | 0       | 0       | 0       | 0       | PAOVF  | PAIF   |

| 0x03F2            | PACNTH   | R<br>W | PACNT15 | PACNT14 | PACNT13 | PACNT12 | PACNT11 | PACNT10 | PACNT9 | PACNT8 |

| 0x03F3            | PACNTL   | R<br>W | PACNT7  | PACNT6  | PACNT5  | PACNT4  | PACNT3  | PACNT2  | PACNT1 | PACNT0 |

| 0x03F4–<br>0x03FB | Reserved | R<br>W |         | 0       | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x03FC            | OCPD     | R<br>W | OCPD7   | OCPD6   | OCPD5   | OCPD4   | OCPD3   | OCPD2   | OCPD1  | OCPD0  |

| 0x03FD            | Reserved | R<br>W |         |         |         |         |         |         |        |        |

| 0x03FE            | PTPSR    | R<br>W | PTPSR7  | PTPSR6  | PTPSR5  | PTPSR4  | PTPSR3  | PTPSR2  | PTPSR1 | PTPSR0 |

| 0x03FF            | Reserved | R<br>W |         |         |         |         |         |         |        |        |