Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xeg128w1maa |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

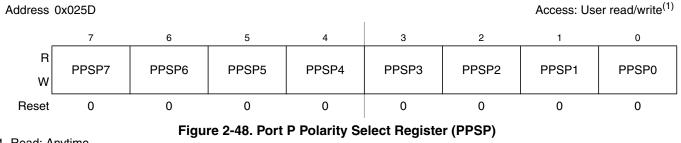

## 2.3.50 Port P Polarity Select Register (PPSP)

1. Read: Anytime. Write: Anytime.

#### Table 2-46. PPSP Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PPSP | <ul> <li>Port P pull device select—Determine pull device polarity on input pins</li> <li>This register serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-<br/>up or pull-down device if enabled.</li> <li>1 A rising edge on the associated Port P pin sets the associated flag bit in the PIFP register. A pull-down device is<br/>connected to the associated Port P pin, if enabled by the associated bit in register PERP and if the port is used<br/>as input.</li> <li>0 A falling edge on the associated Port P pin, if enabled by the associated flag bit in the PIFP register. A pull-up device is<br/>connected to the associated Port P pin, if enabled by the associated flag bit in the PIFP register. A pull-up device is<br/>as input.</li> </ul> |

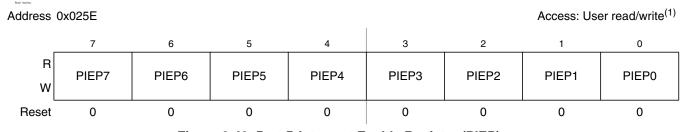

# 2.3.51 Port P Interrupt Enable Register (PIEP)

Figure 2-49. Port P Interrupt Enable Register (PIEP)

1. Read: Anytime. Write: Anytime.

#### Table 2-47. PPSP Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PIEP | Port P interrupt enable—<br>This register disables or enables on a per-pin basis the edge sensitive external interrupt associated with Port P.<br>1 Interrupt is enabled.<br>0 Interrupt is disabled (interrupt flag masked). |

### Table 2-51. DDRH Register Field Descriptions (continued)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1<br>DDRH | Port H data direction—         This register controls the data direction of pin 1.         The enabled SCI6 forces the I/O state to be an output. Depending on the configuration of the enabled routed SPI1 this pin will be forced to be input or output. In those cases the data direction bits will not change. The DDRM bits revert to controlling the I/O direction of a pin when the associated peripheral module is disabled.         1 Associated pin is configured as output.         0 Associated pin is configured as input.                        |  |  |  |  |  |  |  |

| 0<br>DDRH | <ul> <li>Port H data direction—</li> <li>This register controls the data direction of pin 0.</li> <li>The enabled SCI6 forces the I/O state to be an input. Depending on the configuration of the enabled routed SPI1 this pin will be forced to be input or output. In those cases the data direction bits will not change. The DDRM bits revert to controlling the I/O direction of a pin when the associated peripheral module is disabled.</li> <li>1 Associated pin is configured as output.</li> <li>0 Associated pin is configured as input.</li> </ul> |  |  |  |  |  |  |  |

### NOTE

Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read on PTH or PTIH registers, when changing the DDRH register.

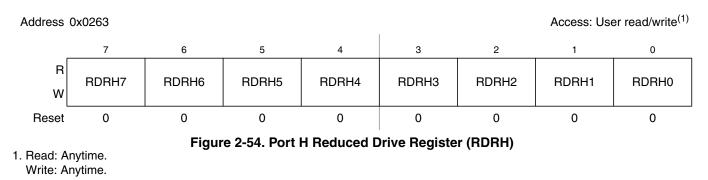

# 2.3.56 Port H Reduced Drive Register (RDRH)

### Table 2-52. RDRH Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>RDRH | <ul> <li>Port H reduced drive—Select reduced drive for outputs</li> <li>This register configures the drive strength of output pins 7 through 0 as either full or reduced independent of the function used on the pins. If a pin is used as input this bit has no effect.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength).</li> <li>0 Full drive strength enabled.</li> </ul> |

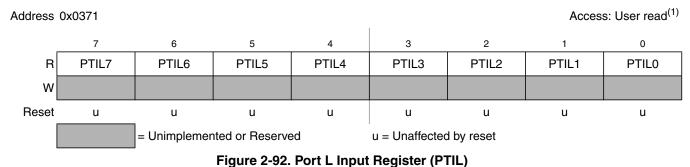

# 2.3.94 Port L Input Register (PTIL)

1. Read: Anytime.

Write:Never, writes to this register have no effect.

### Table 2-89. PTIL Register Field Descriptions

| Field | Description                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0   | Port L input data—                                                                                                                                              |

| PTIL  | This register always reads back the buffered state of the associated pins. This can also be used to detect overload or short circuit conditions on output pins. |

# 2.3.95 Port L Data Direction Register (DDRL)

Address 0x0372

Access: User read/write<sup>(1)</sup>

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | DDRL7 | DDRL6 | DDRL5 | DDRL4 | DDRL3 | DDRL2 | DDRL1 | DDRL0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

### Figure 2-93. Port L Data Direction Register (DDRL)

1. Read: Anytime. Write: Anytime.

### Table 2-90. DDRL Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>DDRL | <b>Port L data direction</b> —<br>This register controls the data direction of pins 7 through 0. This register configures each Port L pin as either input or output.                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | If SPI0 is enabled, the SPI0 determines the pin direction. <i>Refer to SPI section for details</i> .<br>If the associated SCI transmit or receive channel is enabled this register has no effect on the pins. The pin is forced to be an output if a SCI transmit channel is enabled, it is forced to be an input if the SCI receive channel is enabled.<br>The data direction bits revert to controlling the I/O direction of a pin when the associated channel is disabled.<br>1 Associated pin is configured as output.<br>0 Associated pin is configured as input. |

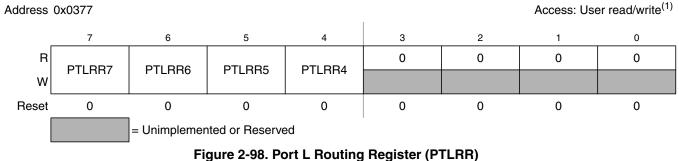

## 2.3.100 Port L Routing Register (PTLRR)

1. Read: Anytime. Write: Anytime.

This register configures the re-routing of SCI7, SCI6, SCI5, and SCI4 on alternative ports.

| Module | PTLRR   |   |     |       | Relate | d Pins |

|--------|---------|---|-----|-------|--------|--------|

|        | 7       | 6 | 5   | 4     |        |        |

|        |         |   | TXD | RXD   |        |        |

| SCI7   | 0       | x | х   | х     | PH3    | PH2    |

|        | 1       | х | х   | х     | PL7    | PL6    |

| SCI6   | 3 x 0 x |   | х   | PH1   | PH0    |        |

|        | х       | 1 | х   | х     | PL5    | PL4    |

| SCI5   | х       | х | 0   | x PH7 |        | PH6    |

|        | х       | х | 1   | х     | PL3    | PL2    |

| SCI4   | х       | х | х   | 0     | PH5    | PH4    |

|        | х       | х | х   | 1     | PL1    | PL0    |

### Table 2-95. Port L Routing Summary

# 2.3.101 Port F Data Register (PTF)

#### Address 0x0378

Access: User read/write<sup>(1)</sup>

|                     | 7      | 6      | 5      | 4      | 3                  | 2     | 1     | 0     |

|---------------------|--------|--------|--------|--------|--------------------|-------|-------|-------|

| R<br>W              | PTF7   | PTFT6  | PTF5   | PTF4   | PTF3               | PTF2  | PTF1  | PTF0  |

| Altern.<br>Function | (TXD3) | (RXD3) | (SCL0) | (SDA0) | ( <del>CS3</del> ) | (CS2) | (CS1) | (CS0) |

| Reset               | 0      | 0      | 0      | 0      | 0                  | 0     | 0     | 0     |

Figure 2-99. Port F Data Register (PTF)

1. Read: Anytime.

Write: Anytime.

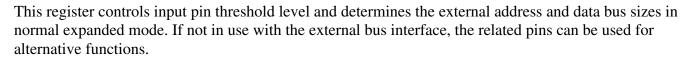

### ter 5 External Bus Interface (S12XEBIV4)

External bus is available as programmed in normal expanded mode and always full-sized in emulation modes and special test mode; function not available in single-chip modes.

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ITHRS       | <b>Reduced Input Threshold</b> — This bit selects reduced input threshold on external data bus pins and specific control input signals which are in use with the external bus interface in order to adapt to external devices with a 3.3 V, 5 V tolerant I/O.                                                                                                                                                                                      |

|                  | <ul> <li>The reduced input threshold level takes effect depending on ITHRS, the operating mode and the related enable signals of the EBI pin function as summarized in Table 5-4.</li> <li>0 Input threshold is at standard level on all pins</li> <li>1 Reduced input threshold level enabled on pins in use with the external bus interface</li> </ul>                                                                                           |

| 5<br>HDBE        | High Data Byte Enable — This bit enables the higher half of the 16-bit data bus. If disabled, only the lower 8-bit data bus can be used with the external bus interface. In this case the unused data pins and the data select signals (UDS and LDS) are free to be used for alternative functions.         0 DATA[15:8], UDS, and LDS disabled         1 DATA[15:8], UDS, and LDS enabled                                                         |

| 4–0<br>ASIZ[4:0] | <b>External Address Bus Size</b> — These bits allow scalability of the external address bus. The programmed value corresponds to the number of available low-aligned address lines (refer to Table 5-5). All address lines ADDR[22:0] start up as outputs after reset in expanded modes. This needs to be taken into consideration when using alternative functions on relevant pins in applications which utilize a reduced external address bus. |

#### Table 5-3. EBICTL0 Field Descriptions

#### Table 5-4. Input Threshold Levels on External Signals

| ITHRS | External Signal            | NS       | SS       | NX                                            | ES       | EX                                          | ST       |

|-------|----------------------------|----------|----------|-----------------------------------------------|----------|---------------------------------------------|----------|

| 0     | DATA[15:8]<br>TAGHI, TAGLO |          | Standard | Standard                                      | Reduced  | Reduced                                     | Standard |

|       | DATA[7:0]                  | Standard |          |                                               |          |                                             |          |

|       | EWAIT                      |          |          |                                               | Standard | Standard                                    |          |

|       | DATA[15:8]<br>TAGHI, TAGLO | Standard | Standard | Reduced<br>if HDBE = 1                        | Reduced  | Reduced                                     | Reduced  |

| 1     | DATA[7:0]                  |          |          | Reduced                                       |          |                                             |          |

|       | EWAIT                      |          |          | Reduced<br>if EWAIT<br>enabled <sup>(1)</sup> | Standard | Reduced<br>if EWAIT<br>enabled <sup>1</sup> | Standard |

EWAIT function is enabled if at least one CSx line is configured respectively in MMCCTL0. Refer to S12X\_MMC section and Table 5-6.

| ASIZ[4:0] | Available External Address Lines |

|-----------|----------------------------------|

| 00000     | None                             |

| 00001     | UDS                              |

| 00010     | ADDR1, UDS                       |

#### Table 5-5. External Address Bus Size

| Register<br>Name     |                             | Bit 7      | 6          | 5          | 4          | 3          | 2          | 1         | Bit 0     |

|----------------------|-----------------------------|------------|------------|------------|------------|------------|------------|-----------|-----------|

| 0x001C<br>TC6 (High) | R<br>W                      | Bit 15     | Bit 14     | Bit 13     | Bit 12     | Bit 11     | Bit 10     | Bit 9     | Bit 8     |

| 0x001D<br>TC6 (Low)  | R<br>W                      | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1     | Bit 0     |

| 0x001E<br>TC7 (High) | R<br>W                      | Bit 15     | Bit 14     | Bit 13     | Bit 12     | Bit 11     | Bit 10     | Bit 9     | Bit 8     |

| 0x001F<br>TC7 (Low)  | R<br>W                      | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1     | Bit 0     |

| 0x0020<br>PACTL      | R<br>W                      | 0          | PAEN       | PAMOD      | PEDGE      | CLK1       | CLK0       | PA0VI     | PAI       |

| 0x0021<br>PAFLG      | R                           | 0          | 0          | 0          | 0          | 0          | 0          | PA0VF     | PAIF      |

| I' La                | W                           |            |            |            |            |            |            |           |           |

| 0x0022<br>PACN3      | R<br>W                      | PACNT7(15) | PACNT6(14) | PACNT5(13) | PACNT4(12) | PACNT3(11) | PACNT2(10) | PACNT1(9) | PACNT0(8) |

| 0x0023<br>PACN2      | R<br>W                      | PACNT7     | PACNT6     | PACNT5     | PACNT4     | PACNT3     | PACNT2     | PACNT1    | PACNT0    |

| 0x0024<br>PACN1      | R<br>W                      | PACNT7(15) | PACNT6(14) | PACNT5(13) | PACNT4(12) | PACNT3(11) | PACNT2(10) | PACNT1(9) | PACNT0(8) |

| 0x0025<br>PACN0      | R<br>W                      | PACNT7     | PACNT6     | PACNT5     | PACNT4     | PACNT3     | PACNT2     | PACNT1    | PACNT0    |

| 0x0026<br>MCCTL      | R<br>W                      | MCZI       | MODMC      | RDMCL      | 0<br>ICLAT | 0<br>FLMC  | MCEN       | MCPR1     | MCPR0     |

| 0x0027<br>MCFLG      | R<br>W                      | MCZF       | 0          | 0          | 0          | POLF3      | POLF2      | POLF1     | POLF0     |

| 0x0028<br>ICPAR      | R<br>W                      | 0          | 0          | 0          | 0          | PA3EN      | PA2EN      | PA1EN     | PAOEN     |

| 0x0029<br>DLYCT      | R<br>W                      | DLY7       | DLY6       | DLY5       | DLY4       | DLY3       | DLY2       | DLY1      | DLY0      |

| 0x002A<br>ICOVW      | R<br>W                      | NOVW7      | NOVW6      | NOVW5      | NOVW4      | NOVW3      | NOVW2      | NOVW1     | NOVW0     |

|                      | = Unimplemented or Reserved |            |            |            |            |            |            |           |           |

### Figure 14-2. ECT Register Summary (Sheet 3 of 5)

| IBC[7:0]<br>(hex) | SCL Divider<br>(clocks) | SDA Hold<br>(clocks) | SCL Hold<br>(start) | SCL Hold<br>(stop) |

|-------------------|-------------------------|----------------------|---------------------|--------------------|

| 59                | 192                     | 18                   | 92                  | 98                 |

| 5A                | 224                     | 34                   | 108                 | 114                |

| 5B                | 256                     | 34                   | 124                 | 130                |

| 5C                | 288                     | 50                   | 140                 | 146                |

| 5D                | 320                     | 50                   | 156                 | 162                |

| 5E                | 384                     | 66                   | 188                 | 194                |

| 5F                | 480                     | 66                   | 236                 | 242                |

| 60                | 320                     | 34                   | 156                 | 162                |

| 61                | 384                     | 34                   | 188                 | 194                |

| 62                | 448                     | 66                   | 220                 | 226                |

| 63                | 512                     | 66                   | 252                 | 258                |

| 64                | 576                     | 98                   | 284                 | 290                |

| 65                | 640                     | 98                   | 316                 | 322                |

| 66                | 768                     | 130                  | 380                 | 386                |

| 67                | 960                     | 130                  | 476                 | 482                |

| 68                | 640                     | 66                   | 316                 | 322                |

| 69                | 768                     | 66                   | 380                 | 386                |

| 6A                | 896                     | 130                  | 444                 | 450                |

| 6B                | 1024                    | 130                  | 508                 | 514                |

| 6C                | 1152                    | 194                  | 572                 | 578                |

| 6D                | 1280                    | 194                  | 636                 | 642                |

| 6E                | 1536                    | 258                  | 764                 | 770                |

| 6F                | 1920                    | 258                  | 956                 | 962                |

| 70                | 1280                    | 130                  | 636                 | 642                |

| 71                | 1536                    | 130                  | 764                 | 770                |

| 72                | 1792                    | 258                  | 892                 | 898                |

| 73                | 2048                    | 258                  | 1020                | 1026               |

| 74                | 2304                    | 386                  | 1148                | 1154               |

| 75                | 2560                    | 386                  | 1276                | 1282               |

| 76                | 3072                    | 514                  | 1532                | 1538               |

| 77                | 3840                    | 514                  | 1916                | 1922               |

| 78                | 2560                    | 258                  | 1276                | 1282               |

| 79                | 3072                    | 258                  | 1532                | 1538               |

| 7A                | 3584                    | 514                  | 1788                | 1794               |

| 7B                | 4096                    | 514                  | 2044                | 2050               |

| 7C                | 4608                    | 770                  | 2300                | 2306               |

| 7D                | 5120                    | 770                  | 2556                | 2562               |

| 7E                | 6144                    | 1026                 | 3068                | 3074               |

| 7F                | 7680                    | 1026                 | 3836                | 3842               |

| MUL=4             |                         |                      |                     |                    |

| 80                | 72                      | 28                   | 24                  | 44                 |

| 81                | 80                      | 28                   | 28                  | 48                 |

| Table 15-7. IIC Divider and Hold Values (Sheet 4 of 6) |

|--------------------------------------------------------|

|--------------------------------------------------------|

# 16.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the MSCAN.

# 16.3.1 Module Memory Map

Figure 16-3 gives an overview on all registers and their individual bits in the MSCAN memory map. The *register address* results from the addition of *base address* and *address offset*. The *base address* is determined at the MCU level and can be found in the MCU memory map description. The *address offset* is defined at the module level.

The MSCAN occupies 64 bytes in the memory space. The base address of the MSCAN module is determined at the MCU level when the MCU is defined. The register decode map is fixed and begins at the first address of the module address offset.

The detailed register descriptions follow in the order they appear in the register map.

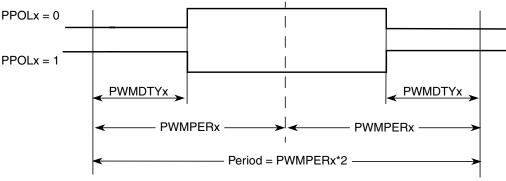

## 19.3.2.14 PWM Channel Duty Registers (PWMDTYx)

There is a dedicated duty register for each channel. The value in this register determines the duty of the associated PWM channel. The duty value is compared to the counter and if it is equal to the counter value a match occurs and the output changes state.

The duty registers for each channel are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to \$00)

- The channel is disabled

In this way, the output of the PWM will always be either the old duty waveform or the new duty waveform, not some variation in between. If the channel is not enabled, then writes to the duty register will go directly to the latches as well as the buffer.

### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active duty due to the double buffering scheme.

See Section 19.4.2.3, "PWM Period and Duty" for more information.

### NOTE

Depending on the polarity bit, the duty registers will contain the count of either the high time or the low time. If the polarity bit is one, the output starts high and then goes low when the duty count is reached, so the duty registers contain a count of the high time. If the polarity bit is zero, the output starts low and then goes high when the duty count is reached, so the duty registers contain a count of the low time.

To calculate the output duty cycle (high time as a% of period) for a particular channel:

• Polarity = 0 (PPOL x = 0)

Duty Cycle = [(PWMPERx-PWMDTYx)/PWMPERx] \* 100%

• Polarity = 1 (PPOLx = 1)

Duty Cycle = [PWMDTYx / PWMPERx] \* 100%

For boundary case programming values, please refer to Section 19.4.2.8, "PWM Boundary Cases".

Module Base + 0x001C = PWMDTY0, 0x001D = PWMDTY1, 0x001E = PWMDTY2, 0x001F = PWMDTY3 Module Base + 0x0020 = PWMDTY4, 0x0021 = PWMDTY5, 0x0022 = PWMDTY6, 0x0023 = PWMDTY7

|        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

Figure 19-16. PWM Channel Duty Registers (PWMDTYx)

Read: Anytime

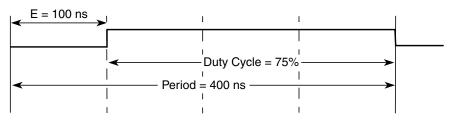

Figure 19-21. PWM Left Aligned Output Example Waveform

## 19.4.2.6 Center Aligned Outputs

For center aligned output mode selection, set the CAEx bit (CAEx = 1) in the PWMCAE register and the corresponding PWM output will be center aligned.

The 8-bit counter operates as an up/down counter in this mode and is set to up whenever the counter is equal to \$00. The counter compares to two registers, a duty register and a period register as shown in the block diagram in Figure 19-19. When the PWM counter matches the duty register, the output flip-flop changes state, causing the PWM waveform to also change state. A match between the PWM counter and the period register changes the counter direction from an up-count to a down-count. When the PWM counter decrements and matches the duty register again, the output flip-flop changes state causing the PWM output to also change state. When the PWM counter decrements and reaches zero, the counter direction changes from a down-count back to an up-count and a load from the double buffer period and duty registers to the associated registers is performed, as described in Section 19.4.2.3, "PWM Period and Duty". The counter counts from 0 up to the value in the period register and then back down to 0. Thus the effective period is PWMPERx\*2.

### NOTE

Changing the PWM output mode from left aligned to center aligned output (or vice versa) while channels are operating can cause irregularities in the PWM output. It is recommended to program the output mode before enabling the PWM channel.

Figure 19-22. PWM Center Aligned Output Waveform

| When SPE = 1                   | Master Mode MSTR = 1                      | Slave Mode MSTR = 0                      |

|--------------------------------|-------------------------------------------|------------------------------------------|

| Normal Mode<br>SPC0 = 0        | Serial Out<br>SPI<br>Serial In MISO       | Serial In MOSI<br>SPI<br>Serial Out MISO |

| Bidirectional Mode<br>SPC0 = 1 | Serial Out<br>SPI<br>BIDIROE<br>Serial In | Serial In<br>SPI<br>Serial Out           |

Table 21-11. Normal Mode and Bidirectional Mode

The direction of each serial I/O pin depends on the BIDIROE bit. If the pin is configured as an output, serial data from the shift register is driven out on the pin. The same pin is also the serial input to the shift register.

- The SCK is output for the master mode and input for the slave mode.

- The  $\overline{SS}$  is the input or output for the master mode, and it is always the input for the slave mode.

- The bidirectional mode does not affect SCK and  $\overline{SS}$  functions.

### NOTE

In bidirectional master mode, with mode fault enabled, both data pins MISO and MOSI can be occupied by the SPI, though MOSI is normally used for transmissions in bidirectional mode and MISO is not used by the SPI. If a mode fault occurs, the SPI is automatically switched to slave mode. In this case MISO becomes occupied by the SPI and MOSI is not used. This must be considered, if the MISO pin is used for another purpose.

## 21.4.6 Error Conditions

The SPI has one error condition:

• Mode fault error

## 21.4.6.1 Mode Fault Error

If the  $\overline{SS}$  input becomes low while the SPI is configured as a master, it indicates a system error where more than one master may be trying to drive the MOSI and SCK lines simultaneously. This condition is not permitted in normal operation, the MODF bit in the SPI status register is set automatically, provided the MODFEN bit is set.

In the special case where the SPI is in master mode and MODFEN bit is cleared, the  $\overline{SS}$  pin is not used by the SPI. In this special case, the mode fault error function is inhibited and MODF remains cleared. In case

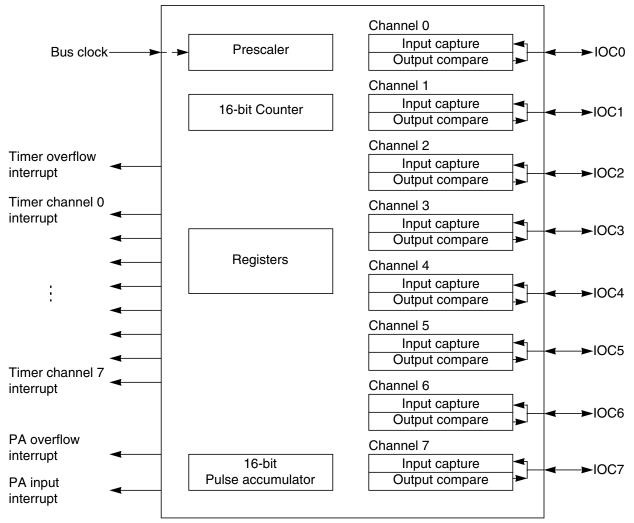

## 22.1.3 Block Diagrams

Figure 22-1. TIM16B8CV2 Block Diagram

# 22.2.7 IOC1 — Input Capture and Output Compare Channel 1 Pin

This pin serves as input capture or output compare for channel 1.

# 22.2.8 IOC0 — Input Capture and Output Compare Channel 0 Pin

This pin serves as input capture or output compare for channel 0.

### NOTE

For the description of interrupts see Section 22.6, "Interrupts".

# 22.3 Memory Map and Register Definition

This section provides a detailed description of all memory and registers.

## 22.3.1 Module Memory Map

The memory map for the TIM16B8CV2 module is given below in Figure 22-5. The address listed for each register is the address offset. The total address for each register is the sum of the base address for the TIM16B8CV2 module and the address offset for each register.

## 22.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

| Register<br>Name |        | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |

|------------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x0000<br>TIOS   | R<br>W | IOS7   | IOS6   | IOS5   | IOS4   | IOS3   | IOS2   | IOS1  | IOS0  |

|                  |        |        |        |        |        |        |        |       |       |

| 0x0001           | R      | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| CFORC            | W      | FOC7   | FOC6   | FOC5   | FOC4   | FOC3   | FOC2   | FOC1  | FOC0  |

|                  | _      |        |        |        |        |        |        |       |       |

| 0x0002<br>OC7M   | R<br>W | OC7M7  | OC7M6  | OC7M5  | OC7M4  | OC7M3  | OC7M2  | OC7M1 | OC7M0 |

| 0x0003<br>OC7D   | R<br>W | OC7D7  | OC7D6  | OC7D5  | OC7D4  | OC7D3  | OC7D2  | OC7D1 | OC7D0 |

| 0x0004<br>TCNTH  | R<br>W | TCNT15 | TCNT14 | TCNT13 | TCNT12 | TCNT11 | TCNT10 | TCNT9 | TCNT8 |

| 0x0005<br>TCNTL  | R<br>W | TCNT7  | TCNT6  | TCNT5  | TCNT4  | TCNT3  | TCNT2  | TCNT1 | TCNT0 |

|                  |        |        |        |        |        |        |        |       |       |

= Unimplemented or Reserved

Figure 22-5. TIM16B8CV2 Register Summary (Sheet 1 of 3)

# Chapter 23 Voltage Regulator (S12VREGL3V3V1)

| Revision<br>Number | Revision Date | Sections<br>Affected | Description of Changes                             |

|--------------------|---------------|----------------------|----------------------------------------------------|

| V01.02             | 09 Sep 2005   | 23.3.2.3/23-822      | - Updates for API external access and LVR flags.   |

| V01.03             | 23 Sep 2005   | 23.3.2.1/23-820      | - VAE reset value is 1.                            |

| V01.04             | 08 Jun 2007   | 23.4.6/23-827        | - Added temperature sensor to customer information |

Table 23-1. Revision History

# 23.1 Introduction

Module VREG\_3V3 is a tri output voltage regulator that provides two separate 1.84V (typical) supplies differing in the amount of current that can be sourced and a 2.82V (typical) supply. The regulator input voltage range is from 3.3V up to 5V (typical).

# 23.1.1 Features

Module VREG\_3V3 includes these distinctive features:

- Three parallel, linear voltage regulators with bandgap reference

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR)

- Low-voltage reset (LVR)

- High Temperature Detect (HTD) with High Temperature Interrupt (HTI)

- Autonomous periodical interrupt (API)

# 23.1.2 Modes of Operation

There are three modes VREG\_3V3 can operate in:

1. Full performance mode (FPM) (MCU is not in stop mode)

The regulator is active, providing the nominal supply voltages with full current sourcing capability. Features LVD (low-voltage detect), LVR (low-voltage reset), and POR (power-on reset) and HTD (High Temperature Detect) are available. The API is available.

2. Reduced power mode (RPM) (MCU is in stop mode)

The purpose is to reduce power consumption of the device. The output voltage may degrade to a lower value than in full performance mode, additionally the current sourcing capability is substantially reduced. Only the POR is available in this mode, LVD, LVR and HTD are disabled. The API is available.

#### Table 26-14. FECCRIX Field Descriptions

| Field | Description                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>ECC Error Register Index</b> — The ECCRIX bits are used to select which word of the FECCR register array is being read. See Section 26.3.2.13, "Flash ECC Error Results Register (FECCR)," for more details. |

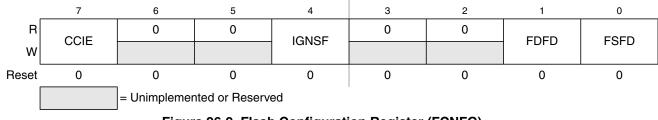

## 26.3.2.5 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU or XGATE.

Offset Module Base + 0x0004

Figure 26-9. Flash Configuration Register (FCNFG)

CCIE, IGNSF, FDFD, and FSFD bits are readable and writable while remaining bits read 0 and are not writable.

| Table 26-15. | FCNFG Field | Descriptions |

|--------------|-------------|--------------|

|--------------|-------------|--------------|

| Field      | Description                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIE  | <ul> <li>Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.</li> <li>0 Command complete interrupt disabled</li> <li>1 An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 26.3.2.7)</li> </ul>                                               |

| 4<br>IGNSF | <ul> <li>Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 26.3.2.8).</li> <li>0 All single bit faults detected during array reads are reported</li> <li>1 Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated</li> </ul> |

| FPOPEN | FPHDIS | FPLDIS | Function <sup>(1)</sup>         |

|--------|--------|--------|---------------------------------|

| 1      | 1      | 1      | No P-Flash Protection           |

| 1      | 1      | 0      | Protected Low Range             |

| 1      | 0      | 1      | Protected High Range            |

| 1      | 0      | 0      | Protected High and Low Ranges   |

| 0      | 1      | 1      | Full P-Flash Memory Protected   |

| 0      | 1      | 0      | Unprotected Low Range           |

| 0      | 0      | 1      | Unprotected High Range          |

| 0      | 0      | 0      | Unprotected High and Low Ranges |

#### Table 26-20. P-Flash Protection Function

1. For range sizes, refer to Table 26-21 and Table 26-22.

#### Table 26-21. P-Flash Protection Higher Address Range

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x7F_F800-0x7F_FFFF  | 2 Kbytes       |

| 01        | 0x7F_F000-0x7F_FFFF  | 4 Kbytes       |

| 10        | 0x7F_E000-0x7F_FFFF  | 8 Kbytes       |

| 11        | 0x7F_C000-0x7F_FFFF  | 16 Kbytes      |

#### Table 26-22. P-Flash Protection Lower Address Range

| FPLS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x7F_8000-0x7F_83FF  | 1 Kbyte        |

| 01        | 0x7F_8000-0x7F_87FF  | 2 Kbytes       |

| 10        | 0x7F_8000-0x7F_8FFF  | 4 Kbytes       |

| 11        | 0x7F_8000-0x7F_9FFF  | 8 Kbytes       |

All possible P-Flash protection scenarios are shown in Figure 26-14. Although the protection scheme is loaded from the Flash memory at global address 0x7F\_FF0C during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

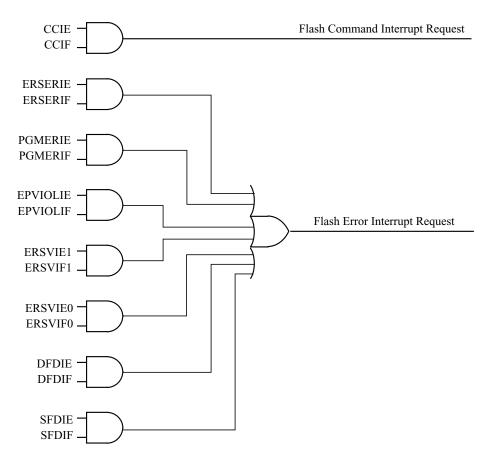

## 26.4.3 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an EEE error or an ECC fault.

| Interrupt Source                   | Interrupt Flag                 | Local Enable                   | Global (CCR)<br>Mask |

|------------------------------------|--------------------------------|--------------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)       | CCIE<br>(FCNFG register)       | I Bit                |

| Flash EEE Erase Error              | ERSERIF<br>(FERSTAT register)  | ERSERIE<br>(FERCNFG register)  | I Bit                |

| Flash EEE Program Error            | PGMERIF<br>(FERSTAT register)  | PGMERIE<br>(FERCNFG register)  | I Bit                |

| Flash EEE Protection Violation     | EPVIOLIF<br>(FERSTAT register) | EPVIOLIE<br>(FERCNFG register) | I Bit                |

| Flash EEE Error Type 1 Violation   | ERSVIF1<br>(FERSTAT register)  | ERSVIE1<br>(FERCNFG register)  | I Bit                |

| Flash EEE Error Type 0 Violation   | ERSVIF0<br>(FERSTAT register)  | ERSVIE0<br>(FERCNFG register)  | I Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register)    | DFDIE<br>(FERCNFG register)    | I Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register)    | SFDIE<br>(FERCNFG register)    | l Bit                |

| Table 26-79. | Flash | Interrupt | Sources |

|--------------|-------|-----------|---------|

|              |       |           |         |

### NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

### 26.4.3.1 Description of Flash Interrupt Operation

The Flash module uses the CCIF flag in combination with the CCIE interrupt enable bit to generate the Flash command interrupt request. The Flash module uses the ERSEIF, PGMEIF, EPVIOLIF, ERSVIF1, ERSVIF0, DFDIF and SFDIF flags in combination with the ERSEIE, PGMEIE, EPVIOLIE, ERSVIE1, ERSVIE0, DFDIE and SFDIE interrupt enable bits to generate the Flash error interrupt request. For a detailed description of the register bits involved, refer to Section 26.3.2.5, "Flash Configuration Register (FCNFG)", Section 26.3.2.6, "Flash Error Configuration Register (FERCNFG)", Section 26.3.2.7, "Flash Status Register (FSTAT)", and Section 26.3.2.8, "Flash Error Status Register (FERSTAT)".

The logic used for generating the Flash module interrupts is shown in Figure 26-27.

| CCOBIX[2:0] | FCCOB Parameters                                                   |              |  |  |  |

|-------------|--------------------------------------------------------------------|--------------|--|--|--|

| 000         | 0x0F                                                               | Not required |  |  |  |

| 001         | Number of 256 byte sectors for the D-Flash user partition (DFPART) |              |  |  |  |

| 010         | Number of 256 byte sectors for buffer RAM EEE partition (ERPART)   |              |  |  |  |

### Table 27-63. Full Partition D-Flash Command FCCOB Requirements

Upon clearing CCIF to launch the Full Partition D-Flash command, the following actions are taken to define a partition within the D-Flash block for direct access (DFPART) and a partition within the buffer RAM for EEE use (ERPART):

- Validate the DFPART and ERPART values provided:

- DFPART <= 128 (maximum number of 256 byte sectors in D-Flash block)

- ERPART <= 16 (maximum number of 256 byte sectors in buffer RAM)

- If ERPART > 0, 128 DFPART >= 12 (minimum number of 256 byte sectors in the D-Flash block required to support EEE)

- If ERPART > 0, ((128-DFPART)/ERPART) >= 8 (minimum ratio of D-Flash EEE space to buffer RAM EEE space to support EEE)

- Erase the D-Flash block and the EEE nonvolatile information register

- Program DFPART to the EEE nonvolatile information register at global address 0x12\_0000 (see Table 27-7)

- Program a duplicate DFPART to the EEE nonvolatile information register at global address 0x12\_0002 (see Table 27-7)

- Program ERPART to the EEE nonvolatile information register at global address 0x12\_0004 (see Table 27-7)

- Program a duplicate ERPART to the EEE nonvolatile information register at global address 0x12\_0006 (see Table 27-7)

The D-Flash user partition will start at global address  $0x10_{0000}$ . The buffer RAM EEE partition will end at global address  $0x13_{FFFF}$ . After the Full Partition D-Flash operation has completed, the CCIF flag will set.

Running the Full Partition D-Flash command a second time will result in the previous partition values and the entire D-Flash memory being erased. The data value written corresponds to the number of 256 byte sectors allocated for either direct D-Flash access (DFPART) or buffer RAM EEE access (ERPART).

# 29.4.1.3 Valid Flash Module Commands

| Table 29-30. | Flash Co | ommands | by | Mode |

|--------------|----------|---------|----|------|

|--------------|----------|---------|----|------|

|      | Command                      |           | Unsecured |                   |                   |           | Secured   |                   |                   |  |

|------|------------------------------|-----------|-----------|-------------------|-------------------|-----------|-----------|-------------------|-------------------|--|

| FCMD |                              | NS<br>(1) | NX<br>(2) | SS <sup>(3)</sup> | ST <sup>(4)</sup> | NS<br>(5) | NX<br>(6) | SS <sup>(7)</sup> | ST <sup>(8)</sup> |  |

| 0x01 | Erase Verify All Blocks      | *         | *         | *                 | *                 | *         | *         | *                 | *                 |  |

| 0x02 | Erase Verify Block           | *         | *         | *                 | *                 | *         | *         | *                 | *                 |  |

| 0x03 | Erase Verify P-Flash Section | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x04 | Read Once                    | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x05 | Load Data Field              | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x06 | Program P-Flash              | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x07 | Program Once                 | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x08 | Erase All Blocks             |           |           | *                 | *                 |           |           | *                 | *                 |  |

| 0x09 | Erase P-Flash Block          | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x0A | Erase P-Flash Sector         | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x0B | Unsecure Flash               |           |           | *                 | *                 |           |           | *                 | *                 |  |

| 0x0C | Verify Backdoor Access Key   | *         |           |                   |                   | *         |           |                   |                   |  |

| 0x0D | Set User Margin Level        | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x0E | Set Field Margin Level       |           |           | *                 | *                 |           |           |                   |                   |  |

| 0x0F | Full Partition D-Flash       |           |           | *                 | *                 |           |           |                   |                   |  |

| 0x10 | Erase Verify D-Flash Section | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x11 | Program D-Flash              | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x12 | Erase D-Flash Sector         | *         | *         | *                 | *                 | *         |           |                   |                   |  |

| 0x13 | Enable EEPROM Emulation      | *         | *         | *                 | *                 | *         | *         | *                 | *                 |  |

| 0x14 | Disable EEPROM Emulation     | *         | *         | *                 | *                 | *         | *         | *                 | *                 |  |

| 0x15 | EEPROM Emulation Query       | *         | *         | *                 | *                 | *         | *         | *                 | *                 |  |

| 0x20 | Partition D-Flash            | *         | *         | *                 | *                 | *         | *         | *                 | *                 |  |

1. Unsecured Normal Single Chip mode.

2. Unsecured Normal Expanded mode.

3. Unsecured Special Single Chip mode.

4. Unsecured Special Mode.

5. Secured Normal Single Chip mode.

6. Secured Normal Expanded mode.

7. Secured Special Single Chip mode.

8. Secured Special Mode.

Figure 29-27. Flash Module Interrupts Implementation

## 29.4.4 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 29.4.3, "Interrupts").

## 29.4.5 Stop Mode

If a Flash command is active (CCIF = 0) or an EE-Emulation operation is pending when the MCU requests stop mode, the current Flash operation will be completed before the CPU is allowed to enter stop mode.

# 29.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 29-12). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x7F\_FF0F.