Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 1MB (1M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xep100w1mal |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>)</b> P |                                               |

|------------|-----------------------------------------------|

| Chapter 26 | 384 KByte Flash Module (S12XFTM384K2V1)953    |

| Chapter 27 | 512 KByte Flash Module (S12XFTM512K3V1)1016   |

| Chapter 28 | 768 KByte Flash Module (S12XFTM768K4V2)1077   |

| Chapter 29 | 1024 KByte Flash Module (S12XFTM1024K5V2)1140 |

| Appendix A | Electrical Characteristics1201                |

| Appendix B | Package Information1258                       |

| Appendix C | PCB Layout Guidelines1260                     |

| Appendix D | Derivative Differences                        |

| Appendix E | Detailed Register Address Map                 |

| Appendix F | Ordering Information                          |

# 1.2.3.43 PK[3:0] / ADDR[19:16] / IQSTAT[3:0] — Port K I/O Pins [3:0]

PK3-PK0 are general-purpose input or output pins. In MCU expanded modes of operation, these pins provide the expanded address ADDR[19:16] for the external bus and carry instruction pipe information.

# 1.2.3.44 PL7 / TXD7 — Port L I/O Pin 7

PL7 is a general-purpose input or output pin. It can be configured as the transmit pin TXD of serial communication interface 7 (SCI7).

## 1.2.3.45 PL6 / RXD7 — Port L I/O Pin 6

PL6 is a general-purpose input or output pin. It can be configured as the receive pin RXD of serial communication interface 7 (SCI7).

## 1.2.3.46 PL5 / TXD6 — Port L I/O Pin 5

PL5 is a general-purpose input or output pin. It can be configured as the transmit pin TXD of serial communication interface 6 (SCI6).

## 1.2.3.47 PL4 / RXD6 — Port L I/O Pin 4

PL4 is a general-purpose input or output pin. It can be configured as the receive pin RXD of serial communication interface 6 (SCI6).

## 1.2.3.48 PL3 / TXD5 — Port L I/O Pin 3

PL3 is a general-purpose input or output pin. It can be configured as the transmit pin TXD of serial communication interface 5 (SCI5).

## 1.2.3.49 PL2 / RXD5 — Port L I/O Pin 2

PL2 is a general-purpose input or output pin. It can be configured as the receive pin RXD of serial communication interface 5 (SCI5).

## 1.2.3.50 PL1 / TXD4 — Port L I/O Pin 1

PL1 is a general-purpose input or output pin. It can be configured as the transmit pin TXD of serial communication interface 4 (SCI4).

## 1.2.3.51 PL0 / RXD4 — Port L I/O Pin 0

PL0 is a general-purpose input or output pin. It can be configured as the receive pin RXD of serial communication interface 4 (SCI4).

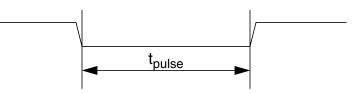

Figure 2-109. Pulse Illustration

A valid edge on an input is detected if 4 consecutive samples of a passive level are followed by 4 consecutive samples of an active level directly or indirectly.

The filters are continuously clocked by the bus clock in RUN and WAIT mode. In STOP mode the clock is generated by an RC-oscillator in the Port Integration Module. To maximize current saving the RC oscillator runs only if the following condition is true on any pin individually:

Sample count <= 4 and interrupt enabled (PIE=1) and interrupt flag not set (PIF=0)

# 2.5 Initialization Information

## 2.5.1 Port Data and Data Direction Register writes

It is not recommended to write PORTx/PTx and DDRx in a word access. When changing the register pins from inputs to outputs, the data may have extra transitions during the write access. Initialize the port data register before enabling the outputs.

#### ter 10 XGATE (S12XGATEV3)

**Section** for information on how to select priority levels for XGATE threads. Low priority threads (interrupt levels 1 to 3) can be interrupted by high priority threads (interrupt levels 4 to 7). High priority threads are not interruptible. The register content of an interrupted thread is maintained and restored by the XGATE hardware.

To signal the completion of a task the XGATE is able to send interrupts to the S12X\_CPU. Each XGATE channel has its own interrupt vector. Refer to the S12X\_INT Section for detailed information.

The XGATE module also provides a set of hardware semaphores which are necessary to ensure data consistency whenever RAM locations or peripherals are shared with the S12X\_CPU.

The following sections describe the components of the XGATE module in further detail.

## 10.4.1 XGATE RISC Core

The RISC core is a 16 bit processor with an instruction set that is well suited for data transfers, bit manipulations, and simple arithmetic operations (see Section 10.8, "Instruction Set").

It is able to access the MCU's internal memories and peripherals without blocking these resources from the  $S12X\_CPU^1$ . Whenever the  $S12X\_CPU$  and the RISC core access the same resource, the RISC core will be stalled until the resource becomes available again.<sup>1</sup>

The XGATE offers a high access rate to the MCU's internal RAM. Depending on the bus load, the RISC core can perform up to two RAM accesses per S12X\_CPU bus cycle.

Bus accesses to peripheral registers or flash are slower. A transfer rate of one bus access per S12X\_CPU cycle can not be exceeded.

The XGATE module is intended to execute short interrupt service routines that are triggered by peripheral modules or by software.

|    | Register Block     |   |    | F | Program Cou | unter            |

|----|--------------------|---|----|---|-------------|------------------|

| 15 | R7 (Stack Pointer) | 0 | 15 |   | PC          | 0                |

| 15 | R6                 | 0 |    |   |             | Condition        |

| 15 | R5                 | 0 |    |   |             | Code<br>Register |

| 15 | R4                 | 0 |    |   |             | NZVC             |

| 15 | R3                 | 0 |    |   |             | 3210             |

| 15 | R2                 | 0 |    |   |             |                  |

| 15 | R1(Data Pointer)   | 0 |    |   |             |                  |

| 15 | R0 = 0             | 0 | ]  |   |             |                  |

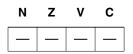

## 10.4.2 Programmer's Model

### Figure 10-22. Programmer's Model

1. With the exception of PRR registers (see Section "S12X\_MMC").

# BLO

## Branch if Carry Set (Same as BCS)

# BLO

## Operation

If C = 1, then PC +  $0002 + (REL9 \le 1) \Rightarrow PC$

Branch instruction to compare unsigned numbers.

## Branch if RS1 < RS2:

SUB R0,RS1,RS2 BLO REL9

## **CCR Effects**

- N: Not affected.

- Z: Not affected.

- V: Not affected.

- C: Not affected.

## **Code and CPU Cycles**

| Source Form | Address<br>Mode | Machine Code       | Cycles |

|-------------|-----------------|--------------------|--------|

| BLO REL9    | REL9            | 0 0 1 0 0 0 1 REL9 | PP/P   |

# 11.6.1 Description of Interrupt Operation

## 11.6.1.1 Real Time Interrupt

The S12XECRG generates a real time interrupt when the selected interrupt time period elapses. RTI interrupts are locally disabled by setting the RTIE bit to zero. The real time interrupt flag (RTIF) is set to 1 when a timeout occurs, and is cleared to 0 by writing a 1 to the RTIF bit.

The RTI continues to run during Pseudo Stop Mode if the PRE bit is set to 1. This feature can be used for periodic wakeup from Pseudo Stop if the RTI interrupt is enabled.

## 11.6.1.2 IPLL Lock Interrupt

The S12XECRG generates a IPLL Lock interrupt when the LOCK condition of the IPLL has changed, either from a locked state to an unlocked state or vice versa. Lock interrupts are locally disabled by setting the LOCKIE bit to zero. The IPLL Lock interrupt flag (LOCKIF) is set to1 when the LOCK condition has changed, and is cleared to 0 by writing a 1 to the LOCKIF bit.

## 11.6.1.3 Self Clock Mode Interrupt

The S12XECRG generates a Self Clock Mode interrupt when the SCM condition of the system has changed, either entered or exited Self Clock Mode. SCM conditions are caused by a failing clock quality check after power on reset (POR) or low voltage reset (LVR) or recovery from Full Stop Mode (PSTP = 0) or Clock Monitor failure. For details on the clock quality check refer to Section 11.4.1.4, "Clock Quality Checker". If the clock monitor is enabled (CME = 1) a loss of external clock will also cause a SCM condition (SCME = 1).

SCM interrupts are locally disabled by setting the SCMIE bit to zero. The SCM interrupt flag (SCMIF) is set to1 when the SCM condition has changed, and is cleared to 0 by writing a 1 to the SCMIF bit.

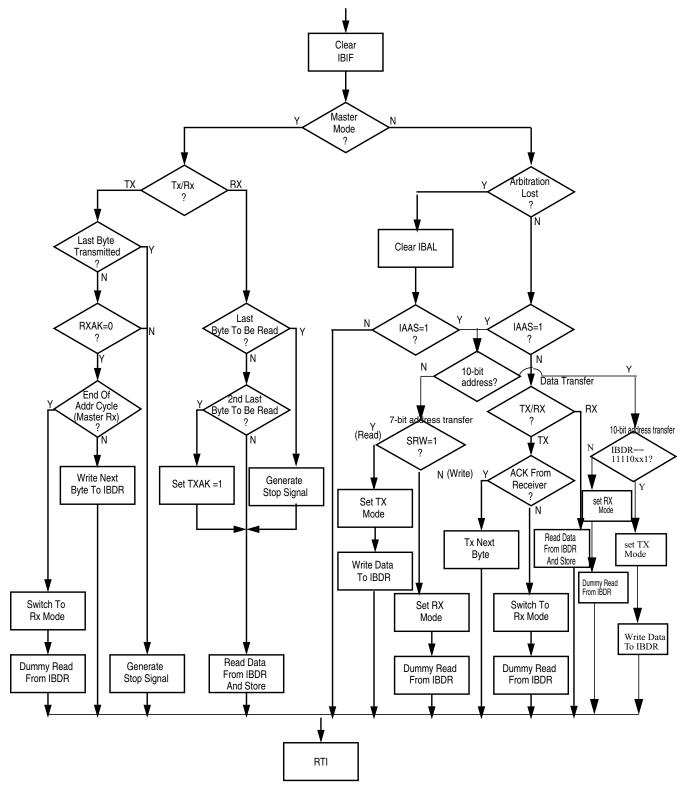

attempt to engage the bus is failed. When considering these cases, the slave service routine should test the IBAL first and the software should clear the IBAL bit if it is set.

Figure 15-15. Flow-Chart of Typical IIC Interrupt Routine

MC9S12XE-Family Reference Manual Rev. 1.25

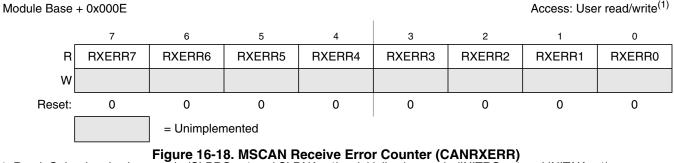

1. Read: Anytime

Write: Anytime when out of initialization mode; exceptions are read-only RXACT and SYNCH, RXFRM (which is set by the module only), and INITRQ (which is also writable in initialization mode)

## NOTE

The CANCTL0 register, except WUPE, INITRQ, and SLPRQ, is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable again as soon as the initialization mode is exited (INITRQ = 0 and INITAK = 0).

#### Table 16-3. CANCTL0 Register Field Descriptions

| Field                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXFRM                | <ul> <li>Received Frame Flag — This bit is read and clear only. It is set when a receiver has received a valid message correctly, independently of the filter configuration. After it is set, it remains set until cleared by software or reset. Clearing is done by writing a 1. Writing a 0 is ignored. This bit is not valid in loopback mode.</li> <li>0 No valid message was received since last clearing this flag</li> <li>1 A valid message was received since last clearing of this flag</li> </ul>                                                                                                                                                                                                                               |

| 6<br>RXACT                | <ul> <li>Receiver Active Status — This read-only flag indicates the MSCAN is receiving a message<sup>(1)</sup>. The flag is controlled by the receiver front end. This bit is not valid in loopback mode.</li> <li>0 MSCAN is transmitting or idle</li> <li>1 MSCAN is receiving a message (including when arbitration is lost)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5<br>CSWAI <sup>(2)</sup> | <ul> <li>CAN Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling all the clocks at the CPU bus interface to the MSCAN module.</li> <li>0 The module is not affected during wait mode</li> <li>1 The module ceases to be clocked during wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>SYNCH                | <ul> <li>Synchronized Status — This read-only flag indicates whether the MSCAN is synchronized to the CAN bus and able to participate in the communication process. It is set and cleared by the MSCAN.</li> <li>0 MSCAN is not synchronized to the CAN bus</li> <li>1 MSCAN is synchronized to the CAN bus</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3<br>TIME                 | <ul> <li>Timer Enable — This bit activates an internal 16-bit wide free running timer which is clocked by the bit clock rate. If the timer is enabled, a 16-bit time stamp will be assigned to each transmitted/received message within the active TX/RX buffer. Right after the EOF of a valid message on the CAN bus, the time stamp is written to the highest bytes (0x000E, 0x000F) in the appropriate buffer (see Section 16.3.3, "Programmer's Model of Message Storage"). In loopback mode no receive timestamp is generated. The internal timer is reset (all bits set to 0) when disabled. This bit is held low in initialization mode.</li> <li>0 Disable internal MSCAN timer</li> <li>1 Enable internal MSCAN timer</li> </ul> |

| 2<br>WUPE <sup>(3)</sup>  | <ul> <li>Wake-Up Enable — This configuration bit allows the MSCAN to restart from sleep mode or from power down mode (entered from sleep) when traffic on CAN is detected (see Section 16.4.5.5, "MSCAN Sleep Mode"). This bit must be configured before sleep mode entry for the selected function to take effect.</li> <li>0 Wake-up disabled — The MSCAN ignores traffic on CAN</li> <li>1 Wake-up enabled — The MSCAN is able to restart</li> </ul>                                                                                                                                                                                                                                                                                    |

I

1. Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

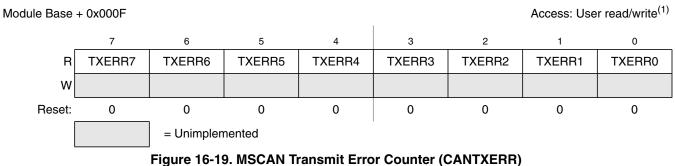

## 16.3.2.16 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

1. Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

#### Chapter 17 Periodic Interrupt Timer (S12PIT24B8CV2)

|                                        | MOVB                | #\$01,PITINTE              | ; enable interupt channel 0                                                                   |

|----------------------------------------|---------------------|----------------------------|-----------------------------------------------------------------------------------------------|

|                                        | MOVB                | #\$80,PITCFLMT             | ; enable PIT                                                                                  |

|                                        | CLI                 |                            | ; clear Interupt disable Mask bit                                                             |

| .*****************<br>?                | **** Main P         | rogram ****************    | *****                                                                                         |

| MAIN:                                  | BRA *               |                            | ; loop until interrupt                                                                        |

| •************************************* | **** Channe         | 10 Interupt Routine ****** | ******                                                                                        |

| CH0_ISR:                               | LDAA<br>MOVB<br>RTI | PITTF<br>#\$01,PITTF       | ; 8 bit read of PIT time out flags<br>; clear PIT channel 0 time out flag<br>; return to MAIN |

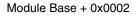

Read: Anytime

Write: Anytime

## NOTE

Register bits PCLK0 to PCLK7 can be written anytime. If a clock select is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

| Table 19-4 | . PWMCLK | Field | Descriptions |

|------------|----------|-------|--------------|

|------------|----------|-------|--------------|

| Field      | Description                                                                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PCLK7 | Pulse Width Channel 7 Clock Select         0       Clock B is the clock source for PWM channel 7.         1       Clock SB is the clock source for PWM channel 7. |

| 6<br>PCLK6 | Pulse Width Channel 6 Clock Select         0       Clock B is the clock source for PWM channel 6.         1       Clock SB is the clock source for PWM channel 6. |

| 5<br>PCLK5 | Pulse Width Channel 5 Clock Select0Clock A is the clock source for PWM channel 5.1Clock SA is the clock source for PWM channel 5.                                 |

| 4<br>PCLK4 | Pulse Width Channel 4 Clock Select         0       Clock A is the clock source for PWM channel 4.         1       Clock SA is the clock source for PWM channel 4. |

| 3<br>PCLK3 | Pulse Width Channel 3 Clock Select         0       Clock B is the clock source for PWM channel 3.         1       Clock SB is the clock source for PWM channel 3. |

| 2<br>PCLK2 | Pulse Width Channel 2 Clock Select         0       Clock B is the clock source for PWM channel 2.         1       Clock SB is the clock source for PWM channel 2. |

| 1<br>PCLK1 | Pulse Width Channel 1 Clock Select         0 Clock A is the clock source for PWM channel 1.         1 Clock SA is the clock source for PWM channel 1.             |

| 0<br>PCLK0 | Pulse Width Channel 0 Clock Select         0 Clock A is the clock source for PWM channel 0.         1 Clock SA is the clock source for PWM channel 0.             |

## 19.3.2.4 PWM Prescale Clock Select Register (PWMPRCLK)

This register selects the prescale clock source for clocks A and B independently.

MC9S12XE-Family Reference Manual Rev. 1.25

| Register                           | Error Bit | Error Condition                                                |

|------------------------------------|-----------|----------------------------------------------------------------|

| ACCERR                             |           | Set if CCOBIX[2:0] != 000 at command launch                    |

|                                    | AUCENN    | Set if command not available in current mode (see Table 24-30) |

| FSTAT FPVIOL<br>MGSTAT1<br>MGSTAT0 |           | None                                                           |

|                                    |           | None                                                           |

|                                    |           | None                                                           |

| FERSTAT                            | EPVIOLIF  | None                                                           |

Table 24-74. EEPROM Emulation Query Command Error Handling

## 24.4.2.21 Partition D-Flash Command

The Partition D-Flash command allows the user to allocate sectors within the D-Flash block for applications and a partition within the buffer RAM for EEPROM access. The D-Flash block consists of 32 sectors with 256 bytes per sector. The Erase All Blocks command must be run prior to launching the Partition D-Flash command.

Table 24-75. Partition D-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                   |              |  |  |

|-------------|--------------------------------------------------------------------|--------------|--|--|

| 000         | 0x20                                                               | Not required |  |  |

| 001         | Number of 256 byte sectors for the D-Flash user partition (DFPART) |              |  |  |

| 010         | Number of 256 byte sectors for buffer RAM EEE partition (ERPART)   |              |  |  |

Upon clearing CCIF to launch the Partition D-Flash command, the following actions are taken to define a partition within the D-Flash block for direct access (DFPART) and a partition within the buffer RAM for EEE use (ERPART):

- Validate the DFPART and ERPART values provided:

- DFPART <= 128 (maximum number of 256 byte sectors in D-Flash block)

- ERPART <= 8 (maximum number of 256 byte sectors in buffer RAM)

- If ERPART > 0, 128 DFPART >= 12 (minimum number of 256 byte sectors in the D-Flash block required to support EEE)

- If ERPART > 0, ((128-DFPART)/ERPART) >= 8 (minimum ratio of D-Flash EEE space to buffer RAM EEE space to support EEE)

- Erase verify the D-Flash block and the EEE nonvolatile information register

- Program DFPART to the EEE nonvolatile information register at global address 0x12\_0000 (see Table 24-7)

- Program a duplicate DFPART to the EEE nonvolatile information register at global address 0x12\_0002 (see Table 24-7)

MC9S12XE-Family Reference Manual Rev. 1.25

# Chapter 25 256 KByte Flash Module (S12XFTM256K2V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                                                                                                                 |

|--------------------|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.08             | 14 Nov 2007      | 25.5.2/25-951<br>25.4.2/25-927 | <ul> <li>Changed terminology from 'word program' to "Program P-Flash' in the BDM unsecuring description, Section 25.5.2</li> <li>Added requirement that user not write any Flash module register during</li> </ul>                     |

|                    |                  | 20.4.2/20-927                  | execution of commands 'Erase All Blocks', Section 25.4.2.8, and 'Unsecure Flash', Section 25.4.2.11                                                                                                                                    |

|                    |                  | 25.4.2.8/25-933                | - Added statement that security is released upon successful completion of command 'Erase All Blocks', Section 25.4.2.8                                                                                                                 |

| V01.09             | 19 Dec 2007      | 25.4.2.5/25-930                | - Corrected Error Handling table for Load Data Field command                                                                                                                                                                           |

|                    |                  | 25.4.2/25-927                  | - Corrected Error Handling table for Full Partition D-Flash, Partition D-Flash, and EEPROM Emulation Query commands                                                                                                                    |

|                    |                  | 25.3.1/25-896                  | - Corrected P-Flash IFR Accessibility table                                                                                                                                                                                            |

| V01.10             | 25 Sep 2009      | 25.1/25-891                    | - Clarify single bit fault correction for P-Flash phrase                                                                                                                                                                               |

|                    |                  | 25.3.2.1/25-903                | - Expand FDIV vs OSCCLK Frequency table                                                                                                                                                                                                |

|                    |                  | 25.4.2.4/25-930                | - Add statement concerning code runaway when executing Read Once command from Flash block containing associated fields                                                                                                                 |

|                    |                  | 25.4.2.7/25-932                | - Add statement concerning code runaway when executing Program Once command from Flash block containing associated fields                                                                                                              |

|                    |                  | 25.4.2.12/25-<br>936           | <ul> <li>Add statement concerning code runaway when executing Verify Backdoor</li> <li>Access Key command from Flash block containing associated fields</li> <li>Relate Key 0 to associated Backdoor Comparison Key address</li> </ul> |

|                    |                  | 25.4.2.12/25-                  | - Change "power down reset" to "reset"                                                                                                                                                                                                 |

|                    |                  | 936                            | - Add ACCERR condition for Disable EEPROM Emulation command                                                                                                                                                                            |

|                    |                  | 25.4.2.12/25-                  | The following changes were made to clarify module behavior related to Flash                                                                                                                                                            |

|                    |                  | 936                            | register access during reset sequence and while Flash commands are active:                                                                                                                                                             |

|                    |                  | 25.4.2.20/25-                  | - Add caution concerning register writes while command is active                                                                                                                                                                       |

|                    |                  | 945                            | - Writes to FCLKDIV are allowed during reset sequence while CCIF is clear                                                                                                                                                              |

|                    |                  |                                | - Add caution concerning register writes while command is active<br>- Writes to FCCOBIX, FCCOBHI, FCCOBLO registers are ignored during                                                                                                 |

|                    |                  | 25.3.2/25-901                  | reset sequence                                                                                                                                                                                                                         |

|                    |                  | 25.3.2.1/25-903                |                                                                                                                                                                                                                                        |

|                    |                  | 25.4.1.2/25-922                |                                                                                                                                                                                                                                        |

|                    |                  | 25.6/25-951                    |                                                                                                                                                                                                                                        |

|                    |                  |                                |                                                                                                                                                                                                                                        |

### Table 25-1. Revision History

## 25.1 Introduction

The FTM256K2 module implements the following:

• 256 Kbytes of P-Flash (Program Flash) memory, consisting of 2 physical Flash blocks, intended primarily for nonvolatile code storage

## 26.4.2.10 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| 000         | 0x0A                                                                                                                     | Global address [22:16] to identify<br>P-Flash block to be erased |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 26.1.2.1 for the P-Flash sector size. |                                                                  |  |

Table 26-51. Erase P-Flash Sector Command FCCOB Requirements

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| Register              | Error Bit | Error Condition                                                                     |

|-----------------------|-----------|-------------------------------------------------------------------------------------|

|                       |           | Set if CCOBIX[2:0] != 001 at command launch                                         |

|                       |           | Set if a Load Data Field command sequence is currently active                       |

|                       | ACCERR    | Set if command not available in current mode (see Table 26-30)                      |

|                       |           | Set if an invalid global address [22:16] is supplied <sup>(1)</sup>                 |

| FSTAT                 |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|                       | FPVIOL    | Set if the selected P-Flash sector is protected                                     |

|                       | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|                       | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

| FERSTAT EPVIOLIF None |           | None                                                                                |

Table 26-52. Erase P-Flash Sector Command Error Handling

1. As defined by the memory map for FTM512K3.

## 26.4.2.11 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and D-Flash memory space and, if the erase is successful, will release security.

### Table 26-53. Unsecure Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |  |

|-------------|------------------|--------------|--|--|--|

| 000         | 0x0B             | Not required |  |  |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and D-Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security

| Register | Error Bit | Error Condition                                                                     |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                       |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 27-30)                      |  |  |  |  |

|          |           | Set if an invalid global address [22:0] is supplied                                 |  |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |  |

|          |           | Set if the global address [22:0] points to the D-Flash EEE partition                |  |  |  |  |

|          | FPVIOL    | None                                                                                |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                |  |  |  |  |

## 27.4.2.19 Enable EEPROM Emulation Command

MGSTAT0

**EPVIOLIF**

None

None

The Enable EEPROM Emulation command causes the Memory Controller to enable EEE activity. EEE activity is disabled after any reset.

Table 27-71. Enable EEPROM Emulation Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |  |

|-------------|------------------|--------------|--|--|--|

| 000         | 0x13             | Not required |  |  |  |

Upon clearing CCIF to launch the Enable EEPROM Emulation command, the CCIF flag will set after the Memory Controller enables EEE operations using the contents of the EEE tag RAM and tag counter. The Full Partition D-Flash or the Partition D-Flash command must be run prior to launching the Enable EEPROM Emulation command.

|          | Table 27-72. Enable EEF Nom Enhalation Command Error Handling |                                                                               |  |  |  |  |  |

|----------|---------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| Register | Error Bit                                                     | Error Condition                                                               |  |  |  |  |  |

|          |                                                               | Set if CCOBIX[2:0] != 000 at command launch                                   |  |  |  |  |  |

| FSTAT    | ACCERR                                                        | Set if a Load Data Field command sequence is currently active                 |  |  |  |  |  |

|          |                                                               | Set if Full Partition D-Flash or Partition D-Flash command not previously run |  |  |  |  |  |

| FOTAL    | FPVIOL                                                        | None                                                                          |  |  |  |  |  |

|          | MGSTAT1                                                       | None                                                                          |  |  |  |  |  |

FERSTAT

| SEC[1:0] | Status of Security     |

|----------|------------------------|

| 00       | SECURED                |

| 01       | SECURED <sup>(1)</sup> |

| 10       | UNSECURED              |

| 11       | SECURED                |

Table 29-12. Flash Security States

1. Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 29.5.

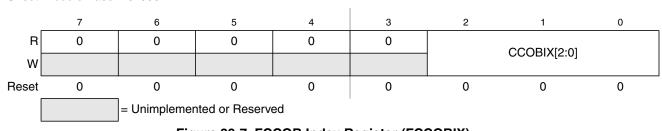

## 29.3.2.3 Flash CCOB Index Register (FCCOBIX)

Offset Module Base + 0x0002

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Figure 29-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

Table 29-13. FCCOBIX Field Descriptions

| Field              | Description                                                                                                                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See Section 29.3.2.11, "Flash Common Command Object Register (FCCOB)," for more details. |

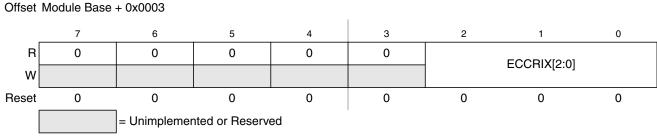

## 29.3.2.4 Flash ECCR Index Register (FECCRIX)

The FECCRIX register is used to index the FECCR register for ECC fault reporting.

## Figure 29-8. FECCR Index Register (FECCRIX)

ECCRIX bits are readable and writable while remaining bits read 0 and are not writable.

MC9S12XE-Family Reference Manual Rev. 1.25

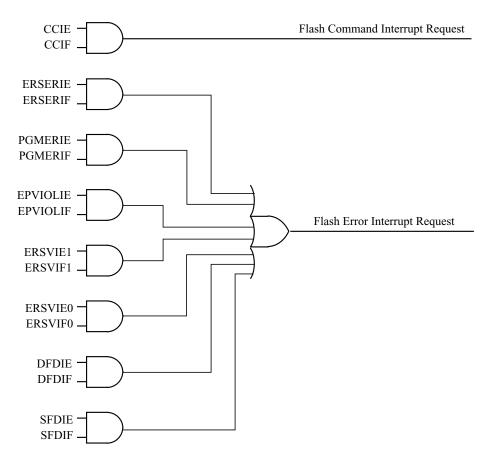

Figure 29-27. Flash Module Interrupts Implementation

## 29.4.4 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 29.4.3, "Interrupts").

## 29.4.5 Stop Mode

If a Flash command is active (CCIF = 0) or an EE-Emulation operation is pending when the MCU requests stop mode, the current Flash operation will be completed before the CPU is allowed to enter stop mode.

## 29.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 29-12). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0x7F\_FF0F.

#### A.3.1.24 **EEE Copy Down**

The typical EEE copy down time is given by the following equation

$$t_{dfcd} = (14000 + (316 \cdot ERPART) + (1500 \cdot (124 - DFPART))) \times \frac{1}{f_{NVMBUS}}$$

The maximum EEE copy down time is given by the following equation

$$t_{dfcd} = (34000 + (316 \cdot \text{ERPART}) + (1500 \cdot (124 - \text{DFPART}))) \times \frac{1}{f_{\text{NVMBUS}}}$$

Worst case for Enable EEPROM Emulation allows for all the EEE records to have to be copied which is a very low probability scenario only likely in the case that the EEE is mostly full of unchanging data (the records for which are stored in consecutive D-Flash sectors).

| Num | С | Rating                                                             | Symbol              | Min | Тур                | Max                   | Unit             |

|-----|---|--------------------------------------------------------------------|---------------------|-----|--------------------|-----------------------|------------------|

| 1   | D | External oscillator clock                                          | f <sub>NVMOSC</sub> | 2   | _                  | 50 <sup>(1)</sup>     | MHz              |

| 2   | D | Bus frequency for programming or erase operations                  | f <sub>NVMBUS</sub> | 1   | _                  | 50                    | MHz              |

| 3   | D | Operating frequency                                                | f <sub>NVMOP</sub>  | 800 | _                  | 1050                  | kHz              |

| 4   | D | P-Flash phrase programming                                         | t <sub>bwpgm</sub>  | _   | 162                | 173                   | μs               |

| 5a  | D | P- Flash phrase program time using D-LOAD on 4 blocks              | t <sub>bwpgm4</sub> | _   | 231                | 264                   | μs               |

| 5b  | D | P-Flash phrase program time using D-LOAD on 3 blocks               | t <sub>bwpgm3</sub> | _   | 208                | 233                   | μs               |

| 5c  | D | P-Flash phrase program time using D-LOAD on 2 blocks               | t <sub>bwpgm2</sub> | _   | 185                | 202                   | μs               |

| 6   | Ρ | P-Flash sector erase time                                          | t <sub>era</sub>    | _   | 20                 | 21                    | ms               |

| 7   | Ρ | Erase All Blocks (Mass erase) time                                 | t <sub>mass</sub>   | _   | 101                | 102                   | ms               |

| 7a  | D | Unsecure Flash                                                     | t <sub>uns</sub>    | _   | 101                | 102                   | ms               |

| 8   | D | P-Flash erase verify (blank check) time <sup>(2)</sup>             | t <sub>check</sub>  | _   | _                  | 33500 <sup>2</sup>    | t <sub>cyc</sub> |

| 9a  | D | D-Flash word programming one word                                  | t <sub>dpgm</sub>   | _   | 88                 | 95                    | μs               |

| 9b  | D | D-Flash word programming two words                                 | t <sub>dpgm</sub>   | _   | 153                | 165                   | μs               |

| 9c  | D | D-Flash word programming three words                               | t <sub>dpgm</sub>   | _   | 212                | 230                   | μs               |

| 9d  | D | D-Flash word programming four words                                | t <sub>dpgm</sub>   | _   | 282                | 316                   | μs               |

| 9e  | D | D-Flash word programming four words crossing row boundary          | t <sub>dpgm</sub>   | _   | 298                | 342                   | μs               |

| 10  | D | D-Flash sector erase time                                          | t <sub>eradf</sub>  | _   | 5.2 <sup>(3)</sup> | 21                    | ms               |

| 11  | D | D-Flash erase verify (blank check) time                            | t <sub>check</sub>  | _   | _                  | 17500                 | t <sub>cyc</sub> |

| 12  | D | EEE copy down (mask sets 5M48H, 3M25J, 2M53J, 1M12S, 1N35H, 1N36H) | t <sub>dfrcd</sub>  | _   | 255000             | 275000 <sup>(4)</sup> | t <sub>cyc</sub> |

| 12  | D | EEE copy down (other mask sets)                                    | t <sub>dfrcd</sub>  | _   | 205000             | 225000 <sup>(5)</sup> | t <sub>cyc</sub> |

| Table | Δ-19  | NVM | Timina  | Characteristics |

|-------|-------|-----|---------|-----------------|

| lable | A-13. |     | rinning | Characteristics |

Hostington of oscillator in crystal mode apply.

Valid for both "Erase verify all" or "Erase verify block" on 256K block without failing locations

This is a typical value for a new device

Maximum partitioning

#### **Output Loads** A.5

#### A.5.1 **Resistive Loads**

The voltage regulator is intended to supply the internal logic and oscillator. It allows no external DC loads.

#### A.5.2 **Capacitive Loads**

The capacitive loads are specified in Table A-22. Ceramic capacitors with X7R dielectricum are required.

| Num | Characteristic                    | Symbol                | Min | Recommended | Max | Unit |

|-----|-----------------------------------|-----------------------|-----|-------------|-----|------|

| 1   | VDD/VDDF external capacitive load | C <sub>DDext</sub>    | 176 | 220         | 264 | nF   |

| 3   | VDDPLL external capacitive load   | C <sub>DDPLLext</sub> | 80  | 220         | 264 | nF   |

Table A-22. - Required Capacitive Loads

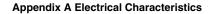

#### A.5.3 Chip Power-up and Voltage Drops

LVI (low voltage interrupt), POR (power-on reset) and LVRs (low voltage reset) handle chip power-up or drops of the supply voltage. Their function is shown in Figure A-3.

Figure A-3. MC9S12XE-Family - Chip Power-up and Voltage Drops (not scaled)

## 0x0380-0x03BF XGATE Map (Sheet 2 of 3)

| Address | Name      |             | Bit 7                     | Bit 6   | Bit 5   | Bit 4      | Bit 3        | Bit 2   | Bit 1   | Bit 0 |

|---------|-----------|-------------|---------------------------|---------|---------|------------|--------------|---------|---------|-------|

| 0x0396  | XGIF      | R<br>W      | XGIF_0F                   | XGIF_0E | XGIF_0D | XGIF_0C    | XGIF_0B      | XGIF_0A | XGIF_09 | 0     |

| 0x0397  | XGIF      | R           | 0                         | 0       | 0       | 0          | 0            | 0       | 0       | 0     |

| 0x0398  | XGSWTM    | W<br>R<br>W | 0                         | 0       | 0       | 0<br>XGSW/ | 0<br>TM[7:0] | 0       | 0       | 0     |

| 0x0399  | XGSWT     | R           | XGSWTM[7:0]<br>XGSWT[7:0] |         |         |            |              |         |         |       |

| 0x039A  | XGSEMM    | R<br>W      | 0                         | 0       | 0       | 0<br>XGSEN | 0<br>/M[7:0] | 0       | 0       | 0     |

| 0x039B  | XGSEM     | R           | XGSEM[7:0]                |         |         |            |              |         |         |       |

| 0x039C  | Reserved  | R           | 0                         | 0       | 0       | 0          | 0            | 0       | 0       | 0     |

| 0x039D  | XGCCR     | R<br>W      | 0                         | 0       | 0       | 0          | XGN          | XGZ     | XGV     | XGC   |

| 0x039E  | XGPC (hi) | R<br>W      | XGPC[15:8]                |         |         |            |              |         |         |       |

| 0x039F  | XGPC (lo) | R<br>W      | XGPC[7:0]                 |         |         |            |              |         |         |       |

| 0x03A0  | Reserved  | R<br>W      | 0                         | 0       | 0       | 0          | 0            | 0       | 0       | 0     |

| 0x03A1  | Reserved  | R<br>W      | 0                         | 0       | 0       | 0          | 0            | 0       | 0       | 0     |

| 0x03A2  | XGR1 (hi) | R<br>W      | XGR1[15:8]                |         |         |            |              |         |         |       |

| 0x03A3  | XGR1 (lo) | R<br>W      | XGR1[7:0]                 |         |         |            |              |         |         |       |

| 0x03A4  | XGR2 (hi) | R<br>W      | XGR2[15:8]                |         |         |            |              |         |         |       |

| 0x03A5  | XGR2 (lo) | R<br>W      | XGR2[7:0]                 |         |         |            |              |         |         |       |

| 0x03A6  | XGR3 (hi) | R<br>W      | XGR3[15:8]                |         |         |            |              |         |         |       |

| 0x03A7  | XGR3 (lo) | R<br>W      | XGR3[7:0]                 |         |         |            |              |         |         |       |

| 0x03A8  | XGR4 (hi) | R<br>W      | XGR4[15:8]                |         |         |            |              |         |         |       |

| 0x03A9  | XGR4 (lo) | R<br>W      | XGR4[7:0]                 |         |         |            |              |         |         |       |

| 0x03AA  | XGR5 (hi) | R<br>W      | XGR5[15:8]                |         |         |            |              |         |         |       |

| 0x03AB  | XGR5(lo)  | R<br>W      | XGR5[7:0]                 |         |         |            |              |         |         |       |

| 0x03AC  | XGR6 (hi) | R<br>W      | XGR6[15:8]                |         |         |            |              |         |         |       |