Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 119                                                                     |

| Program Memory Size        | 384KB (384K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 24K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 24x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xeq384f1mag |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.3.29 Port S Data Register (PTS)

Access: User read/write<sup>(1)</sup> Address 0x0248 7 6 5 4 3 2 1 0 R PTS7 PTST6 PTS5 PTS4 PTS3 PTS2 PTS1 PTS0 W Altern. SS0 SCK0 MOSI0 MISO0 TXD1 RXD1 TXD0 RXD0 Function 0 0 0 0 0 0 0 0 Reset

Figure 2-27. Port S Data Register (PTS)

1. Read: Anytime. Write: Anytime.

#### Table 2-26. PTS Register Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PTS | Port S general purpose input/output data—Data Register<br>Port S pin 7 is associated with the SS signal of the SPI0 module.<br>When not used with the alternative function, this pin can be used as general purpose I/O.<br>If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the<br>buffered pin input state is read.   |

| 6<br>PTS | Port S general purpose input/output data—Data Register<br>Port S pin 6 is associated with the SCK signal of the SPI0 module.<br>When not used with the alternative function, this pin can be used as general purpose I/O.<br>If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the<br>buffered pin input state is read.  |

| 5<br>PTS | Port S general purpose input/output data—Data Register<br>Port S pin 5 is associated with the MOSI signal of the SPI0 module.<br>When not used with the alternative function, this pin can be used as general purpose I/O.<br>If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the<br>buffered pin input state is read. |

| 4<br>PTS | Port S general purpose input/output data—Data RegisterPort S pin 4 is associated with the MISO signal of the SPI0 module.When not used with the alternative function, this pin can be used as general purpose I/O.If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the buffered pin input state is read.                |

| 3<br>PTS | Port S general purpose input/output data—Data Register<br>Port S pin 3 is associated with the TXD signal of the SCI1 module.<br>When not used with the alternative function, this pin can be used as general purpose I/O.<br>If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the<br>buffered pin input state is read.  |

| 2<br>PTS | Port S general purpose input/output data—Data Register<br>Port S bits 2 is associated with the RXD signal of the SCI1 module.<br>When not used with the alternative function, this pin can be used as general purpose I/O.<br>If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the<br>buffered pin input state is read. |

#### 3.3 **Memory Map and Registers**

#### 3.3.1 **Module Memory Map**

A summary of the registers associated with the MMC block is shown in Figure 3-2. Detailed descriptions of the registers and bits are given in the subsections that follow.

| Address          | Register<br>Name |        | Bit 7       | 6           | 5           | 4           | 3           | 2           | 1           | Bit 0       |

|------------------|------------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0x000A           | MMCCTL0          | R<br>W | CS3E1       | CS3E0       | CS2E1       | CS2E0       | CS1E1       | CS1E0       | CS0E1       | CS0E0       |

| 0x000B           | MODE             | R<br>W | MODC        | MODB        | MODA        | 0           | 0           | 0           | 0           | 0           |

| 0x0010           | GPAGE            | R<br>W | 0           | GP6         | GP5         | GP4         | GP3         | GP2         | GP1         | GP0         |

| 0x0011           | DIRECT           | R<br>W | DP15        | DP14        | DP13        | DP12        | DP11        | DP10        | DP9         | DP8         |

| 0x0012           | Reserved         | R<br>W | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| 0x0013           | MMCCTL1          | R<br>W | TGMRAMON    | 0           | EEEIFRON    | PGMIFRON    | RAMHM       | EROMON      | ROMHM       | ROMON       |

| 0x0014           | Reserved         | R<br>W | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| 0x0015           |                  |        |             |             |             |             |             |             |             |             |

|                  | PPAGE            | R<br>W | PIX7        | PIX6        | PIX5        | PIX4        | PIX3        | PIX2        | PIX1        | PIX0        |

| 0x0016           | PPAGE<br>RPAGE   |        | PIX7<br>RP7 | PIX6<br>RP6 | PIX5<br>RP5 | PIX4<br>RP4 | PIX3<br>RP3 | PIX2<br>RP2 | PIX1<br>RP1 | PIX0<br>RP0 |

| 0x0016<br>0x0017 |                  | W<br>R |             |             |             |             |             |             |             |             |

Figure 3-2. MMC Register Summary

| ASIZ[4:0]           | Available External Address Lines |

|---------------------|----------------------------------|

| 00011               | ADDR[2:1], UDS                   |

| :                   | :                                |

| 10110               | ADDR[21:1], UDS                  |

| 10111<br>:<br>11111 | ADDR[22:1], UDS                  |

Table 5-5. External Address Bus Size

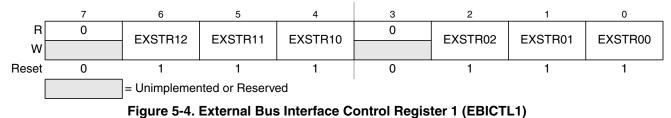

## 5.3.2.2 External Bus Interface Control Register 1 (EBICTL1)

Module Base +0x000F (PRR)

Read: Anytime. In emulation modes, read operations will return the data from the external bus, in all other modes the data is read from this register.

Write: Anytime. In emulation modes, write operations will also be directed to the external bus.

This register allows programming of two independent values determining the amount of additional stretch cycles for external accesses (wait states).

With two bits in S12X\_MMC register MMCCTL0 for every individual  $\overline{CSx}$  line one of the two counter options or the  $\overline{EWAIT}$  input is selected as stretch source. The chip select outputs can also be disabled to free up the pins for alternative functions (Table 5-6). Refer also to S12X\_MMC section for register bit descriptions.

| CSxE1 | CSxE0 | Function                  |

|-------|-------|---------------------------|

| 0     | 0     | CSx disabled              |

| 0     | 1     | CSx stretched with EXSTR0 |

| 1     | 0     | CSx stretched with EXSTR1 |

| 1     | 1     | CSx stretched with EWAIT  |

| Table 5-6. Chip | select function |

|-----------------|-----------------|

|-----------------|-----------------|

If  $\overline{\text{EWAIT}}$  input usage is selected in MMCCTL0 the minimum number of stretch cycles is 2 for accesses to the related address range.

If configured respectively, stretch cycles are added as programmed or dependent on  $\overline{\text{EWAIT}}$  in normal expanded mode and emulation expanded mode; function not available in all other operating modes.

GO\_UNTIL command can not be aborted. Only the corresponding ACK pulse can be aborted by the SYNC command.

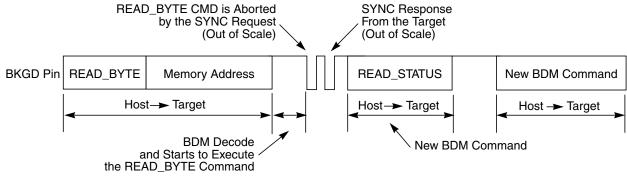

Although it is not recommended, the host could abort a pending BDM command by issuing a low pulse in the BKGD pin shorter than 128 serial clock cycles, which will not be interpreted as the SYNC command. The ACK is actually aborted when a negative edge is perceived by the target in the BKGD pin. The short abort pulse should have at least 4 clock cycles keeping the BKGD pin low, in order to allow the negative edge to be detected by the target. In this case, the target will not execute the SYNC protocol but the pending command will be aborted along with the ACK pulse. The potential problem with this abort procedure is when there is a conflict between the ACK pulse and the short abort pulse. In this case, the target may not perceive the abort pulse. The worst case is when the pending command is a read command (i.e., READ\_BYTE). If the abort pulse is not perceived by the target the host to retrieve the accessed memory byte. In this case, host and target will run out of synchronism. However, if the command to be aborted is not a read command the short abort pulse could be used. After a command is aborted the target assumes the next negative edge, after the abort pulse, is the first bit of a new BDM command.

### NOTE

The details about the short abort pulse are being provided only as a reference for the reader to better understand the BDM internal behavior. It is not recommended that this procedure be used in a real application.

Since the host knows the target serial clock frequency, the SYNC command (used to abort a command) does not need to consider the lower possible target frequency. In this case, the host could issue a SYNC very close to the 128 serial clock cycles length. Providing a small overhead on the pulse length in order to assure the SYNC pulse will not be misinterpreted by the target. See Section 7.4.9, "SYNC — Request Timed Reference Pulse".

Figure 7-13 shows a SYNC command being issued after a READ\_BYTE, which aborts the READ\_BYTE command. Note that, after the command is aborted a new command could be issued by the host computer.

Figure 7-13. ACK Abort Procedure at the Command Level

### NOTE

Figure 7-13 does not represent the signals in a true timing scale

Figure 7-14 shows a conflict between the ACK pulse and the SYNC request pulse. This conflict could occur if a POD device is connected to the target BKGD pin and the target is already in debug active mode.

### Table 13-13. ATDCTL4 Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–5<br>SMP[2:0] | <b>Sample Time Select</b> — These three bits select the length of the sample time in units of ATD conversion clock cycles. Note that the ATD conversion clock period is itself a function of the prescaler value (bits PRS4-0). Table 13-14 lists the available sample time lengths. |

| 4–0<br>PRS[4:0] | ATD Clock Prescaler — These 5 bits are the binary prescaler value PRS. The ATD conversion clock frequency is calculated as follows:                                                                                                                                                  |

|                 | $f_{ATDCLK} = \frac{f_{BUS}}{2 \times (PRS + 1)}$                                                                                                                                                                                                                                    |

|                 | Refer to Device Specification for allowed frequency range of f <sub>ATDCLK</sub> .                                                                                                                                                                                                   |

| SMP2 | SMP1 | SMP0 | Sample Time<br>in Number of<br>ATD Clock Cycles |

|------|------|------|-------------------------------------------------|

| 0    | 0    | 0    | 4                                               |

| 0    | 0    | 1    | 6                                               |

| 0    | 1    | 0    | 8                                               |

| 0    | 1    | 1    | 10                                              |

| 1    | 0    | 0    | 12                                              |

| 1    | 0    | 1    | 16                                              |

| 1    | 1    | 0    | 20                                              |

| 1    | 1    | 1    | 24                                              |

### Table 13-14. Sample Time Select

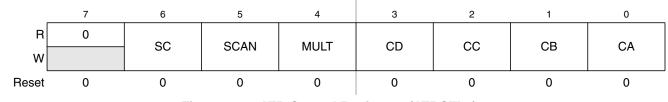

## 13.3.2.6 ATD Control Register 5 (ATDCTL5)

Writes to this register will abort current conversion sequence and start a new conversion sequence. If external trigger is enabled (ETRIGE=1) an initial write to ATDCTL5 is required to allow starting of a conversion sequence which will then occur on each trigger event. Start of conversion means the beginning of the sampling phase.

Module Base + 0x0005

Figure 13-8. ATD Control Register 5 (ATDCTL5)

Read: Anytime

Write: Anytime

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>PBEN  | <ul> <li>Pulse Accumulator B System Enable — PBEN is independent from TEN. With timer disabled, the pulse accumulator can still function unless pulse accumulator is disabled.</li> <li>0 16-bit pulse accumulator system disabled. 8-bit PAC1 and PAC0 can be enabled when their related enable bits in ICPAR are set.</li> <li>1 Pulse accumulator B system enabled. The two 8-bit pulse accumulators PAC1 and PAC0 are cascaded to form the PACB 16-bit pulse accumulator B. When PACB is enabled, the PACN1 and PACN0 registers contents are respectively the high and low byte of the PACB.</li> <li>PA1EN and PA0EN control bits in ICPAR have no effect. The PACB shares the input pin with ICO.</li> </ul> |

| 1<br>PBOVI | Pulse Accumulator B Overflow Interrupt Enable         0 Interrupt inhibited         1 Interrupt requested if PBOVF is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

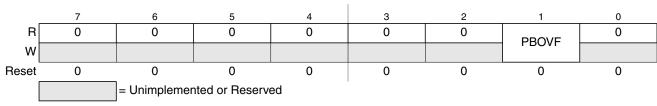

## 14.3.2.29 Pulse Accumulator B Flag Register (PBFLG)

### Figure 14-52. Pulse Accumulator B Flag Register (PBFLG)

### Read: Anytime

Module Base + 0x0031

Write used in the flag clearing mechanism. Writing a one to the flag clears the flag. Writing a zero will not affect the current status of the bit.

### NOTE

When TFFCA = 1, the flag cannot be cleared via the normal flag clearing mechanism (writing a one to the flag). Reference Section 14.3.2.6, "Timer System Control Register 1 (TSCR1)".

All bits reset to zero.

PBFLG indicates when interrupt conditions have occurred. The flag can be cleared via the normal flag clearing mechanism (writing a one to the flag) or via the fast flag clearing mechanism (Reference TFFCA bit in Section 14.3.2.6, "Timer System Control Register 1 (TSCR1)").

### Table 14-38. PBFLG Field Descriptions

| Field      | Description                                                                                                                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>PBOVF | <b>Pulse Accumulator B Overflow Flag</b> — This bit is set when the 16-bit pulse accumulator B overflows from 0xFFFF to 0x0000, or when 8-bit pulse accumulator 1 (PAC1) overflows from 0x00FF to 0x0000. |

|            | When PACMX = 1, PBOVF bit can also be set if 8-bit pulse accumulator 1 (PAC1) reaches 0x00FF and an active edge follows on IC1.                                                                           |

| Register<br>Name |   | Bit 7  | 6                                                           | 5             | 4            | 3             | 2           | 1      | Bit 0  |  |

|------------------|---|--------|-------------------------------------------------------------|---------------|--------------|---------------|-------------|--------|--------|--|

| 0x000F           | R | TXERR7 | TXERR6                                                      | TXERR5        | TXERR4       | TXERR3        | TXERR2      | TXERR1 | TXERR0 |  |

| CANTXERR         | W |        |                                                             |               |              |               |             |        |        |  |

| 0x0010-0x0013    | R | AC7    | AC6                                                         | AC5           | AC4          | AC3           | AC2         | AC1    | AC0    |  |

| CANIDAR0-3       | W | 707    | 700                                                         | 703           | 704          | 700           | 702         | ACT    | 700    |  |

| 0x0014-0x0017    | R | AM7    | AM6                                                         | AM5           | AM4          | АМЗ           | AM2         | AM1    | AMO    |  |

| CANIDMRx         | W |        | Alvio                                                       | AIVIS         | Alvi4        | Alvio         | Alviz       | AIVIT  | AIVIO  |  |

| 0x0018-0x001B    | R | AC7    | AC6                                                         | AC5           | AC4          | AC3           | AC2         | AC1    | AC0    |  |

| CANIDAR4-7       | W | AU7    | ACO                                                         | ACS           | A04          | A03           | A02         | ACT    | ACU    |  |

| 0x001C-0x001F    | R | AM7    | AM6                                                         | AM5           | AM4          | АМЗ           | AM2         | AM1    | AMO    |  |

| CANIDMR4-7       | w | Alvi7  | Alvio                                                       | CIVIA         | Alvi4        | Alvið         | Alviz       | AIVIT  | Alviu  |  |

| 0x0020-0x002F    | R |        | 0                                                           |               | "D           |               | Manage Ob   |        |        |  |

| CANRXFG          | w |        | See S                                                       | ection 16.3.3 | s, "Programm | er's Model of | Message Sto | brage  |        |  |

| 0x0030–0x003F R  |   |        |                                                             |               |              |               |             |        |        |  |

| CANTXFG          | w |        | See Section 16.3.3, "Programmer's Model of Message Storage" |               |              |               |             |        |        |  |

|                  |   |        | = Unimplemented or Reserved                                 |               |              |               |             |        |        |  |

Figure 16-3. MSCAN Register Summary (continued)

## 16.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the MSCAN module. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. All bits of all registers in this module are completely synchronous to internal clocks during a register read.

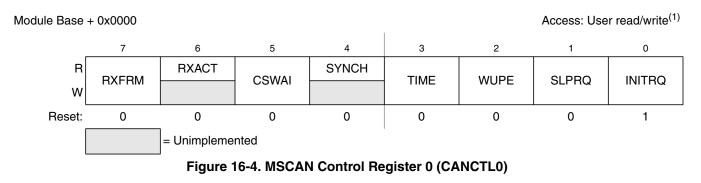

## 16.3.2.1 MSCAN Control Register 0 (CANCTL0)

The CANCTL0 register provides various control bits of the MSCAN module as described below.

Chapter 16 Freescale's Scalable Controller Area Network (S12MSCANV3)

If the WUPE bit in CANCTL0 is not asserted, the MSCAN will mask any activity it detects on CAN. RXCAN is therefore held internally in a recessive state. This locks the MSCAN in sleep mode. WUPE must be set before entering sleep mode to take effect.

The MSCAN is able to leave sleep mode (wake up) only when:

- CAN bus activity occurs and WUPE = 1 or

- the CPU clears the SLPRQ bit

### NOTE

The CPU cannot clear the SLPRQ bit before sleep mode (SLPRQ = 1 and SLPAK = 1) is active.

After wake-up, the MSCAN waits for 11 consecutive recessive bits to synchronize to the CAN bus. As a consequence, if the MSCAN is woken-up by a CAN frame, this frame is not received.

The receive message buffers (RxFG and RxBG) contain messages if they were received before sleep mode was entered. All pending actions will be executed upon wake-up; copying of RxBG into RxFG, message aborts and message transmissions. If the MSCAN remains in bus-off state after sleep mode was exited, it continues counting the 128 occurrences of 11 consecutive recessive bits.

## 16.4.5.6 MSCAN Power Down Mode

The MSCAN is in power down mode (Table 16-38) when

• CPU is in stop mode

or

• CPU is in wait mode and the CSWAI bit is set

When entering the power down mode, the MSCAN immediately stops all ongoing transmissions and receptions, potentially causing CAN protocol violations. To protect the CAN bus system from fatal consequences of violations to the above rule, the MSCAN immediately drives TXCAN into a recessive state.

### NOTE

The user is responsible for ensuring that the MSCAN is not active when power down mode is entered. The recommended procedure is to bring the MSCAN into Sleep mode before the STOP or WAI instruction (if CSWAI is set) is executed. Otherwise, the abort of an ongoing message can cause an error condition and impact other CAN bus devices.

In power down mode, all clocks are stopped and no registers can be accessed. If the MSCAN was not in sleep mode before power down mode became active, the module performs an internal recovery cycle after powering up. This causes some fixed delay before the module enters normal mode again.

## 20.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Writes to a reserved register locations do not have any effect and reads of these locations return a zero. Details of register bit and field function follow the register diagrams, in bit order.

| Register<br>Name               |        | Bit 7   | 6       | 5    | 4     | 3     | 2      | 1       | Bit 0 |

|--------------------------------|--------|---------|---------|------|-------|-------|--------|---------|-------|

| 0x0000<br>SCIBDH <sup>1</sup>  | R<br>W | IREN    | TNP1    | TNP0 | SBR12 | SBR11 | SBR10  | SBR9    | SBR8  |

| 0x0001<br>SCIBDL <sup>1</sup>  | R<br>W | SBR7    | SBR6    | SBR5 | SBR4  | SBR3  | SBR2   | SBR1    | SBR0  |

| 0x0002<br>SCICR1 <sup>1</sup>  | R<br>W | LOOPS   | SCISWAI | RSRC | М     | WAKE  | ILT    | PE      | PT    |

| 0x0000<br>SCIASR1 <sup>2</sup> | R      | RXEDGIF | 0       | 0    | 0     | 0     | BERRV  | BERRIF  | BKDIF |

| SUASHI                         | W      | _       |         |      |       |       |        | DETIT   |       |

| 0x0001                         | R      | RXEDGIE | 0       | 0    | 0     | 0     | 0      | BERRIE  | BKDIE |

| SCIACR1 <sup>2</sup>           | W      |         |         |      |       |       |        | DETITIE | BRBIE |

| 0x0002                         | R      | 0       | 0       | 0    | 0     | 0     | BERRM1 | BERRM0  | BKDFE |

| SCIACR2 <sup>2</sup>           | w      |         |         |      |       |       |        |         | DIGIL |

| 0x0003<br>SCICR2               | R<br>W | TIE     | TCIE    | RIE  | ILIE  | TE    | RE     | RWU     | SBK   |

| 0x0004                         | R      | TDRE    | TC      | RDRF | IDLE  | OR    | NF     | FE      | PF    |

| SCISR1                         | w      |         |         |      |       |       |        |         |       |

| 0x0005                         | R      |         | 0       | 0    | турој | RXPOL | BRK13  | TXDIR   | RAF   |

| SCISR2                         | w      | AMAP    |         |      | TXPOL |       |        |         |       |

| 0x0006                         | R      | R8      | TO      | 0    | 0     | 0     | 0      | 0       | 0     |

| SCIDRH \                       | w      |         | Т8      |      |       |       |        |         |       |

| 0x0007                         | R      | R7      | R6      | R5   | R4    | R3    | R2     | R1      | R0    |

| SCIDRL                         | w      | T7      | T6      | T5   | T4    | Т3    | T2     | T1      | ТО    |

1. These registers are accessible if the AMAP bit in the SCISR2 register is set to zero.

2, These registers are accessible if the AMAP bit in the SCISR2 register is set to one.

= Unimplemented or Reserved

Figure 20-2. SCI Register Summary

The SCI also sets a flag, the transmit data register empty flag (TDRE), every time it transfers data from the buffer (SCIDRH/L) to the transmitter shift register. The transmit driver routine may respond to this flag by writing another byte to the Transmitter buffer (SCIDRH/SCIDRL), while the shift register is still shifting out the first byte.

To initiate an SCI transmission:

- 1. Configure the SCI:

- a) Select a baud rate. Write this value to the SCI baud registers (SCIBDH/L) to begin the baud rate generator. Remember that the baud rate generator is disabled when the baud rate is zero. Writing to the SCIBDH has no effect without also writing to SCIBDL.

- b) Write to SCICR1 to configure word length, parity, and other configuration bits (LOOPS,RSRC,M,WAKE,ILT,PE,PT).

- c) Enable the transmitter, interrupts, receive, and wake up as required, by writing to the SCICR2 register bits (TIE,TCIE,RIE,ILIE,TE,RE,RWU,SBK). A preamble or idle character will now be shifted out of the transmitter shift register.

- 2. Transmit Procedure for each byte:

- a) Poll the TDRE flag by reading the SCISR1 or responding to the TDRE interrupt. Keep in mind that the TDRE bit resets to one.

- b) If the TDRE flag is set, write the data to be transmitted to SCIDRH/L, where the ninth bit is written to the T8 bit in SCIDRH if the SCI is in 9-bit data format. A new transmission will not result until the TDRE flag has been cleared.

- 3. Repeat step 2 for each subsequent transmission.

### NOTE

The TDRE flag is set when the shift register is loaded with the next data to be transmitted from SCIDRH/L, which happens, generally speaking, a little over half-way through the stop bit of the previous frame. Specifically, this transfer occurs 9/16ths of a bit time AFTER the start of the stop bit of the previous frame.

Writing the TE bit from 0 to a 1 automatically loads the transmit shift register with a preamble of 10 logic 1s (if M = 0) or 11 logic 1s (if M = 1). After the preamble shifts out, control logic transfers the data from the SCI data register into the transmit shift register. A logic 0 start bit automatically goes into the least significant bit position of the transmit shift register. A logic 1 stop bit goes into the most significant bit position.

Hardware supports odd or even parity. When parity is enabled, the most significant bit (MSB) of the data character is the parity bit.

The transmit data register empty flag, TDRE, in SCI status register 1 (SCISR1) becomes set when the SCI data register transfers a byte to the transmit shift register. The TDRE flag indicates that the SCI data register can accept new data from the internal data bus. If the transmit interrupt enable bit, TIE, in SCI control register 2 (SCICR2) is also set, the TDRE flag generates a transmitter interrupt request.

The prescaler divides the bus clock by a prescalar value. Prescaler select bits PR[2:0] of in timer system control register 2 (TSCR2) are set to define a prescalar value that generates a divide by 1, 2, 4, 8, 16, 32, 64 and 128 when the PRNT bit in TSCR1 is disabled.

By enabling the PRNT bit of the TSCR1 register, the performance of the timer can be enhanced. In this case, it is possible to set additional prescaler settings for the main timer counter in the present timer by using PTPSR[7:0] bits of PTPSR register.

# 22.4.2 Input Capture

Clearing the I/O (input/output) select bit, IOSx, configures channel x as an input capture channel. The input capture function captures the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the timer transfers the value in the timer counter into the timer channel registers, TCx.

The minimum pulse width for the input capture input is greater than two bus clocks.

An input capture on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module or Pulse Accumulator must stay enabled (TEN bit of TSCR1 or PAEN bit of PACTL regsiter must be set to one) while clearing CxF (writing one to CxF).

# 22.4.3 Output Compare

Setting the I/O select bit, IOSx, configures channel x as an output compare channel. The output compare function can generate a periodic pulse with a programmable polarity, duration, and frequency. When the timer counter reaches the value in the channel registers of an output compare channel, the timer can set, clear, or toggle the channel pin if the corresponding OCPDx bit is set to zero. An output compare on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module or Pulse Accumulator must stay enabled (TEN bit of TSCR1 or PAEN bit of PACTL register must be set to one) while clearing CxF (writing one to CxF).

The output mode and level bits, OMx and OLx, select set, clear, toggle on output compare. Clearing both OMx and OLx results in no output compare action on the output compare channel pin.

Setting a force output compare bit, FOCx, causes an output compare on channel x. A forced output compare does not set the channel flag.

A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides output compares on all other output compare channels. The output compare 7 mask register masks the bits in the output compare 7 data register. The timer counter reset enable bit, TCRE, enables channel 7 output compares to reset the timer counter. A channel 7 output compare can reset the timer counter even if the IOC7 pin is being used as the pulse accumulator input.

Writing to the timer port bit of an output compare pin does not affect the pin state. The value written is stored in an internal latch. When the pin becomes available for general-purpose output, the last value written to the bit appears at the pin.

When TCRE is set and TC7 is not equal to 0, then TCNT will cycle from 0 to TC7. When TCNT reaches TC7 value, it lasts only one bus cycle then resets to 0.

# Chapter 25 256 KByte Flash Module (S12XFTM256K2V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                                                                                                                 |

|--------------------|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.08             | 14 Nov 2007      | 25.5.2/25-951<br>25.4.2/25-927 | <ul> <li>Changed terminology from 'word program' to "Program P-Flash' in the BDM unsecuring description, Section 25.5.2</li> <li>Added requirement that user not write any Flash module register during</li> </ul>                     |

|                    |                  | 20.4.2/20-927                  | execution of commands 'Erase All Blocks', Section 25.4.2.8, and 'Unsecure Flash', Section 25.4.2.11                                                                                                                                    |

|                    |                  | 25.4.2.8/25-933                | - Added statement that security is released upon successful completion of command 'Erase All Blocks', Section 25.4.2.8                                                                                                                 |

| V01.09             | 19 Dec 2007      | 25.4.2.5/25-930                | - Corrected Error Handling table for Load Data Field command                                                                                                                                                                           |

|                    |                  | 25.4.2/25-927                  | - Corrected Error Handling table for Full Partition D-Flash, Partition D-Flash, and EEPROM Emulation Query commands                                                                                                                    |

|                    |                  | 25.3.1/25-896                  | - Corrected P-Flash IFR Accessibility table                                                                                                                                                                                            |

| V01.10             | 25 Sep 2009      | 25.1/25-891                    | - Clarify single bit fault correction for P-Flash phrase                                                                                                                                                                               |

|                    |                  | 25.3.2.1/25-903                | - Expand FDIV vs OSCCLK Frequency table                                                                                                                                                                                                |

|                    |                  | 25.4.2.4/25-930                | - Add statement concerning code runaway when executing Read Once command from Flash block containing associated fields                                                                                                                 |

|                    |                  | 25.4.2.7/25-932                | - Add statement concerning code runaway when executing Program Once command from Flash block containing associated fields                                                                                                              |

|                    |                  | 25.4.2.12/25-<br>936           | <ul> <li>Add statement concerning code runaway when executing Verify Backdoor</li> <li>Access Key command from Flash block containing associated fields</li> <li>Relate Key 0 to associated Backdoor Comparison Key address</li> </ul> |

|                    |                  | 25.4.2.12/25-                  | - Change "power down reset" to "reset"                                                                                                                                                                                                 |

|                    |                  | 936                            | - Add ACCERR condition for Disable EEPROM Emulation command                                                                                                                                                                            |

|                    |                  | 25.4.2.12/25-                  | The following changes were made to clarify module behavior related to Flash                                                                                                                                                            |

|                    |                  | 936                            | register access during reset sequence and while Flash commands are active:                                                                                                                                                             |

|                    |                  | 25.4.2.20/25-                  | - Add caution concerning register writes while command is active                                                                                                                                                                       |

|                    |                  | 945                            | - Writes to FCLKDIV are allowed during reset sequence while CCIF is clear                                                                                                                                                              |

|                    |                  |                                | - Add caution concerning register writes while command is active<br>- Writes to FCCOBIX, FCCOBHI, FCCOBLO registers are ignored during                                                                                                 |

|                    |                  | 25.3.2/25-901                  | reset sequence                                                                                                                                                                                                                         |

|                    |                  | 25.3.2.1/25-903                |                                                                                                                                                                                                                                        |

|                    |                  | 25.4.1.2/25-922                |                                                                                                                                                                                                                                        |

|                    |                  | 25.6/25-951                    |                                                                                                                                                                                                                                        |

|                    |                  |                                |                                                                                                                                                                                                                                        |

### Table 25-1. Revision History

# 25.1 Introduction

The FTM256K2 module implements the following:

• 256 Kbytes of P-Flash (Program Flash) memory, consisting of 2 physical Flash blocks, intended primarily for nonvolatile code storage

**D-Flash Sector** — The D-Flash sector is the smallest portion of the D-Flash memory that can be erased. The D-Flash sector consists of four 64 byte rows for a total of 256 bytes.

**EEE (Emulated EEPROM)** — A method to emulate the small sector size features and endurance characteristics associated with an EEPROM.

**EEE IFR** — Nonvolatile information register located in the D-Flash block that contains data required to partition the D-Flash memory and buffer RAM for EEE. The EEE IFR is visible in the global memory map by setting the EEEIFRON bit in the MMCCTL1 register.

**NVM Command Mode** — An NVM mode using the CPU to setup the FCCOB register to pass parameters required for Flash command execution.

**Phrase** — An aligned group of four 16-bit words within the P-Flash memory. Each phrase includes eight ECC bits for single bit fault correction and double bit fault detection within the phrase.

P-Flash Memory — The P-Flash memory constitutes the main nonvolatile memory store for applications.

**P-Flash Sector** — The P-Flash sector is the smallest portion of the P-Flash memory that can be erased. Each P-Flash sector contains 1024 bytes.

**Program IFR** — Nonvolatile information register located in the P-Flash block that contains the Device ID, Version ID, and the Program Once field. The Program IFR is visible in the global memory map by setting the PGMIFRON bit in the MMCCTL1 register.

## 25.1.2 Features

### 25.1.2.1 P-Flash Features

- 256 Kbytes of P-Flash memory composed of two 128 Kbyte Flash blocks. The 128 Kbyte Flash blocks are each divided into 128 sectors of 1024 bytes.

- Single bit fault correction and double bit fault detection within a 64-bit phrase during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and phrase program operation

- Ability to program up to one phrase in each P-Flash block simultaneously

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

## 25.1.2.2 D-Flash Features

- Up to 32 Kbytes of D-Flash memory with 256 byte sectors for user access

- Dedicated commands to control access to the D-Flash memory over EEE operation

- Single bit fault correction and double bit fault detection within a word during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and word program operation

- Ability to program up to four words in a burst sequence

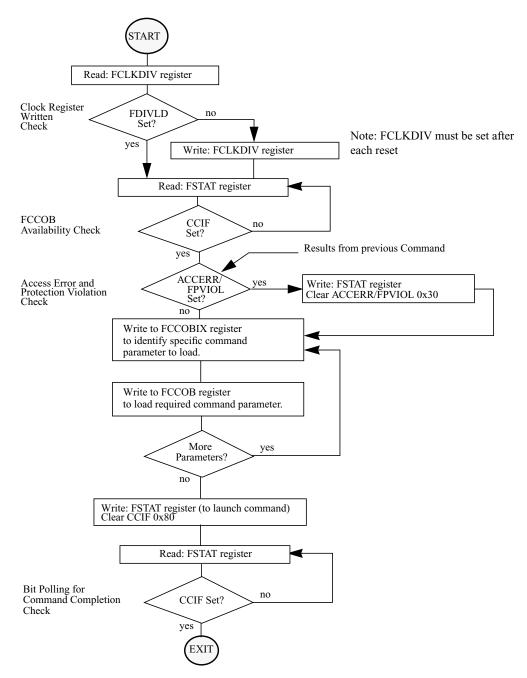

Figure 25-26. Generic Flash Command Write Sequence Flowchart

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                             |

|          |           | Set if a Load Data Field command sequence is currently active           |

|          |           | Set if command not available in current mode (see Table 25-30)          |

| FSTAT    |           | Set if an invalid DFPART or ERPART selection is supplied                |

|          | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

| FERSTAT  | EPVIOLIF  | None                                                                    |

Table 25-64. Full Partition D-Flash Command Error Handling

## 25.4.2.16 Erase Verify D-Flash Section Command

The Erase Verify D-Flash Section command will verify that a section of code in the D-Flash user partition is erased. The Erase Verify D-Flash Section command defines the starting point of the data to be verified and the number of words.

Table 25-65. Erase Verify D-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB P                    | arameters                                            |

|-------------|----------------------------|------------------------------------------------------|

| 000         | 0x10                       | Global address [22:16] to identify the D-Flash block |

| 001         | Global address [15:0] of t | he first word to be verified                         |

| 010         | Number of wore             | ds to be verified                                    |

Upon clearing CCIF to launch the Erase Verify D-Flash Section command, the Memory Controller will verify the selected section of D-Flash memory is erased. The CCIF flag will set after the Erase Verify D-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                             |

|          |           | Set if a Load Data Field command sequence is currently active           |

|          |           | Set if command not available in current mode (see Table 26-30)          |

| FSTAT    |           | Set if an invalid DFPART or ERPART selection is supplied                |

|          | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

| FERSTAT  | EPVIOLIF  | None                                                                    |

### Table 26-64. Full Partition D-Flash Command Error Handling

## 26.4.2.16 Erase Verify D-Flash Section Command

The Erase Verify D-Flash Section command will verify that a section of code in the D-Flash user partition is erased. The Erase Verify D-Flash Section command defines the starting point of the data to be verified and the number of words.

Table 26-65. Erase Verify D-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB P                    | arameters                                            |

|-------------|----------------------------|------------------------------------------------------|

| 000         | 0x10                       | Global address [22:16] to identify the D-Flash block |

| 001         | Global address [15:0] of t | he first word to be verified                         |

| 010         | Number of wore             | ds to be verified                                    |

Upon clearing CCIF to launch the Erase Verify D-Flash Section command, the Memory Controller will verify the selected section of D-Flash memory is erased. The CCIF flag will set after the Erase Verify D-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                                                                  |  |  |

|----------|-----------|------------------------------------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                                                       |  |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                                                       |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                                                    |  |  |

|          |           | Set if command not available in current mode (see Table 26-30)                                                   |  |  |

|          | ACCERR    | Set if an invalid global address [22:0] is supplied                                                              |  |  |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)                                           |  |  |

| FSTAT    |           | Set if the global address [22:0] points to an area in the D-Flash EEE partition                                  |  |  |

|          |           | Set if the requested group of words breaches the end of the D-Flash block or goes into the D-Flash EEE partition |  |  |

|          | FPVIOL    | None                                                                                                             |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                              |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                              |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                                             |  |  |

### Table 26-68. Program D-Flash Command Error Handling

## 26.4.2.18 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash user partition.

Table 26-69. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB                                                                                                         | Parameters                                          |

|-------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 000         | 0x12                                                                                                          | Global address [22:16] to identify<br>D-Flash block |

| 001         | Global address [15:0] anywhere within the sector to be erase<br>See Section 26.1.2.2 for D-Flash sector size. |                                                     |

Upon clearing CCIF to launch the Erase D-Flash Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase D-Flash Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if a Load Data Field command sequence is currently active                       |

|          |           | Set if command not available in current mode (see Table 27-30)                      |

| FSTAT    |           | Set if an invalid global address [22:16] is supplied                                |

|          | FPVIOL    | Set if an area of the selected P-Flash block is protected                           |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

| FERSTAT  | EPVIOLIF  | None                                                                                |

#### Table 27-50. Erase P-Flash Block Command Error Handling

## 27.4.2.10 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

| CCOBIX[2:0] | FCCOB | Parameters                                                            |

|-------------|-------|-----------------------------------------------------------------------|

| 000         | 0x0A  | Global address [22:16] to identify<br>P-Flash block to be erased      |

| 001         |       | ere within the sector to be erased.<br>1 for the P-Flash sector size. |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                       |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 27-30)                      |  |  |  |

|          |           | Set if an invalid global address [22:16] is supplied                                |  |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |  |  |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                |  |  |  |

Table 27-52. Erase P-Flash Sector Command Error Handling

| Conditions are shown in Table A-4. unless otherwise noted. $V_{REF} = V_{RH} - V_{RL} = 5.12V$ . $f_{ATDCLK} = 8.3MHz$<br>The values are tested to be valid with no PortAD output drivers switching simultaneous with conversions. |   |                                        |        |        |      |      |     |        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------|--------|--------|------|------|-----|--------|--|

| Num                                                                                                                                                                                                                                | С | Rating <sup>(1)</sup> , <sup>(2)</sup> |        | Symbol | Min  | Тур  | Max | Unit   |  |

| 1                                                                                                                                                                                                                                  | Ρ | Resolution                             | 12-Bit | LSB    | _    | 1.25 | _   | mV     |  |

| 2                                                                                                                                                                                                                                  | Ρ | Differential Nonlinearity              | 12-Bit | DNL    | -4   | ±2   | 4   | counts |  |

| 3                                                                                                                                                                                                                                  | Ρ | Integral Nonlinearity                  | 12-Bit | INL    | -5   | ±2.5 | 5   | counts |  |

| 4                                                                                                                                                                                                                                  | Ρ | Absolute Error <sup>(3)</sup>          | 12-Bit | AE     | -7   | ±4   | 7   | counts |  |

| 5                                                                                                                                                                                                                                  | С | Resolution                             | 10-Bit | LSB    | _    | 5    | _   | mV     |  |

| 6                                                                                                                                                                                                                                  | С | Differential Nonlinearity              | 10-Bit | DNL    | -1   | ±0.5 | 1   | counts |  |

| 7                                                                                                                                                                                                                                  | С | Integral Nonlinearity                  | 10-Bit | INL    | -2   | ±1   | 2   | counts |  |

| 8                                                                                                                                                                                                                                  | С | Absolute Error <sup>3.</sup>           | 10-Bit | AE     | -3   | ±2   | 3   | counts |  |

| 9                                                                                                                                                                                                                                  | С | Resolution                             | 8-Bit  | LSB    | —    | 20   | _   | mV     |  |

| 10                                                                                                                                                                                                                                 | С | Differential Nonlinearity              | 8-Bit  | DNL    | -0.5 | ±0.3 | 0.5 | counts |  |

| 11                                                                                                                                                                                                                                 | С | Integral Nonlinearity                  | 8-Bit  | INL    | -1   | ±0.5 | 1   | counts |  |

| 12                                                                                                                                                                                                                                 | С | Absolute Error <sup>3.</sup>           | 8-Bit  | AE     | -1.5 | ±1   | 1.5 | counts |  |

#### Table A-17. ATD Conversion Performance 5V range

The 8-bit and 10-bit mode operation is structurally tested in production test. Absolute values are tested in 12-bit mode.

Better performance is possible using specially designed multi-layer PCBs or averaging techniques.

These values include the quantization error which is inherently 1/2 count for any A/D converter.

#### Table A-18. ATD Conversion Performance 3.3V range

| Conditions are shown in Table A-4. unless otherwise noted. $V_{REF} = V_{RH} - V_{RL} = 3.3V$ . $f_{ATDCLK} = 8.3MHz$<br>The values are tested to be valid with no PortAD output drivers switching simultaneous with conversions. |   |                               |        |        |      |       |     |        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------|--------|--------|------|-------|-----|--------|--|

| Num                                                                                                                                                                                                                               | С | Rating <sup>(1),(2)</sup>     |        | Symbol | Min  | Тур   | Max | Unit   |  |

| 1                                                                                                                                                                                                                                 | Р | Resolution                    | 12-Bit | LSB    | _    | 0.80  |     | mV     |  |

| 2                                                                                                                                                                                                                                 | Р | Differential Nonlinearity     | 12-Bit | DNL    | -6   | ±3    | 6   | counts |  |

| 3                                                                                                                                                                                                                                 | Р | Integral Nonlinearity         | 12-Bit | INL    | -7   | ±3    | 7   | counts |  |

| 4                                                                                                                                                                                                                                 | Р | Absolute Error <sup>(3)</sup> | 12-Bit | AE     | -8   | ±4    | 8   | counts |  |

| 5                                                                                                                                                                                                                                 | С | Resolution                    | 10-Bit | LSB    | _    | 3.22  |     | mV     |  |

| 6                                                                                                                                                                                                                                 | С | Differential Nonlinearity     | 10-Bit | DNL    | -1.5 | ±1    | 1.5 | counts |  |

| 7                                                                                                                                                                                                                                 | С | Integral Nonlinearity         | 10-Bit | INL    | -2   | ±1    | 2   | counts |  |

| 8                                                                                                                                                                                                                                 | С | Absolute Error <sup>3.</sup>  | 10-Bit | AE     | -3   | ±2    | 3   | counts |  |

| 9                                                                                                                                                                                                                                 | С | Resolution                    | 8-Bit  | LSB    | _    | 12.89 |     | mV     |  |

| 10                                                                                                                                                                                                                                | С | Differential Nonlinearity     | 8-Bit  | DNL    | -0.5 | ±0.3  | 0.5 | counts |  |

| 11                                                                                                                                                                                                                                | С | Integral Nonlinearity         | 8-Bit  | INL    | -1   | ±0.5  | 1   | counts |  |

| 12                                                                                                                                                                                                                                | С | Absolute Error <sup>3.</sup>  | 8-Bit  | AE     | -1.5 | ±1    | 1.5 | counts |  |

The 8-bit and 10-bit mode operation is structurally tested in production test. Absolute values are tested in 12-bit mode.

Better performance is possible using specially designed multi-layer PCBs or averaging techniques.

These values include the quantization error which is inherently 1/2 count for any A/D converter.

| Address | Name         |        | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|---------|--------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x0360  | PITLD6 (hi)  | R<br>W | PLD15  | PLD14  | PLD13  | PLD12  | PLD11  | PLD10  | PLD9  | PLD8  |

| 0x0361  | PITLD6 (lo)  | R<br>W | PLD7   | PLD6   | PLD5   | PLD4   | PLD3   | PLD2   | PLD1  | PLD0  |

| 0x0362  | PITCNT6 (hi) | R<br>W | PCNT15 | PCNT14 | PCNT13 | PCNT12 | PCNT11 | PCNT10 | PCNT9 | PCNT8 |

| 0x0363  | PITCNT6 (lo) | R<br>W | PCNT7  | PCNT6  | PCNT5  | PCNT4  | PCNT3  | PCNT2  | PCNT1 | PCNT0 |

| 0x0364  | PITLD7 (hi)  | R<br>W | PLD15  | PLD14  | PLD13  | PLD12  | PLD11  | PLD10  | PLD9  | PLD8  |

| 0x0365  | PITLD7 (lo)  | R<br>W | PLD7   | PLD6   | PLD5   | PLD4   | PLD3   | PLD2   | PLD1  | PLD0  |

| 0x0366  | PITCNT7 (hi) | R<br>W | PCNT15 | PCNT14 | PCNT13 | PCNT12 | PCNT11 | PCNT10 | PCNT9 | PCNT8 |

| 0x0367  | PITCNT7 (lo) | R<br>W | PCNT7  | PCNT6  | PCNT5  | PCNT4  | PCNT3  | PCNT2  | PCNT1 | PCNT0 |

### 0x00340–0x0367 – Periodic Interrupt Timer (PIT) Map (Sheet 3 of 3)