Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xeq512bmal |

|----------------------------|------------------------------------------------------------------------|

| Supplier Device Package    | 112-LQFP (20x20)                                                       |

| Package / Case             | 112-LQFP                                                               |

| Mounting Type              | Surface Mount                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Oscillator Type            | External                                                               |

| Data Converters            | A/D 16x12b                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                           |

| RAM Size                   | 32K x 8                                                                |

| EEPROM Size                | 4K x 8                                                                 |

| Program Memory Type        | FLASH                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Number of I/O              | 91                                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                      |

| Speed                      | 50MHz                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Core Processor             | HCS12X                                                                 |

| Product Status             | Active                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 16-Bit CPU12X

- Upward compatible with MC9S12 instruction set with the exception of five Fuzzy instructions (MEM, WAV, WAVR, REV, REVW) which have been removed

- Enhanced indexed addressing

- Access to large data segments independent of PPAGE

- INT (interrupt module)

- Eight levels of nested interrupts

- Flexible assignment of interrupt sources to each interrupt level.

- External non-maskable high priority interrupt (XIRQ)

- Internal non-maskable high priority Memory Protection Unit interrupt

- Up to 24 pins on ports J, H and P configurable as rising or falling edge sensitive interrupts

- EBI (external bus interface)(available in 208-Pin and 144-Pin packages only)

- Up to four chip select outputs to select 16K, 1M, 2M and up to 4MByte address spaces

- Each chip select output can be configured to complete transaction on either the time-out of one

of the two wait state generators or the deassertion of EWAIT signal

- MMC (module mapping control)

- DBG (debug module)

- Monitoring of CPU and/or XGATE busses with tag-type or force-type breakpoint requests

- 64 x 64-bit circular trace buffer captures change-of-flow or memory access information

- BDM (background debug mode)

- MPU (memory protection unit)

- 8 address regions definable per active program task

- Address range granularity as low as 8-bytes

- No write / No execute Protection Attributes

- Non-maskable interrupt on access violation

- XGATE

- Programmable, high performance I/O coprocessor module

- Transfers data to or from all peripherals and RAM without CPU intervention or CPU wait states

- Performs logical, shifts, arithmetic, and bit operations on data

- Can interrupt the HCS12X CPU signalling transfer completion

- Triggers from any hardware module as well as from the CPU possible

- Two interrupt levels to service high priority tasks

- Hardware support for stack pointer initialisation

- OSC\_LCP (oscillator)

- Low power loop control Pierce oscillator utilizing a 4MHz to 16MHz crystal

- Good noise immunity

- Full-swing Pierce option utilizing a 2MHz to 40MHz crystal

- Transconductance sized for optimum start-up margin for typical crystals

- IPLL (Internally filtered, frequency modulated phase-locked-loop clock generation)

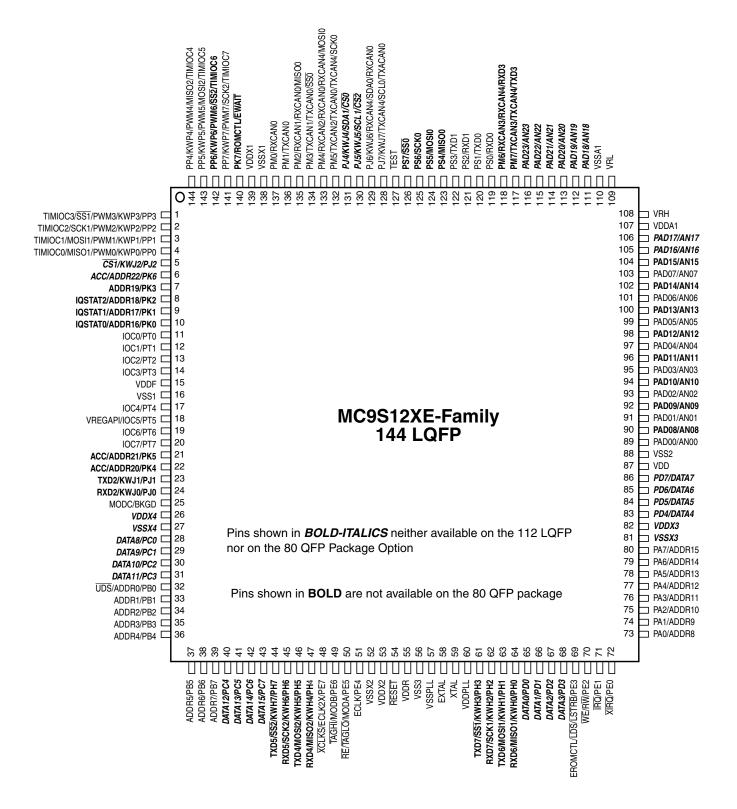

Figure 1-5. MC9S12XE-Family Pin Assignments 144-pin LQFP Package

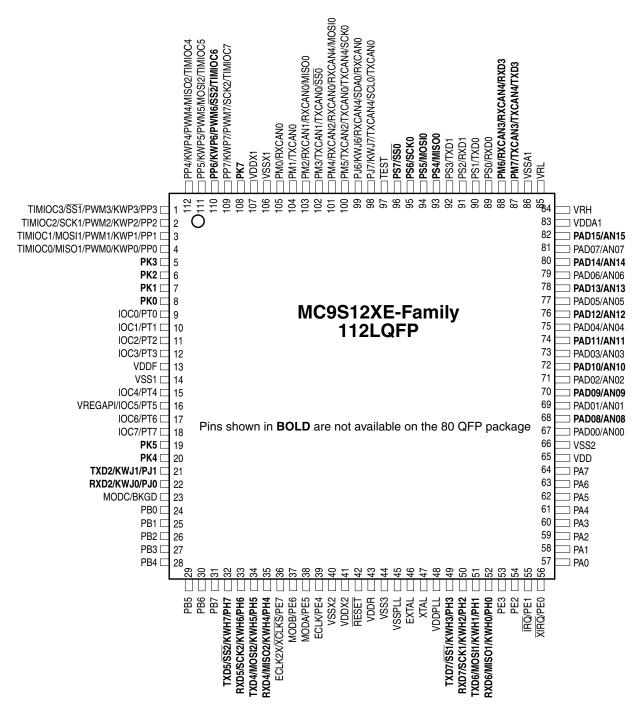

Figure 1-6. MC9S12XE-Family Pin Assignments 112-pin LQFP Package

# 1.4.1.5 Emulation of Single-Chip Mode

Developers use this mode for emulation systems in which the user's target application is normal singlechip mode. Code is executed from external memory or from internal memory depending on the state of ROMON and EROMON bit. In this mode the internal operation is visible on external bus interface.

## 1.4.1.6 Special Test Mode

This is for Freescale internal use only.

## 1.4.2 Power Modes

The MCU features two main low-power modes. Consult the respective module description for module specific behavior in system stop, system pseudo stop, and system wait mode. An important source of information about the clock system is the Clock and Reset Generator description (CRG).

### 1.4.2.1 System Stop Modes

The system stop modes are entered if the CPU executes the STOP instruction unless either the XGATE is active or an NVM command is active. The XGATE is active if it executes a thread or the XGFACT bit in the XGMCTL register is set. Depending on the state of the PSTP bit in the CLKSEL register the MCU goes into pseudo stop mode or full stop mode. Please refer to CRG description. Asserting RESET, XIRQ, IRQ or any other interrupt that is not masked exits system stop modes. System stop modes can be exited by XGATE or CPU activity independently, depending on the configuration of the interrupt request. If System-Stop is exited on an XGATE request then, as long as the XGATE does not set an interrupt flag on the CPU and the XGATE fake activity bit (FACT) remains cleared, once XGATE activity is completed System Stop mode will automatically be re-entered.

If the CPU executes the STOP instruction whilst XGATE is active or an NVM command is being processed, then the system clocks continue running until XGATE/NVM activity is completed. If a non-masked interrupt occurs within this time then the system does not effectively enter stop mode although the STOP instruction has been executed.

## 1.4.2.2 Full Stop Mode

The oscillator is stopped in this mode. By default all clocks are switched off and all counters and dividers remain frozen. The Autonomous Periodic Interrupt (API) and ATD modules may be enabled to self wake the device. A Fast wake up mode is available to allow the device to wake from Full Stop mode immediately on the PLL internal clock without starting the oscillator clock.

## 1.4.2.3 Pseudo Stop Mode

In this mode the system clocks are stopped but the oscillator is still running and the real time interrupt (RTI) and watchdog (COP), API and ATD modules may be enabled. Other peripherals are turned off. This mode consumes more current than system stop mode but, as the oscillator continues to run, the full speed wake up time from this mode is significantly shorter.

NP

| Register<br>Name                                 | _      | Bit 7 | 6                     | 5              | 4           | 3           | 2     | 1     | Bit 0 |  |  |  |  |

|--------------------------------------------------|--------|-------|-----------------------|----------------|-------------|-------------|-------|-------|-------|--|--|--|--|

| 0x000E–<br>0x001B<br>Non-PIM<br>Address<br>Range | R<br>W |       |                       |                | Non-PIM Add | dress Range |       |       |       |  |  |  |  |

| 0x001C<br>ECLKCTL                                | R<br>W | NECLK | NCLKX2                | DIV16          | EDIV0       |             |       |       |       |  |  |  |  |

| 0x001D<br>Reserved                               | R<br>W | 0     | 0                     | 0              | 0           | 0           | 0     | 0     | 0     |  |  |  |  |

| 0x001E<br>IRQCR                                  | R<br>W | IRQE  | IRQEN                 | 0              | 0           | 0           | 0     | 0     | 0     |  |  |  |  |

| 0x001F                                           | R      | 0     | 0                     | 0              | 0           | 0           | 0     | 0     | 0     |  |  |  |  |

| Reserved                                         | w      |       |                       |                |             |             |       |       |       |  |  |  |  |

| 0x0020–<br>0x0031<br>Non-PIM<br>Address<br>Range | R<br>W |       | Non-PIM Address Range |                |             |             |       |       |       |  |  |  |  |

| 0x0032<br>PORTK                                  | R<br>W | PK7   | PK6                   | PK5            | PK4         | РКЗ         | PK2   | PK1   | PK0   |  |  |  |  |

| 0x0033<br>DDRK                                   | R<br>W | DDRK7 | DDRK6                 | DDRK5          | DDRK4       | DDRK3       | DDRK2 | DDRK1 | DDRK0 |  |  |  |  |

| 0x0034–<br>0x023F<br>Non-PIM<br>Address<br>Range | R<br>W |       |                       |                | Non-PIM Ade | dress Range |       |       |       |  |  |  |  |

| 0x0240<br>PTT                                    | R<br>W | PTT7  | PTT6                  | PTT5           | PTT4        | PTT3        | PTT2  | PTT1  | PTT0  |  |  |  |  |

| 0x0241<br>PTIT                                   | R<br>W | PTIT7 | PTIT6                 | PTIT5          | PTIT4       | PTIT3       | PTIT2 | PTIT1 | PTIT0 |  |  |  |  |

| 0x0242<br>DDRT                                   | R<br>W | DDRT7 | DDRT6                 | DDRT5          | DDRT4       | DDRT3       | DDRT2 | DDRT1 | DDRT0 |  |  |  |  |

| 0x0243<br>RDRT                                   | R<br>W | RDRT7 | RDRT6                 | RDRT5          | RDRT4       | RDRT3       | RDRT2 | RDRT1 | RDRT0 |  |  |  |  |

|                                                  |        |       | ] = Unimpleme         | ented or Reser | ved         |             |       |       |       |  |  |  |  |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>CSZ  | <ul> <li>Access Type Indicator — This bit indicates if the access was a byte or word size access. This bit only contains valid information when tracing CPU12X activity in Detail Mode.</li> <li>0 Word Access</li> <li>1 Byte Access</li> </ul>                                                                                                                    |

| 5<br>CRW  | <ul> <li>Read Write Indicator — This bit indicates if the corresponding stored address corresponds to a read or write access. This bit only contains valid information when tracing CPU12X activity in Detail Mode.</li> <li>Write Access</li> <li>Read Access</li> </ul>                                                                                           |

| 4<br>COCF | <ul> <li>CPU12X Opcode Fetch Indicator — This bit indicates if the stored address corresponds to an opcode fetch cycle. This bit only contains valid information when tracing the XGATE accesses in Detail Mode.</li> <li>0 Stored information does not correspond to opcode fetch cycle</li> <li>1 Stored information corresponds to opcode fetch cycle</li> </ul> |

| 3<br>XACK | <ul> <li>XGATE Access Indicator — This bit indicates if the stored XGATE address corresponds to a free cycle. This bit only contains valid information when tracing the CPU12X accesses in Detail Mode.</li> <li>0 Stored information corresponds to free cycle</li> <li>1 Stored information does not correspond to free cycle</li> </ul>                          |

| 2<br>XSZ  | <ul> <li>Access Type Indicator — This bit indicates if the access was a byte or word size access. This bit only contains valid information when tracing XGATE activity in Detail Mode.</li> <li>0 Word Access</li> <li>1 Byte Access</li> </ul>                                                                                                                     |

| 1<br>XRW  | Read Write Indicator — This bit indicates if the corresponding stored address corresponds to a read or write<br>access. This bit only contains valid information when tracing XGATE activity in Detail Mode.0Write Access1Read Access                                                                                                                               |

| 0<br>XOCF | XGATE Opcode Fetch Indicator — This bit indicates if the stored address corresponds to an opcode fetch<br>cycle. This bit only contains valid information when tracing the CPU12X accesses in Detail Mode.0Stored information does not correspond to opcode fetch cycle1Stored information corresponds to opcode fetch cycle                                        |

#### Table 8-46. CXINF Field Descriptions (continued)

### 8.4.5.4 Reading Data from Trace Buffer

The data stored in the Trace Buffer can be read using either the background debug module (BDM) module, the XGATE or the CPU12X provided the S12XDBG module is not armed, is configured for tracing and the system not secured. When the ARM bit is written to 1 the trace buffer is locked to prevent reading. The trace buffer can only be unlocked for reading by an aligned word write to DBGTB when the module is disarmed.

The Trace Buffer can only be read through the DBGTB register using aligned word reads, any byte or misaligned reads return 0 and do not cause the trace buffer pointer to increment to the next trace buffer address. The Trace Buffer data is read out first-in first-out. By reading CNT in DBGCNT the number of valid 64-bit lines can be determined. DBGCNT will not decrement as data is read.

Whilst reading an internal pointer is used to determine the next line to be read. After a tracing session, the pointer points to the oldest data entry, thus if no overflow has occurred, the pointer points to line0, otherwise it points to the line with the oldest entry. The pointer is initialized by each aligned write to DBGTBH to point to the oldest data again. This enables an interrupted trace buffer read sequence to be easily restarted from the oldest data entry.

# 10.2 External Signal Description

The XGATE module has no external pins.

# 10.3 Memory Map and Register Definition

This section provides a detailed description of address space and registers used by the XGATE module.

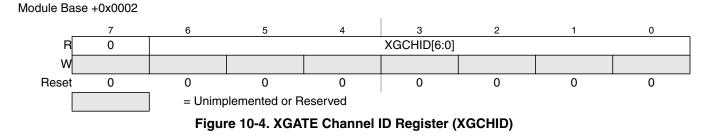

The memory map for the XGATE module is given below in Figure 10-2. The address listed for each register is the sum of a base address and an address offset. The base address is defined at the SoC level and the address offset is defined at the module level. Reserved registers read zero. Write accesses to the reserved registers have no effect.

# 10.3.1 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bits and field functions follow the register diagrams, in bit order.

| Register<br>Name  |        | 15   | 14         | 13         | 12      | 11          | 10  | 9           | 8      | 7    | 6     | 5     | 4    | 3      | 2    | 1      | 0       |

|-------------------|--------|------|------------|------------|---------|-------------|-----|-------------|--------|------|-------|-------|------|--------|------|--------|---------|

| 0x0000            | R      | 0    | 0          | 0          | 0       | 0           | 0   | 0           | 0      |      |       |       |      | XG     | 0    | XG     |         |

| XGMCTL            | w      | XGEM | XG<br>FRZM | XG<br>DBGM | XGSSM   | XG<br>FACTM |     | XG<br>SWEFM | XGIEM  | XGE  | XGFRZ | XGDBG | XGSS | FACT   |      | SWEF   | XGIE    |

| 0x0002            | R      |      |            |            |         |             |     |             |        | 0    |       |       | XG   | CHID[6 | 6:0] |        |         |

| XGCHID            | W      |      |            |            |         |             |     |             |        |      |       |       |      |        |      |        |         |

| 0x0003            | R      |      |            |            |         |             |     |             |        | 0    | 0     | 0     | 0    | 0      | XG   | CHPL[2 | 2:0]    |

| XGCHPL            | w      |      |            |            |         |             |     |             |        |      |       |       |      |        |      |        |         |

| 0x0004            | R      |      |            |            |         |             |     |             |        |      |       |       |      |        |      |        |         |

| Reserved          | w      |      |            |            |         |             |     |             |        |      |       |       |      |        |      |        |         |

| 0x0005            | R      |      |            |            |         |             |     |             |        | 0    | 0     | 0     | 0    | 0      | 0    | VOIDE  |         |

| XGISPSEL          | w      |      |            |            |         |             |     |             |        |      |       |       |      |        |      | XGISPS | EL[1:0] |

| 0x0006            | R      |      |            |            |         |             |     |             |        |      |       |       |      |        |      |        | 0       |

| XGISP74           | w      |      |            |            |         |             |     | XGI         | SP74[1 | 5:1] |       |       |      |        |      |        |         |

| 0x0006<br>XGISP31 | R      |      |            |            |         |             |     | XGI         | SP31[1 | 5:1] |       |       |      |        |      |        | 0       |

|                   | W      |      |            |            |         |             |     | _           |        | - 1  |       |       |      |        |      |        | -       |

| 0x0006<br>XGVBR   | R<br>W |      |            |            |         |             |     | XG          | VBR[1  | 5:1] |       |       |      |        |      |        | 0       |

|                   | ••     |      | = Unin     | npleme     | nted or | Reserv      | /ed |             |        |      |       |       |      |        |      |        |         |

#### Read: Anytime

Write: In Debug Mode<sup>1</sup>

Table 10-3. XGCHID Field Descriptions

| Field              | Description                                             |

|--------------------|---------------------------------------------------------|

| 6–0<br>XGCHID[6:0] | Request Identifier — ID of the currently active channel |

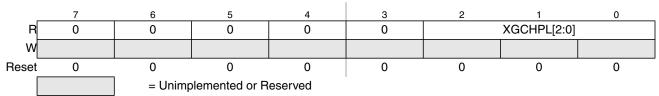

# 10.3.1.3 XGATE Channel Priority Level (XGCHPL)

The XGATE Channel Priority Level Register (Figure 10-5) shows the priority level of the current thread. In debug mode this register can be used to select a priority level when launching a thread (see Section 10.6.1, "Debug Features").

Module Base +0x0003

#### Figure 10-5. XGATE Channel Priority Level Register (XGCHPL)

Read: Anytime

Write: In Debug Mode<sup>1</sup>

#### Table 10-4. XGCHPL Field Descriptions

| Field              | Description                                                    |

|--------------------|----------------------------------------------------------------|

| 2-0<br>XGCHPL[2:0] | Priority Level— Priority level of the currently active channel |

## 10.3.1.4 XGATE Initial Stack Pointer Select Register (XGISPSEL)

The XGATE Initial Stack Pointer Select Register (Figure 10-6) determines the register which is mapped to address "Module Base +0x0006". A value of zero selects the Vector Base Register (XGVBR). Setting

1. Refer to Section 10.6.1, "Debug Features"

#### Table 10-9. XGVBR Field Descriptions

| Field               | Description                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------|

| 15–1<br>XBVBR[15:1] | Vector Base Address — The XGVBR register holds the start address of the vector block in the XGATE memory map. |

### 10.3.1.8 XGATE Channel Interrupt Flag Vector (XGIF)

The XGATE Channel Interrupt Flag Vector (Figure 10-10) provides access to the interrupt flags of all channels. Each flag may be cleared by writing a "1" to its bit location. Refer to Section 10.5.2, "Outgoing Interrupt Requests" for further information.

Module Base +0x0008

| _      | 127     | 126     | 125     | 124     | 123     | 122     | 121     | 120     | 119     | 118     | 117     | 116     | 115     | 114     | 113      | 112     |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------|---------|

| R      | 0       | 0       | 0       | 0       | 0       | 0       | 0       | XGIF 78 | XGF 77  | XGIF_76 | XGIF_75 | XGIF_74 | XGIF_73 | XGIF_72 | XGIF 71  | XGIF_70 |

| W      |         |         |         |         |         |         |         | AGIF_/0 | AGF_//  | AGIF_70 | AGIF_75 | AGIF_/4 | AGIF_/3 | AGIF_72 | AGIF_/ I | AGIF_70 |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0        | 0       |

|        |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |         |

|        | 111     | 110     | 109     | 108     | 107     | 106     | 105     | 104     | 103     | 102     | 101     | 100     | 99      | 98      | 97       | 96      |

| R<br>W | XGIF_6F | XGIF_6E | XGIF_6D | XGIF_6C | XGIF_6B | XGIF_6A | XGIF_69 | XGIF_68 | XGF_67  | XGIF_66 | XGIF_65 | XGIF_64 | XGIF_63 | XGIF_62 | XGIF_61  | XGIF_60 |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0        | 0       |

|        |         |         |         |         |         |         |         |         |         |         |         |         | I       |         |          |         |

| _      | 95      | 94      | 93      | 92      | 91      | 90      | 89      | 88      | 87      | 86      | 85      | 84      | 83      | 82      | 81       | 80      |

| R<br>W | XGIF_5F | XGIF_5E | XGIF_5D | XGIF_5C | XGIF_5B | XGIF_5A | XGIF_59 | XGIF_58 | XGF_57  | XGIF_56 | XGIF_55 | XGIF_54 | XGIF_53 | XGIF_52 | XGIF_51  | XGIF_50 |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0        | 0       |

|        |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |         |

| _      | 79      | 78      | 77      | 76      | 75      | 74      | 73      | 72      | 71      | 70      | 69      | 68      | 67      | 66      | 65       | 64      |

| R<br>W | XGIF_4F | XGIF_4E | XGIF_4D | XGIF_4C | XGIF_4B | XGIF_4A | XGIF_49 | XGIF_48 | XGF _47 | XGIF_46 | XGIF_45 | XGIF_44 | XGIF_43 | XGIF_42 | XGIF_41  | XGIF_40 |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0        | 0       |

Figure 10-10. XGATE Channel Interrupt Flag Vector (XGIF)

The programmer's model of the XGATE RISC core is shown in Figure 10-22. The processor offers a set of seven general purpose registers (R1 - R7), which serve as accumulators and index registers. An additional eighth register (R0) is tied to the value "\$0000". Registers R1 and R7 have additional functionality. R1 is preloaded with the initial data pointer of the channel's service request vector (see Figure 10-23). R7 is either preloaded with the content of XGISP74 if the interrupt priority of the current channel is in the range 7 to 4, or it is with preloaded the content of XGISP31 if the interrupt priority of the current channel is in the range 3 to 1. The remaining general purpose registers will be reset to an unspecified value at the beginning of each thread.

The 16 bit program counter allows the addressing of a 64 kbyte address space.

The condition code register contains four bits: the sign bit (S), the zero flag (Z), the overflow flag (V), and the carry bit (C). The initial content of the condition code register is undefined.

## 10.4.3 Memory Map

The XGATE's RISC core is able to access an address space of 64K bytes. The allocation of memory blocks within this address space is determined on chip level. Refer to the **S12X\_MMC Section** for a detailed information.

The XGATE vector block assigns a start address and a data pointer to each XGATE channel. Its position in the XGATE memory map can be adjusted through the XGVBR register (see Section 10.3.1.7, "XGATE Vector Base Address Register (XGVBR)"). Figure 10-23 shows the layout of the vector block. Each vector consists of two 16 bit words. The first contains the start address of the service routine. This value will be loaded into the program counter before a service routine is executed. The second word is a pointer to the service routine's data space. This value will be loaded into register R1 before a service routine is executed.

Store Byte to Memory (Low Byte)

#### Operation

$$\begin{split} & \text{RS.L} \Rightarrow \text{M[RB, \#OFFS5]} \\ & \text{RS.L} \Rightarrow \text{M[RB, RI]} \\ & \text{RS.L} \Rightarrow \text{M[RB, RI]}; \qquad \text{RI+1} \Rightarrow \text{RI}; \\ & \text{RI-1} \Rightarrow \text{RI}; \qquad \qquad \text{RS.L} \Rightarrow \text{M[RB, RI]}^1 \end{split}$$

Stores the low byte of register RS to memory.

#### **CCR Effects**

- N: Not affected.

- Z: Not affected.

- V: Not affected.

- C: Not affected.

#### **Code and CPU Cycles**

| Source Form           | Address<br>Mode |   |   |   |   |   | Machin | e Code |       |   |   | Cycles |

|-----------------------|-----------------|---|---|---|---|---|--------|--------|-------|---|---|--------|

| STB RS, (RB, #OFFS5), | IDO5            | 0 | 1 | 0 | 1 | 0 | RS     | RB     | OFFS5 |   |   | Pw     |

| STB RS, (RB, RI)      | IDR             | 0 | 1 | 1 | 1 | 0 | RS     | RB     | RI    | 0 | 0 | Pw     |

| STB RS, (RB, RI+)     | IDR+            | 0 | 1 | 1 | 1 | 0 | RS     | RB     | RI    | 0 | 1 | Pw     |

| STB RS, (RB, -RI)     | -IDR            | 0 | 1 | 1 | 1 | 0 | RS     | RB     | RI    | 1 | 0 | Pw     |

1. If the same general purpose register is used as index (RI) and source register (RS), the unmodified content of the source register is written to the memory: RS.L  $\Rightarrow$  M[RB, RS-1]; RS-1  $\Rightarrow$  RS

Write: Has no meaning or effect in the normal mode; only writable in special modes (test\_mode = 1).

The period of the first count after a write to the TCNT registers may be a different size because the write is not synchronized with the prescaler clock.

## 22.3.2.6 Timer System Control Register 1 (TSCR1)

Module Base + 0x0006

|       | 7   | 6            | 5               | 4     | 3    | 2 | 1 | 0 |

|-------|-----|--------------|-----------------|-------|------|---|---|---|

| R     | TEN | TSWAI        | TSFRZ           | TFFCA | PRNT | 0 | 0 | 0 |

| W     |     | TOVIAI       | ISFNZ           | TFFCA | FUNI |   |   |   |

| Reset | 0   | 0            | 0               | 0     | 0    | 0 | 0 | 0 |

|       |     | = Unimplemer | nted or Reserve |       |      |   |   |   |

Figure 22-12. Timer System Control Register 1 (TSCR1)

Read: Anytime

Write: Anytime

| Field      | Description                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TEN   | Timer Enable         0       Disables the main timer, including the counter. Can be used for reducing power consumption.         1       Allows the timer to function normally.         If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler. |

| 6<br>TSWAI | <ul> <li>Timer Module Stops While in Wait</li> <li>Allows the timer module to continue running during wait.</li> <li>Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.</li> <li>TSWAI also affects pulse accumulator.</li> </ul>                                  |

| 5<br>TSFRZ | <ul> <li>Timer Stops While in Freeze Mode</li> <li>0 Allows the timer counter to continue running while in freeze mode.</li> <li>1 Disables the timer counter whenever the MCU is in freeze mode. This is useful for emulation.</li> <li>TSFRZ does not stop the pulse accumulator.</li> </ul>                                          |

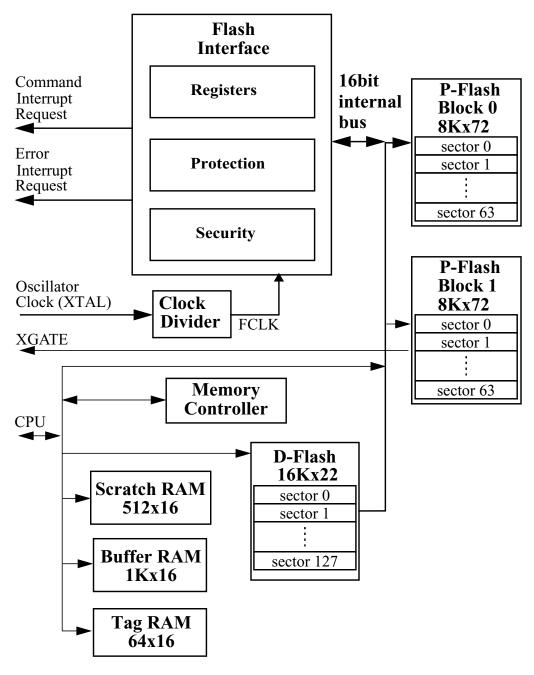

Figure 24-1. FTM128K2 Block Diagram

# 24.2 External Signal Description

The Flash module contains no signals that connect off-chip.

# Chapter 25 256 KByte Flash Module (S12XFTM256K2V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                                                                                                                 |

|--------------------|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.08             | 14 Nov 2007      | 25.5.2/25-951<br>25.4.2/25-927 | <ul> <li>Changed terminology from 'word program' to "Program P-Flash' in the BDM unsecuring description, Section 25.5.2</li> <li>Added requirement that user not write any Flash module register during</li> </ul>                     |

|                    |                  | 20.4.2/20-927                  | execution of commands 'Erase All Blocks', Section 25.4.2.8, and 'Unsecure Flash', Section 25.4.2.11                                                                                                                                    |

|                    |                  | 25.4.2.8/25-933                | - Added statement that security is released upon successful completion of command 'Erase All Blocks', Section 25.4.2.8                                                                                                                 |

| V01.09             | 19 Dec 2007      | 25.4.2.5/25-930                | - Corrected Error Handling table for Load Data Field command                                                                                                                                                                           |

|                    |                  | 25.4.2/25-927                  | - Corrected Error Handling table for Full Partition D-Flash, Partition D-Flash, and EEPROM Emulation Query commands                                                                                                                    |

|                    |                  | 25.3.1/25-896                  | - Corrected P-Flash IFR Accessibility table                                                                                                                                                                                            |

| V01.10             | 25 Sep 2009      | 25.1/25-891                    | - Clarify single bit fault correction for P-Flash phrase                                                                                                                                                                               |

|                    |                  | 25.3.2.1/25-903                | - Expand FDIV vs OSCCLK Frequency table                                                                                                                                                                                                |

|                    |                  | 25.4.2.4/25-930                | - Add statement concerning code runaway when executing Read Once command from Flash block containing associated fields                                                                                                                 |

|                    |                  | 25.4.2.7/25-932                | - Add statement concerning code runaway when executing Program Once command from Flash block containing associated fields                                                                                                              |

|                    |                  | 25.4.2.12/25-<br>936           | <ul> <li>Add statement concerning code runaway when executing Verify Backdoor</li> <li>Access Key command from Flash block containing associated fields</li> <li>Relate Key 0 to associated Backdoor Comparison Key address</li> </ul> |

|                    |                  | 25.4.2.12/25-                  | - Change "power down reset" to "reset"                                                                                                                                                                                                 |

|                    |                  | 936                            | - Add ACCERR condition for Disable EEPROM Emulation command                                                                                                                                                                            |

|                    |                  | 25.4.2.12/25-                  | The following changes were made to clarify module behavior related to Flash                                                                                                                                                            |

|                    |                  | 936                            | register access during reset sequence and while Flash commands are active:                                                                                                                                                             |

|                    |                  | 25.4.2.20/25-                  | - Add caution concerning register writes while command is active                                                                                                                                                                       |

|                    |                  | 945                            | - Writes to FCLKDIV are allowed during reset sequence while CCIF is clear                                                                                                                                                              |

|                    |                  |                                | - Add caution concerning register writes while command is active<br>- Writes to FCCOBIX, FCCOBHI, FCCOBLO registers are ignored during                                                                                                 |

|                    |                  | 25.3.2/25-901                  | reset sequence                                                                                                                                                                                                                         |

|                    |                  | 25.3.2.1/25-903                |                                                                                                                                                                                                                                        |

|                    |                  | 25.4.1.2/25-922                |                                                                                                                                                                                                                                        |

|                    |                  | 25.6/25-951                    |                                                                                                                                                                                                                                        |

|                    |                  |                                |                                                                                                                                                                                                                                        |

#### Table 25-1. Revision History

# 25.1 Introduction

The FTM256K2 module implements the following:

• 256 Kbytes of P-Flash (Program Flash) memory, consisting of 2 physical Flash blocks, intended primarily for nonvolatile code storage

### CAUTION

A Flash word or phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash word or phrase is not allowed.

### 25.4.2.1 Erase Verify All Blocks Command

The Erase Verify All Blocks command will verify that all P-Flash and D-Flash blocks have been erased.

Table 25-33. Erase Verify All Blocks Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters  |  |  |

|-------------|-------------------|--|--|

| 000         | 0x01 Not required |  |  |

Upon clearing CCIF to launch the Erase Verify All Blocks command, the Memory Controller will verify that the entire Flash memory space is erased. The CCIF flag will set after the Erase Verify All Blocks operation has completed.

| Register | Error Bit | Error Condition                                                         |  |

|----------|-----------|-------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                             |  |

|          |           | Set if a Load Data Field command sequence is currently active           |  |

| FSTAT    | FPVIOL    | None                                                                    |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |

| FERSTAT  | EPVIOLIF  | None                                                                    |  |

# 25.4.2.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or D-Flash block has been erased. The FCCOB upper global address bits determine which block must be verified.

Table 25-35. Erase Verify Block Command FCCOB Requirements

| ссо | BIX[2:0] | FCCOB Parameters |                                                              |

|-----|----------|------------------|--------------------------------------------------------------|

|     | 000      | 0x02             | Global address [22:16] of the<br>Flash block to be verified. |

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or D-Flash block is erased. The CCIF flag will set after the Erase Verify Block operation has completed.

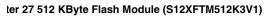

Figure 27-26. Generic Flash Command Write Sequence Flowchart

| Register | Error Bit Error Condition |                                                                                     |  |

|----------|---------------------------|-------------------------------------------------------------------------------------|--|

|          | ACCERR                    | Set if CCOBIX[2:0] != 001 at command launch                                         |  |

|          |                           | Set if a Load Data Field command sequence is currently active                       |  |

|          |                           | Set if command not available in current mode (see Table 27-30)                      |  |

| FSTAT    |                           | Set if an invalid global address [22:16] is supplied                                |  |

|          | FPVIOL                    | Set if an area of the selected P-Flash block is protected                           |  |

|          | MGSTAT1                   | Set if any errors have been encountered during the verify operation                 |  |

|          | MGSTAT0                   | Set if any non-correctable errors have been encountered during the verify operation |  |

| FERSTAT  | EPVIOLIF                  | None                                                                                |  |

#### Table 27-50. Erase P-Flash Block Command Error Handling

### 27.4.2.10 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

| CCOBIX[2:0] | FCCOB Parameters                                                                                                         |                                                                  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| 000         | 0x0A                                                                                                                     | Global address [22:16] to identify<br>P-Flash block to be erased |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 27.1.2.1 for the P-Flash sector size. |                                                                  |  |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                       |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 27-30)                      |  |  |

|          |           | Set if an invalid global address [22:16] is supplied                                |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |  |  |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                |  |  |

Table 27-52. Erase P-Flash Sector Command Error Handling

| FCMD | Command                          | Function on D-Flash Memory                                                                                                                                                                                                                                |  |

|------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x08 | Erase All Blocks                 | Erase all D-Flash (and P-Flash) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN<br>bits in the FPROT register and the EPDIS and EPOPEN bits in the EPROT register are<br>set prior to launching the command. |  |

| 0x0B | Unsecure Flash                   | Supports a method of releasing MCU security by erasing all D-Flash (and P-Flash) blocks and verifying that all D-Flash (and P-Flash) blocks are erased.                                                                                                   |  |

| 0x0D | Set User Margin<br>Level         | Specifies a user margin read level for the D-Flash block.                                                                                                                                                                                                 |  |

| 0x0E | Set Field Margin<br>Level        | Specifies a field margin read level for the D-Flash block (special modes only).                                                                                                                                                                           |  |

| 0x0F | Full Partition D-<br>Flash       | Erase the D-Flash block and partition an area of the D-Flash block for user access.                                                                                                                                                                       |  |

| 0x10 | Erase Verify D-<br>Flash Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                                          |  |

| 0x11 | Program D-Flash                  | Program up to four words in the D-Flash block.                                                                                                                                                                                                            |  |

| 0x12 | Erase D-Flash<br>Sector          | Erase all bytes in a sector of the D-Flash block.                                                                                                                                                                                                         |  |

| 0x13 | Enable EEPROM<br>Emulation       | Enable EEPROM emulation where writes to the buffer RAM EEE partition will be copied to the D-Flash EEE partition.                                                                                                                                         |  |

| 0x14 | Disable EEPROM<br>Emulation      | Suspend all current erase and program activity related to EEPROM emulation but leave current EEE tags set.                                                                                                                                                |  |

| 0x15 | EEPROM<br>Emulation Query        | Returns EEE partition and status variables.                                                                                                                                                                                                               |  |

| 0x20 | Partition D-Flash                | Partition an area of the D-Flash block for user access.                                                                                                                                                                                                   |  |

| Table 29-32. | <b>D-Flash</b> | Commands  |

|--------------|----------------|-----------|

|              | Dilaon         | oominanao |

# 29.4.2 Flash Command Description

This section provides details of all available Flash commands launched by a command write sequence. The ACCERR bit in the FSTAT register will be set during the command write sequence if any of the following illegal steps are performed, causing the command not to be processed by the Memory Controller:

- Starting any command write sequence that programs or erases Flash memory before initializing the FCLKDIV register

- Writing an invalid command as part of the command write sequence

- For additional possible errors, refer to the error handling table provided for each command

If a Flash block is read during execution of an algorithm (CCIF = 0) on that same block, the read operation will return invalid data. If the SFDIF or DFDIF flags were not previously set when the invalid read operation occurred, both the SFDIF and DFDIF flags will be set and the FECCR registers will be loaded with the global address used in the invalid read operation with the data and parity fields set to all 0.

If the ACCERR or FPVIOL bits are set in the FSTAT register, the user must clear these bits before starting any command write sequence (see Section 29.3.2.7).

#### 0x02F0–0x02F7 Voltage Regulator (VREG\_3V3) Map

| Address | Name      |   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3    | Bit 2  | Bit 1 | Bit 0 |

|---------|-----------|---|--------|--------|--------|--------|----------|--------|-------|-------|

| 0x02F0  | VREGHTCL  | R | 0 0    | 0      | VSEL   | VAE    | HTEN     | HTDS   | HTIE  | HTIF  |

|         |           | W |        |        |        |        |          |        |       |       |

| 0x02F1  | VREGCTRL  | R | 0      | 0      | 0      | 0      | 0        | LVDS   | LVIE  | LVIF  |

|         |           | W |        |        |        |        |          |        |       |       |

| 0x02F2  | VREGAPICL | R | APICLK | 0      | 0      | APIFES | ES APIEA | APIFE  | APIE  | APIF  |

|         |           | W | / 1021 |        |        | /      |          |        |       |       |

| 0x02F3  | VREGAPITR | R | APITR5 | APITR4 | APITR3 | APITR2 | APITR1   | APITR0 | 0     | 0     |

| 0.02.0  | -         | W |        |        |        |        |          |        |       |       |

| 0x02F4  | VREGAPIRH | R | APIR15 | APIR14 | APIR13 | APIR12 | APIR11   | APIR10 | APIR9 | APIR8 |

|         |           |   | W      |        |        |        |          |        |       |       |

| 0x02F5  | VREGAPIRL | R | APIR7  | APIR6  | APIR5  | APIR4  | APIR3    | APIR2  | APIR1 | APIR0 |

|         |           | W |        |        |        |        |          |        |       |       |

| 0x02F6  | Reserved  | R | 0      | 0      | 0      | 0      | 0        | 0      | 0     | 0     |

|         |           | W |        |        |        |        |          |        |       |       |

| 0x02F7  | VREGHTTR  |   | HTOEN  | 0      | 0      | 0      | HTTR3    | HTTR2  | HTTR1 | HTTR0 |

|         |           | W |        |        |        |        |          |        |       |       |

### 0x02F8–0x02FF Reserved

| Address | Name        |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x02F8- | Reserved    | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x02FF  | i lesel veu | w |       |       |       |       |       |       |       |       |

#### 0x0300–0x0327 Pulse Width Modulator 8-Bit 8-Channel (PWM) Map (Sheet 1 of 3)

| Address | Name      |         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |   |

|---------|-----------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---|

| 0x0300  | PWME      | R<br>W  | PWME7 | PWME6 | PWME5 | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |   |

| 0x0301  | PWMPOL    | R<br>W  | PPOL7 | PPOL6 | PPOL5 | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |   |

| 0x0302  | PWMCLK    | R<br>W  | PCLK7 | PCLK6 | PCLK5 | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |   |

| 0x0303  | PWMPRCLK  | R<br>W  | 0     | PCKB2 | PCKB1 | PCKB0 | 0     | PCKA2 | PCKA1 | PCKA0 |   |

| 0x0304  | PWMCAE    | R<br>W  | CAE7  | CAE6  | CAE5  | CAE4  | CAE3  | CAE2  | CAE1  | CAE0  |   |

| 0x0305  | PWMCTL    | R<br>W  | CON67 | CON45 | CON23 | CON01 | PSWAI | PFRZ  | 0     | 0     |   |

| 0x0306  | PWMTST    | R       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |   |

| 0x0300  | Test Only | W       |       |       |       |       |       |       |       |       |   |

| 0x0307  | PWMPRSC   | PWMPBSC | R     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 |

|         |           | W       |       |       |       |       |       |       |       |       |   |

| 0x0308  | PWMSCLA   | R<br>W  | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |   |

| 0x0309  | PWMSCLB   | R<br>W  | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |   |