Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorHCS12XCore Size16-BitSpeed50MHzConnectivityCANbus, EBI/EMI, PC, IrDA, SCI, SPIPeripheralsLVD, POR, PWM, WDTNumber of I/O59Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)Purchase URLhttps://www.e-xfl.com/product-detail/nxp-semiconductors/s912xet256j2maa | Details                    |                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|

| Core Size16-BitSpeed50MHzConnectivityCANbus, EBI/EMI, IPC, IrDA, SCI, SPIPeripheralsLVD, POR, PWM, WDTNumber of I/O59Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                    | Product Status             | Active                                                                  |

| Speed50MHzConnectivityCANbus, EBI/EMI, I²C, IrDA, SCI, SPIPeripheralsLVD, POR, PWM, WDTNumber of I/O59Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFP (14x14)                                                                                                                                                | Core Processor             | HCS12X                                                                  |

| ConnectivityCANbus, EBI/EMI, I²C, IrDA, SCI, SPIPeripheralsLVD, POR, PWM, WDTNumber of I/O59Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                             | Core Size                  | 16-Bit                                                                  |

| PeripheralsLVD, POR, PWM, WDTNumber of I/O59Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                             | Speed                      | 50MHz                                                                   |

| Number of I/O59Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                          | Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Program Memory Size256KB (256K × 8)Program Memory TypeFLASHEEPROM Size4K × 8RAM Size16K × 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                                         | Peripherals                | LVD, POR, PWM, WDT                                                      |

| Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                                                                            | Number of I/O              | 59                                                                      |

| EEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                                                                                                    | Program Memory Size        | 256KB (256K x 8)                                                        |

| RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                                                                                                                     | Program Memory Type        | FLASH                                                                   |

| Voltage - Supply (Vcc/Vdd)1.72V ~ 5.5VData ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                                                                                                                                    | EEPROM Size                | 4K x 8                                                                  |

| Data ConvertersA/D 8x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                                                                                                                                                                          | RAM Size                   | 16K x 8                                                                 |

| Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case80-QFPSupplier Device Package80-QFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                  | Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     80-QFP       Supplier Device Package     80-QFP (14x14)                                                                                                                                                                                                                                                                                                                                                                | Data Converters            | A/D 8x12b                                                               |

| Mounting Type     Surface Mount       Package / Case     80-QFP       Supplier Device Package     80-QFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                   | Oscillator Type            | External                                                                |

| Package / Case     80-QFP       Supplier Device Package     80-QFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Supplier Device Package 80-QFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mounting Type              | Surface Mount                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Package / Case             | 80-QFP                                                                  |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xet256j2maa                                                                                                                                                                                                                                                                                                                                                                                                                                               | Supplier Device Package    | 80-QFP (14x14)                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xet256j2maa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 208<br>MAPBGA | LQFP<br>144 | LQFP<br>112 | QFP <sup>(1)</sup><br>80 | Pin   | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func. | 5th<br>Func. |

|---------------|-------------|-------------|--------------------------|-------|--------------|--------------|--------------|--------------|

| D13           | 108         | 84          | 60                       | VRH   |              |              |              |              |

| C13           | 109         | 85          | 61                       | VRL   |              |              |              |              |

| E13           | 110         | 86          | 62                       | VSSA1 |              |              |              |              |

| B14           | 111         |             |                          | PAD18 | AN18         |              |              |              |

| A14           | 112         |             |                          | PAD19 | AN19         |              |              |              |

| C12           | 113         |             |                          | PAD20 | AN20         |              |              |              |

| B13           | 114         |             |                          | PAD21 | AN21         |              |              |              |

| D12           | 115         |             |                          | PAD22 | AN22         |              |              |              |

| B12           | 116         |             |                          | PAD23 | AN23         |              |              |              |

| C11           | 117         | 87          |                          | PM7   | TXCAN3       | TXCAN4       | TXD3         |              |

| A13           | 118         | 88          |                          | PM6   | RXCAN3       | RXCAN4       | RXD3         |              |

| D11           | 119         | 89          | 63                       | PS0   | RXD0         |              |              |              |

| B11           | 120         | 90          | 64                       | PS1   | TXD0         |              |              |              |

| C10           | 121         | 91          | 65                       | PS2   | RXD1         |              |              |              |

| A12           | 122         | 92          | 66                       | PS3   | TXD1         |              |              |              |

| VSSX          |             |             |                          | VSSX6 |              |              |              |              |

| VDDX          |             |             |                          | VDDX6 |              |              |              |              |

| B10           | 123         | 93          |                          | PS4   | MISO0        |              |              |              |

| A11           | 124         | 94          |                          | PS5   | MOSI0        |              |              |              |

| A10           | 125         | 95          |                          | PS6   | SCK0         |              |              |              |

| C9            | 126         | 96          |                          | PS7   | <u>SS0</u>   |              |              |              |

| B9            | 127         | 97          | 67                       | TEST  |              |              |              |              |

| D9            | 128         | 98          | 68                       | PJ7   | KWJ7         | TXCAN4       | SCL0         | TXCAN0       |

| A9            | 129         | 99          | 69                       | PJ6   | KWJ6         | RXCAN4       | SDA0         | RXCAN0       |

| C8            | 130         |             |                          | PJ5   | KWJ5         | SCL1         | CS2          |              |

| B8            |             |             |                          | PF0   | CS0          |              |              |              |

| D8            | 131         |             |                          | PJ4   | KWJ4         | SDA1         | CSO          |              |

| A8            |             |             |                          | PF1   | CS1          |              |              |              |

| D7            | 132         | 100         | 70                       | PM5   | TXCAN2       | TXCAN0       | TXCAN4       | SCK0         |

#### Table 2-51. DDRH Register Field Descriptions (continued)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DDRH | Port H data direction—         This register controls the data direction of pin 1.         The enabled SCI6 forces the I/O state to be an output. Depending on the configuration of the enabled routed SPI1 this pin will be forced to be input or output. In those cases the data direction bits will not change. The DDRM bits revert to controlling the I/O direction of a pin when the associated peripheral module is disabled.         1 Associated pin is configured as output.         0 Associated pin is configured as input.                        |

| 0<br>DDRH | <ul> <li>Port H data direction—</li> <li>This register controls the data direction of pin 0.</li> <li>The enabled SCI6 forces the I/O state to be an input. Depending on the configuration of the enabled routed SPI1 this pin will be forced to be input or output. In those cases the data direction bits will not change. The DDRM bits revert to controlling the I/O direction of a pin when the associated peripheral module is disabled.</li> <li>1 Associated pin is configured as output.</li> <li>0 Associated pin is configured as input.</li> </ul> |

#### NOTE

Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read on PTH or PTIH registers, when changing the DDRH register.

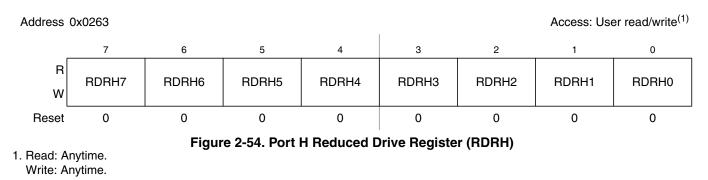

# 2.3.56 Port H Reduced Drive Register (RDRH)

#### Table 2-52. RDRH Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>RDRH | <ul> <li>Port H reduced drive—Select reduced drive for outputs</li> <li>This register configures the drive strength of output pins 7 through 0 as either full or reduced independent of the function used on the pins. If a pin is used as input this bit has no effect.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength).</li> <li>0 Full drive strength enabled.</li> </ul> |

# 2.4.2.9 Interrupt flag register (PIFx)

If the pin is used as an interrupt input this register holds the interrupt flag after a valid pin event.

## 2.4.2.10 Module routing register (MODRR, PTRRR, PTLRR, PTFRR)

This register supports the re-routing of the CAN0, CAN4, SPI2-0, SCI7-3, IIC0, TIM and CS[3:0] pins to alternative ports. This allows a software re-configuration of the pinouts of the different package options with respect to above peripherals.

# 2.4.3 Pins and Ports

#### NOTE

Please refer to the SOC Guide to determine the pin availability in the different package options.

#### 2.4.3.1 BKGD pin

The BKGD pin is associated with the S12X\_BDM and S12X\_EBI modules.

During reset, the BKGD pin is used as MODC input.

## 2.4.3.2 Port A, B

Port A pins PA[7:0] and Port B pins PB[7:0] can be used for either general-purpose I/O with the external bus interface. In this case Port A and Port B are associated with the external address bus outputs ADDR15-ADDR8 and ADDR7-ADDR0, respectively. PB0 is the ADDR0 or UDS output.

## 2.4.3.3 Port C, D

Port C pins PC[7:0] and Port D pins PD[7:0] can be used for either general-purpose I/O with the external bus interface. In this case Port C and Port D are associated with the external data bus inputs/outputs DATA15-DATA8 and DATA7-DATA0, respectively.

These pins are configured for reduced input threshold in certain operating modes (refer to S12X\_EBI section).

## 2.4.3.4 Port E

Port E is associated with the external bus control outputs  $\overline{RW}$ ,  $\overline{LSTRB}$ ,  $\overline{LDS}$  and  $\overline{RE}$ , the free-running clock outputs ECLK and ECLK2X, as well as with the TAGHI, TAGLO, MODA and MODB and interrupt inputs  $\overline{IRQ}$  and  $\overline{XIRQ}$ .

Port E pins PE[7:2] can be used for either general-purpose I/O or with the alternative functions.

Port E pin PE[7] can be used for either general-purpose I/O or as the free-running clock ECLKX2 output running at the Core Clock rate. The clock output is always enabled in emulation modes.

;many cases assemblers are "direct page aware" and can ;automatically select direct mode.

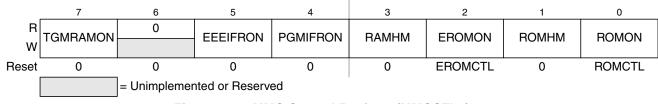

#### 3.3.2.5 MMC Control Register (MMCCTL1)

Address: 0x0013 PRR

Figure 3-10. MMC Control Register (MMCCTL1)

Read: Anytime. In emulation modes read operations will return the data from the external bus. In all other modes the data are read from this register.

Write: Refer to each bit description. In emulation modes write operations will also be directed to the external bus.

#### CAUTION

XGATE write access to this register during an CPU access which makes use of this register could lead to unexpected results.

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>TGMRAMON | <ul> <li>EEE Tag RAM and FTM SCRATCH RAM visible in the memory map</li> <li>Write: Anytime</li> <li>This bit is used to made the EEE Tag RAM nd FTM SCRATCH RAM visible in the global memory map.</li> <li>0 Not visible in the memory map.</li> <li>1 Visible in the memory map.</li> </ul>                                                                                             |  |  |

| 5<br>EEEIFRON | <ul> <li>EEE IFR visible in the memory map</li> <li>Write: Anytime</li> <li>This bit is used to made the IFR sector of EEE DATA FLASH visible in the global memory map.</li> <li>0 Not visible in the memory map.</li> <li>1 Visible in the memory map.</li> </ul>                                                                                                                       |  |  |

| 4<br>PGMIFRON | <ul> <li>Program IFR visible in the memory map</li> <li>Write: Anytime</li> <li>This bit is used to made the IFR sector of the Program Flash visible in the global memory map.</li> <li>0 Not visible in the memory map.</li> <li>1 Visible in the memory map.</li> </ul>                                                                                                                |  |  |

| 3<br>RAMHM    | <ul> <li>RAM only in higher Half of the memory map</li> <li>Write: Once in normal and emulation modes and anytime in special modes</li> <li>0 Accesses to \$4000-\$7FFF will be mapped to \$14_4000-\$14_7FFF in the global memory space (external access).</li> <li>1 Accesses to \$4000-\$7FFF will be mapped to \$0F_C000-\$0F_FFFF in the global memory space (RAM area).</li> </ul> |  |  |

Table 3-11. MMCCTL1 Field Descriptions

#### ter 3 Memory Mapping Control (S12XMMCV4)

#### Expansion of the BDM Local Address Map

PPAGE, RPAGE, and EPAGE registers are also used for the expansion of the BDM local address to the global address. These registers can be read and written by the BDM.

The BDM expansion scheme is the same as the CPU expansion scheme.

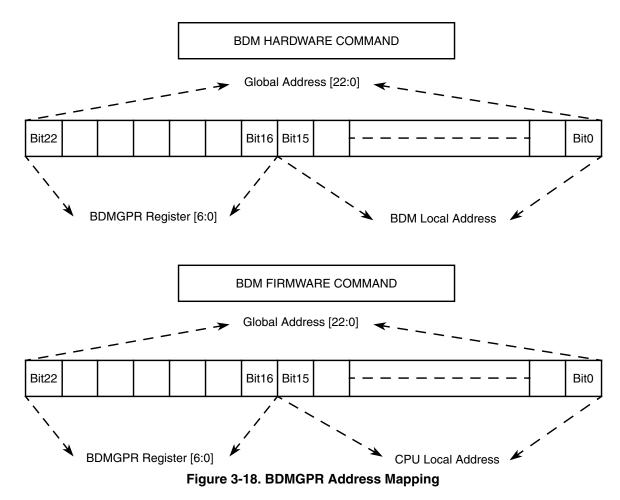

# 3.4.2.2 Global Addresses Based on the Global Page

#### **CPU Global Addresses Based on the Global Page**

The seven global page index bits allow access to the full 8 Mbyte address map that can be accessed with 23 address bits. This provides an alternative way to access all of the various pages of FLASH, RAM and EEE as well as additional external memory.

The GPAGE Register is used only when the CPU is executing a global instruction (see Section 3.3.2.3, "Global Page Index Register (GPAGE)). The generated global address is the result of concatenation of the CPU local address [15:0] with the GPAGE register [22:16] (see Figure 3-7).

#### **BDM Global Addresses Based on the Global Page**

The seven BDMGPR Global Page index bits allow access to the full 8 Mbyte address map that can be accessed with 23 address bits. This provides an alternative way to access all of the various pages of FLASH, RAM and EEE as well as additional external memory.

The BDM global page index register (BDMGPR) is used only in the case the CPU is executing a firmware command which uses a global instruction (like GLDD, GSTD) or by a BDM hardware command (like WRITE\_W, WRITE\_BYTE, READ\_W, READ\_BYTE). See the BDM Block Guide for further details.

The generated global address is a result of concatenation of the BDM local address with the BDMGPR register [22:16] in the case of a hardware command or concatenation of the CPU local address and the BDMGPR register [22:16] in the case of a firmware command (see Figure 3-18).

## 3.4.2.3 Implemented Memory Map

The global memory spaces reserved for the internal resources (RAM, EEE, and FLASH) are not determined by the MMC module. Size of the individual internal resources are however fixed in the design of the device cannot be changed by the user. Please refer to the Device User Guide for further details. Figure 3-19 and Table 3-17 show the memory spaces occupied by the on-chip resources. Please note that the memory spaces have fixed top addresses.

| Internal Resource \$Address                              |  |  |  |  |

|----------------------------------------------------------|--|--|--|--|

| RAM RAM_LOW = 0x10_0000 minus RAMSIZE <sup>(1)</sup>     |  |  |  |  |

| FLASH FLASH_LOW = 0x80_0000 minus FLAS                   |  |  |  |  |

| 1. RAMSIZE is the hexadecimal value of RAM SIZE in bytes |  |  |  |  |

| Table 3-17. Global Implemented Memory Space | Table 3-17. | Global | Implemented | Memory | Space |

|---------------------------------------------|-------------|--------|-------------|--------|-------|

|---------------------------------------------|-------------|--------|-------------|--------|-------|

2. FLASHSIZE is the hexadecimal value of FLASH SIZE in bytes

When the device is operating in expanded modes except emulation single-chip mode, accesses to global addresses which are not occupied by the on-chip resources (unimplemented areas or external memory space) result in accesses to the external bus (see Figure 3-19).

# 5.1.1 Glossary or Terms

| bus clock         | System Clock. Refer to CRG Block Guide.                                                            |

|-------------------|----------------------------------------------------------------------------------------------------|

| expanded modes    | Normal Expanded Mode<br>Emulation Single-Chip Mode<br>Emulation Expanded Mode<br>Special Test Mode |

| single-chip modes | Normal Single-Chip Mode<br>Special Single-Chip Mode                                                |

| emulation modes   | Emulation Single-Chip Mode<br>Emulation Expanded Mode                                              |

| normal modes      | Normal Single-Chip Mode<br>Normal Expanded Mode                                                    |

| special modes     | Special Single-Chip Mode<br>Special Test Mode                                                      |

| NS                | Normal Single-Chip Mode                                                                            |

| SS                | Special Single-Chip Mode                                                                           |

| NX                | Normal Expanded Mode                                                                               |

| ES                | Emulation Single-Chip Mode                                                                         |

| EX                | Emulation Expanded Mode                                                                            |

| ST                | Special Test Mode                                                                                  |

| external resource | Addresses outside MCU                                                                              |

| PRR               | Port Replacement Registers                                                                         |

| PRU               | Port Replacement Unit                                                                              |

| EMULMEM           | External emulation memory                                                                          |

| access source     | CPU or BDM or XGATE                                                                                |

# 5.1.2 Features

The XEBI includes the following features:

- Output of up to 23-bit address bus and control signals to be used with a non-muxed external bus

- Bidirectional 16-bit external data bus with option to disable upper half

- Visibility of internal bus activity

# 5.1.3 Modes of Operation

• Single-chip modes

The external bus interface is not available in these modes.

• Expanded modes

Address, data, and control signals are activated on the external bus in normal expanded mode and special test mode.

• Emulation modes

The external bus is activated to interface to an external tool for emulation of normal expanded mode or normal single-chip mode applications.

# 8.3.2 Register Descriptions

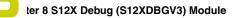

This section consists of the S12XDBG control and trace buffer register descriptions in address order. Each comparator has a bank of registers that are visible through an 8-byte window between 0x0028 and 0x002F in the S12XDBG module register address map. When ARM is set in DBGC1, the only bits in the S12XDBG module registers that can be written are ARM, TRIG, and COMRV[1:0].

# 8.3.2.1 Debug Control Register 1 (DBGC1)

Address: 0x0020

Figure 8-3. Debug Control Register (DBGC1)

Read: Anytime

Write: Bits 7, 1, 0 anytime

Bit 6 can be written anytime but always reads back as 0. Bits 5:2 anytime S12XDBG is not armed.

#### NOTE

If a write access to DBGC1 with the ARM bit position set occurs simultaneously to a hardware disarm from an internal trigger event, then the ARM bit is cleared due to the hardware disarm.

#### NOTE

When disarming the S12XDBG by clearing ARM with software, the contents of bits[5:2] are not affected by the write, since up until the write operation, ARM = 1 preventing these bits from being written. These bits must be cleared using a second write if required.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ARM  | <ul> <li>Arm Bit — The ARM bit controls whether the S12XDBG module is armed. This bit can be set and cleared by user software and is automatically cleared on completion of a tracing session, or if a breakpoint is generated with tracing not enabled. On setting this bit the state sequencer enters State1.</li> <li>0 Debugger disarmed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>TRIG | Immediate Trigger Request Bit — This bit when written to 1 requests an immediate trigger independent of comparator or external tag signal status. When tracing is complete a forced breakpoint may be generated depending upon DBGBRK and BDM bit settings. This bit always reads back a 0. Writing a 0 to this bit has no effect. If TSOURCE are clear no tracing is carried out. If tracing has already commenced using BEGIN- or MID trigger alignment, it continues until the end of the tracing session as defined by the TALIGN bit settings, thus TRIG has no affect. In secure mode tracing is disabled and writing to this bit has no effect. 0 Do not trigger until the state sequencer enters the Final State. 1 Trigger immediately . |

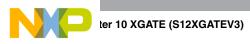

The programmer's model of the XGATE RISC core is shown in Figure 10-22. The processor offers a set of seven general purpose registers (R1 - R7), which serve as accumulators and index registers. An additional eighth register (R0) is tied to the value "\$0000". Registers R1 and R7 have additional functionality. R1 is preloaded with the initial data pointer of the channel's service request vector (see Figure 10-23). R7 is either preloaded with the content of XGISP74 if the interrupt priority of the current channel is in the range 7 to 4, or it is with preloaded the content of XGISP31 if the interrupt priority of the current channel is in the range 3 to 1. The remaining general purpose registers will be reset to an unspecified value at the beginning of each thread.

The 16 bit program counter allows the addressing of a 64 kbyte address space.

The condition code register contains four bits: the sign bit (S), the zero flag (Z), the overflow flag (V), and the carry bit (C). The initial content of the condition code register is undefined.

# 10.4.3 Memory Map

The XGATE's RISC core is able to access an address space of 64K bytes. The allocation of memory blocks within this address space is determined on chip level. Refer to the **S12X\_MMC Section** for a detailed information.

The XGATE vector block assigns a start address and a data pointer to each XGATE channel. Its position in the XGATE memory map can be adjusted through the XGVBR register (see Section 10.3.1.7, "XGATE Vector Base Address Register (XGVBR)"). Figure 10-23 shows the layout of the vector block. Each vector consists of two 16 bit words. The first contains the start address of the service routine. This value will be loaded into the program counter before a service routine is executed. The second word is a pointer to the service routine's data space. This value will be loaded into register R1 before a service routine is executed.

# Arithmetic Shift Right

#### Operation

#### n = RS or IMM4

Shifts the bits in register RD *n* positions to the right. The higher *n* bits of the register RD become filled with the sign bit (RD[15]). The carry flag will be updated to the bit contained in RD[n-1] before the shift for n > 0.

*n* can range from 0 to 16.

In immediate address mode, *n* is determined by the operand IMM4. *n* is considered to be 16 if IMM4 is equal to 0.

In dyadic address mode, *n* is determined by the content of RS. *n* is considered to be 16 if the content of RS is greater than 15.

#### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | Δ | Δ |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: Set if a two's complement overflow resulted from the operation; cleared otherwise.  $RD[15]_{old} \wedge RD[15]_{new}$

- C: Set if n > 0 and RD[n-1] = 1; if n = 0 unaffected.

#### Code and CPU Cycles

| Source Form   | Address<br>Mode |   | Machine Code |   |   |   |    |      | Cycles |   |   |   |   |   |

|---------------|-----------------|---|--------------|---|---|---|----|------|--------|---|---|---|---|---|

| ASR RD, #IMM4 | IMM4            | 0 | 0            | 0 | 0 | 1 | RD | IMM4 |        | 1 | 0 | 0 | 1 | Р |

| ASR RD, RS    | DYA             | 0 | 0            | 0 | 0 | 1 | RD | RS   | 1      | 0 | 0 | 0 | 1 | Р |

# CMP

Compare

#### Operation

$\begin{array}{ll} RS1 - RS2 & \Rightarrow NONE \mbox{ (translates to SUB R0, RS1, RS2)} \\ RD - IMM16 & \Rightarrow NONE \mbox{ (translates to CMPL RD, #IMM16[7:0]; CPCH RD, #IMM16[15:8])} \end{array}$

Subtracts two 16 bit values and discards the result.

#### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | Δ | Δ |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: Set if a two's complement overflow resulted from the operation; cleared otherwise. RS1[15] & RS2[15] & result[15] | RS1[15] & RS2[15] & result[15] RD[15] & IMM16[15] & result[15] | RD[15] & IMM16[15] & result[15]

- C: Set if there is a carry from the bit 15 of the result; cleared otherwise. RS1[15] & RS2[15] | RS1[15] & result[15] | RS2[15] & result[15] RD[15] & IMM16[15] | RD[15] & result[15] | IMM16[15] & result[15]

## Code and CPU Cycles

| Source Form    | Address<br>Mode |   | Machine Code |   |   |   |                | Cycles |   |            |     |   |   |   |

|----------------|-----------------|---|--------------|---|---|---|----------------|--------|---|------------|-----|---|---|---|

| CMP RS1, RS2   | TRI             | 0 | 0            | 0 | 1 | 1 | 0              | 0      | 0 | RS1        | RS2 | 0 | 0 | Р |

| CMP RS, #IMM16 | IMM8            | 1 | 1            | 0 | 1 | 0 |                | RS     |   | IMM16[7:0] |     | Р |   |   |

|                | IMM8            | 1 | 1            | 0 | 1 | 1 | RS IMM16[15:8] |        | Р |            |     |   |   |   |

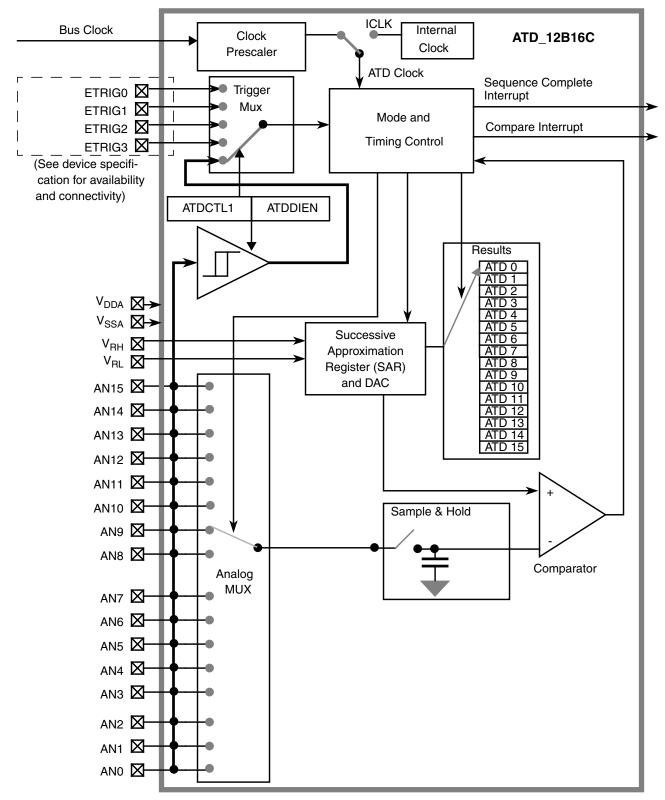

# 13.1.3 Block Diagram

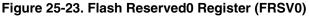

Offset Module Base + 0x0011

All bits in the FRSV0 register read 0 and are not writable.

## 25.3.2.16 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Figure 25-24. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

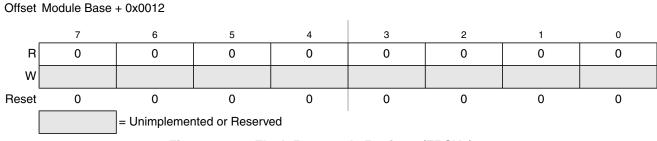

# 25.3.2.17 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

All bits in the FRSV2 register read 0 and are not writable.

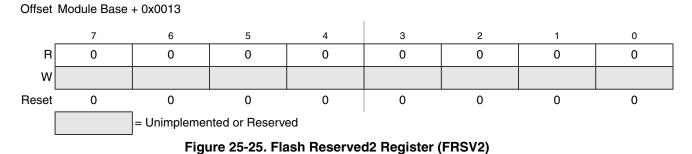

Figure 27-4. FTM512K3 Register Summary (continued)

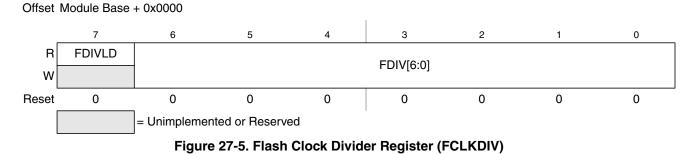

# 27.3.2.1 Flash Clock Divider Register (FCLKDIV)

The FCLKDIV register is used to control timed events in program and erase algorithms.

All bits in the FCLKDIV register are readable, bits 6–0 are write once and bit 7 is not writable.

#### Table 27-8. FCLKDIV Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                                                                                                                             |

| 6–0<br>FDIV[6:0] | <b>Clock Divider Bits</b> — FDIV[6:0] must be set to effectively divide OSCCLK down to generate an internal Flash clock, FCLK, with a target frequency of 1 MHz for use by the Flash module to control timed events during program and erase algorithms. Table 27-9 shows recommended values for FDIV[6:0] based on OSCCLK frequency. Please refer to Section 27.4.1, "Flash Command Operations," for more information. |

#### CAUTION

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0). The FCLKDIV register is writable during the Flash reset sequence even though CCIF is clear.

The Full Partition D-Flash command (see Section 28.4.2.15) is used to program the EEE nonvolatile information register fields where address  $0x12_0000$  defines the D-Flash partition for user access and address  $0x12_0004$  defines the buffer RAM partition for EEE operations.

| Global Address<br>(EEEIFRON) | Size<br>(Bytes) | Description                                                                                       |

|------------------------------|-----------------|---------------------------------------------------------------------------------------------------|

| 0x12_0000 - 0x12_0001        | 2               | D-Flash User Partition (DFPART)<br>Refer to Section 28.4.2.15, "Full Partition D-Flash Command"   |

| 0x12_0002 - 0x12_0003        | 2               | D-Flash User Partition (duplicate <sup>(1)</sup> )                                                |

| 0x12_0004 - 0x12_0005        | 2               | Buffer RAM EEE Partition (ERPART)<br>Refer to Section 28.4.2.15, "Full Partition D-Flash Command" |

| 0x12_0006 - 0x12_0007        | 2               | Buffer RAM EEE Partition (duplicate <sup>1</sup> )                                                |

| 0x12_0008 - 0x12_007F        | 120             | Reserved                                                                                          |

Table 28-7. EEE Nonvolatile Information Register Fields

1. Duplicate value used if primary value generates a double bit fault when read during the reset sequence.

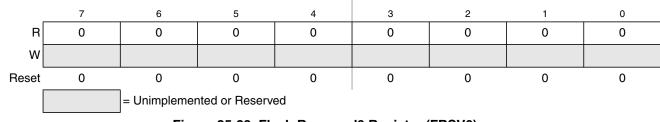

# 28.3.2 Register Descriptions

The Flash module contains a set of 20 control and status registers located between Flash module base + 0x0000 and 0x0013. A summary of the Flash module registers is given in Figure 28-4 with detailed descriptions in the following subsections.

#### CAUTION

Writes to any Flash register must be avoided while a Flash command is active (CCIF=0) to prevent corruption of Flash register contents and Memory Controller behavior.

| Address<br>& Name |        | 7      | 6      | 5     | 4     | 3     | 2       | 1       | 0       |

|-------------------|--------|--------|--------|-------|-------|-------|---------|---------|---------|

| 0x0000<br>FCLKDIV | R<br>W | FDIVLD | FDIV6  | FDIV5 | FDIV4 | FDIV3 | FDIV2   | FDIV1   | FDIV0   |

| 0x0001<br>FSEC    | R<br>W | KEYEN1 | KEYEN0 | RNV5  | RNV4  | RNV3  | RNV2    | SEC1    | SEC0    |

| 0x0002<br>FCCOBIX | R<br>W | 0      | 0      | 0     | 0     | 0     | CCOBIX2 | CCOBIX1 | CCOBIX0 |

| 0x0003<br>FECCRIX | R<br>W | 0      | 0      | 0     | 0     | 0     | ECCRIX2 | ECCRIX1 | ECCRIX0 |

| 0x0004<br>FCNFG   | R<br>W | CCIE   | 0      | 0     | IGNSF | 0     | 0       | FDFD    | FSFD    |

Figure 28-4. FTM768K4 Register Summary

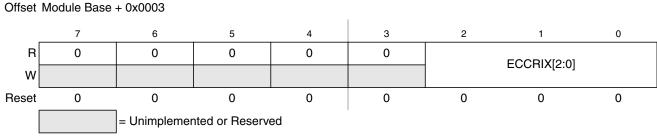

#### Table 28-14. FECCRIX Field Descriptions

| Field | Description                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>ECC Error Register Index</b> — The ECCRIX bits are used to select which word of the FECCR register array is being read. See Section 28.3.2.13, "Flash ECC Error Results Register (FECCR)," for more details. |

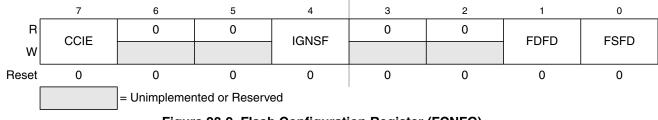

# 28.3.2.5 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU or XGATE.

Offset Module Base + 0x0004

Figure 28-9. Flash Configuration Register (FCNFG)

CCIE, IGNSF, FDFD, and FSFD bits are readable and writable while remaining bits read 0 and are not writable.

| Field      | Description                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIE  | <ul> <li>Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.</li> <li>0 Command complete interrupt disabled</li> <li>1 An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 28.3.2.7)</li> </ul>                                               |

| 4<br>IGNSF | <ul> <li>Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 28.3.2.8).</li> <li>0 All single bit faults detected during array reads are reported</li> <li>1 Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated</li> </ul> |

| Register | Error Bit | Error Condition                                                |

|----------|-----------|----------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 000 at command launch                    |

|          | ACCERR    | Set if a Load Data Field command sequence is currently active  |

| FSTAT    |           | Set if command not available in current mode (see Table 28-30) |

| FSTAI    | FPVIOL    | None                                                           |

|          | MGSTAT1   | None                                                           |

|          | MGSTAT0   | None                                                           |

| FERSTAT  | EPVIOLIF  | None                                                           |

Table 28-76. EEPROM Emulation Query Command Error Handling

## 28.4.2.22 Partition D-Flash Command

The Partition D-Flash command allows the user to allocate sectors within the D-Flash block for applications and a partition within the buffer RAM for EEPROM access. The D-Flash block consists of 128 sectors with 256 bytes per sector. The Erase All Blocks command must be run prior to launching the Partition D-Flash command.

Table 28-77. Partition D-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                   |              |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------|--------------|--|--|--|--|--|--|

| 000         | 0x20                                                               | Not required |  |  |  |  |  |  |

| 001         | Number of 256 byte sectors for the D-Flash user partition (DFPART) |              |  |  |  |  |  |  |

| 010         | Number of 256 byte sectors for buffer RAM EEE partition (ERPART)   |              |  |  |  |  |  |  |

Upon clearing CCIF to launch the Partition D-Flash command, the following actions are taken to define a partition within the D-Flash block for direct access (DFPART) and a partition within the buffer RAM for EEE use (ERPART):

- Validate the DFPART and ERPART values provided:

- DFPART <= 128 (maximum number of 256 byte sectors in D-Flash block)

- ERPART <= 16 (maximum number of 256 byte sectors in buffer RAM)

- If ERPART > 0, 128 DFPART >= 12 (minimum number of 256 byte sectors in the D-Flash block required to support EEE)

- If ERPART > 0, ((128-DFPART)/ERPART) >= 8 (minimum ratio of D-Flash EEE space to buffer RAM EEE space to support EEE)

- Erase verify the D-Flash block and the EEE nonvolatile information register

- Program DFPART to the EEE nonvolatile information register at global address 0x12\_0000 (see Table 28-7)

**Command Write Sequence** — An MCU instruction sequence to execute built-in algorithms (including program and erase) on the Flash memory.

**D-Flash Memory** — The D-Flash memory constitutes the nonvolatile memory store required for EEE. Memory space in the D-Flash memory not required for EEE can be partitioned to provide nonvolatile memory space for applications.

**D-Flash Sector** — The D-Flash sector is the smallest portion of the D-Flash memory that can be erased. The D-Flash sector consists of four 64 byte rows for a total of 256 bytes.

**EEE (Emulated EEPROM)** — A method to emulate the small sector size features and endurance characteristics associated with an EEPROM.

**EEE IFR** — Nonvolatile information register located in the D-Flash block that contains data required to partition the D-Flash memory and buffer RAM for EEE. The EEE IFR is visible in the global memory map by setting the EEEIFRON bit in the MMCCTL1 register.

**NVM Command Mode** — An NVM mode using the CPU to setup the FCCOB register to pass parameters required for Flash command execution.

**Phrase** — An aligned group of four 16-bit words within the P-Flash memory. Each phrase includes eight ECC bits for single bit fault correction and double bit fault detection within the phrase.

P-Flash Memory — The P-Flash memory constitutes the main nonvolatile memory store for applications.

**P-Flash Sector** — The P-Flash sector is the smallest portion of the P-Flash memory that can be erased. Each P-Flash sector contains 1024 bytes.

**Program IFR** — Nonvolatile information register located in the P-Flash block that contains the Device ID, Version ID, and the Program Once field. The Program IFR is visible in the global memory map by setting the PGMIFRON bit in the MMCCTL1 register.

# 29.1.2 Features

## 29.1.2.1 P-Flash Features

- 1024 Kbytes of P-Flash memory composed of three 256 Kbyte Flash blocks and two 128 Kbyte Flash blocks. The 256 Kbyte Flash block consists of two 128 Kbyte sections each divided into 128 sectors of 1024 bytes. The 128 Kbyte Flash blocks are each divided into 128 sectors of 1024 bytes.

- Single bit fault correction and double bit fault detection within a 64-bit phrase during read operations

- Automated program and erase algorithm with verify and generation of ECC parity bits

- Fast sector erase and phrase program operation

- Ability to program up to one phrase in each P-Flash block simultaneously

- Flexible protection scheme to prevent accidental program or erase of P-Flash memory

| SEC[1:0] | Status of Security     |

|----------|------------------------|

| 00       | SECURED                |

| 01       | SECURED <sup>(1)</sup> |

| 10       | UNSECURED              |

| 11       | SECURED                |

Table 29-12. Flash Security States

1. Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 29.5.

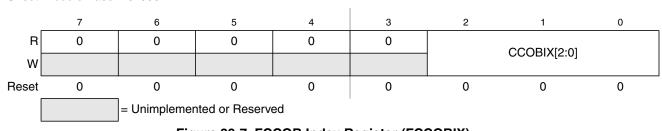

# 29.3.2.3 Flash CCOB Index Register (FCCOBIX)

Offset Module Base + 0x0002

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Figure 29-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

Table 29-13. FCCOBIX Field Descriptions

| Field              | Description                                                                                                                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See Section 29.3.2.11, "Flash Common Command Object Register (FCCOB)," for more details. |

# 29.3.2.4 Flash ECCR Index Register (FECCRIX)

The FECCRIX register is used to index the FECCR register for ECC fault reporting.

#### Figure 29-8. FECCR Index Register (FECCRIX)

ECCRIX bits are readable and writable while remaining bits read 0 and are not writable.

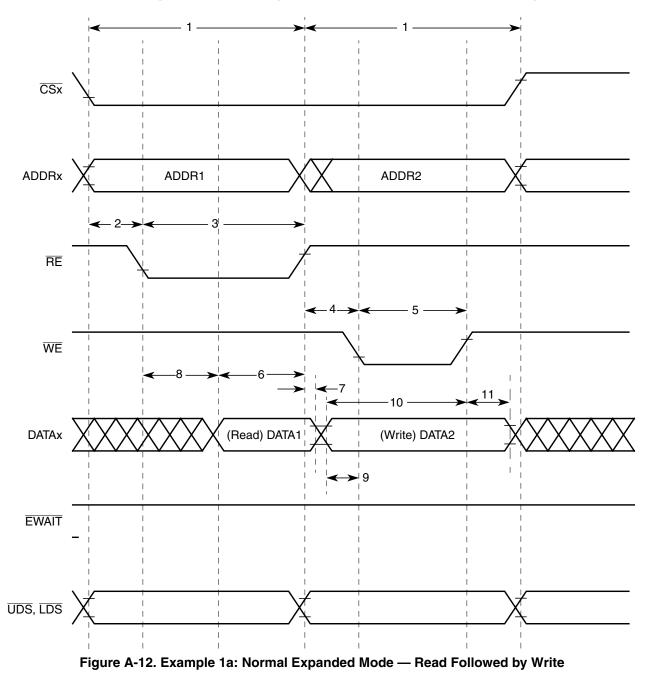

# A.7.3 External Bus Timing

The following conditions are assumed for all following external bus timing values:

- Crystal input within 45% to 55% duty

- Equal 25 pF load on all pins

- Pad full drive (reduced drive must be off)

#### A.7.3.1 Normal Expanded Mode (External Wait Feature Disabled)