Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | HCS12X                                                                   |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 50MHz                                                                    |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                        |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 59                                                                       |

| Program Memory Size        | 256КВ (256К х 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 16K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                             |

| Data Converters            | A/D 8x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 80-QFP                                                                   |

| Supplier Device Package    | 80-QFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xet256j2maar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 1-3 shows XGATE local address translation to the global memory map. It indicates also the location of used internal resources in the memory map.

| Internal Resource | Size /KByte        | \$Address                |

|-------------------|--------------------|--------------------------|

| XGATE RAM 32K     |                    | XGRAM_LOW = 0x0F_8000    |

| FLASH             | 30K <sup>(1)</sup> | XGFLASH_HIGH = 0x78_8000 |

Table 1-3. XGATE Resources

1. This value is calculated by the following formula: (64K -2K- XGRAMSIZE)

| Device                                | FLASH_LOW                | PPAGE | RAM_LOW   | RPAGE | EE_LOW    | EPAGE                |

|---------------------------------------|--------------------------|-------|-----------|-------|-----------|----------------------|

| 9S12XEP100                            | 0x70_0000                | 64    | 0x0F_0000 | 16    | 0x13_F000 | $4^{(3)} + 32^{(4)}$ |

| 9S12XEP768                            | 0x74_0000                | 48    | 0x0F_4000 | 12    | 0x13_F000 | 4 + 32               |

| 9S12XEQ512                            | 0x78_0000                | 32    | 0x0F_8000 | 8     | 0x13_F000 | 4 + 32               |

| 9S12XEx384                            | 0x78_0000 <sup>(5)</sup> | 24    | 0x0F_A000 | 6     | 0x13_F000 | 4 + 32               |

| 9S12XET256<br>9S12XEA256<br>(6)       | 0x78_0000 <sup>(7)</sup> | 16    | 0x0F_C000 | 4     | 0x13_F000 | 4 + 32               |

| 9S12XEG128<br>9S12XEA128 <sup>6</sup> | 0x78_0000 <sup>(8)</sup> | 8     | 0x0F_D000 | 3     | 0x13_F800 | 2 + 32               |

#### Table 1-4. Derivative Dependent Memory Parameters

1. Number of 16K pages addressable via PPAGE register

2. Number of 4K pages addressing the RAM. RAM can also be mapped to 0x4000 - 0x7FFF

3. Number of 1K pages addressing the Cache RAM via the EPAGE register counting downwards from 0xFF

4. Number of 1K pages addressing the Data flash via the EPAGE register starting upwards from 0x00

5. The 384K memory map is split into a 128K block from 0x78\_0000 to 0x79\_FFFF and a 256K block from 0x7C\_0000 to 0x7F\_FFFF

6. The 9S12XEA devices are a special bondout for access to extra ADC channels in 80QFP. Available in 80QFP only. WARNING: NOT PIN-COMPATIBLE WITH REST OF FAMILY.

7. The 256K memory map is split into a 128K block from 0x78\_0000 to 0x79\_FFFF and a 128K block from 0x7E\_0000 to 0x7F\_FFFF

8. The 128K memory map is split into a 64K block from 0x78\_0000 to 0x78\_FFFF and a 64K block from 0x7F\_0000 to 0x7F\_FFFF

| Device     | 0x70_0000 | 0x74_0000 | 0x78_0000 | 0x7A_0000 | 0x7C_0000 | 0x7E_0000 |  |

|------------|-----------|-----------|-----------|-----------|-----------|-----------|--|

| 9S12XEP100 | B3        | B2        | B1S       | B1N       | B0        |           |  |

| 9S12XEP768 | _         | B2        | B1S       | B1N       | B0        |           |  |

| 9S12XEQ512 | _         | _         | B1S       | B1N       | B0        |           |  |

| 9S12XEx384 | _         | _         | B1S       | _         | В         | 0         |  |

| Table 1-5. Derivative | Dependent Flash | Block Mapping |

|-----------------------|-----------------|---------------|

|-----------------------|-----------------|---------------|

|         | 9    | 5    | 42   | 13   | 4    | 0    | -    | 2    | <i>m</i> | 4    | 10   | 6    | ~    |      | _    | 2    |                  |    |            |            |            |            |     |

|---------|------|------|------|------|------|------|------|------|----------|------|------|------|------|------|------|------|------------------|----|------------|------------|------------|------------|-----|

|         | CANO | CAN1 | CAN2 | CAN3 | CAN4 | SCIO | SCI1 | SCI2 | SC13     | SCI4 | SCI5 | SCI6 | SCI7 | SP10 | SPI1 | SPI2 | E<br>I<br>C<br>0 | l⊡ | <u>cso</u> | <u>CS1</u> | <u>CS2</u> | <u>CS3</u> | TIM |

| PF[0]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    | Х          |            |            |            |     |

| PF[1]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            | Х          |            |            |     |

| PF[2]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            | Х          |            |     |

| PF[3]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            | Х          |     |

| PF[5:4] |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      | Х                |    |            |            |            |            |     |

| PF[7:6] |      |      |      |      |      |      |      |      | Х        |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PH[1:0] |      |      |      |      |      |      |      |      |          |      |      | 0    |      |      | Х    |      |                  |    |            |            |            |            |     |

| PH[3:2] |      |      |      |      |      |      |      |      |          |      |      |      | 0    |      | Х    |      |                  |    |            |            |            |            |     |

| PH[5:4] |      |      |      |      |      |      |      |      |          | 0    |      |      |      |      |      | Х    |                  |    |            |            |            |            |     |

| PH[7:6] |      |      |      |      |      |      |      |      |          |      | 0    |      |      |      |      | Х    |                  |    |            |            |            |            |     |

| PJ[0]   |      |      |      |      |      |      |      | 0    |          |      |      |      |      |      |      |      |                  |    |            |            |            | 0          |     |

| PJ[1]   |      |      |      |      |      |      |      | 0    |          |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PJ[2]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            | 0          |            |            |     |

| PJ[3]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PJ[4]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  | 0  | 0          |            |            |            |     |

| PJ[5]   |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  | 0  |            |            | 0          |            |     |

| PJ[7:6] | X    |      |      |      | 0    |      |      |      |          |      |      |      |      |      |      |      | 0                |    |            |            |            |            |     |

| PL[1:0] |      |      |      |      |      |      |      |      |          | Х    |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PL[3:2] |      |      |      |      |      |      |      |      |          |      | Х    |      |      |      |      |      |                  |    |            |            |            |            |     |

| PL[5:4] |      |      |      |      |      |      |      |      |          |      |      | Х    |      |      |      |      |                  |    |            |            |            |            |     |

| PL[7:6] |      |      |      |      |      |      |      |      |          |      |      |      | Х    |      |      |      |                  |    |            |            |            |            |     |

| PM[1:0] | 0    |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PM[3:2] | X    | 0    |      |      |      |      |      |      |          |      |      |      |      | х    |      |      |                  |    |            |            |            |            |     |

| PM[5:4] | X    |      | 0    |      | х    |      |      |      |          |      |      |      |      | х    |      |      |                  |    |            |            |            |            |     |

| PM[7:6] |      |      |      | 0    | х    |      |      |      | 0        |      |      |      |      |      |      |      |                  |    |            |            |            |            |     |

| PP[3:0] |      |      |      |      |      |      |      |      |          |      |      |      |      |      | 0    |      |                  |    |            |            |            |            | Х   |

| PP[7:4] |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      | 0    |                  |    |            |            |            |            | х   |

| PR[7:0] |      |      |      |      |      |      |      |      |          |      |      |      |      |      |      |      |                  |    |            |            |            |            | 0   |

# Table 1-8. Peripheral - Port Routing Options<sup>(1)</sup>

## NOTE

Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read on PTT or PTIT registers, when changing the DDRT register.

# 2.3.24 Port T Reduced Drive Register (RDRT)

Access: User read/write<sup>(1)</sup> Address 0x0243 5 2 7 6 4 3 0 1 R RDRT7 RDRT6 RDRT5 RDRT4 RDRT3 RDRT2 RDRT0 RDRT1 W 0 0 0 0 0 Reset 0 0 0

Figure 2-22. Port T Reduced Drive Register (RDRT)

1. Read: Anytime. Write: Anytime.

#### Table 2-23. RDRT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>RDRT | <ul> <li>Port T reduced drive—Select reduced drive for outputs</li> <li>This register configures the drive strength of output pins 7 through 0 as either full or reduced independent of the function used on the pins. If a pin is used as input this bit has no effect.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength).</li> <li>0 Full drive strength enabled.</li> </ul> |

# 2.3.25 Port T Pull Device Enable Register (PERT)

Address 0x0244

Access: User read/write<sup>(1)</sup>

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | PERT7 | PERT6 | PERT5 | PERT4 | PERT3 | PERT2 | PERT1 | PERT0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 2-23. Port T Pull Device Enable Register (PERT)

1. Read: Anytime. Write: Anytime.

#### Table 2-24. PERT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PERT | <ul> <li>Port T pull device enable—Enable pull devices on input pins</li> <li>These bits configure whether a pull device is activated, if the associated pin is used as an input. This bit has no effect if the pin is used as an output. Out of reset no pull device is enabled.</li> <li>1 Pull device enabled.</li> <li>0 Pull device disabled.</li> </ul> |

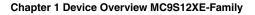

# 2.3.87 Port R Data Direction Register (DDRR)

1. Read: Anytime. Write: Anytime.

#### Table 2-83. DDRR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>DDRR | Port R data direction—         This register controls the data direction of pins 7 through 0.         The TIM forces the I/O state to be an output for each timer port associated with an enabled output compare. In this case the data direction bits will not change.         The data direction bits revert to controlling the I/O direction of a pin when the associated timer output compare is disabled.         The timer Input Capture always monitors the state of the pin.         1 Associated pin is configured as output.         0 Associated pin is configured as high-impedance input. |

#### NOTE

Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read on PTR or PTIR registers, when changing the DDRR register.

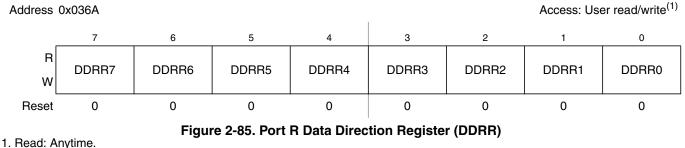

## 2.3.88 Port R Reduced Drive Register (RDRR)

1. Read: Anytime. Write: Anytime.

#### Table 2-86. PPSR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PPSR | <ul> <li>Port R pull device select—Determine pull device polarity on input pins</li> <li>This register selects whether a pull-down or a pull-up device is connected to the pin.</li> <li>1 A pull-down device is connected to the associated pin, if enabled and if the pin is used as input.</li> <li>0 A pull-up device is connected to the associated pin, if enabled and if the pin is used as input.</li> </ul> |

# 2.3.91 PIM Reserved Register

| Address | Address 0x036E Access: User read <sup>(1)</sup> |   |            |              |              |   |   |   |  |  |  |  |

|---------|-------------------------------------------------|---|------------|--------------|--------------|---|---|---|--|--|--|--|

|         | 7                                               | 6 | 5          | 4            | 3            | 2 | 1 | 0 |  |  |  |  |

| R       | 0                                               | 0 | 0          | 0            | 0            | 0 | 0 | 0 |  |  |  |  |

| w       |                                                 |   |            |              |              |   |   |   |  |  |  |  |

| Reset   | 0                                               | 0 | 0          | 0            | 0            | 0 | 0 | 0 |  |  |  |  |

| [       | = Unimplemented or Reserved                     |   |            |              |              |   |   |   |  |  |  |  |

|         |                                                 |   | Figure 2-8 | 39. PIM Rese | rved Registe | r |   |   |  |  |  |  |

1. Read: Always reads 0x00 Write: Unimplemented

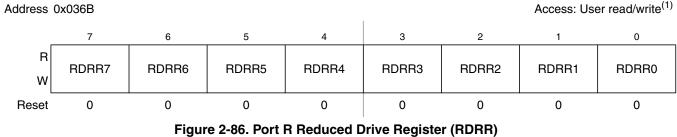

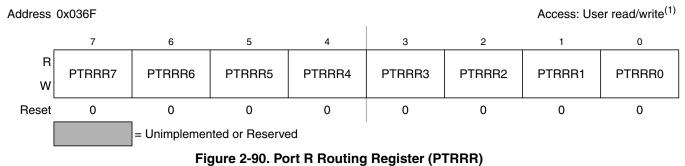

# 2.3.92 Port R Routing Register (PTRRR)

1. Read: Anytime. Write: Anytime.

#### Table 2-87. PTR Routing Register Field Descriptions

| Field      | Description                                                                                                                                                 |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>PTRRR | Port R routing—<br>This register configures the re-routing of the associated TIM channel.<br>1 TIMIOC7 is available on PP7<br>0 TIMIOC7 is available on PR7 |  |  |  |  |

| 6<br>PTRRR | Port R routing—<br>This register configures the re-routing of the associated TIM channel.<br>1 TIMIOC6 is available on PP6<br>0 TIMIOC6 is available on PR6 |  |  |  |  |

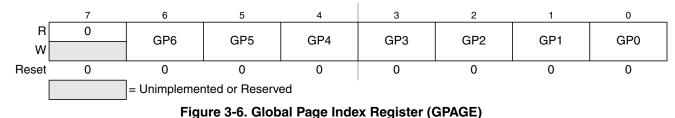

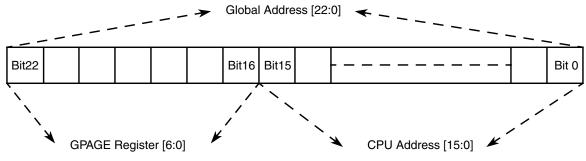

## 3.3.2.3 Global Page Index Register (GPAGE)

Address: 0x0010

#### Read: Anytime

Write: Anytime

The global page index register is used to construct a 23 bit address in the global map format. It is only used when the CPU is executing a global instruction (GLDAA, GLDAB, GLDD, GLDS, GLDX, GLDY,GSTAA, GSTAB, GSTD, GSTS, GSTX, GSTY) (see CPU Block Guide). The generated global address is the result of concatenation of the CPU local address [15:0] with the GPAGE register [22:16] (see Figure 3-7).

#### CAUTION

XGATE write access to this register during an CPU access which makes use of this register could lead to unexpected results.

Figure 3-7. GPAGE Address Mapping

#### Table 3-9. GPAGE Field Descriptions

| Field          | Description                                                                                                                        |

|----------------|------------------------------------------------------------------------------------------------------------------------------------|

| 6–0<br>GP[6:0] | <b>Global Page Index Bits 6–0</b> — These page index bits are used to select which of the 128 64-kilobyte pages is to be accessed. |

#### Example 3-1. This example demonstrates usage of the GPAGE register

| LDX   | #0x5000      | ;Set GPAGE offset to the value of 0x5000          |

|-------|--------------|---------------------------------------------------|

| MOVB  | #0x14, GPAGE | ;Initialize GPAGE register with the value of 0x14 |

| GLDAA | Х            | ;Load Accu A from the global address 0x14_5000    |

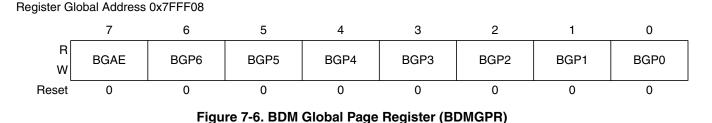

# 7.3.2.4 BDM Global Page Index Register (BDMGPR)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>BGAE       | <ul> <li>BDM Global Page Access Enable Bit — BGAE enables global page access for BDM hardware and firmware read/write instructions The BDM hardware commands used to access the BDM registers (READ_BD_ and WRITE_BD_) can not be used for global accesses even if the BGAE bit is set.</li> <li>0 BDM Global Access disabled</li> <li>1 BDM Global Access enabled</li> </ul> |  |  |  |  |

| 6–0<br>BGP[6:0] | <b>BDM Global Page Index Bits 6–0</b> — These bits define the extended address bits from 22 to 16. For more detailed information regarding the global page window scheme, please refer to the S12X_MMC Block Guide.                                                                                                                                                           |  |  |  |  |

# 7.3.3 Family ID Assignment

The family ID is a 8-bit value located in the firmware ROM (at global address: 0x7FFF0F). The read-only value is a unique family ID which is 0xC1 for S12X devices.

# 7.4 Functional Description

The BDM receives and executes commands from a host via a single wire serial interface. There are two types of BDM commands: hardware and firmware commands.

Hardware commands are used to read and write target system memory locations and to enter active background debug mode, see Section 7.4.3, "BDM Hardware Commands". Target system memory includes all memory that is accessible by the CPU.

Firmware commands are used to read and write CPU resources and to exit from active background debug mode, see Section 7.4.4, "Standard BDM Firmware Commands". The CPU resources referred to are the accumulator (D), X index register (X), Y index register (Y), stack pointer (SP), and program counter (PC).

Hardware commands can be executed at any time and in any mode excluding a few exceptions as highlighted (see Section 7.4.3, "BDM Hardware Commands") and in secure mode (see Section 7.4.1, "Security"). Firmware commands can only be executed when the system is not secure and is in active background debug mode (BDM).

#### Table 7-7. Firmware Commands

| Command <sup>(1)</sup>   | Opcode<br>(hex) | Data            | Description                                                                                                                                                      |

|--------------------------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ_NEXT <sup>(2)</sup> | 62              | 16-bit data out | Increment X index register by 2 ( $X = X + 2$ ), then read word X points to.                                                                                     |

| READ_PC                  | 63              | 16-bit data out | Read program counter.                                                                                                                                            |

| READ_D                   | 64              | 16-bit data out | Read D accumulator.                                                                                                                                              |

| READ_X                   | 65              | 16-bit data out | Read X index register.                                                                                                                                           |

| READ_Y                   | 66              | 16-bit data out | Read Y index register.                                                                                                                                           |

| READ_SP                  | 67              | 16-bit data out | Read stack pointer.                                                                                                                                              |

| WRITE_NEXT               | 42              | 16-bit data in  | Increment X index register by 2 (X = X + 2), then write word to location pointed to by X.                                                                        |

| WRITE_PC                 | 43              | 16-bit data in  | Write program counter.                                                                                                                                           |

| WRITE_D                  | 44              | 16-bit data in  | Write D accumulator.                                                                                                                                             |

| WRITE_X                  | 45              | 16-bit data in  | Write X index register.                                                                                                                                          |

| WRITE_Y                  | 46              | 16-bit data in  | Write Y index register.                                                                                                                                          |

| WRITE_SP                 | 47              | 16-bit data in  | Write stack pointer.                                                                                                                                             |

| GO                       | 08              | none            | Go to user program. If enabled, ACK will occur when leaving active background mode.                                                                              |

| GO_UNTIL <sup>(3)</sup>  | 0C              | none            | Go to user program. If enabled, ACK will occur upon returning to active background mode.                                                                         |

| TRACE1                   | 10              | none            | Execute one user instruction then return to active BDM. If enabled, ACK will occur upon returning to active background mode.                                     |

| TAGGO -> GO              | 18              | none            | (Previous enable tagging and go to user program.)<br>This command will be deprecated and should not be used anymore.<br>Opcode will be executed as a GO command. |

1. If enabled, ACK will occur when data is ready for transmission for all BDM READ commands and will occur after the write is complete for all BDM WRITE commands.

2. When the firmware command READ\_NEXT or WRITE\_NEXT is used to access the BDM address space the BDM resources are accessed rather than user code. Writing BDM firmware is not possible.

3. System stop disables the ACK function and ignored commands will not have an ACK-pulse (e.g., CPU in stop or wait mode). The GO\_UNTIL command will not get an Acknowledge if CPU executes the wait or stop instruction before the "UNTIL" condition (BDM active again) is reached (see Section 7.4.7, "Serial Interface Hardware Handshake Protocol" last Note).

## 7.4.5 BDM Command Structure

Hardware and firmware BDM commands start with an 8-bit opcode followed by a 16-bit address and/or a 16-bit data word depending on the command. All the read commands return 16 bits of data despite the byte or word implication in the command name.

8-bit reads return 16-bits of data, of which, only one byte will contain valid data. If reading an even address, the valid data will appear in the MSB. If reading an odd address, the valid data will appear in the LSB.

after a system stop mode the handshake feature must be enabled again by sending the ACK\_ENABLE command.

# 7.4.11 Serial Communication Time Out

The host initiates a host-to-target serial transmission by generating a falling edge on the BKGD pin. If BKGD is kept low for more than 128 target clock cycles, the target understands that a SYNC command was issued. In this case, the target will keep waiting for a rising edge on BKGD in order to answer the SYNC request pulse. If the rising edge is not detected, the target will keep waiting forever without any time-out limit.

Consider now the case where the host returns BKGD to logic one before 128 cycles. This is interpreted as a valid bit transmission, and not as a SYNC request. The target will keep waiting for another falling edge marking the start of a new bit. If, however, a new falling edge is not detected by the target within 512 clock cycles since the last falling edge, a time-out occurs and the current command is discarded without affecting memory or the operating mode of the MCU. This is referred to as a soft-reset.

If a read command is issued but the data is not retrieved within 512 serial clock cycles, a soft-reset will occur causing the command to be disregarded. The data is not available for retrieval after the time-out has occurred. This is the expected behavior if the handshake protocol is not enabled. However, consider the behavior where the BDM is running in a frequency much greater than the CPU frequency. In this case, the command could time out before the data is ready to be retrieved. In order to allow the data to be retrieved even with a large clock frequency mismatch (between BDM and CPU) when the hardware handshake protocol is enabled, the time out between a read command and the data retrieval is disabled. Therefore, the host could wait for more then 512 serial clock cycles and still be able to retrieve the data from an issued read command. However, once the handshake pulse (ACK pulse) is issued, the time-out feature is re-activated, meaning that the target will time out after 512 clock cycles. Therefore, the host needs to retrieve the data within a 512 serial clock cycles time frame after the ACK pulse had been issued. After that period, the read command is discarded and the data is no longer available for retrieval. Any negative edge in the BKGD pin after the time-out period is considered to be a new command or a SYNC request.

Note that whenever a partially issued command, or partially retrieved data, has occurred the time out in the serial communication is active. This means that if a time frame higher than 512 serial clock cycles is observed between two consecutive negative edges and the command being issued or data being retrieved is not complete, a soft-reset will occur causing the partially received command or data retrieved to be disregarded. The next negative edge in the BKGD pin, after a soft-reset has occurred, is considered by the target as the start of a new BDM command, or the start of a SYNC request pulse.

#### Table 10-7. XGISP74 Field Descriptions

| Field                 | Description                                                                                                                           |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 15–1<br>XBISP74[15:1] | <b>Initial Stack Pointer</b> — The XGISP74 register holds the initial value of RISC core register R7, for threads of priority 7 to 4. |  |  |  |  |  |

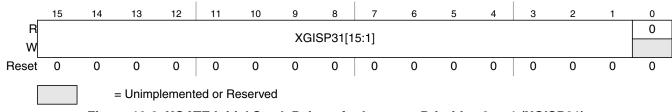

# 10.3.1.6 XGATE Initial Stack Pointer for Interrupt Priorities 3 to 1 (XGISP31)

The XGISP31 register is intended to point to the stack region that is used by XGATE channels of priority 3 to 1. Every time a thread of such priority is started, RISC core register R7 will be initialized with the content of XGISP31.

Read: Anytime

Write: Only if XGATE requests are disabled (XGE = 0) and idle (XGCHID = \$00))

#### Table 10-8. XGISP31 Field Descriptions

| Field | Description                                                                                                                           |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Initial Stack Pointer</b> — The XGISP31 register holds the initial value of RISC core register R7, for threads of priority 3 to 1. |

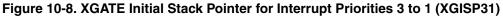

## 10.3.1.7 XGATE Vector Base Address Register (XGVBR)

The Vector Base Address Register (Figure 10-9) determines the location of the XGATE vector block (see Section Figure 10-23., "XGATE Vector Block).

Figure 10-9. XGATE Vector Base Address Register (XGVBR)

Read: Anytime

Write: Only if XGATE requests are disabled (XGE = 0) and idle (XGCHID = \$00))

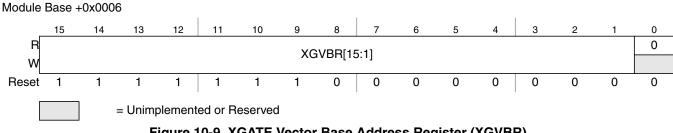

ter 13 Analog-to-Digital Converter (ADC12B16CV1)

| Address | Name    | Bit 7  | 6                                                                                                                               | 5           | 4       | 3                                  | 2       | 1 | Bit 0 |

|---------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------|-------------|---------|------------------------------------|---------|---|-------|

| 0x0024  | ATDDR10 | R<br>W | See Section 13.3.2.12.1, "Left Justified Result Data (DJM=0)"<br>and Section 13.3.2.12.2, "Right Justified Result Data (DJM=1)" |             |         |                                    |         |   |       |

| 0x0026  | ATDDR11 | R<br>W | See Section 13.3.2.12.1, "Left Justified Result Data (DJM=0)"<br>and Section 13.3.2.12.2, "Right Justified Result Data (DJM=1)" |             |         |                                    |         |   |       |

| 0x0028  | ATDDR12 | R<br>W | See Section 13.3.2.12.1, "Left Justified Result Data (DJM=0)"<br>and Section 13.3.2.12.2, "Right Justified Result Data (DJM=1)" |             |         |                                    |         |   |       |

| 0x002A  | ATDDR13 | R<br>W | See Section 13.3.2.12.1, "Left Justified Result Data (DJM=0)"<br>and Section 13.3.2.12.2, "Right Justified Result Data (DJM=1)" |             |         |                                    |         |   |       |

| 0x002C  | ATDDR14 | R<br>W |                                                                                                                                 |             | ,       | ft Justified Re<br>ht Justified Re | × *     | / |       |

| 0x002E  | ATDDR15 | R<br>W |                                                                                                                                 |             |         | ft Justified Re<br>ht Justified Re | · · · · | , |       |

|         |         |        | = Unimplem                                                                                                                      | ented or Re | eserved |                                    |         |   |       |

## 13.3.2 Register Descriptions

This section describes in address order all the ADC12B16C registers and their individual bits.

## 13.3.2.1 ATD Control Register 0 (ATDCTL0)

Writes to this register will abort current conversion sequence.

Module Base + 0x0000

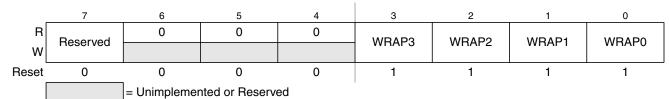

Figure 13-3. ATD Control Register 0 (ATDCTL0)

#### Read: Anytime

Write: Anytime, in special modes always write 0 to Reserved Bit 7.

#### Table 13-2. ATDCTL0 Field Descriptions

| Field            | Description                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                      |

| 3-0<br>WRAP[3-0] | Wrap Around Channel Select Bits — These bits determine the channel for wrap around when doing multi-<br>channel conversions. The coding is summarized in Table 13-3. |

#### Table 13-3. Multi-Channel Wrap Around Coding

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 0     | 0     | 0     | Reserved <sup>(1)</sup>                                                       |

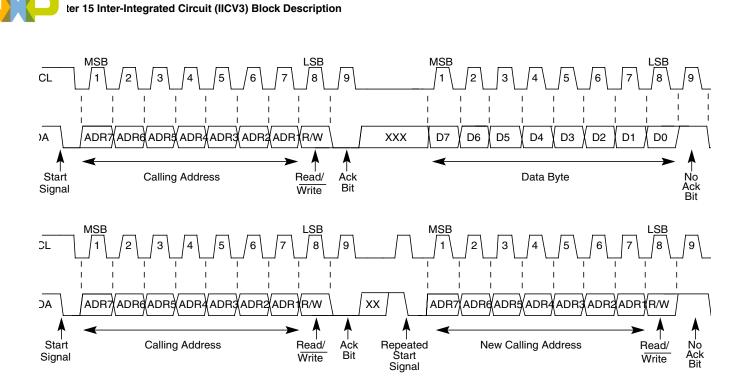

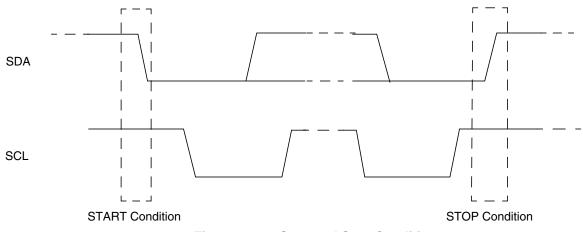

Figure 15-10. IIC-Bus Transmission Signals

## 15.4.1.1 START Signal

When the bus is free, i.e. no master device is engaging the bus (both SCL and SDA lines are at logical high), a master may initiate communication by sending a START signal.As shown in Figure 15-10, a START signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

Figure 15-11. Start and Stop Conditions

| Field    | Description                                                                                                                                                                                                                                                                 |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>TOF | <b>Timer Overflow Flag</b> — Set when 16-bit free-running timer overflows from 0xFFFF to 0x0000. Clearing this bit requires writing a one to bit 7 of TFLG2 register while the TEN bit of TSCR1 or PAEN bit of PACTL is set to one (See also TCRE control bit explanation.) |  |

#### Table 22-17. TRLG2 Field Descriptions

# 22.3.2.14 Timer Input Capture/Output Compare Registers High and Low 0–7 (TCxH and TCxL)

|        | 0x0010 = TC0<br>0x0012 = TC<br>0x0014 = TC2<br>0x0016 = TC3 | 1H<br>2H      | 0x0018 = TC4<br>0x001A = TC5<br>0x001C = TC6<br>0x001C = TC6 | 5H<br>6H    |             |             |        |       |

|--------|-------------------------------------------------------------|---------------|--------------------------------------------------------------|-------------|-------------|-------------|--------|-------|

| _      | 15                                                          | 14            | 13                                                           | 12          | 11          | 10          | 9      | 0     |

| R<br>W | Bit 15                                                      | Bit 14        | Bit 13                                                       | Bit 12      | Bit 11      | Bit 10      | Bit 9  | Bit 8 |

| Reset  | 0                                                           | 0             | 0                                                            | 0           | 0           | 0           | 0      | 0     |

|        | Figure 22                                                   | 2-22. Timer I | nput Captur                                                  | e/Output Co | ompare Regi | ster x High | (TCxH) |       |

|        | 0x0011 = TC<br>0x0013 = TC<br>0x0015 = TC<br>0x0017 = TC    | 1L<br>2L      | 0x0019 = TC4<br>0x001B = TC3<br>0x001D = TC<br>0x001F = TC3  | 5L<br>6L    |             |             |        |       |

|        | 7                                                           | 6             | 5                                                            | 4           | 3           | 2           | 1      | 0     |

| R<br>W | Bit 7                                                       | Bit 6         | Bit 5                                                        | Bit 4       | Bit 3       | Bit 2       | Bit 1  | Bit 0 |

| Reset  | 0                                                           | 0             | 0                                                            | 0           | 0           | 0           | 0      | 0     |

Figure 22-23. Timer Input Capture/Output Compare Register x Low (TCxL)

Depending on the TIOS bit for the corresponding channel, these registers are used to latch the value of the free-running counter when a defined transition is sensed by the corresponding input capture edge detector or to trigger an output action for output compare.

Read: Anytime

Write: Anytime for output compare function. Writes to these registers have no meaning or effect during input capture. All timer input capture/output compare registers are reset to 0x0000.

#### NOTE

Read/Write access in byte mode for high byte should takes place before low byte otherwise it will give a different result.

## 22.3.2.15 16-Bit Pulse Accumulator Control Register (PACTL)

Module Base + 0x0020

|       | 7 | 6            | 5              | 4     | 3     | 2    | 1       | 0   |  |

|-------|---|--------------|----------------|-------|-------|------|---------|-----|--|

| R     | 0 |              | DAMOD          | DEDOE | 0.144 |      | DA 01// | DAL |  |

| w     |   | PAEN         | PAMOD          | PEDGE | CLK1  | CLK0 | PAOVI   | PAI |  |

| Reset | 0 | 0            | 0              | 0     | 0     | 0    | 0       | 0   |  |

|       |   | Unimplemente | ed or Reserved |       |       |      |         |     |  |

#### Figure 22-24. 16-Bit Pulse Accumulator Control Register (PACTL)

When PAEN is set, the PACT is enabled. The PACT shares the input pin with IOC7.

Read: Any time

Write: Any time

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>PAEN       | Pulse Accumulator System Enable       PAEN is independent from TEN. With timer disabled, the pulse accumulator can function unless pulse accumulator is disabled.         0       16-Bit Pulse Accumulator system disabled.         1       Pulse Accumulator system enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>PAMOD      | Pulse Accumulator Mode — This bit is active only when the Pulse Accumulator is enabled (PAEN = 1). See Table 22-19.         0 Event counter mode.         1 Gated time accumulation mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>PEDGE      | <ul> <li>Pulse Accumulator Edge Control — This bit is active only when the Pulse Accumulator is enabled (PAEN = 1).</li> <li>For PAMOD bit = 0 (event counter mode). See Table 22-19.</li> <li>0 Falling edges on IOC7 pin cause the count to be incremented.</li> <li>1 Rising edges on IOC7 pin cause the count to be incremented.</li> <li>For PAMOD bit = 1 (gated time accumulation mode).</li> <li>0 IOC7 input pin high enables M (bus clock) divided by 64 clock to Pulse Accumulator and the trailing falling edge on IOC7 sets the PAIF flag.</li> <li>1 IOC7 input pin low enables M (bus clock) divided by 64 clock to Pulse Accumulator and the trailing rising edge on IOC7 sets the PAIF flag.</li> </ul> |

| 3:2<br>CLK[1:0] | Clock Select Bits — Refer to Table 22-20.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1<br>PAOVI      | Pulse Accumulator Overflow Interrupt Enable         0 Interrupt inhibited.         1 Interrupt requested if PAOVF is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>PAI        | Pulse Accumulator Input Interrupt Enable         0 Interrupt inhibited.         1 Interrupt requested if PAIF is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 22-18. PACTL Field Descriptions

# 23.2.4 VDDF — Regulator Output2 (NVM Logic) Pins

Signals VDDF/VSS are the secondary outputs of VREG\_3V3 that provide the power supply for the NVM logic. These signals are connected to device pins to allow external decoupling capacitors (220 nF, X7R ceramic).

In Shutdown Mode an external supply driving VDDF/VSS can replace the voltage regulator.

# 23.2.5 VDDPLL, VSSPLL — Regulator Output3 (PLL) Pins

Signals VDDPLL/VSSPLL are the secondary outputs of VREG\_3V3 that provide the power supply for the PLL and oscillator. These signals are connected to device pins to allow external decoupling capacitors (100 nF...220 nF, X7R ceramic).

In Shutdown Mode, an external supply driving VDDPLL/VSSPLL can replace the voltage regulator.

# 23.2.6 VDDX — Power Input Pin

Signals VDDX/VSS are monitored by VREG\_3V3 with the LVR feature.

## 23.2.7 VREGEN — Optional Regulator Enable Pin

This optional signal is used to shutdown VREG\_3V3. In that case, VDD/VSS and VDDPLL/VSSPLL must be provided externally. Shutdown mode is entered with VREGEN being low. If VREGEN is high, the VREG\_3V3 is either in Full Performance Mode or in Reduced Power Mode.

For the connectivity of VREGEN, see device specification.

#### NOTE

Switching from FPM or RPM to shutdown of VREG\_3V3 and vice versa is not supported while MCU is powered.

# 23.2.8 VREG\_API — Optional Autonomous Periodical Interrupt Output Pin

This pin provides the signal selected via APIEA if system is set accordingly. See 23.3.2.3, "Autonomous Periodical Interrupt Control Register (VREGAPICL) and 23.4.8, "Autonomous Periodical Interrupt (API) for details.

For the connectivity of VREG\_API, see device specification.

# 23.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in VREG\_3V3.

If enabled in the system, the VREG\_3V3 will abort all read and write accesses to reserved registers within it's memory slice. See device level specification for details.

# 24.4.2.19 Disable EEPROM Emulation Command

The Disable EEPROM Emulation command causes the Memory Controller to suspend current EEE activity.

#### Table 24-71. Disable EEPROM Emulation Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |  |  |

|-------------|------------------|--------------|--|--|--|--|

| 000         | 0x14             | Not required |  |  |  |  |

Upon clearing CCIF to launch the Disable EEPROM Emulation command, the Memory Controller will halt EEE operations at the next convenient point without clearing the EEE tag RAM or tag counter before setting the CCIF flag.

Table 24-72. Disable EEPROM Emulation Command Error Handling

| Register | Error Bit | Error Condition                                                               |

|----------|-----------|-------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                   |

|          | ACCENN    | Set if Full Partition D-Flash or Partition D-Flash command not previously run |

| FSTAT    | FPVIOL    | None                                                                          |

|          | MGSTAT1   | None                                                                          |

|          | MGSTAT0   | None                                                                          |

| FERSTAT  | EPVIOLIF  | None                                                                          |

## 24.4.2.20 EEPROM Emulation Query Command

The EEPROM Emulation Query command returns EEE partition and status variables.

Table 24-73. EEPROM Emulation Query Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                   |  |  |  |  |  |  |

|-------------|----------------------------------------------------|--|--|--|--|--|--|

| 000         | 0x15 Not required                                  |  |  |  |  |  |  |

| 001         | Return DFPART                                      |  |  |  |  |  |  |

| 010         | Return ERPART                                      |  |  |  |  |  |  |

| 011         | Return ECOUNT <sup>(1)</sup>                       |  |  |  |  |  |  |

| 100         | Return Dead Sector Count Return Ready Sector Count |  |  |  |  |  |  |

1. Indicates sector erase count

Upon clearing CCIF to launch the EEPROM Emulation Query command, the CCIF flag will set after the EEE partition and status variables are stored in the FCCOBIX register. If the Emulation Query command is executed prior to partitioning (Partition D-Flash Command Section 24.4.2.14), the following reset values are returned: DFPART =  $0x_FFFF$ , ERPART =  $0x_FFFF$ , ECOUNT =  $0x_FFFF$ , Dead Sector Count =  $0x_00$ , Ready Sector Count =  $0x_00$ .

# Chapter 25 256 KByte Flash Module (S12XFTM256K2V1)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected           | Description of Changes                                                                                                                                                                                                                 |

|--------------------|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.08             | 14 Nov 2007      | 25.5.2/25-951<br>25.4.2/25-927 | <ul> <li>Changed terminology from 'word program' to "Program P-Flash' in the BDM unsecuring description, Section 25.5.2</li> <li>Added requirement that user not write any Flash module register during</li> </ul>                     |

|                    |                  | 25.4.2/25-927                  | execution of commands 'Erase All Blocks', Section 25.4.2.8, and 'Unsecure Flash', Section 25.4.2.11                                                                                                                                    |

|                    |                  | 25.4.2.8/25-933                | - Added statement that security is released upon successful completion of command 'Erase All Blocks', Section 25.4.2.8                                                                                                                 |

| V01.09             | 19 Dec 2007      | 25.4.2.5/25-930                | - Corrected Error Handling table for Load Data Field command                                                                                                                                                                           |

|                    |                  | 25.4.2/25-927                  | - Corrected Error Handling table for Full Partition D-Flash, Partition D-Flash, and EEPROM Emulation Query commands                                                                                                                    |

|                    |                  | 25.3.1/25-896                  | - Corrected P-Flash IFR Accessibility table                                                                                                                                                                                            |

| V01.10             | 25 Sep 2009      | 25.1/25-891                    | - Clarify single bit fault correction for P-Flash phrase                                                                                                                                                                               |

|                    |                  | 25.3.2.1/25-903                | - Expand FDIV vs OSCCLK Frequency table                                                                                                                                                                                                |

|                    |                  | 25.4.2.4/25-930                | - Add statement concerning code runaway when executing Read Once command from Flash block containing associated fields                                                                                                                 |

|                    |                  | 25.4.2.7/25-932                | - Add statement concerning code runaway when executing Program Once command from Flash block containing associated fields                                                                                                              |

|                    |                  | 25.4.2.12/25-<br>936           | <ul> <li>Add statement concerning code runaway when executing Verify Backdoor</li> <li>Access Key command from Flash block containing associated fields</li> <li>Relate Key 0 to associated Backdoor Comparison Key address</li> </ul> |

|                    |                  | 25.4.2.12/25-                  | - Change "power down reset" to "reset"                                                                                                                                                                                                 |

|                    |                  | 936                            | - Add ACCERR condition for Disable EEPROM Emulation command                                                                                                                                                                            |

|                    |                  | 25.4.2.12/25-                  | The following changes were made to clarify module behavior related to Flash                                                                                                                                                            |

|                    |                  | 936                            | register access during reset sequence and while Flash commands are active:                                                                                                                                                             |

|                    |                  | 25.4.2.20/25-                  | - Add caution concerning register writes while command is active                                                                                                                                                                       |

|                    |                  | 945                            | <ul> <li>Writes to FCLKDIV are allowed during reset sequence while CCIF is clear</li> <li>Add caution concerning register writes while command is active</li> </ul>                                                                    |

|                    |                  |                                | - Writes to FCCOBIX, FCCOBHI, FCCOBLO registers are ignored during                                                                                                                                                                     |

|                    |                  | 25.3.2/25-901                  | reset sequence                                                                                                                                                                                                                         |

|                    |                  | 25.3.2.1/25-903                |                                                                                                                                                                                                                                        |

|                    |                  | 25.4.1.2/25-922                |                                                                                                                                                                                                                                        |

|                    |                  | 25.6/25-951                    |                                                                                                                                                                                                                                        |

|                    |                  |                                |                                                                                                                                                                                                                                        |

#### Table 25-1. Revision History

# 25.1 Introduction

The FTM256K2 module implements the following:

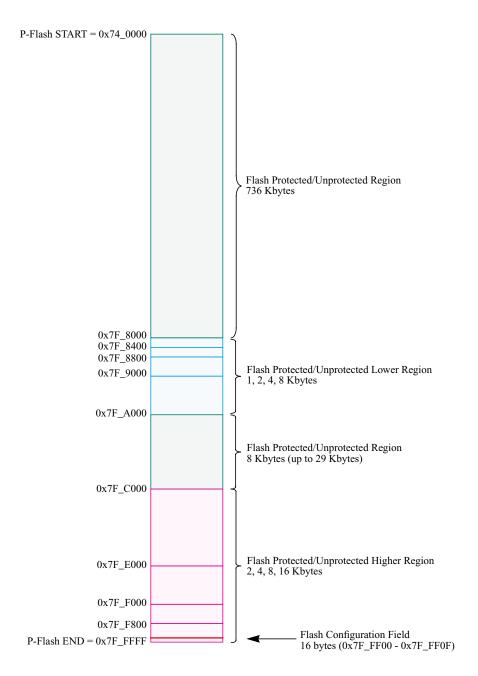

• 256 Kbytes of P-Flash (Program Flash) memory, consisting of 2 physical Flash blocks, intended primarily for nonvolatile code storage

Figure 28-2. P-Flash Memory Map

# A.3.1.19 Enable EEE (FCMD=0x13)

The maximum time to enable EPROM emulation is given by

$$t = \left( \left( \left( (1100 \cdot \text{BWN} + (176 \cdot (1 + \text{BWN}) + (\text{BWN} + \text{N}_{\text{SEC}}) \cdot 32364) \right) \right) \cdot \frac{1}{f_{\text{NVMOP}}} \right) + \left( (3050 \cdot (1 + \text{BWN}) + (\text{N}_{\text{SEC}} + \text{BWN}) \cdot 290500) \cdot \frac{1}{f_{\text{NVMBUS}}} \right) \right)$$

where  $N_{SEC}$  is the number of sectors of constant data. A constant sector is one in which all 63 records contain the latest active data and would need to be copied. The maximum possible is 33 (2048 EEE RAM words /63 =32.5) although this is a highly unlikely scenario. The impact of a worst case brownout recovery scenario is denoted by BWN = 2 for non brownout situations BWN =0.

| Name                    |                                                                                                                                                                                                                                  | Bit 7                                                                                                                                                                                                                                                                                               | Bit 6                                                                                                                                                                                                        | Bit 5                                                                                                                                                                                                                                                | Bit 4                                                                                                                                                                                                                                                                                           | Bit 3                                                  | Bit 2                                                                                                                                                                                                                                                                                                                         | Bit 1                                                  | Bit 0                                                  |           |       |       |                       |   |       |   |   |   |   |        |        |       |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-----------|-------|-------|-----------------------|---|-------|---|---|---|---|--------|--------|-------|

| SCI7BDH <sup>(1)</sup>  |                                                                                                                                                                                                                                  | IREN                                                                                                                                                                                                                                                                                                | TNP1                                                                                                                                                                                                         | TNP0                                                                                                                                                                                                                                                 | SBR12                                                                                                                                                                                                                                                                                           | SBR11                                                  | SBR10                                                                                                                                                                                                                                                                                                                         | SBR9                                                   | SBR8                                                   |           |       |       |                       |   |       |   |   |   |   |        |        |       |

| SCI7BDL <sup>1</sup>    | R<br>W                                                                                                                                                                                                                           | SBR7                                                                                                                                                                                                                                                                                                | SBR6                                                                                                                                                                                                         | SBR5                                                                                                                                                                                                                                                 | SBR4                                                                                                                                                                                                                                                                                            | SBR3                                                   | SBR2                                                                                                                                                                                                                                                                                                                          | SBR1                                                   | SBR0                                                   |           |       |       |                       |   |       |   |   |   |   |        |        |       |

| SCI7CR1 <sup>1</sup>    | R<br>W                                                                                                                                                                                                                           | LOOPS                                                                                                                                                                                                                                                                                               | SCISWAI                                                                                                                                                                                                      | RSRC                                                                                                                                                                                                                                                 | М                                                                                                                                                                                                                                                                                               | WAKE                                                   | ILT                                                                                                                                                                                                                                                                                                                           | PE                                                     | PT                                                     |           |       |       |                       |   |       |   |   |   |   |        |        |       |

| SCI7ASB1 <sup>(2)</sup> | R                                                                                                                                                                                                                                | BXEDGIE                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                               | 0                                                      | BEBBV                                                                                                                                                                                                                                                                                                                         | BEBBIE                                                 | BKDIF                                                  |           |       |       |                       |   |       |   |   |   |   |        |        |       |