Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | HCS12X                                                        |

| Core Size                  | 16-Bit                                                        |

| Speed                      | 50MHz                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI             |

| Peripherals                | LVD, POR, PWM, WDT                                            |

| Number of I/O              | 91                                                            |

| Program Memory Size        | 256КВ (256К х 8)                                              |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | 4K x 8                                                        |

| RAM Size                   | 16K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                  |

| Data Converters            | A/D 16x12b                                                    |

| Oscillator Type            | External                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 112-LQFP                                                      |

| Supplier Device Package    | 112-LQFP (20x20)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s912xet256j2malr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin        | Pin Pin Pin Pin<br>Name Name Name Name |           | Pin<br>Name Power |   | Internal Pull<br>Resistor |                                 | Description    |                                                       |

|------------|----------------------------------------|-----------|-------------------|---|---------------------------|---------------------------------|----------------|-------------------------------------------------------|

| Function 1 | Function 2                             |           | Function 4        |   | Supply                    | CTRL                            | Reset<br>State | Description                                           |

| EXTAL      | —                                      | _         |                   | — | V <sub>DDPLL</sub>        | NA                              | NA             | Oscillator pins                                       |

| XTAL       |                                        |           |                   |   | $V_{DDPLL}$               | NA                              | NA             |                                                       |

| RESET      | —                                      | —         | —                 | — | V <sub>DDX</sub>          | PULLI                           | JP             | External reset                                        |

| TEST       |                                        |           |                   |   | N.A.                      | RESET pin                       | DOWN           | Test input                                            |

| BKGD       | MODC                                   | _         | _                 | — | V <sub>DDX</sub>          | Always on                       | Up             | Background debug                                      |

| PAD[31:16] | AN[31:16]                              | _         | _                 | — | V <sub>DDA</sub>          | PER0AD1<br>PER1AD1              | Disabled       | Port AD inputs of ATD1,<br>analog inputs of ATD1      |

| PAD[15:0]  | AN[15:0]                               | —         | —                 | _ | V <sub>DDA</sub>          | PER0AD0<br>PER1AD0              | Disabled       | Port AD inputs of ATD0,<br>analog inputs of ATD0      |

| PA[7:0]    | ADDR[15:8]                             | IVD[15:8] | —                 | — | V <sub>DDX</sub>          | PUCR                            | Disabled       | Port A I/O, address bus,<br>internal visibility data  |

| PB[7:1]    | ADDR[7:1]                              | IVD[7:0]  | _                 | _ | V <sub>DDX</sub>          | PUCR                            | Disabled       | Port B I/O, address bus, internal visibility data     |

| PB0        | ADDR0                                  | UDS       |                   |   | V <sub>DDX</sub>          | PUCR                            | Disabled       | Port B I/O, address bus,<br>upper data strobe         |

| PC[7:0]    | DATA[15:8]                             | _         | _                 | _ | V <sub>DDX</sub>          | PUCR                            | Disabled       | Port C I/O, data bus                                  |

| PD[7:0]    | DATA[7:0]                              | _         | _                 | _ | V <sub>DDX</sub>          | PUCR                            | Disabled       | Port D I/O, data bus                                  |

| PE7        | ECLKX2                                 | XCLKS     | _                 | _ | V <sub>DDX</sub>          | PUCR                            | Up             | Port E I/O, system clock<br>output, clock select      |

| PE6        | TAGHI                                  | MODB      | _                 | _ | V <sub>DDX</sub>          | While RESET<br>pin is low: down |                | Port E I/O, tag high, mode input                      |

| PE5        | RE                                     | MODA      | TAGLO             | _ | V <sub>DDX</sub>          | While RE pin is low:            |                | Port E I/O, read enable,<br>mode input, tag low input |

| PE4        | ECLK                                   |           | _                 | _ | V <sub>DDX</sub>          | PUCR                            | Up             | Port E I/O, bus clock output                          |

| PE3        | LSTRB                                  | LDS       | EROMCTL           | _ | V <sub>DDX</sub>          | PUCR                            | Up             | Port E I/O, low byte data strobe, EROMON control      |

| PE2        | R/W                                    | WE        | _                 | _ | V <sub>DDX</sub>          | PUCR                            | Up             | Port E I/O, read/write                                |

| PE1        | ĪRQ                                    | _         | _                 | _ | V <sub>DDX</sub>          | PUCR                            | Up             | Port E Input, maskable<br>interrupt                   |

| PE0        | XIRQ                                   | —         | —                 | _ | V <sub>DDX</sub>          | PUCR                            | Up             | Port E input, non-maskable interrupt                  |

| PF7        | TXD3                                   | _         | _                 | _ | V <sub>DDX</sub>          | PERF/<br>PPSF                   | Up             | Port F I/O, interrupt, TXD of SCI3                    |

| PF6        | RXD3                                   |           |                   |   | V <sub>DDX</sub>          | PERF/<br>PPSF                   | Up             | Port F I/O, interrupt, RXD of SCI3                    |

| PF5        | SCL0                                   |           |                   |   | V <sub>DDX</sub>          | PERF/<br>PPSF                   | Up             | Port F I/O, interrupt, SCL of IIC0                    |

| PF4        | SDA0                                   | —         | —                 |   | V <sub>DDX</sub>          | PERF/<br>PPSF                   | Up             | Port F I/O, interrupt, SDA of IIC0                    |

| PF3        | CS3                                    | —         | —                 | — | V <sub>DDX</sub>          | PERF/<br>PPSF                   | Up             | Port F I/O, interrupt, chip select 3                  |

Table 1-10. Signal Properties Summary (Sheet 1 of 4)

#### ter 1 Device Overview MC9S12XE-Family

The program Flash memory and the EEPROM are supplied by the bus clock and the oscillator clock. The oscillator clock is used as a time base to derive the program and erase times for the NVM's.

The CAN modules may be configured to have their clock sources derived either from the bus clock or directly from the oscillator clock. This allows the user to select its clock based on the required jitter performance.

In order to ensure the presence of the clock the MCU includes an on-chip clock monitor connected to the output of the oscillator. The clock monitor can be configured to invoke the PLL self-clocking mode or to generate a system reset if it is allowed to time out as a result of no oscillator clock being present.

In addition to the clock monitor, the MCU also provides a clock quality checker which performs a more accurate check of the clock. The clock quality checker counts a predetermined number of clock edges within a defined time window to insure that the clock is running. The checker can be invoked following specific events such as on wake-up or clock monitor failure.

# 1.4 Modes of Operation

The MCU can operate in different modes associated with MCU resource mapping and bus interface configuration. These are described in 1.4.1 Chip Configuration Summary.

The MCU can operate in different power modes to facilitate power saving when full system performance is not required. These are described in 1.4.2 Power Modes.

Some modules feature a software programmable option to freeze the module status whilst the background debug module is active to facilitate debugging. This is described in 1.4.3 Freeze Mode.

For system integrity support separate system states are featured as explained in 1.4.4 System States.

# 1.4.1 Chip Configuration Summary

The MCU can operate in six different modes associated with resource configuration. The different modes, the state of ROMCTL and EROMCTL signal on rising edge of  $\overline{\text{RESET}}$  and the security state of the MCU affect the following device characteristics:

- External bus interface configuration

- Flash in memory map, or not

- Debug features enabled or disabled

The operating mode out of reset is determined by the states of the MODC, MODB, and MODA signals during reset (see Table 1-12). The MODC, MODB, and MODA bits in the MODE register show the current operating mode and provide limited mode switching during operation. The states of the MODC, MODB, and MODA signals are latched into these bits on the rising edge of RESET.

In normal expanded mode and in emulation modes the ROMON bit and the EROMON bit in the MMCCTL1 register defines if the on chip flash memory is the memory map, or not. (See Table 1-12.) For a detailed explanation of the ROMON and EROMON bits refer to the MMC description.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>CSZ  | <ul> <li>Access Type Indicator — This bit indicates if the access was a byte or word size access. This bit only contains valid information when tracing CPU12X activity in Detail Mode.</li> <li>0 Word Access</li> <li>1 Byte Access</li> </ul>                                                                                                                    |

| 5<br>CRW  | <ul> <li>Read Write Indicator — This bit indicates if the corresponding stored address corresponds to a read or write access. This bit only contains valid information when tracing CPU12X activity in Detail Mode.</li> <li>Write Access</li> <li>Read Access</li> </ul>                                                                                           |

| 4<br>COCF | <ul> <li>CPU12X Opcode Fetch Indicator — This bit indicates if the stored address corresponds to an opcode fetch cycle. This bit only contains valid information when tracing the XGATE accesses in Detail Mode.</li> <li>0 Stored information does not correspond to opcode fetch cycle</li> <li>1 Stored information corresponds to opcode fetch cycle</li> </ul> |

| 3<br>XACK | <ul> <li>XGATE Access Indicator — This bit indicates if the stored XGATE address corresponds to a free cycle. This bit only contains valid information when tracing the CPU12X accesses in Detail Mode.</li> <li>0 Stored information corresponds to free cycle</li> <li>1 Stored information does not correspond to free cycle</li> </ul>                          |

| 2<br>XSZ  | <ul> <li>Access Type Indicator — This bit indicates if the access was a byte or word size access. This bit only contains valid information when tracing XGATE activity in Detail Mode.</li> <li>0 Word Access</li> <li>1 Byte Access</li> </ul>                                                                                                                     |

| 1<br>XRW  | Read Write Indicator — This bit indicates if the corresponding stored address corresponds to a read or write<br>access. This bit only contains valid information when tracing XGATE activity in Detail Mode.0Write Access1Read Access                                                                                                                               |

| 0<br>XOCF | XGATE Opcode Fetch Indicator — This bit indicates if the stored address corresponds to an opcode fetch<br>cycle. This bit only contains valid information when tracing the CPU12X accesses in Detail Mode.0Stored information does not correspond to opcode fetch cycle1Stored information corresponds to opcode fetch cycle                                        |

#### Table 8-46. CXINF Field Descriptions (continued)

## 8.4.5.4 Reading Data from Trace Buffer

The data stored in the Trace Buffer can be read using either the background debug module (BDM) module, the XGATE or the CPU12X provided the S12XDBG module is not armed, is configured for tracing and the system not secured. When the ARM bit is written to 1 the trace buffer is locked to prevent reading. The trace buffer can only be unlocked for reading by an aligned word write to DBGTB when the module is disarmed.

The Trace Buffer can only be read through the DBGTB register using aligned word reads, any byte or misaligned reads return 0 and do not cause the trace buffer pointer to increment to the next trace buffer address. The Trace Buffer data is read out first-in first-out. By reading CNT in DBGCNT the number of valid 64-bit lines can be determined. DBGCNT will not decrement as data is read.

Whilst reading an internal pointer is used to determine the next line to be read. After a tracing session, the pointer points to the oldest data entry, thus if no overflow has occurred, the pointer points to line0, otherwise it points to the line with the oldest entry. The pointer is initialized by each aligned write to DBGTBH to point to the oldest data again. This enables an interrupted trace buffer read sequence to be easily restarted from the oldest data entry.

## Branch if Higher

### Operation

If C | Z = 0, then PC +  $0002 + (REL9 \le 1) \Rightarrow PC$

Branch instruction to compare <u>unsigned numbers</u>.

#### Branch if RS1 > RS2:

SUB R0,RS1,RS2 BHI REL9

### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| _ | _ | _ |   |

- N: Not affected.

- Z: Not affected.

- V: Not affected.

- C: Not affected.

### **Code and CPU Cycles**

| Source Form | Address<br>Mode | Machine Code       | Cycles |

|-------------|-----------------|--------------------|--------|

| BHI REL9    | REL9            | 0 0 1 1 0 0 0 REL9 | PP/P   |

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PLLSEL | PLL Select BitWrite: Anytime.Writing a one when LOCK=0 has no effect. This prevents the selection of an unstable PLLCLK as SYSCLK.PLLSEL bit is cleared when the MCU enters Self Clock Mode, Stop Mode or Wait Mode with PLLWAI bit set.It is recommended to read back the PLLSEL bit to make sure PLLCLK has really been selected asSYSCLK, as LOCK status bit could theoretically change at the very moment writing the PLLSEL bit.00System clocks are derived from OSCCLK (f <sub>BUS</sub> = f <sub>OSC</sub> / 2).11System clocks are derived from PLLCLK (f <sub>BUS</sub> = f <sub>PLL</sub> / 2). |

| 6<br>PSTP   | <ul> <li>Pseudo Stop Bit</li> <li>Write: Anytime</li> <li>This bit controls the functionality of the oscillator during Stop Mode.</li> <li>0 Oscillator is disabled in Stop Mode.</li> <li>1 Oscillator continues to run in Stop Mode (Pseudo Stop).</li> <li>Note: Pseudo Stop Mode allows for faster STOP recovery and reduces the mechanical stress and aging of the resonator in case of frequent STOP conditions at the expense of a slightly increased power consumption.</li> </ul>                                                                                                                |

| 5<br>XCLKS  | <ul> <li>Oscillator Configuration Status Bit — This read-only bit shows the oscillator configuration status.</li> <li>0 Loop controlled Pierce Oscillator is selected.</li> <li>1 External clock / full swing Pierce Oscillator is selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |

| 3<br>PLLWAI | PLL Stops in Wait Mode Bit         Write: Anytime         If PLLWAI is set, the S12XECRG will clear the PLLSEL bit before entering Wait Mode. The PLLON bit remains set during Wait Mode but the IPLL is powered down. Upon exiting Wait Mode, the PLLSEL bit has to be set manually if PLL clock is required.         0       IPLL keeps running in Wait Mode.         1       IPLL stops in Wait Mode.                                                                                                                                                                                                  |

| 1<br>RTIWAI | <b>RTI Stops in Wait Mode Bit</b> Write: Anytime         0       RTI keeps running in Wait Mode.         1       RTI stops and initializes the RTI dividers whenever the part goes into Wait Mode.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0<br>COPWAI | <ul> <li>COP Stops in Wait Mode Bit</li> <li>Normal modes: Write once</li> <li>Special modes: Write anytime</li> <li>0 COP keeps running in Wait Mode.</li> <li>1 COP stops and initializes the COP counter whenever the part goes into Wait Mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

#### Table 11-6. CLKSEL Field Descriptions

# 11.3.2.7 S12XECRG IPLL Control Register (PLLCTL)

This register controls the IPLL functionality.

Module Base + 0x0006

| _      | 7   | 6     | 5   | 4   | 3      | 2   | 1   | 0    |

|--------|-----|-------|-----|-----|--------|-----|-----|------|

| R<br>W | CME | PLLON | FM1 | FM0 | FSTWKP | PRE | PCE | SCME |

| Reset  | 1   | 1     | 0   | 0   | 0      | 0   | 0   | 1    |

| S8C | S4C | S2C | S1C | Number of Conversions per Sequence |

|-----|-----|-----|-----|------------------------------------|

| 0   | 0   | 0   | 0   | 16                                 |

| 0   | 0   | 0   | 1   | 1                                  |

| 0   | 0   | 1   | 0   | 2                                  |

| 0   | 0   | 1   | 1   | 3                                  |

| 0   | 1   | 0   | 0   | 4                                  |

| 0   | 1   | 0   | 1   | 5                                  |

| 0   | 1   | 1   | 0   | 6                                  |

| 0   | 1   | 1   | 1   | 7                                  |

| 1   | 0   | 0   | 0   | 8                                  |

| 1   | 0   | 0   | 1   | 9                                  |

| 1   | 0   | 1   | 0   | 10                                 |

| 1   | 0   | 1   | 1   | 11                                 |

| 1   | 1   | 0   | 0   | 12                                 |

| 1   | 1   | 0   | 1   | 13                                 |

| 1   | 1   | 1   | 0   | 14                                 |

| 1   | 1   | 1   | 1   | 15                                 |

#### Table 13-11. Conversion Sequence Length Coding

Table 13-12. ATD Behavior in Freeze Mode (Breakpoint)

| FRZ1 | FRZ0 | Behavior in Freeze Mode                |  |  |  |

|------|------|----------------------------------------|--|--|--|

| 0    | 0    | Continue conversion                    |  |  |  |

| 0    | 1    | Reserved                               |  |  |  |

| 1    | 0    | Finish current conversion, then freeze |  |  |  |

| 1    | 1    | Freeze Immediately                     |  |  |  |

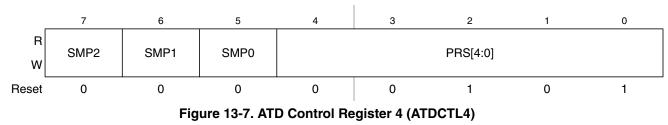

## 13.3.2.5 ATD Control Register 4 (ATDCTL4)

Writes to this register will abort current conversion sequence.

Module Base + 0x0004

Read: Anytime

Write: Anytime

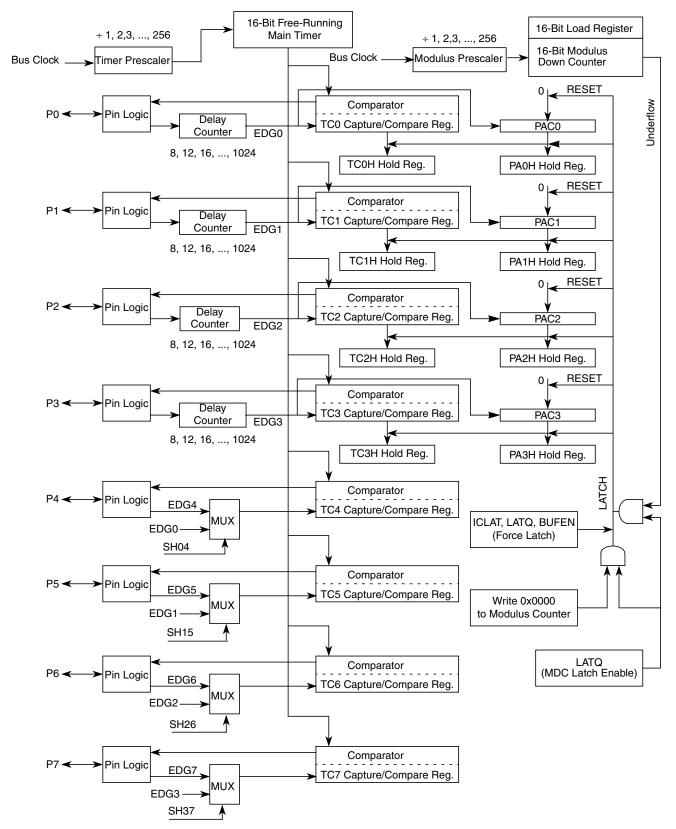

ter 14 Enhanced Capture Timer (ECT16B8CV3)

Figure 14-68. Detailed Timer Block Diagram in Latch Mode when PRNT = 1

1. Read: Anytime

Write: Anytime when not in initialization mode

### NOTE

The CANTIER register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable when not in initialization mode (INITRQ = 0 and INITAK = 0).

#### Table 16-14. CANTIER Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0<br>TXEIE[2:0] | <ul> <li>Transmitter Empty Interrupt Enable</li> <li>0 No interrupt request is generated from this event.</li> <li>1 A transmitter empty (transmit buffer available for transmission) event causes a transmitter empty interrupt request.</li> </ul> |

## 16.3.2.9 MSCAN Transmitter Message Abort Request Register (CANTARQ)

The CANTARQ register allows abort request of queued messages as described below.

Module Base + 0x0008

Access: User read/write<sup>(1)</sup>

|        | 7               | 6 | 5 | 4 | 3 | 2       | 1      | 0      |

|--------|-----------------|---|---|---|---|---------|--------|--------|

| R      | 0               | 0 | 0 | 0 | 0 | ABTRQ2  | ABTRQ1 | ABTRQ0 |

| w      |                 |   |   |   |   | ADTINUZ | ADINQI | ADINGU |

| Reset: | 0               | 0 | 0 | 0 | 0 | 0       | 0      | 0      |

|        | = Unimplemented |   |   |   |   |         |        |        |

#### Figure 16-12. MSCAN Transmitter Message Abort Request Register (CANTARQ)

1. Read: Anytime

Write: Anytime when not in initialization mode

#### NOTE

The CANTARQ register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable when not in initialization mode (INITRQ = 0 and INITAK = 0).

#### Table 16-15. CANTARQ Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0<br>ABTRQ[2:0] | Abort Request — The CPU sets the ABTRQx bit to request that a scheduled message buffer (TXEx = 0) be<br>aborted. The MSCAN grants the request if the message has not already started transmission, or if the<br>transmission is not successful (lost arbitration or error). When a message is aborted, the associated TXE (see<br>Section 16.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and abort acknowledge flags (ABTAK, see<br>Section 16.3.2.10, "MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)") are set and a<br>transmit interrupt occurs if enabled. The CPU cannot reset ABTRQx. ABTRQx is reset whenever the associated<br>TXE flag is set.<br>0 No abort request<br>1 Abort request pending |

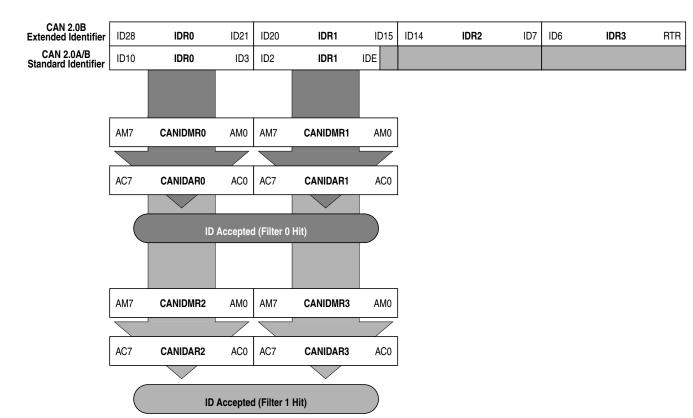

ter 16 Freescale's Scalable Controller Area Network (S12MSCANV3)

Figure 16-41. 16-bit Maskable Identifier Acceptance Filters

## 21.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

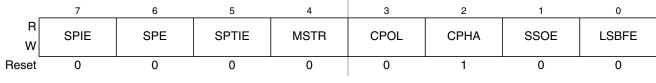

# 21.3.2.1 SPI Control Register 1 (SPICR1)

Module Base +0x0000

Figure 21-3. SPI Control Register 1 (SPICR1)

Read: Anytime

Write: Anytime

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable Bit — This bit enables SPI interrupt requests, if SPIF or MODF status flag is set.</li> <li>O SPI interrupts disabled.</li> <li>1 SPI interrupts enabled.</li> </ul>                                                                                                                                                                                                                                                   |

| 6<br>SPE   | <ul> <li>SPI System Enable Bit — This bit enables the SPI system and dedicates the SPI port pins to SPI system functions. If SPE is cleared, SPI is disabled and forced into idle state, status bits in SPISR register are reset.</li> <li>SPI disabled (lower power consumption).</li> <li>SPI enabled, port pins are dedicated to SPI functions.</li> </ul>                                                                                        |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This bit enables SPI interrupt requests, if SPTEF flag is set.</li> <li>O SPTEF interrupt disabled.</li> <li>1 SPTEF interrupt enabled.</li> </ul>                                                                                                                                                                                                                                                          |

| 4<br>MSTR  | <ul> <li>SPI Master/Slave Mode Select Bit — This bit selects whether the SPI operates in master or slave mode.</li> <li>Switching the SPI from master to slave or vice versa forces the SPI system into idle state.</li> <li>SPI is in slave mode.</li> <li>SPI is in master mode.</li> </ul>                                                                                                                                                        |

| 3<br>CPOL  | <ul> <li>SPI Clock Polarity Bit — This bit selects an inverted or non-inverted SPI clock. To transmit data between SPI modules, the SPI modules must have identical CPOL values. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Active-high clocks selected. In idle state SCK is low.</li> <li>1 Active-low clocks selected. In idle state SCK is high.</li> </ul> |

| 2<br>CPHA  | <ul> <li>SPI Clock Phase Bit — This bit is used to select the SPI clock format. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Sampling of data occurs at odd edges (1,3,5,) of the SCK clock.</li> <li>1 Sampling of data occurs at even edges (2,4,6,) of the SCK clock.</li> </ul>                                                                               |

#### Table 21-2. SPICR1 Field Descriptions

#### Table 22-21. PAFLG Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>PAOVF | <b>Pulse Accumulator Overflow Flag</b> — Set when the 16-bit pulse accumulator overflows from 0xFFFF to 0x0000. Clearing this bit requires writing a one to this bit in the PAFLG register while TEN bit of TSCR1 or PAEN bit of PACTL register is set to one.            |

| 0<br>PAIF  | <b>Pulse Accumulator Input edge Flag</b> — Set when the selected edge is detected at the IOC7 input pin.In event mode the event edge triggers PAIF and in gated time accumulation mode the trailing edge of the gate signal at the IOC7 input pin triggers PAIF.          |

|            | Clearing this bit requires writing a one to this bit in the PAFLG register while TEN bit of TSCR1 or PAEN bit of PACTL register is set to one. Any access to the PACNT register will clear all the flags in this register when TFFCA bit in register TSCR(0x0006) is set. |

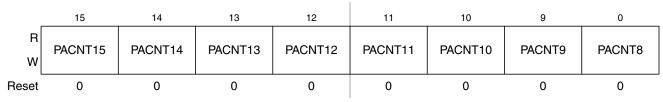

## 22.3.2.17 Pulse Accumulators Count Registers (PACNT)

Module Base + 0x0022

Module Base + 0x0023

|       | 7      | 6       | 5       | 4      | 3       | 2       | 1       | 0       |

|-------|--------|---------|---------|--------|---------|---------|---------|---------|

| R     |        | DAONITO | DAONITE |        | DAONITO | DAONITO | DAONITA | DAONITO |

| w     | PACNT7 | PACNT6  | PACNT5  | PACNT4 | PACNT3  | PACNT2  | PACNT1  | PACNT0  |

| Reset | 0      | 0       | 0       | 0      | 0       | 0       | 0       | 0       |

Figure 22-27. Pulse Accumulator Count Register Low (PACNTL)

Read: Anytime

Write: Anytime

These registers contain the number of active input edges on its input pin since the last reset.

When PACNT overflows from 0xFFFF to 0x0000, the Interrupt flag PAOVF in PAFLG (0x0021) is set.

Full count register access should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

### NOTE

Reading the pulse accumulator counter registers immediately after an active edge on the pulse accumulator input pin may miss the last count because the input has to be synchronized with the bus clock first.

## CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

Table 24-41. Program P-Flash Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                         |                                                     |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|

| 000         | 0x06                                                                     | Global address [22:16] to<br>identify P-Flash block |  |  |  |  |  |

| 001         | Global address [15:0] of phrase location to be programmed <sup>(1)</sup> |                                                     |  |  |  |  |  |

| 010         | Word 0 program value                                                     |                                                     |  |  |  |  |  |

| 011         | Word 1 program value                                                     |                                                     |  |  |  |  |  |

| 100         | Word 2 program value                                                     |                                                     |  |  |  |  |  |

| 101         | Word 3 pro                                                               | Word 3 program value                                |  |  |  |  |  |

1. Global address [2:0] must be 000

Upon clearing CCIF to launch the Program P-Flash command, the Memory Controller will program the data words to the supplied global address and will then proceed to verify the data words read back as expected. The CCIF flag will set after the Program P-Flash operation has completed.

| Register | Error Bit | Error Condition                                                                                  |

|----------|-----------|--------------------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 101 at command launch                                                      |

|          | ACCERR    | Set if command not available in current mode (see Table 24-30)                                   |

|          | ACCERR    | Set if an invalid global address [22:0] is supplied <sup>(1)</sup>                               |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                     |

|          | FPVIOL    | Set if the global address [22:0] points to a protected area                                      |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation <sup>(2)</sup>               |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation <sup>2</sup> |

| FERSTAT  | EPVIOLIF  | None                                                                                             |

Table 24-42. Program P-Flash Command Error Handling

1. As defined by the memory map for FTM256K2.

2. As found in the memory map for FTM256K2.

## 24.4.2.6 Program Once Command

The Program Once command restricts programming to a reserved 64 byte field (8 phrases) in the nonvolatile information register located in P-Flash block 0. The Program Once reserved field can be read using the Read Once command as described in Section 24.4.2.4. The Program Once command must only be issued once since the nonvolatile information register in P-Flash block 0 cannot be erased. The Program

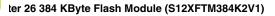

Figure 26-26. Generic Flash Command Write Sequence Flowchart

| Register | Error Bit Error Condition |                                                                                      |  |  |  |  |

|----------|---------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

|          |                           | Set if CCOBIX[2:0] != 010 at command launch                                          |  |  |  |  |

|          |                           | Set if a Load Data Field command sequence is currently active                        |  |  |  |  |

|          |                           | Set if command not available in current mode (see Table 26-30)                       |  |  |  |  |

|          | ACCERR                    | Set if an invalid global address [22:0] is supplied <sup>(1)</sup>                   |  |  |  |  |

| FSTAT    |                           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)         |  |  |  |  |

|          |                           | Set if the requested section crosses a 256 Kbyte boundary                            |  |  |  |  |

|          | FPVIOL                    | None                                                                                 |  |  |  |  |

|          | MGSTAT1                   | Set if any errors have been encountered during the read <sup>(2)</sup>               |  |  |  |  |

|          | MGSTAT0                   | Set if any non-correctable errors have been encountered during the read <sup>2</sup> |  |  |  |  |

| FERSTAT  | EPVIOLIF                  | None                                                                                 |  |  |  |  |

Table 26-38. Erase Verify P-Flash Section Command Error Handling

1. As defined by the memory map for FTM512K3.

2. As found in the memory map for FTM512K3.

## 26.4.2.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash block 0. The Read Once field is programmed using the Program Once command described in Section 26.4.2.7. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters                         |              |  |  |  |  |  |

|-------------|------------------------------------------|--------------|--|--|--|--|--|

| 000         | 0x04                                     | Not Required |  |  |  |  |  |

| 001         | Read Once phrase index (0x0000 - 0x0007) |              |  |  |  |  |  |

| 010         | Read Once word 0 value                   |              |  |  |  |  |  |

| 011         | Read Once word 1 value                   |              |  |  |  |  |  |

| 100         | Read Once word 2 value                   |              |  |  |  |  |  |

| 101         | Read Once                                | word 3 value |  |  |  |  |  |

Table 26-39. Read Once Command FCCOB Requirements

Upon clearing CCIF to launch the Read Once command, a Read Once phrase is fetched and stored in the FCCOB indexed register. The CCIF flag will set after the Read Once operation has completed. Valid phrase index values for the Read Once command range from 0x0000 to 0x0007. During execution of the Read Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

| SEC[1:0] | Status of Security     |

|----------|------------------------|

| 00       | SECURED                |

| 01       | SECURED <sup>(1)</sup> |

| 10       | UNSECURED              |

| 11       | SECURED                |

Table 29-12. Flash Security States

1. Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 29.5.

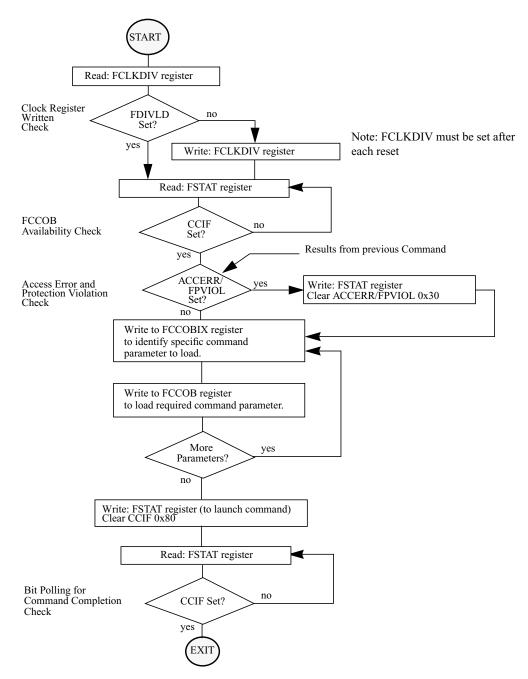

## 29.3.2.3 Flash CCOB Index Register (FCCOBIX)

Offset Module Base + 0x0002

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Figure 29-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

Table 29-13. FCCOBIX Field Descriptions

| Field              | Description                                                                                                                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2–0<br>CCOBIX[1:0] | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See Section 29.3.2.11, "Flash Common Command Object Register (FCCOB)," for more details. |

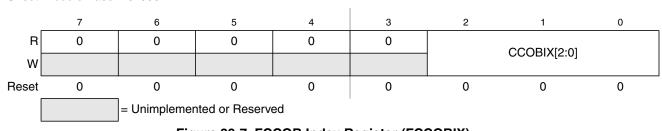

# 29.3.2.4 Flash ECCR Index Register (FECCRIX)

The FECCRIX register is used to index the FECCR register for ECC fault reporting.

### Figure 29-8. FECCR Index Register (FECCRIX)

ECCRIX bits are readable and writable while remaining bits read 0 and are not writable.

#### Table A-8. 5V I/O Characteristics

| Num | C | Rating                                                                                                                                                                                                                                               | Symbol                               | Min                     | Тур | Max                     | Unit |

|-----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------|-----|-------------------------|------|

| 1   | Р | Input high voltage                                                                                                                                                                                                                                   | VIH                                  | 0.65*V <sub>DD35</sub>  | _   | _                       | v    |

|     | Т | Input high voltage                                                                                                                                                                                                                                   | VIH                                  | _                       | _   | V <sub>DD35</sub> + 0.3 | v    |

| 2   | Р | Input low voltage                                                                                                                                                                                                                                    | V <sub>IL</sub>                      | _                       | _   | 0.35*V <sub>DD35</sub>  | V    |

|     | Т | Input low voltage                                                                                                                                                                                                                                    | V <sub>IL</sub>                      | V <sub>SS35</sub> – 0.3 | _   | _                       | v    |

| 3   | Т | Input hysteresis                                                                                                                                                                                                                                     | VHYS                                 | _                       | 250 | _                       | mV   |

| 4a  | Ρ | Input leakage current (pins in high impedance input<br>mode) <sup>(1)</sup> $V_{in} = V_{DD35}$ or $V_{SS35}$<br><b>M</b> Temperature range -40°C to 150°C<br><b>V</b> Temperature range -40°C to 130°C<br><b>C</b> Temperature range -40°C to 110°C | I <sub>in</sub>                      | -1<br>-0.75<br>-0.5     |     | 1<br>0.75<br>0.5        | μΑ   |

| 4b  | C | Input leakage current (pins in high impedance input mode) $V_{in} = V_{DD35}$ or $V_{SS35}$<br>-40°C<br>27°C<br>70°C<br>85°C<br>100°C<br>105°C<br>110°C<br>120°C<br>125°C<br>130°C<br>130°C<br>150°C                                                 | I <sub>in</sub>                      |                         |     |                         | nA   |

| 5   | С | Output high voltage (pins in output mode)<br>Partial drive I <sub>OH</sub> = -2 mA                                                                                                                                                                   | V <sub>OH</sub>                      | V <sub>DD35</sub> – 0.8 | _   | —                       | V    |

| 6   | Р | Output high voltage (pins in output mode)<br>Full drive I <sub>OH</sub> = -10 mA                                                                                                                                                                     | V <sub>OH</sub>                      | V <sub>DD35</sub> – 0.8 | _   | —                       | V    |

| 7   | С | Output low voltage (pins in output mode)<br>Partial drive I <sub>OL</sub> = +2 mA                                                                                                                                                                    | V <sub>OL</sub>                      | _                       | _   | 0.8                     | V    |

| 3   | Р | Output low voltage (pins in output mode)<br>Full drive I <sub>OL</sub> = +10 mA                                                                                                                                                                      | V <sub>OL</sub>                      | —                       | —   | 0.8                     | V    |

| )   | Р | Internal pull up resistance<br>V <sub>IH</sub> min > input voltage > V <sub>IL</sub> max                                                                                                                                                             | R <sub>PUL</sub>                     | 25                      | _   | 50                      | KΩ   |

| 0   | Р | Internal pull down resistance<br>V <sub>IH</sub> min > input voltage > V <sub>IL</sub> max                                                                                                                                                           | R <sub>PDH</sub>                     | 25                      |     | 50                      | ΚΩ   |

| 1   | D | Input capacitance                                                                                                                                                                                                                                    | C <sub>in</sub>                      | _                       | 6   |                         | pF   |

| 12  | Т | Injection current <sup>(2)</sup><br>Single pin limit<br>Total device Limit, sum of all injected currents                                                                                                                                             | I <sub>ICS</sub><br>I <sub>ICP</sub> | -2.5<br>-25             | —   | 2.5<br>25               | mA   |

| 3   | Ρ | Port H, J, P interrupt input pulse filtered(STOP) $^{(3)}$                                                                                                                                                                                           | t <sub>PULSE</sub>                   |                         | _   | 3                       | μs   |

| 14  | Ρ | Port H, J, P interrupt input pulse passed(STOP) <sup>3</sup>                                                                                                                                                                                         | t <sub>PULSE</sub>                   | 10                      |     |                         | μs   |

| 15  | D | Port H, J, P interrupt input pulse filtered (STOP)                                                                                                                                                                                                   | t <sub>PULSE</sub>                   |                         |     | 3                       | tcyc |

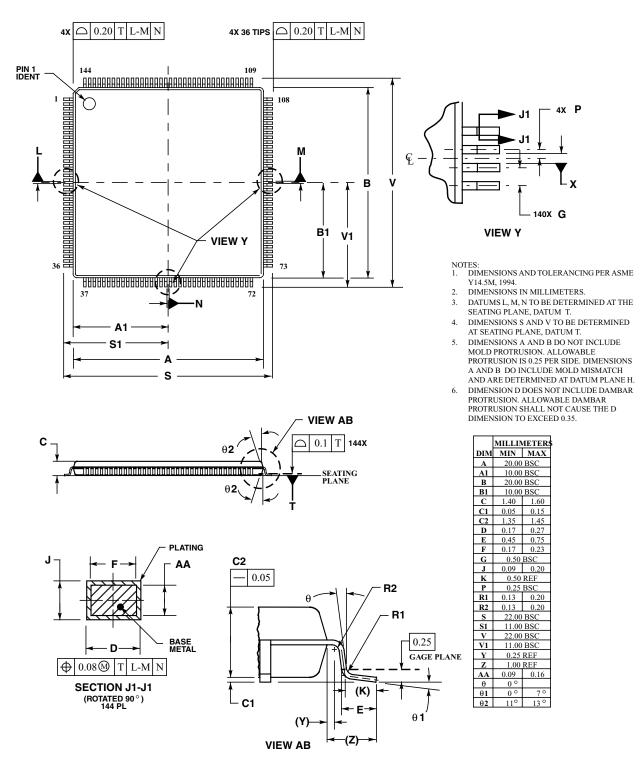

Figure B-2. 144-Pin LQFP Mechanical Dimensions (Case No. 918-03)

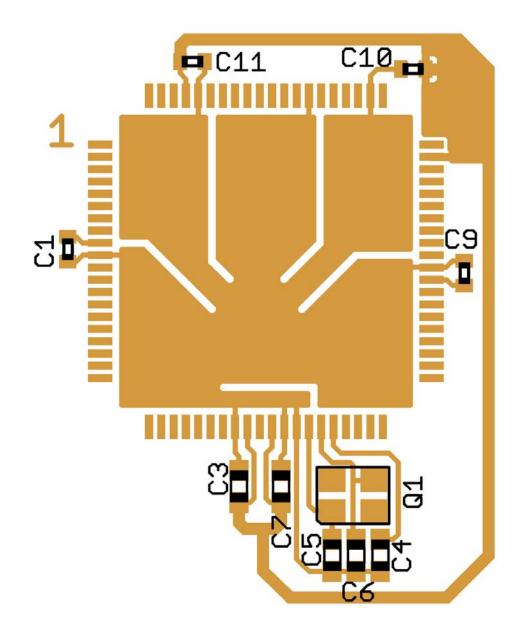

Figure C-3. 80-Pin QFP Recommended PCB Layout (Loop Controlled Pierce Oscillator)

ndix E Detailed Register Address Map

### 0x0030–0x0031 Reserved Register Space

| 0x0030 | Reserved | R | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|--------|----------|---|---|---|---|---|---|---|---|---|

| 0x0000 | neserveu | W |   |   |   |   |   |   |   |   |

| 0x0031 | Reserved | R | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0x0031 | Reserved | W |   |   |   |   |   |   |   |   |

## 0x0032–0x0033 Port Integration Module (PIM) Map 4 of 6

| Address | Name  |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0032  | PORTK | R<br>W | PK7   | PK6   | PK5   | PK4   | PK3   | PK2   | PK1   | PK0   |

| 0x0033  | DDRK  | R<br>W | DDRK7 | DDRK6 | DDRK5 | DDRK4 | DDRK3 | DDRK2 | DDRK1 | DDRK0 |

## 0x0034–0x003F Clock and Reset Generator (CRG) Map

| Address | Name    |         | Bit 7  | Bit 6                     | Bit 5        | Bit 4         | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |  |

|---------|---------|---------|--------|---------------------------|--------------|---------------|---------|---------|---------|---------|--|--|

| 0x0034  | SYNR    | R<br>W  | VCOFF  | RQ[1:0]                   | SYNDIV5      | SYNDIV4       | SYNDIV3 | SYNDIV2 | SYNDIV1 | SYNDIV0 |  |  |

| 0x0035  | REFDV   | R<br>W  | REFFF  | RQ[1:0]                   | REFDIV5      | REFDIV4       | REFDIV3 | REFDIV2 | REFDIV1 | REFDIV0 |  |  |

| 0x0036  | POSTDIV | R<br>W  | 0      | 0                         | 0            | POSTDIV[4:0]] |         |         |         |         |  |  |

| 0x0037  | CRGFLG  | R<br>W  | RTIF   | PORF                      | LVRF         | LOCKIF        | LOCK    | ILAF    | SCMIF   | SCM     |  |  |

| 0x0038  | CRGINT  | R<br>W  | RTIE   | 0                         | 0            | LOCKIE        | 0       | 0       | SCMIE   | 0       |  |  |

| 0x0039  | CLKSEL  | R<br>W  | PLLSEL | PSTP                      | XCLKS        | 0             | PLLWAI  | 0       | RTIWAI  | COPWAI  |  |  |

| 0x003A  | PLLCTL  | R<br>W  | CME    | PLLON                     | FM1          | FM0           | FSTWKP  | PRE     | PCE     | SCME    |  |  |

| 0x003B  | RTICTL  | R<br>W  | RTDEC  | RTR6                      | RTR5         | RTR4          | RTR3    | RTR2    | RTR1    | RTR0    |  |  |

| 0x003C  | COPCTL  | R<br>W  | WCOP   | RSBCK                     | 0<br>WRTMASK | 0             | 0       | CR2     | CR1     | CR0     |  |  |

| 0x003D  | FORBYP  | R       | 0      | 0                         | 0            | 0             | 0       | 0       | 0       | 0       |  |  |

| ONCOOL  | 1011011 | W       |        | Reserved For Factory Test |              |               |         |         |         |         |  |  |

| 0x003E  | CTCTL   | CTCTL R | 0      | 0                         | 0            | 0             | <b></b> | 0       | 0       | 0       |  |  |

|         |         | W       |        |                           | 1            | Reserved Fo   | -       |         |         |         |  |  |

| 0x003F  | ARMCOP  | R       | 0      | 0                         | 0            | 0             | 0       | 0       | 0       | 0       |  |  |

|         |         | W       | Bit 7  | 6                         | 5            | 4             | 3       | 2       | 1       | Bit 0   |  |  |

| Address | Name                    |                           | Bit 7    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0   |     |

|---------|-------------------------|---------------------------|----------|---------|-------|-------|-------|--------|--------|---------|-----|

| 0x00C8  | SCI0BDH <sup>(1)</sup>  | R<br>W                    | IREN     | TNP1    | TNP0  | SBR12 | SBR11 | SBR10  | SBR9   | SBR8    |     |

| 0x00C9  | SCI0BDL <sup>1</sup>    | R<br>W                    | SBR7     | SBR6    | SBR5  | SBR4  | SBR3  | SBR2   | SBR1   | SBR0    |     |

| 0x00CA  | SCI0CR11                | R<br>W                    | LOOPS    | SCISWAI | RSRC  | М     | WAKE  | ILT    | PE     | PT      |     |

| 0x00C8  | SCI0ASR1 <sup>(2)</sup> |                           | RXEDGIF  | 0       | 0     | 0     | 0     | BERRV  | BERRIF | BKDIF   |     |

|         |                         | W                         | INCLUGII |         |       |       |       | DENIN  |        |         |     |

| 0x00C9  | SCI0ACR1 <sup>2</sup>   | 0ACR1 <sup>2</sup> R<br>W | RXEDGIE  | 0       | 0     | 0     | 0     | 0      | BERRIE | BKDIE   |     |

|         |                         |                           | INCLUCIE |         |       |       |       |        |        | DICDIE  |     |

| 0x00CA  | SCI0ACR2 <sup>2</sup>   | R                         | 0        | 0       | 0     | 0     | 0     | BERRM1 | BERRM0 | BKDFE   |     |

|         |                         | CONTRACT                  | W        |         |       |       |       |        | DEFRIN | DEITIMO |     |

| 0x00CB  | SCI0CR2                 | R<br>W                    | TIE      | TCIE    | RIE   | ILIE  | TE    | RE     | RWU    | SBK     |     |

| 0x00CC  | SCI0SR1                 | R                         | TDRE     | TC      | RDRF  | IDLE  | OR    | NF     | FE     | PF      |     |

|         |                         | W                         |          |         |       |       |       |        |        |         |     |

| 0x00CD  | SCI0SR2                 |                           | R        | AMAP    | 0     | 0     | TXPOL | RXPOL  | BRK13  | TXDIR   | RAF |

|         |                         | W                         |          |         |       |       |       |        |        |         |     |

| 0x00CE  | SCI0DRH                 | R                         | R8 T8    | 0       | 0     | 0     | 0     | 0      | 0      |         |     |

|         |                         | W                         |          | 10      |       |       |       |        |        |         |     |

| 0x00CF  | SCI0DRL                 | R                         | R7       | R6      | R5    | R4    | R3    | R2     | R1     | R0      |     |

|         |                         | W                         | T7       | T6      | T5    | T4    | Т3    | T2     | T1     | Т0      |     |

### 0x00C8–0x00CF Asynchronous Serial Interface (SCI0) Map

1. Those registers are accessible if the AMAP bit in the SCI0SR2 register is set to zero 2. Those registers are accessible if the AMAP bit in the SCI0SR2 register is set to one

### 0x00D0-0x00D7 Asynchronous Serial Interface (SCI1) Map

| Address | Name                    |        | Bit 7   | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 |

|---------|-------------------------|--------|---------|---------|-------|-------|-------|--------|--------|-------|

| 0x00D0  | SCI1BDH <sup>(1)</sup>  | R<br>W | IREN    | TNP1    | TNP0  | SBR12 | SBR11 | SBR10  | SBR9   | SBR8  |

| 0x00D1  | SCI1BDL <sup>1</sup>    | R<br>W | SBR7    | SBR6    | SBR5  | SBR4  | SBR3  | SBR2   | SBR1   | SBR0  |

| 0x00D2  | SCI1CR1 <sup>1</sup>    | R<br>W | LOOPS   | SCISWAI | RSRC  | М     | WAKE  | ILT    | PE     | PT    |

| 0x00D0  | SCI1ASR1 <sup>(2)</sup> | R<br>W | RXEDGIF | 0       | 0     | 0     | 0     | BERRV  | BERRIF | BKDIF |

| 0x00D1  | SCI1ACR1 <sup>2</sup>   | R<br>W | RXEDGIE | 0       | 0     | 0     | 0     | 0      | BERRIE | BKDIE |

| 0x00D2  | SCI1ACR2 <sup>2</sup>   | R<br>W | 0       | 0       | 0     | 0     | 0     | BERRM1 | BERRM0 | BKDFE |

| 0x00D3  | SCI1CR2                 | R<br>W | TIE     | TCIE    | RIE   | ILIE  | TE    | RE     | RWU    | SBK   |

| 0x00D4  | SCI1SR1                 | R<br>W | TDRE    | TC      | RDRF  | IDLE  | OR    | NF     | FE     | PF    |