Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 16K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xet256w1maa |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

when the opcode is fetched from the memory. This precedes the instruction execution by an indefinite number of cycles due to instruction pipe lining. For a comparator match of an opcode at an odd address when TAG = 0, the corresponding even address must be contained in the comparator register. Thus for an opcode at odd address (n), the comparator register must contain address (n–1).

Once a successful comparator match has occurred, the condition that caused the original match is not verified again on subsequent matches. Thus if a particular data value is verified at a given address, this address may not still contain that data value when a subsequent match occurs.

Comparators C and D can also be used to select an address range to trace from. This is determined by the TRANGE bits in the DBGTCR register. The TRANGE encoding is shown in Table 8-12. If the TRANGE bits select a range definition using comparator D, then comparator D is configured for trace range definition and cannot be used for address bus comparisons. Similarly if the TRANGE bits select a range definition using comparator C is configured for trace range definition and cannot be used for address bus comparisons.

Match[0, 1, 2, 3] map directly to Comparators[A, B, C, D] respectively, except in range modes (see Section 8.3.2.4). Comparator priority rules are described in the trigger priority section (Section 8.4.3.6).

# 8.4.2.1 Exact Address Comparator Match (Comparators A and C)

With range comparisons disabled, the match condition is an exact equivalence of address/data bus with the value stored in the comparator address/data registers. Further qualification of the type of access (R/W, word/byte) is possible.

Comparators A and C do not feature SZE or SZ control bits, thus the access size is not compared. Table 8-40 lists access considerations without data bus compare. Table 8-39 lists access considerations with data bus comparison. To compare byte accesses DBGxDH must be loaded with the data byte, the low byte must be masked out using the DBGxDLM mask register. On word accesses the data byte of the lower address is mapped to DBGxDH.

| Access | Address | DBGxDH  | DBGxDL    | DBGxDHM | DBGxDLM | Example Valid Match  |         |

|--------|---------|---------|-----------|---------|---------|----------------------|---------|

| Word   | ADDR[n] | Data[n] | Data[n+1] | \$FF    | \$FF    | MOVW #\$WORD ADDR[n] | config1 |

| Byte   | ADDR[n] | Data[n] | х         | \$FF    | \$00    | MOVB #\$BYTE ADDR[n] | config2 |

| Word   | ADDR[n] | Data[n] | х         | \$FF    | \$00    | MOVW #\$WORD ADDR[n] | config2 |

| Word   | ADDR[n] | x       | Data[n+1] | \$00    | \$FF    | MOVW #\$WORD ADDR[n] | config3 |

Table 8-39. Comparator A and C Data Bus Considerations

Code may contain various access forms of the same address, i.e. a word access of ADDR[n] or byte access of ADDR[n+1] both access n+1. At a word access of ADDR[n], address ADDR[n+1] does not appear on the address bus and so cannot cause a comparator match if the comparator contains ADDR[n]. Thus it is not possible to monitor all data accesses of ADDR[n+1] with one comparator.

To detect an access of ADDR[n+1] through a word access of ADDR[n] the comparator can be configured to ADDR[n], DBGxDL is loaded with the data pattern and DBGxDHM is cleared so only the data[n+1] is compared on accesses of ADDR[n].

Add Immediate 8 bit Constant (Low Byte)

### Operation

RD +\$00:IMM8  $\Rightarrow$  RD

Adds the content of register RD and an unsigned immediate 8 bit constant using binary addition and stores the result in the destination register RD. This instruction must be used first for a 16 bit immediate addition in conjunction with the ADDH instruction.

## **CCR Effects**

| Ν | Ζ | V | С |

|---|---|---|---|

| Δ | Δ | Δ | Δ |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: Set if a two's complement overflow resulted from the 8 bit operation; cleared otherwise.  $\overline{RD[15]}_{old}$  & RD[15]<sub>new</sub>

- C: Set if there is a carry from the bit 15 of the result; cleared otherwise.  $RD[15]_{old} \& \overline{RD[15]}_{new}$

### Code and CPU Cycles

| Source Form    | Address<br>Mode | Machine Code |                   | e Code | Cycles |

|----------------|-----------------|--------------|-------------------|--------|--------|

| ADDL RD, #IMM8 | IMM8            | 1            | 1 1 1 0 0 RD IMM8 |        | Р      |

## Load Immediate 8 bit Constant (Low Byte)

### Operation

IMM8  $\Rightarrow$  RD.L; \$00  $\Rightarrow$  RD.H

Loads an 8 bit immediate constant into the low byte of register RD. The high byte is cleared.

#### **CCR Effects**

- N: Not affected.

- Z: Not affected.

- V: Not affected.

- C: Not affected.

### Code and CPU Cycles

| Source Form   | Address<br>Mode | Machine Code |   | e Code | Cycles |   |    |      |   |

|---------------|-----------------|--------------|---|--------|--------|---|----|------|---|

| LDL RD, #IMM8 | IMM8            | 1            | 1 | 1      | 1      | 0 | RD | IMM8 | Р |

## Logical OR Immediate 8 bit Constant (High Byte)

#### Operation

$RD.H \mid IMM8 \Rightarrow RD.H$

Performs a bit wise logical OR between the high byte of register RD and an immediate 8 bit constant and stores the result in the destination register RD.H. The low byte of RD is not affected.

### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | 0 | — |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the 8 bit result is \$00; cleared otherwise.

- V: 0; cleared.

- C: Not affected.

### Code and CPU Cycles

| Source Form   | Address<br>Mode | Machine Code |   | e Code | Cycles |   |    |      |   |

|---------------|-----------------|--------------|---|--------|--------|---|----|------|---|

| ORH RD, #IMM8 | IMM8            | 1            | 0 | 1      | 0      | 1 | RD | IMM8 | Р |

- General Call Address detection

- Compliant to ten-bit address

# 15.1.2 Modes of Operation

The IIC functions the same in normal, special, and emulation modes. It has two low power modes: wait and stop modes.

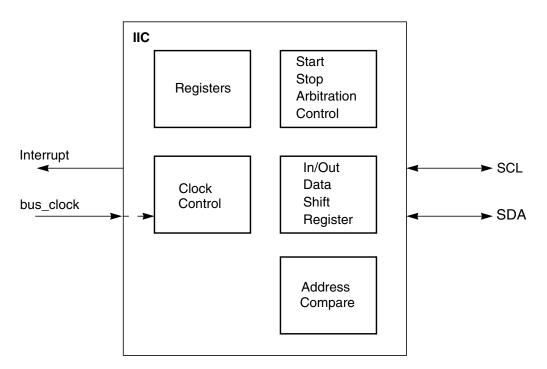

# 15.1.3 Block Diagram

The block diagram of the IIC module is shown in Figure 15-1.

# 15.2 External Signal Description

The IICV3 module has two external pins.

# 15.2.1 IIC\_SCL — Serial Clock Line Pin

This is the bidirectional serial clock line (SCL) of the module, compatible to the IIC bus specification.

# 15.2.2 IIC\_SDA — Serial Data Line Pin

This is the bidirectional serial data line (SDA) of the module, compatible to the IIC bus specification.

| IBC[7:0]<br>(hex) | SCL Divider<br>(clocks) | SDA Hold<br>(clocks) | SCL Hold<br>(start) | SCL Hold<br>(stop) |  |  |

|-------------------|-------------------------|----------------------|---------------------|--------------------|--|--|

| 82                | 88                      | 32                   | 32                  | 52                 |  |  |

| 83                | 96                      | 32                   | 36                  | 56                 |  |  |

| 84                | 104                     | 36                   | 40                  | 60                 |  |  |

| 85                | 112                     | 36                   | 44                  | 64                 |  |  |

| 86                | 128                     | 40                   | 52                  | 72                 |  |  |

| 87                | 152                     | 40                   | 64                  | 84                 |  |  |

| 88                | 112                     | 28                   | 40                  | 60                 |  |  |

| 89                | 128                     | 28                   | 48                  | 68                 |  |  |

| 8A                | 144                     | 36                   | 56                  | 76                 |  |  |

| 8B                | 160                     | 36                   | 64                  | 84                 |  |  |

| 8C                | 176                     | 44                   | 72                  | 92                 |  |  |

| 8D                | 192                     | 44                   | 80                  | 100                |  |  |

| 8E                | 224                     | 52                   | 96                  | 116                |  |  |

| 8F                | 272                     | 52                   | 120                 | 140                |  |  |

| 90                | 192                     | 36                   | 72                  | 100                |  |  |

| 91                | 224                     | 36                   | 88                  | 116                |  |  |

| 92                | 256                     | 52                   | 104                 | 132                |  |  |

| 93                | 288                     | 52                   | 120                 | 148                |  |  |

| 94                | 320                     | 68                   | 136                 | 164                |  |  |

| 95                | 352                     | 68                   | 152                 | 180                |  |  |

| 96                | 416                     | 84                   | 184                 | 212                |  |  |

| 97                | 512                     | 84                   | 232                 | 260                |  |  |

| 98                | 320                     | 36                   | 152                 | 164                |  |  |

| 99                | 384                     | 36                   | 184                 | 196                |  |  |

| 9A                | 448                     | 68                   | 216                 | 228                |  |  |

| 9B                | 512                     | 68                   | 248                 | 260                |  |  |

| 9C                | 576                     | 100                  | 280                 | 292                |  |  |

| 9D                | 640                     | 100                  | 312                 | 324                |  |  |

| 9E                | 768                     | 132                  | 376                 | 388                |  |  |

| 9F                | 960                     | 132                  | 472                 | 484                |  |  |

| A0                | 640                     | 68                   | 312                 | 324                |  |  |

| A1                | 768                     | 68                   | 376                 | 388                |  |  |

| A2                | 896                     | 132                  | 440                 | 452                |  |  |

| A3                | 1024                    | 132                  | 504                 | 516                |  |  |

| A4                | 1152                    | 196                  | 568                 | 580                |  |  |

| A5                | 1280                    | 196                  | 632                 | 644                |  |  |

| A6                | 1536                    | 260                  | 760                 | 772                |  |  |

| A7                | 1920                    | 260                  | 952                 | 964                |  |  |

| A8                | 1280                    | 132                  | 632                 | 644                |  |  |

| A9                | 1536                    | 132                  | 760                 | 772                |  |  |

| AA                | 1792                    | 260                  | 888                 | 900                |  |  |

| AB                | 2048                    | 260                  | 1016                | 1028               |  |  |

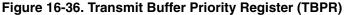

• The transmission buffer with the lowest local priority field wins the prioritization.

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

Access: User read/write<sup>(1)</sup> Module Base + 0x00XD 7 6 5 4 3 2 1 0 R PRIO7 PRIO6 PRIO4 PRIO3 PRIO2 PRIO1 PRIO0 PRIO5 w 0 Reset: 0 0 0 0 0 0 0

1. Read: Anytime when TXEx flag is set (see Section 16.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 16.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

Write: Anytime when TXEx flag is set (see Section 16.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 16.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

## 16.3.3.5 Time Stamp Register (TSRH–TSRL)

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer right after the EOF of a valid message on the CAN bus (see Section 16.3.2.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

Module Base + 0x00XE

Access: User read/write<sup>(1)</sup>

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|--------|-------|-------|-------|-------|-------|-------|------|------|

| R      | TSR15 | TSR14 | TSR13 | TSR12 | TSR11 | TSR10 | TSR9 | TSR8 |

| w      |       |       |       |       |       |       |      |      |

| Reset: | x     | x     | x     | x     | х     | x     | x    | x    |

Figure 16-37. Time Stamp Register — High Byte (TSRH)

1. Read: For transmit buffers: Anytime when TXEx flag is set (see Section 16.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 16.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). For receive buffers: Anytime when RXF is set. Write: Unimplemented

#### Table 18-8. PITMTLD0–1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMTLD[7:0] | <b>PIT Micro Timer Load Bits 7:0</b> — These bits set the 8-bit modulus down-counter load value of the micro timers. Writing a new value into the PITMTLD register will not restart the timer. When the micro timer has counted down to zero, the PMTLD register value will be loaded. The PFLMT bits in the PITCFLMT register can be used to immediately update the count register with the new value if an immediate load is desired. |

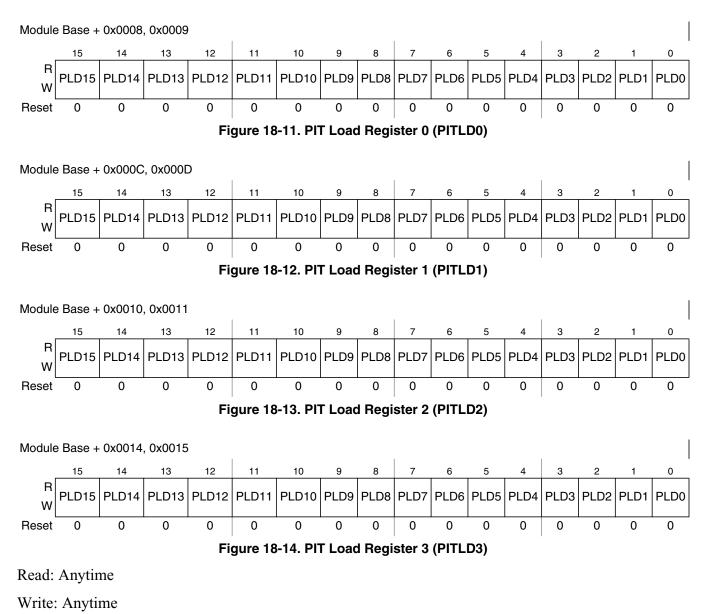

# 18.3.0.8 PIT Load Register 0 to 3 (PITLD0–3)

Enable single-wire operation by setting the LOOPS bit and the receiver source bit, RSRC, in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the RXD pin to the receiver. Setting the RSRC bit connects the TXD pin to the receiver. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1). The TXDIR bit (SCISR2[1]) determines whether the TXD pin is going to be used as an input (TXDIR = 0) or an output (TXDIR = 1) in this mode of operation.

## NOTE

In single-wire operation data from the TXD pin is inverted if RXPOL is set.

# 20.4.8 Loop Operation

In loop operation the transmitter output goes to the receiver input. The RXD pin is disconnected from the SCI.

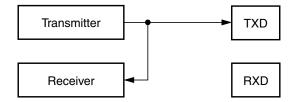

Figure 20-31. Loop Operation (LOOPS = 1, RSRC = 0)

Enable loop operation by setting the LOOPS bit and clearing the RSRC bit in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the RXD pin to the receiver. Clearing the RSRC bit connects the transmitter output to the receiver input. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1).

### NOTE

In loop operation data from the transmitter is not recognized by the receiver if RXPOL and TXPOL are not the same.

# 20.5 Initialization/Application Information

# 20.5.1 Reset Initialization

See Section 20.3.2, "Register Descriptions".

# 20.5.2 Modes of Operation

## 20.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 20.4.5.2, "Character Transmission".

When all bits are clear (the default condition), the SPI module clock is divided by 2. When the selection bits (SPR2–SPR0) are 001 and the preselection bits (SPPR2–SPPR0) are 000, the module clock divisor becomes 4. When the selection bits are 010, the module clock divisor becomes 8, etc.

When the preselection bits are 001, the divisor determined by the selection bits is multiplied by 2. When the preselection bits are 010, the divisor is multiplied by 3, etc. See Table 21-7 for baud rate calculations for all bit conditions, based on a 25 MHz bus clock. The two sets of selects allows the clock to be divided by a non-power of two to achieve other baud rates such as divide by 6, divide by 10, etc.

The baud rate generator is activated only when the SPI is in master mode and a serial transfer is taking place. In the other cases, the divider is disabled to decrease  $I_{DD}$  current.

### NOTE

For maximum allowed baud rates, please refer to the SPI Electrical Specification in the Electricals chapter of this data sheet.

# 21.4.5 Special Features

## 21.4.5.1 **SS** Output

The  $\overline{SS}$  output feature automatically drives the  $\overline{SS}$  pin low during transmission to select external devices and drives it high during idle to deselect external devices. When  $\overline{SS}$  output is selected, the  $\overline{SS}$  output pin is connected to the  $\overline{SS}$  input pin of the external device.

The  $\overline{SS}$  output is available only in master mode during normal SPI operation by asserting SSOE and MODFEN bit as shown in Table 21-3.

The mode fault feature is disabled while  $\overline{SS}$  output is enabled.

### NOTE

Care must be taken when using the  $\overline{SS}$  output feature in a multimaster system because the mode fault feature is not available for detecting system errors between masters.

# 21.4.5.2 Bidirectional Mode (MOMI or SISO)

The bidirectional mode is selected when the SPC0 bit is set in SPI control register 2 (see Table 21-11). In this mode, the SPI uses only one serial data pin for the interface with external device(s). The MSTR bit decides which pin to use. The MOSI pin becomes the serial data I/O (MOMI) pin for the master mode, and the MISO pin becomes serial data I/O (SISO) pin for the slave mode. The MISO pin in master mode and MOSI pin in slave mode are not used by the SPI.

The prescaler divides the bus clock by a prescalar value. Prescaler select bits PR[2:0] of in timer system control register 2 (TSCR2) are set to define a prescalar value that generates a divide by 1, 2, 4, 8, 16, 32, 64 and 128 when the PRNT bit in TSCR1 is disabled.

By enabling the PRNT bit of the TSCR1 register, the performance of the timer can be enhanced. In this case, it is possible to set additional prescaler settings for the main timer counter in the present timer by using PTPSR[7:0] bits of PTPSR register.

# 22.4.2 Input Capture

Clearing the I/O (input/output) select bit, IOSx, configures channel x as an input capture channel. The input capture function captures the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the timer transfers the value in the timer counter into the timer channel registers, TCx.

The minimum pulse width for the input capture input is greater than two bus clocks.

An input capture on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module or Pulse Accumulator must stay enabled (TEN bit of TSCR1 or PAEN bit of PACTL regsiter must be set to one) while clearing CxF (writing one to CxF).

# 22.4.3 Output Compare

Setting the I/O select bit, IOSx, configures channel x as an output compare channel. The output compare function can generate a periodic pulse with a programmable polarity, duration, and frequency. When the timer counter reaches the value in the channel registers of an output compare channel, the timer can set, clear, or toggle the channel pin if the corresponding OCPDx bit is set to zero. An output compare on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module or Pulse Accumulator must stay enabled (TEN bit of TSCR1 or PAEN bit of PACTL register must be set to one) while clearing CxF (writing one to CxF).

The output mode and level bits, OMx and OLx, select set, clear, toggle on output compare. Clearing both OMx and OLx results in no output compare action on the output compare channel pin.

Setting a force output compare bit, FOCx, causes an output compare on channel x. A forced output compare does not set the channel flag.

A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides output compares on all other output compare channels. The output compare 7 mask register masks the bits in the output compare 7 data register. The timer counter reset enable bit, TCRE, enables channel 7 output compares to reset the timer counter. A channel 7 output compare can reset the timer counter even if the IOC7 pin is being used as the pulse accumulator input.

Writing to the timer port bit of an output compare pin does not affect the pin state. The value written is stored in an internal latch. When the pin becomes available for general-purpose output, the last value written to the bit appears at the pin.

When TCRE is set and TC7 is not equal to 0, then TCNT will cycle from 0 to TC7. When TCNT reaches TC7 value, it lasts only one bus cycle then resets to 0.

# 24.4.2.1 Erase Verify All Blocks Command

The Erase Verify All Blocks command will verify that all P-Flash and D-Flash blocks have been erased.

Table 24-33. Erase Verify All Blocks Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |  |  |  |

|-------------|------------------|--------------|--|--|--|--|--|

| 000         | 0x01             | Not required |  |  |  |  |  |

Upon clearing CCIF to launch the Erase Verify All Blocks command, the Memory Controller will verify that the entire Flash memory space is erased. The CCIF flag will set after the Erase Verify All Blocks operation has completed.

Table 24-34. Erase Verify All Blocks Command Error Handling

| Register | Error Bit | Error Condition                                                                      |

|----------|-----------|--------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                          |

| FSTAT -  | FPVIOL    | None                                                                                 |

|          | MGSTAT1   | Set if any errors have been encountered during the read <sup>(1)</sup>               |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read <sup>1</sup> |

| FERSTAT  | EPVIOLIF  | None                                                                                 |

1. As found in the memory map for FTM256K2.

# 24.4.2.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or D-Flash block has been erased. The FCCOB upper global address bits determine which block must be verified.

Table 24-35. Erase Verify Block Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |                                                              |

|-------------|------------------|--------------------------------------------------------------|

| 000         | 0x02             | Global address [22:16] of the<br>Flash block to be verified. |

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or D-Flash block is erased. The CCIF flag will set after the Erase Verify Block operation has completed.

Offset Module Base + 0x0005

#### Table 25-15. FCNFG Field Descriptions (continued)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>FDFD | <ul> <li>Force Double Bit Fault Detect — The FDFD bit allows the user to simulate a double bit fault during Flash array read operations and check the associated interrupt routine. The FDFD bit is cleared by writing a 0 to FDFD. The FECCR registers will not be updated during the Flash array read operation with FDFD set unless an actual double bit fault is detected.</li> <li>0 Flash array read operations will set the DFDIF flag in the FERSTAT register only if a double bit fault is detected 1 Any Flash array read operation will force the DFDIF flag in the FERSTAT register to be set (see Section 25.3.2.7) and an interrupt will be generated as long as the DFDIE interrupt enable in the FERCNFG register is set (see Section 25.3.2.6)</li> </ul> |

| 0<br>FSFD | <ul> <li>Force Single Bit Fault Detect — The FSFD bit allows the user to simulate a single bit fault during Flash array read operations and check the associated interrupt routine. The FSFD bit is cleared by writing a 0 to FSFD. The FECCR registers will not be updated during the Flash array read operation with FSFD set unless an actual single bit fault is detected.</li> <li>0 Flash array read operations will set the SFDIF flag in the FERSTAT register only if a single bit fault is detected 1 Flash array read operation will force the SFDIF flag in the FERSTAT register to be set (see Section 25.3.2.7) and an interrupt will be generated as long as the SFDIE interrupt enable in the FERCNFG register is set (see Section 25.3.2.6)</li> </ul>     |

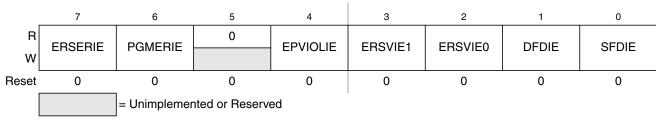

# 25.3.2.6 Flash Error Configuration Register (FERCNFG)

The FERCNFG register enables the Flash error interrupts for the FERSTAT flags.

# Figure 25-10. Flash Error Configuration Register (FERCNFG)

All assigned bits in the FERCNFG register are readable and writable.

| Field         | Description                                                                                                                                                                                                                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ERSERIE  | <ul> <li>EEE Erase Error Interrupt Enable — The ERSERIE bit controls interrupt generation when a failure is detected during an EEE erase operation.</li> <li>0 ERSERIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the ERSERIF flag is set (see Section 25.3.2.8)</li> </ul>                                           |

| 6<br>PGMERIE  | <ul> <li>EEE Program Error Interrupt Enable — The PGMERIE bit controls interrupt generation when a failure is detected during an EEE program operation.</li> <li>0 PGMERIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the PGMERIF flag is set (see Section 25.3.2.8)</li> </ul>                                       |

| 4<br>EPVIOLIE | <ul> <li>EEE Protection Violation Interrupt Enable — The EPVIOLIE bit controls interrupt generation when a protection violation is detected during a write to the buffer RAM EEE partition.</li> <li>0 EPVIOLIF interrupt disabled</li> <li>1 An interrupt will be requested whenever the EPVIOLIF flag is set (see Section 25.3.2.8)</li> </ul> |

| CCOBIX[2:0] | FCCOB Parameters                                                   |              |  |

|-------------|--------------------------------------------------------------------|--------------|--|

| 000         | 0x0F                                                               | Not required |  |

| 001         | Number of 256 byte sectors for the D-Flash user partition (DFPART) |              |  |

| 010         | Number of 256 byte sectors for buffer RAM EEE partition (ERPART)   |              |  |

#### Table 25-63. Full Partition D-Flash Command FCCOB Requirements

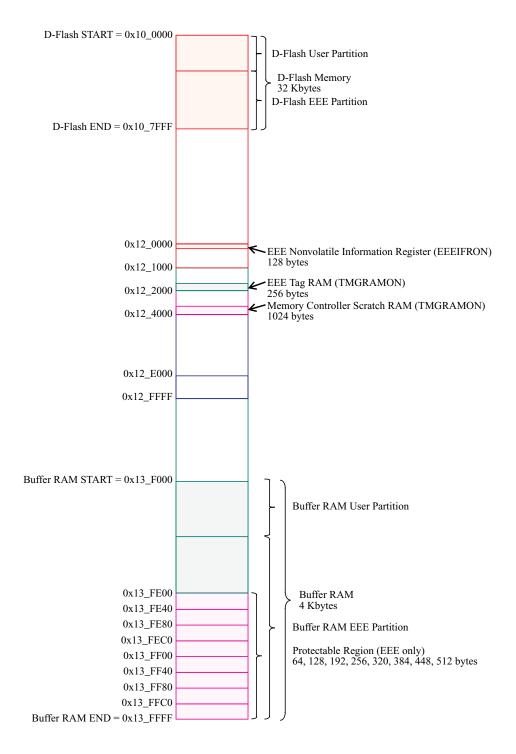

Upon clearing CCIF to launch the Full Partition D-Flash command, the following actions are taken to define a partition within the D-Flash block for direct access (DFPART) and a partition within the buffer RAM for EEE use (ERPART):

- Validate the DFPART and ERPART values provided:

- DFPART <= 128 (maximum number of 256 byte sectors in D-Flash block)

- ERPART <= 16 (maximum number of 256 byte sectors in buffer RAM)

- If ERPART > 0, 128 DFPART >= 12 (minimum number of 256 byte sectors in the D-Flash block required to support EEE)

- If ERPART > 0, ((128-DFPART)/ERPART) >= 8 (minimum ratio of D-Flash EEE space to buffer RAM EEE space to support EEE)

- Erase the D-Flash block and the EEE nonvolatile information register

- Program DFPART to the EEE nonvolatile information register at global address 0x12\_0000 (see Table 25-7)

- Program a duplicate DFPART to the EEE nonvolatile information register at global address 0x12\_0002 (see Table 25-7)

- Program ERPART to the EEE nonvolatile information register at global address 0x12\_0004 (see Table 25-7)

- Program a duplicate ERPART to the EEE nonvolatile information register at global address 0x12\_0006 (see Table 25-7)

The D-Flash user partition will start at global address  $0x10_{0000}$ . The buffer RAM EEE partition will end at global address  $0x13_{FFFF}$ . After the Full Partition D-Flash operation has completed, the CCIF flag will set.

Running the Full Partition D-Flash command a second time will result in the previous partition values and the entire D-Flash memory being erased. The data value written corresponds to the number of 256 byte sectors allocated for either direct D-Flash access (DFPART) or buffer RAM EEE access (ERPART).

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                             |

|          |           | Set if a Load Data Field command sequence is currently active           |

|          |           | Set if command not available in current mode (see Table 25-30)          |

| FSTAT    |           | Set if an invalid DFPART or ERPART selection is supplied                |

|          | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

| FERSTAT  | EPVIOLIF  | None                                                                    |

Table 25-64. Full Partition D-Flash Command Error Handling

## 25.4.2.16 Erase Verify D-Flash Section Command

The Erase Verify D-Flash Section command will verify that a section of code in the D-Flash user partition is erased. The Erase Verify D-Flash Section command defines the starting point of the data to be verified and the number of words.

Table 25-65. Erase Verify D-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                       |                                                      |

|-------------|--------------------------------------------------------|------------------------------------------------------|

| 000         | 0x10                                                   | Global address [22:16] to identify the D-Flash block |

| 001         | Global address [15:0] of the first word to be verified |                                                      |

| 010         | Number of words to be verified                         |                                                      |

Upon clearing CCIF to launch the Erase Verify D-Flash Section command, the Memory Controller will verify the selected section of D-Flash memory is erased. The CCIF flag will set after the Erase Verify D-Flash Section operation has completed.

- Program a duplicate DFPART to the EEE nonvolatile information register at global address 0x12\_0002 (see Table 27-7)

- Program ERPART to the EEE nonvolatile information register at global address 0x12\_0004 (see Table 27-7)

- Program a duplicate ERPART to the EEE nonvolatile information register at global address 0x12\_0006 (see Table 27-7)

The D-Flash user partition will start at global address  $0x10_{0000}$ . The buffer RAM EEE partition will end at global address  $0x13_{FFF}$ . After the Partition D-Flash operation has completed, the CCIF flag will set.

Running the Partition D-Flash command a second time will result in the ACCERR bit within the FSTAT register being set. The data value written corresponds to the number of 256 byte sectors allocated for either direct D-Flash access (DFPART) or buffer RAM EEE access (ERPART).

| Register | Error Bit | Error Condition                                                         |  |

|----------|-----------|-------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                             |  |

|          |           | Set if a Load Data Field command sequence is currently active           |  |

|          |           | Set if command not available in current mode (see Table 27-30)          |  |

| FSTAT    |           | Set if partitions have already been defined                             |  |

| FSTAI    |           | Set if an invalid DFPART or ERPART selection is supplied                |  |

|          | FPVIOL    | None                                                                    |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |

| FERSTAT  | EPVIOLIF  | None                                                                    |  |

Table 27-78. Partition D-Flash Command Error Handling

ter 28 768 KByte Flash Module (S12XFTM768K4V2)

1. MMCCTL1 register bit

Figure 28-3. EEE Resource Memory Map

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>CCIF          | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>0 Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                                                                                                             |  |  |

| 5<br>ACCERR        | Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 28.4.1.2) or issuing an illegal Flash command or when errors are encountered while initializing the EEE buffer ram during the reset sequence. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR. 0 No access error detected 1 Access error detected |  |  |

| 4<br>FPVIOL        | <ul> <li>Flash Protection Violation Flag — The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.</li> <li>0 No protection violation detected</li> <li>1 Protection violation detected</li> </ul>                                                             |  |  |

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0) or is handling internal EEE operations</li> </ul>                                                                                                                                                                                                                                                                                         |  |  |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 1–0<br>MGSTAT[1:0] | Memory Controller Command Completion Status Flag — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 28.4.2, "Flash Command Description," and Section 28.6, "Initialization" for details.                                                                                                                                                                                                                                                                            |  |  |

#### Table 28-17. FSTAT Field Descriptions

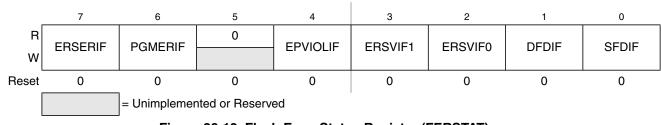

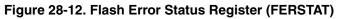

# 28.3.2.8 Flash Error Status Register (FERSTAT)

Offset Module Base + 0x0007

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

| Register | Error Bit | Error Condition                                                                                                  |  |

|----------|-----------|------------------------------------------------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                                                       |  |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                                                       |  |

|          |           | Set if a Load Data Field command sequence is currently active                                                    |  |

|          |           | Set if command not available in current mode (see Table 28-30)                                                   |  |

|          |           | Set if an invalid global address [22:0] is supplied                                                              |  |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)                                           |  |

| FSTAT    |           | Set if the global address [22:0] points to an area in the D-Flash EEE partition                                  |  |

|          |           | Set if the requested group of words breaches the end of the D-Flash block or goes into the D-Flash EEE partition |  |

|          | FPVIOL    | None                                                                                                             |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                              |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                              |  |

| FERSTAT  | EPVIOLIF  | None                                                                                                             |  |

#### Table 28-68. Program D-Flash Command Error Handling

# 28.4.2.18 Erase D-Flash Sector Command

The Erase D-Flash Sector operation will erase all addresses in a sector of the D-Flash user partition.

Table 28-69. Erase D-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                |                                                     |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| 000         | 0x12                                                                                                            | Global address [22:16] to identify<br>D-Flash block |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 28.1.2.2 for D-Flash sector size. |                                                     |  |

Upon clearing CCIF to launch the Erase D-Flash Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase D-Flash Sector operation has completed.

# Appendix E Detailed Register Address Map

The following tables show the detailed register map of the S12XE-Family.

NOTE

Smaller derivatives within the S12XE-Family feature a subset of the listed modules. Refer to Appendix D Derivative Differences for more information about derivative device module subsets.

| Address | Name  |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0000  | PORTA | R<br>W | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA 0  |

| 0x0001  | PORTB | R<br>W | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| 0x0002  | DDRA  | R<br>W | DDRA7 | DDRA6 | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 |

| 0x0003  | DDRB  | R<br>W | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| 0x0004  | PORTC | R<br>W | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| 0x0005  | PORTD | R<br>W | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| 0x0006  | DDRC  | R<br>W | DDRC7 | DDRC6 | DDRC5 | DDRC4 | DDRC3 | DDRC2 | DDRC1 | DDRC0 |

| 0x0007  | DDRD  | R<br>W | DDRD7 | DDRD6 | DDRD5 | DDRD4 | DDRD3 | DDRD2 | DDRD1 | DDRD0 |

| 0x0008  | PORTE | R<br>W | PE7   | PE6   | PE5   | PE4   | PE3   | PE2   | PE1   | PE0   |

| 0x0009  | DDRE  | R<br>W | DDRE7 | DDRE6 | DDRE5 | DDRE4 | DDRE3 | DDRE2 | 0     | 0     |

### 0x0000–0x0009 Port Integration Module (PIM) Map 1 of 6

#### 0x000A–0x000B Module Mapping Control (S12XMMC) Map 1 of 2

| Address | Name    |        | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |   |

|---------|---------|--------|-------|-------|--------|-------|-------|-------|-------|-------|---|

| 0x000A  | MMCCTL0 | R<br>W | CS3E1 | CS2E1 | CS1E1  | CS0E1 | CS3E0 | CS2E0 | CS1E0 | CS0E0 |   |

| 0x000B  | MODE    | MODE   | R     | MODC  | MODB   | MODA  | 0     | 0     | 0     | 0     | 0 |

|         |         | W      | MODO  | NODB  | IVIODA |       |       |       |       |       |   |

#### 0x000C–0x000D Port Integration Module (PIM) Map 2 of 6

| Address | Name  |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x000C  | PUCR  | R | PUPKE | BKPUE | 0     | PUPEE | PUPDE | PUPCE | PUPBE | PUPAE |

|         |       | W |       |       |       |       |       |       |       |       |

| 0x000D  | RDRIV | R | RDPK  | 0 0   | 0     | RDPE  | RDPD  | RDPC  | RDPB  | RDPA  |

|         |       | W | HEIR  |       |       |       |       |       |       |       |