Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SPI                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xet256w1mal |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device                                | 0x70_0000 | 0x74_0000 | 0x78_0000 | 0x7A_0000 | 0x7C_0000 | 0x7E_0000 |

|---------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| 9S12XET256<br>9S12XEA256<br>(1)       | _         | _         | B1S       | _         | _         | B0(128K)  |

| 9S12XEG128<br>9S12XEA128 <sup>1</sup> | _         | _         | B1S (64K) | _         | _         | B0 (64K)  |

Table 1-5. Derivative Dependent Flash Block Mapping (continued)

The 9S12XEA devices are special bondouts for access to extra ADC channels in 80QFP. Available in 80QFP only. WARNING: NOT PIN-COMPATIBLE WITH REST OF FAMILY.

Block B1 is divided into two 128K blocks. The XGATE is always mapped to block B1S.

On the 9S12XEG128 the flash is divided into two 64K blocks B0 and B1S, the B1S range extending from 0x78\_0000 to 0x78\_FFFF, the B0 range extending from 0x7F\_0000 to 0x7F\_FFFF.

The block B0 is a reduced size 128K block on the 256K derivative. On the larger derivatives B0 is a 256K block. The block B0 is a reduced size 64K block on the 128K derivative.

# 1.4.2.4 XGATE Fake Activity Mode

This mode is entered if the CPU executes the STOP instruction when the XGATE is not executing a thread and the XGFACT bit in the XGMCTL register is set. The oscillator remains active and any enabled peripherals continue to function.

# 1.4.2.5 Wait Mode

This mode is entered when the CPU executes the WAI instruction. In this mode the CPU will not execute instructions. The internal CPU clock is switched off. All peripherals and the XGATE can be active in system wait mode. For further power consumption the peripherals can individually turn off their local clocks. Asserting  $\overline{\text{RESET}}$ ,  $\overline{\text{XIRQ}}$ ,  $\overline{\text{IRQ}}$  or any other interrupt that is not masked and is not routed to XGATE ends system wait mode.

## 1.4.2.6 Run Mode

Although this is not a low-power mode, unused peripheral modules should not be enabled in order to save power.

# 1.4.3 Freeze Mode

The enhanced capture timer, pulse width modulator, analog-to-digital converters, and the periodic interrupt timer provide a software programmable option to freeze the module status when the background debug module is active. This is useful when debugging application software. For detailed description of the behavior of the ATD0, ATD1, ECT, PWM, and PIT when the background debug module is active consult the corresponding Block Guides.

# 1.4.4 System States

To facilitate system integrity the MCU can run in Supervisor state or User state. The System States strategy is implemented by additional features on the S12X CPU and a Memory Protection Unit. This is designed to support restricted access for code modules executed by kernels or operating systems supporting access control to system resources.

The current system state is indicated by the U bit in the CPU condition code register. In User state certain CPU instructions are restricted. See the CPU reference guide for details of the U bit and of those instructions affected by User state.

In the case that software task accesses resources outside those defined for it in the MPU a non-maskable interrupt is generated.

## 1.4.4.1 Supervisor State

This state is intended for configuring the MPU for different tasks that are then executed in User state, returning to Supervisor state on completion of each task. This is the default 'state' following reset and can be re-entered from User state by an exception (interrupt). If the SVSEN bit in the MPUSEL register of the

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RDPB | <ul> <li>Port B reduced drive—Select reduced drive for outputs</li> <li>This bit configures the drive strength of all output pins as either full or reduced independent of the function used on the pins. If a pin is used as input this bit has no effect.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength).</li> <li>0 Full drive strength enabled.</li> </ul> |

| 0<br>RDPA | <ul> <li>Port A reduced drive—Select reduced drive for outputs</li> <li>This bit configures the drive strength of all output pins as either full or reduced independent of the function used on the pins. If a pin is used as input this bit has no effect.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength).</li> <li>0 Full drive strength enabled.</li> </ul> |

#### 2.3.15 **ECLK Control Register (ECLKCTL)**

Address 0x001C (PRR)

Access: User read/write<sup>(1)</sup>

| _                      | 7                      | 6            | 5               | 4     | 3     | 2     | 1     | 0     |

|------------------------|------------------------|--------------|-----------------|-------|-------|-------|-------|-------|

| R<br>W                 | NECLK                  | NCLKX2       | DIV16           | EDIV4 | EDIV3 | EDIV2 | EDIV1 | EDIV0 |

| Reset <sup>(2)</sup> : | Mode<br>Depen-<br>dent | 1            | 0               | 0     | 0     | 0     | 0     | 0     |

| SS                     | 0                      | 1            | 0               | 0     | 0     | 0     | 0     | 0     |

| ES                     | 1                      | 1            | 0               | 0     | 0     | 0     | 0     | 0     |

| ST                     | 0                      | 1            | 0               | 0     | 0     | 0     | 0     | 0     |

| EX                     | 0                      | 1            | 0               | 0     | 0     | 0     | 0     | 0     |

| NS                     | 1                      | 1            | 0               | 0     | 0     | 0     | 0     | 0     |

| NX                     | 0                      | 1            | 0               | 0     | 0     | 0     | 0     | 0     |

|                        |                        | = Unimplemen | ited or Reserve | ed    |       |       |       |       |

Figure 2-13. ECLK Control Register (ECLKCTL) 1. Read: Anytime. In emulation modes, read operations will return the data from the external bus, in all other modes the data source is depending on the data direction value.

Write: Anytime. In emulation modes, write operations will also be directed to the external bus.

2. Reset values in emulation modes are identical to those of the target mode.

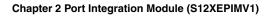

# 2.3.48 Port P Reduced Drive Register (RDRP)

Write: Anytime.

#### Table 2-44. RDRP Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>RDRP | <ul> <li>Port P reduced drive—Select reduced drive for outputs</li> <li>This register configures the drive strength of output pins 7 through 0 as either full or reduced independent of the function used on the pins. If a pin is used as input this bit has no effect.</li> <li>1 Reduced drive selected (approx. 1/5 of the full drive strength).</li> <li>0 Full drive strength enabled.</li> </ul> |

# 2.3.49 Port P Pull Device Enable Register (PERP)

Address 0x025C

Access: User read/write<sup>(1)</sup>

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | PPSP7 | PPSP6 | PPSP5 | PPSP4 | PPSP3 | PPSP2 | PPSP1 | PPSP0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Figure 2-47. Port P Pull Device Enable Register (PERP)

1. Read: Anytime. Write: Anytime.

#### Table 2-45. PERP Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PERP | <ul> <li>Port P pull device enable—Enable pull devices on input pins</li> <li>These bits configure whether a pull device is activated, if the associated pin is used as an input. This bit has no effect if the pin is used as an output. Out of reset no pull device is enabled.</li> <li>1 Pull device enabled.</li> <li>0 Pull device disabled.</li> </ul> |

# Chapter 9 Security (S12XE9SECV2)

| Revision<br>Number | Revision Date | Sections<br>Affected | Description of Changes                                                |

|--------------------|---------------|----------------------|-----------------------------------------------------------------------|

| V02.00             | 27 Aug 2004   |                      | - Reviewed and updated for S12XD architecture                         |

| V02.01             | 21 Feb 2007   |                      | - Added S12XE, S12XF and S12XS architectures                          |

| V02.02             | 19 Apr 2007   |                      | - Corrected statement about Backdoor key access via BDM on XE, XF, XS |

#### Table 9-1. Revision History

# 9.1 Introduction

This specification describes the function of the security mechanism in the S12XE chip family (9SEC).

#### NOTE

No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH and/or EEPROM difficult for unauthorized users.

## 9.1.1 Features

The user must be reminded that part of the security must lie with the application code. An extreme example would be application code that dumps the contents of the internal memory. This would defeat the purpose of security. At the same time, the user may also wish to put a backdoor in the application program. An example of this is the user downloads a security key through the SCI, which allows access to a programming routine that updates parameters stored in another section of the Flash memory.

The security features of the S12XE chip family (in secure mode) are:

- Protect the content of non-volatile memories (Flash, EEPROM)

- Execution of NVM commands is restricted

- Disable access to internal memory via background debug module (BDM)

- Disable access to internal Flash/EEPROM in expanded modes

- Disable debugging features for the CPU and XGATE

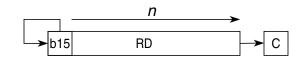

## Arithmetic Shift Right

#### Operation

#### n = RS or IMM4

Shifts the bits in register RD *n* positions to the right. The higher *n* bits of the register RD become filled with the sign bit (RD[15]). The carry flag will be updated to the bit contained in RD[n-1] before the shift for n > 0.

*n* can range from 0 to 16.

In immediate address mode, *n* is determined by the operand IMM4. *n* is considered to be 16 if IMM4 is equal to 0.

In dyadic address mode, *n* is determined by the content of RS. *n* is considered to be 16 if the content of RS is greater than 15.

#### **CCR Effects**

| Ν | z | v | С |

|---|---|---|---|

| Δ | Δ | Δ | Δ |

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the result is \$0000; cleared otherwise.

- V: Set if a two's complement overflow resulted from the operation; cleared otherwise.  $RD[15]_{old} \wedge RD[15]_{new}$

- C: Set if n > 0 and RD[n-1] = 1; if n = 0 unaffected.

#### Code and CPU Cycles

| Source Form   | Address<br>Mode | Machine Code |   |   |   |   | Cycles |      |   |   |   |   |   |   |

|---------------|-----------------|--------------|---|---|---|---|--------|------|---|---|---|---|---|---|

| ASR RD, #IMM4 | IMM4            | 0            | 0 | 0 | 0 | 1 | RD     | IMM4 |   | 1 | 0 | 0 | 1 | Р |

| ASR RD, RS    | DYA             | 0            | 0 | 0 | 0 | 1 | RD     | RS   | 1 | 0 | 0 | 0 | 1 | Р |

| DLY7 | DLY6 | DLY5 | DLY4 | DLY3 | DLY2 | DLY1 | DLY0 | Delay                 |

|------|------|------|------|------|------|------|------|-----------------------|

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 32 bus clock cycles   |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 64 bus clock cycles   |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 128 bus clock cycles  |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 256 bus clock cycles  |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 512 bus clock cycles  |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1024 bus clock cycles |

Table 14-29. Delay Counter Select Examples when PRNT = 1

## 14.3.2.23 Input Control Overwrite Register (ICOVW)

Module Base + 0x002A

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | NOVW7 | NOVW6 | NOVW5 | NOVW4 | NOVW3 | NOVW2 | NOVW1 | NOVW0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 14-46. Input Control Overwrite Register (ICOVW)

Read: Anytime

Write: Anytime

All bits reset to zero.

| Table 14-30. ICOVW Field Descriptions | Table 14-30. | ICOVW | Field | Descriptions |

|---------------------------------------|--------------|-------|-------|--------------|

|---------------------------------------|--------------|-------|-------|--------------|

| Field     | Description                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0       | No Input Capture Overwrite                                                                                                                                                                                                                                |

| NOVW[7:0] | 0 The contents of the related capture register or holding register can be overwritten when a new input capture or latch occurs.                                                                                                                           |

|           | 1 The related capture register or holding register cannot be written by an event unless they are empty (see Section 14.4.1.1, "IC Channels"). This will prevent the captured value being overwritten until it is read or latched in the holding register. |

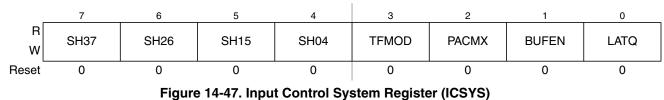

# 14.3.2.24 Input Control System Control Register (ICSYS)

Module Base + 0x002B

Read: Anytime

Write: Once in normal modes

MC9S12XE-Family Reference Manual Rev. 1.25

#### Table 17-5. PITMUX Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PMUX[7:0] | <ul> <li>PIT Multiplex Bits for Timer Channel 7:0 — These bits select if the corresponding 16-bit timer is connected to micro time base 1 or 0. If PMUX is modified, the corresponding 16-bit timer is immediately switched to the other micro time base.</li> <li>0 The corresponding 16-bit timer counts with micro time base 0.</li> <li>1 The corresponding 16-bit timer counts with micro time base 1.</li> </ul> |

## 17.3.0.5 PIT Interrupt Enable Register (PITINTE)

Module Base + 0x0004

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PINTE7 | PINTE6 | PINTE5 | PINTE4 | PINTE3 | PINTE2 | PINTE1 | PINTE0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 17-7. PIT Interrupt Enable Register (PITINTE)

Read: Anytime

Write: Anytime

#### Table 17-6. PITINTE Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PINTE[7:0] | <ul> <li>PIT Time-out Interrupt Enable Bits for Timer Channel 7:0 — These bits enable an interrupt service request whenever the time-out flag PTF of the corresponding PIT channel is set. When an interrupt is pending (PTF set) enabling the interrupt will immediately cause an interrupt. To avoid this, the corresponding PTF flag has to be cleared first.</li> <li>0 Interrupt of the corresponding PIT channel is disabled.</li> <li>1 Interrupt of the corresponding PIT channel is enabled.</li> </ul> |

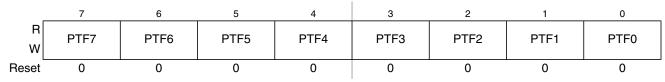

# 17.3.0.6 PIT Time-Out Flag Register (PITTF)

Module Base + 0x0005

Figure 17-8. PIT Time-Out Flag Register (PITTF)

Read: Anytime

Write: Anytime (write to clear)

NP

ter 18 Periodic Interrupt Timer (S12PIT24B4CV2)

| Register<br>Name              | Bit 7  | 6          | 5             | 4      | 3      | 2      | 1     | Bit 0 |

|-------------------------------|--------|------------|---------------|--------|--------|--------|-------|-------|

| 0x000F R<br>PITCNT1 (Low) W   | PCNT7  | PCNT6      | PCNT5         | PCNT4  | PCNT3  | PCNT2  | PCNT1 | PCNT0 |

| 0x0010 R<br>PITLD2 (High) W   | PLD15  | PLD14      | PLD13         | PLD12  | PLD11  | PLD10  | PLD9  | PLD8  |

| 0x0011 R<br>PITLD2 (Low) W    | PLD7   | PLD6       | PLD5          | PLD4   | PLD3   | PLD2   | PLD1  | PLD0  |

| 0x0012 R<br>PITCNT2 (High) W  | PCNT15 | PCNT14     | PCNT13        | PCNT12 | PCNT11 | PCNT10 | PCNT9 | PCNT8 |

| 0x0013 R<br>PITCNT2 (Low) W   | PCNT7  | PCNT6      | PCNT5         | PCNT4  | PCNT3  | PCNT2  | PCNT1 | PCNT0 |

| 0x0014 R<br>PITLD3 (High) W   | PLD15  | PLD14      | PLD13         | PLD12  | PLD11  | PLD10  | PLD9  | PLD8  |

| 0x0015 R<br>PITLD3 (Low) W    | PLD7   | PLD6       | PLD5          | PLD4   | PLD3   | PLD2   | PLD1  | PLD0  |

| 0x0016 R<br>PITCNT3 (High) W  | PCNT15 | PCNT14     | PCNT13        | PCNT12 | PCNT11 | PCNT10 | PCNT9 | PCNT8 |

| 0x0017 R<br>PITCNT3 (Low) W   | PCNT7  | PCNT6      | PCNT5         | PCNT4  | PCNT3  | PCNT2  | PCNT1 | PCNT0 |

| 0x0018–0x0027 R<br>RESERVED W | 0      | 0          | 0             | 0      | 0      | 0      | 0     | 0     |

|                               |        | = Unimplem | ented or Rese | erved  |        |        |       |       |

Figure 18-2. PIT Register Summary (Sheet 2 of 2)

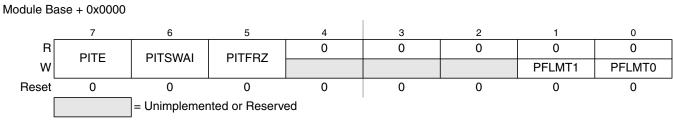

# 18.3.0.1 PIT Control and Force Load Micro Timer Register (PITCFLMT)

Read: Anytime

Write: Anytime; writes to the reserved bits have no effect

Write: Anytime (any value written causes PWM counter to be reset to \$00).

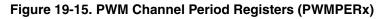

# 19.3.2.13 PWM Channel Period Registers (PWMPERx)

There is a dedicated period register for each channel. The value in this register determines the period of the associated PWM channel.

The period registers for each channel are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to \$00)

- The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period register will go directly to the latches as well as the buffer.

#### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active period due to the double buffering scheme.

See Section 19.4.2.3, "PWM Period and Duty" for more information.

To calculate the output period, take the selected clock source period for the channel of interest (A, B, SA, or SB) and multiply it by the value in the period register for that channel:

- Left aligned output (CAEx = 0)

- PWMx Period=Channel Clock Period \* PWMPERx Center Aligned Output (CAEx=1) PWMx Period = Channel Clock Period \* (2 \* PWMPERx)

For boundary case programming values, please refer to Section 19.4.2.8, "PWM Boundary Cases".

Module Base + 0x0014 = PWMPER0, 0x0015 = PWMPER1, 0x0016 = PWMPER2, 0x0017 = PWMPER3 Module Base + 0x0018 = PWMPER4, 0x0019 = PWMPER5, 0x001A = PWMPER6, 0x001B = PWMPER7

Read: Anytime

Write: Anytime

Read: Anytime but will always return 0x0000 (1 state is transient)

Write: Anytime

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FOC[7:0] | <ul> <li>Force Output Compare Action for Channel 7:0 — A write to this register with the corresponding data bit(s) set causes the action which is programmed for output compare "x" to occur immediately. The action taken is the same as if a successful comparison had just taken place with the TCx register except the interrupt flag does not get set.</li> <li>Note: A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. If forced output compare on any channel occurs at the same time as the successful output compare then forced output compare action will take precedence and interrupt flag won't get set.</li> </ul> |

# 22.3.2.3 Output Compare 7 Mask Register (OC7M)

Module Base + 0x0002

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | OC7M7 | OC7M6 | OC7M5 | OC7M4 | OC7M3 | OC7M2 | OC7M1 | OC7M0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 22-8. Output Compare 7 Mask Register (OC7M)

Read: Anytime

Write: Anytime

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare 7 Mask — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>0 The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>1 The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 and OCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| CCOBIX[2:0] | FCCOB P                                     | FCCOB Parameters          |  |  |  |  |  |  |  |

|-------------|---------------------------------------------|---------------------------|--|--|--|--|--|--|--|

| 000         | 0x07                                        | Not Required              |  |  |  |  |  |  |  |

| 001         | Program Once phrase index (0x0000 - 0x0007) |                           |  |  |  |  |  |  |  |

| 010         | Program Once word 0 value                   |                           |  |  |  |  |  |  |  |

| 011         | Program Once word 1 value                   |                           |  |  |  |  |  |  |  |

| 100         | Program Once                                | Program Once word 2 value |  |  |  |  |  |  |  |

| 101         | Program Once                                | e word 3 value            |  |  |  |  |  |  |  |

| Table 25-45. P | Program Once | <b>Command FCCOB</b> | Requirements |

|----------------|--------------|----------------------|--------------|

|----------------|--------------|----------------------|--------------|

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash block 0 will return invalid data.

| Register | Error Bit | Error Condition                                                                     |  |  |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 101 at command launch                                         |  |  |  |  |  |  |

|          |           | Set if a Load Data Field command sequence is currently active                       |  |  |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 25-30)                      |  |  |  |  |  |  |

|          |           | Set if an invalid phrase index is supplied                                          |  |  |  |  |  |  |

| FSTAT    |           | Set if the requested phrase has already been programmed <sup>(1)</sup>              |  |  |  |  |  |  |

|          | FPVIOL    | None                                                                                |  |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |  |  |  |

|          | MGSTATO   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |  |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                                |  |  |  |  |  |  |

Table 25-46. Program Once Command Error Handling

## 25.4.2.8 Erase All Blocks Command

The Erase All Blocks operation will erase the entire P-Flash and D-Flash memory space including the EEE nonvolatile information register.

#### 26.4.1.3 Valid Flash Module Commands

| Table 26-30. | Flash | Commands | by | Mode |

|--------------|-------|----------|----|------|

|--------------|-------|----------|----|------|

|      |                              |           | Unse      | cured             |                   | Secured   |           |                   |                   |

|------|------------------------------|-----------|-----------|-------------------|-------------------|-----------|-----------|-------------------|-------------------|

| FCMD | Command                      | NS<br>(1) | NX<br>(2) | SS <sup>(3)</sup> | ST <sup>(4)</sup> | NS<br>(5) | NX<br>(6) | SS <sup>(7)</sup> | ST <sup>(8)</sup> |

| 0x01 | Erase Verify All Blocks      | *         | *         | *                 | *                 | *         | *         | *                 | *                 |

| 0x02 | Erase Verify Block           | *         | *         | *                 | *                 | *         | *         | *                 | *                 |

| 0x03 | Erase Verify P-Flash Section | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x04 | Read Once                    | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x05 | Load Data Field              | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x06 | Program P-Flash              | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x07 | Program Once                 | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x08 | Erase All Blocks             |           |           | *                 | *                 |           |           | *                 | *                 |

| 0x09 | Erase P-Flash Block          | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x0A | Erase P-Flash Sector         | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x0B | Unsecure Flash               |           |           | *                 | *                 |           |           | *                 | *                 |

| 0x0C | Verify Backdoor Access Key   | *         |           |                   |                   | *         |           |                   |                   |

| 0x0D | Set User Margin Level        | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x0E | Set Field Margin Level       |           |           | *                 | *                 |           |           |                   |                   |

| 0x0F | Full Partition D-Flash       |           |           | *                 | *                 |           |           |                   |                   |

| 0x10 | Erase Verify D-Flash Section | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x11 | Program D-Flash              | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x12 | Erase D-Flash Sector         | *         | *         | *                 | *                 | *         |           |                   |                   |

| 0x13 | Enable EEPROM Emulation      | *         | *         | *                 | *                 | *         | *         | *                 | *                 |

| 0x14 | Disable EEPROM Emulation     | *         | *         | *                 | *                 | *         | *         | *                 | *                 |

| 0x15 | EEPROM Emulation Query       | *         | *         | *                 | *                 | *         | *         | *                 | *                 |

| 0x20 | Partition D-Flash            | *         | *         | *                 | *                 | *         | *         | *                 | *                 |

1. Unsecured Normal Single Chip mode.

2. Unsecured Normal Expanded mode.

3. Unsecured Special Single Chip mode.

4. Unsecured Special Mode.

5. Secured Normal Single Chip mode.

6. Secured Normal Expanded mode.

7. Secured Special Single Chip mode.

8. Secured Special Mode.

| Global Address          | Size<br>(Bytes) | Description                                                        |

|-------------------------|-----------------|--------------------------------------------------------------------|

| 0x10_0000 - 0x10_7FFF   | 32,768          | D-Flash Memory (User and EEE)                                      |

| 0x10_8000 - 0x11_FFFF   | 98,304          | Reserved                                                           |

| 0x12_0000 - 0x12_007F   | 128             | EEE Nonvolatile Information Register (EEEIFRON <sup>(1)</sup> = 1) |

| 0x12_0080 - 0x12_0FFF   | 3,968           | Reserved                                                           |

| 0x12_1000 - 0x12_1EFF   | 3,840           | Reserved                                                           |

| 0x12_1F00 - 0x12_1FFF   | 256             | EEE Tag RAM (TMGRAMON <sup>1</sup> = 1)                            |

| 0x12_2000 - 0x12_3BFF   | 7,168           | Reserved                                                           |

| 0x12_3C00 - 0x12_3FFF   | 1,024           | Memory Controller Scratch RAM (TMGRAMON <sup>1</sup> = 1)          |

| 0x12_4000 - 0x12_DFFF   | 40,960          | Reserved                                                           |

| 0x12_E000 - 0x12_FFFF   | 8,192           | Reserved                                                           |

| 0x13_0000 - 0x13_EFFF   | 61,440          | Reserved                                                           |

| 0x13_F000 - 0x13_FFFF   | 4,096           | Buffer RAM (User and EEE)                                          |

| 1. MMCCTL1 register bit |                 |                                                                    |

#### Table 29-6. EEE Resource Fields

ter 29 1024 KByte Flash Module (S12XFTM1024K5V2)

- Program a duplicate DFPART to the EEE nonvolatile information register at global address 0x12\_0002 (see Table 29-7)

- Program ERPART to the EEE nonvolatile information register at global address 0x12\_0004 (see Table 29-7)

- Program a duplicate ERPART to the EEE nonvolatile information register at global address 0x12\_0006 (see Table 29-7)

The D-Flash user partition will start at global address  $0x10_{0000}$ . The buffer RAM EEE partition will end at global address  $0x13_{FFF}$ . After the Partition D-Flash operation has completed, the CCIF flag will set.

Running the Partition D-Flash command a second time will result in the ACCERR bit within the FSTAT register being set. The data value written corresponds to the number of 256 byte sectors allocated for either direct D-Flash access (DFPART) or buffer RAM EEE access (ERPART).

| Register | Error Bit | Error Condition                                                         |  |  |  |  |  |  |

|----------|-----------|-------------------------------------------------------------------------|--|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                             |  |  |  |  |  |  |

|          |           | Set if a Load Data Field command sequence is currently active           |  |  |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 29-30)          |  |  |  |  |  |  |

| FSTAT    |           | Set if partitions have already been defined                             |  |  |  |  |  |  |

| FSTAI    |           | Set if an invalid DFPART or ERPART selection is supplied                |  |  |  |  |  |  |

|          | FPVIOL    | None                                                                    |  |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |  |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |  |  |  |  |  |

| FERSTAT  | EPVIOLIF  | None                                                                    |  |  |  |  |  |  |

Table 29-78. Partition D-Flash Command Error Handling

This section describes the characteristics of all I/O pins except EXTAL, XTAL, TEST and supply pins.

| Num | С | Rating                                                                                                                                                                                                                                                                                | Symbol                               | Min                     | Тур | Max                     | Unit |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------|-----|-------------------------|------|

| 1   | Р | Input high voltage                                                                                                                                                                                                                                                                    | V <sub>IH</sub>                      | 0.65*V <sub>DD35</sub>  | _   | _                       | v    |

|     | т | Input high voltage                                                                                                                                                                                                                                                                    | V <sub>IH</sub>                      | —                       | —   | V <sub>DD35</sub> + 0.3 | v    |

| 2   | Р | Input low voltage                                                                                                                                                                                                                                                                     | V <sub>IL</sub>                      | _                       | _   | 0.35*V <sub>DD35</sub>  | V    |

|     | т | Input low voltage                                                                                                                                                                                                                                                                     | V <sub>IL</sub>                      | V <sub>SS35</sub> – 0.3 | —   | —                       | V    |

| 3   | Т | Input hysteresis                                                                                                                                                                                                                                                                      | V <sub>HYS</sub>                     | _                       | 250 | _                       | mV   |

| 4a  | Ρ | <ul> <li>Input leakage current (pins in high impedance input mode)<sup>(1)</sup> V<sub>in</sub> = V<sub>DD35</sub> or V<sub>SS35</sub></li> <li>M Temperature range -40°C to 150°C</li> <li>V Temperature range -40°C to 130°C</li> <li>C Temperature range -40°C to 110°C</li> </ul> |                                      | -1<br>-0.75<br>-0.5     |     | 1<br>0.75<br>0.5        | μΑ   |

| 4b  | С | Input leakage current (pins in high impedance input mode) $V_{in} = V_{DD35}$ or $V_{SS35}$<br>-40°C<br>27°C<br>70°C<br>85°C<br>100°C<br>105°C<br>110°C<br>120°C<br>125°C<br>130°C<br>130°C<br>150°C                                                                                  | I <sub>in</sub>                      |                         |     |                         | nA   |

| 5   | С | Output high voltage (pins in output mode)<br>Partial drive $I_{OH} = -0.75$ mA                                                                                                                                                                                                        | V <sub>OH</sub>                      | V <sub>DD35</sub> - 0.4 | _   | _                       | V    |

| 6   | Ρ | Output high voltage (pins in output mode)<br>Full drive I <sub>OH</sub> = -4 mA                                                                                                                                                                                                       | V <sub>OH</sub>                      | V <sub>DD35</sub> – 0.4 |     | _                       | V    |

| 7   | С | Output low voltage (pins in output mode)<br>Partial Drive I <sub>OL</sub> = +0.9 mA                                                                                                                                                                                                   | V <sub>OL</sub>                      | _                       | _   | 0.4                     | V    |

| В   | Ρ | Output low voltage (pins in output mode)<br>Full Drive I <sub>OL</sub> = +4.75 mA                                                                                                                                                                                                     | V <sub>OL</sub>                      | —                       | —   | 0.4                     | V    |

| 9   | Ρ | Internal pull up resistance<br>V <sub>IH</sub> min > input voltage > V <sub>IL</sub> max                                                                                                                                                                                              | R <sub>PUL</sub>                     | 25                      | —   | 50                      | KΩ   |

| 10  | Ρ | Internal pull down resistance<br>V <sub>IH</sub> min > input voltage > V <sub>IL</sub> max                                                                                                                                                                                            | R <sub>PDH</sub>                     | 25                      | —   | 50                      | KΩ   |

| 11  | D | Input capacitance                                                                                                                                                                                                                                                                     | C <sub>in</sub>                      | -                       | 6   | —                       | pF   |

| 12  | т | Injection current <sup>(2)</sup><br>Single pin limit<br>Total device limit, sum of all injected currents                                                                                                                                                                              | I <sub>ICS</sub><br>I <sub>ICP</sub> | -2.5<br>-25             | —   | 2.5<br>25               | mA   |

| 13  | D | Port H, J, P interrupt input pulse filtered (STOP) <sup>(3)</sup>                                                                                                                                                                                                                     | t <sub>PULSE</sub>                   | <b> </b> _              | _   | 3                       | μs   |

#### Table A-7. 3.3-V I/O Characteristics

| Peripheral | Configuration                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S12XCPU    | 420 cycle loop: 384 DBNE cycles plus subroutine entry to stimulate stacking (RAM access)                                                                                          |

| XGATE      | XGATE fetches code from RAM, XGATE runs in an infinite loop, reading the Status and Flag registers of CAN's, SPI's, SCI's in sequence and doing some bit manipulation on the data |

| MSCAN      | Configured to loop-back mode using a bit rate of 500kbit/s                                                                                                                        |

| SPI        | Configured to master mode, continuously transmit data (0x55 or 0xAA) at 2Mbit/s                                                                                                   |

| SCI        | Configured into loop mode, continuously transmit data (0x55) at speed of 19200 baud                                                                                               |

| IIC        | Operate in master mode and continuously transmit data (0x55 or 0xAA) at 100Kbit/s                                                                                                 |

| PWM        | Configured to toggle its pins at the rate of 1kHz                                                                                                                                 |

| ECT        | The peripheral shall be configured in output compare mode. Pulse accumulator and modulus counter enabled.                                                                         |

| ATD        | The peripheral is configured to operate at its maximum specified frequency and to continuously convert voltages on all input channels in sequence.                                |

| PIT        | PIT is enabled, Micro-timer register 0 and 1 loaded with \$0F and timer registers 0 to 3 are loaded with \$03/07/0F/1F.                                                           |

| RTI        | Enabled with RTI Control Register (RTICTL) set to \$59                                                                                                                            |

| Overhead   | VREG supplying 1.8V from a 5V input voltage, core clock tree active, PLL on                                                                                                       |

#### Table A-10. Module Configurations for Typical Run Supply Current $V_{DD35} {=} 5V$

# Table A-11. Module Configurations for Maximum Run Supply Current $V_{DD35} {=} 5.5 V$

| Peripheral | Configuration                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S12XCPU    | 420 cycle loop: 384 DBNE cycles plus subroutine entry to stimulate stacking (RAM access)                                                                                          |

| XGATE      | XGATE fetches code from RAM, XGATE runs in an infinite loop, reading the Status and Flag registers of CAN's, SPI's, SCI's in sequence and doing some bit manipulation on the data |

| MSCAN      | Configured to loop-back mode using a bit rate of 1Mbit/s                                                                                                                          |

| SPI        | Configured to master mode, continuously transmit data (0x55 or 0xAA) at 4Mbit/s                                                                                                   |

| SCI        | Configured into loop mode, continuously transmit data (0x55) at speed of 57600 baud                                                                                               |

| IIC        | Operate in master mode and continuously transmit data (0x55 or 0xAA) at 100Kbit/s                                                                                                 |

| PWM        | Configured to toggle its pins at the rate of 40kHz                                                                                                                                |

| ECT        | The peripheral shall be configured in output compare mode. Pulse accumulator and modulus counter enabled.                                                                         |

| ATD        | The peripheral is configured to operate at its maximum specified frequency and to continuously convert voltages on all input channels in sequence.                                |

| Overhead   | VREG supplying 1.8V from a 5V input voltage, PLL on                                                                                                                               |

| Device                       | Package    | XGATE | CAN | SCI | SPI | IIC      | ECT | TIM <sup>(1)</sup> | PIT | A/D               | I/O |

|------------------------------|------------|-------|-----|-----|-----|----------|-----|--------------------|-----|-------------------|-----|

| 9S12XEP100                   | 208 MAPBGA |       | 5   | 8   | 3   | 2        | 8ch | 8ch                | 8ch | 2/32              | 152 |

|                              | 144LQFP    |       | 5   | 8   | 3   | 2        | 8ch | 8ch                | 8ch | 2/24              | 119 |

|                              | 112LQFP    |       | 5   | 8   | 3   | 1        | 8ch | 8ch                | 8ch | 2/16 <sup>2</sup> | 91  |

|                              | 208 MAPBGA |       | 5   | 8   | 3   | 2        | 8ch | 8ch                | 8ch | 2/32              | 152 |

| 9S12XEP768                   | 144LQFP    |       | 5   | 8   | 3   | 2        | 8ch | 8ch                | 8ch | 2/24              | 119 |

|                              | 112LQFP    |       | 5   | 8   | 3   | 1        | 8ch | 8ch                | 8ch | 2/16<br>(2)       | 91  |

|                              | 144LQFP    |       | 4   | 6   | 3   | 2        | 8ch | 0                  | 4ch | 2/24              | 119 |

| 9S12XEQ512                   | 112LQFP    | yes   | 4   | 6   | 3   | 1        | 8ch | 0                  | 4ch | 2/16 <sup>2</sup> | 91  |

|                              | 80QFP      |       | 4   | 2   | 3   | 1        | 8ch | 0                  | 4ch | 2/8 <sup>2</sup>  | 59  |

|                              | 144LQFP    |       | 4   | 6   | 3   | 2        | 8ch | 0                  | 4ch | 2/24              | 119 |

| 9S12XEQ384                   | 112LQFP    |       | 4   | 6   | 3   | 1        | 8ch | 0                  | 4ch | 2/16 <sup>2</sup> | 91  |

|                              | 80QFP      |       | 4   | 2   | 3   | 1        | 8ch | 0                  | 4ch | 2/8 <sup>2</sup>  | 59  |

|                              | 144LQFP    |       | 2   | 6   | 3   | 2        | 8ch | 0                  | 4ch | 2/24              | 119 |

| 9S12XEG384                   | 112LQFP    |       | 2   | 6   | 3   | 1        | 8ch | 0                  | 4ch | 2/16 <sup>2</sup> | 91  |

|                              | 80QFP      |       | 2   | 2   | 3   | 1        | 8ch | 0                  | 4ch | 2/8 <sup>2</sup>  | 59  |

|                              | 144LQFP    |       | 1   | 2   | 1   | 2        | 8ch | 0                  | 4ch | 2/24              | 119 |

| 9S12XES384                   | 112LQFP    | no    | 1   | 2   | 1   | 1        | 8ch | 0                  | 4ch | 2/16 <sup>2</sup> | 91  |

|                              | 80QFP      |       | 1   | 2   | 1   | 1        | 8ch | 0                  | 4ch | 2/8 <sup>2</sup>  | 59  |

|                              | 144LQFP    |       | 3   | 4   | 3   | 1        | 8ch | 0                  | 4ch | 2/24              | 119 |

| 9S12XET256                   | 112LQFP    |       | 3   | 4   | 3   | 1        | 8ch | 0                  | 4ch | 2/16 <sup>2</sup> | 91  |

|                              | 80QFP      |       | 3   | 2   | 3   | 1        | 8ch | 0                  | 4ch | 2/8 <sup>2</sup>  | 59  |

| 9S12XEA256<br><sup>(3)</sup> | 80QFP      | yes   | 3   | 2   | 3   | 1        | 8ch | 0                  | 4ch | 2/12 <sup>2</sup> | 59  |

| 9S12XEG256                   | 112LQFP    | -     | 2   | 4   | 3   | 1        | 8ch | 0                  | 4ch | 2/16 <sup>2</sup> | 91  |

| 0810756109                   | 112LQFP    |       | 2   | 2   | 2   | 1        | 8ch | 0                  | 2ch | 1/16              | 91  |

| 9S12XEG128                   | 80QFP      |       | 2   | 2   | 2   | 1        | 8ch | 0                  | 2ch | 1/8               | 59  |

| 9S12XEA128 <sup>3</sup>      | 80QFP      |       | 2   | 2   | 2   | 1        | 8ch | 0                  | 2ch | 2/12 <sup>2</sup> | 59  |

|                              |            |       |     |     |     | <u> </u> | L   | 1                  |     | I                 |     |

TIM available via rerouting on EP100,EP768 devices 112/144 pinout options. TIM not available on EG128,ET256,EA256, EQ384,EQ512 devices.

The device features 2 16-channel ATD modules, only one of which is bonded out in this package option

This is a special bondout for access to extra ADC channels in 80QFP. WARNING: NOT PIN-COMPATIBLE WITH REST OF FAMILY.

The 9S12XET256/9S12XEG128 use the standard 80QFP bondouts, compatible with other family members.

#### 0x0180–0x01BF MSCAN (CAN1) Map (Sheet 2 of 2)

| Address           | Name      |        | Bit 7                                                                                            | Bit 6       | Bit 5 | Bit 4     | Bit 3 | Bit 2 | Bit 1         | Bit 0 |

|-------------------|-----------|--------|--------------------------------------------------------------------------------------------------|-------------|-------|-----------|-------|-------|---------------|-------|

| 0x0196            | CAN1IDMR2 | R<br>W | AM7                                                                                              | AM6         | AM5   | AM4       | AM3   | AM2   | AM1           | AM0   |

| 0x0197            | CAN1IDMR3 | R<br>W | AM7                                                                                              | AM6         | AM5   | AM4       | AM3   | AM2   | AM1           | AM0   |

| 0x0198            | CAN1IDAR4 | R<br>W | AC7                                                                                              | AC6         | AC5   | AC4       | AC3   | AC2   | AC1           | AC0   |

| 0x0199            | CAN1IDAR5 | R<br>W | AC7                                                                                              | AC6         | AC5   | AC4       | AC3   | AC2   | AC1           | AC0   |

| 0x019A            | CAN1IDAR6 | R<br>W | AC7                                                                                              | AC6         | AC5   | AC4       | AC3   | AC2   | AC1           | AC0   |

| 0x019B            | CAN1IDAR7 | R<br>W | AC7                                                                                              | AC6         | AC5   | AC4       | AC3   | AC2   | AC1           | AC0   |

| 0x019C            | CAN1IDMR4 | R<br>W | AM7                                                                                              | AM6         | AM5   | AM4       | AM3   | AM2   | AM1           | AM0   |

| 0x019D            | CAN1IDMR5 | R<br>W | AM7                                                                                              | AM6         | AM5   | AM4       | AM3   | AM2   | AM1           | AM0   |

| 0x019E            | CAN1IDMR6 | R<br>W | AM7                                                                                              | AM6         | AM5   | AM4       | AM3   | AM2   | AM1           | AM0   |

| 0x019F            | CAN1IDMR7 | R<br>W | AM7                                                                                              | AM6         | AM5   | AM4       | AM3   | AM2   | AM1           | AM0   |

| 0x01A0–<br>0x01AF | CAN1RXFG  | R      | FOREGROUND RECEIVE BUFFER<br>(See Detailed MSCAN Foreground Receive and Transmit Buffer Layout)  |             |       |           |       |       |               |       |

|                   |           | w      |                                                                                                  | (COC Dotain |       | eregreand |       |       | liner Edyodt) |       |

| 0x01B0–<br>0x01BF | CAN1TXFG  | R<br>W | FOREGROUND TRANSMIT BUFFER<br>(See Detailed MSCAN Foreground Receive and Transmit Buffer Layout) |             |       |           |       |       |               |       |

#### 0x01C0-0x01FF MSCAN (CAN2) Map (Sheet 1 of 3)

| Address | Name     |        | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|---------|----------|--------|-------|--------|---------|---------|---------|---------|--------|--------|

| 0x01C0  | CAN2CTL0 | R<br>W | RXFRM | RXACT  | CSWAI   | SYNCH   | TIME    | WUPE    | SLPRQ  | INITRQ |

| 0x01C1  | CAN2CTL1 | R<br>W | CANE  | CLKSRC | LOOPB   | LISTEN  | BORM    | WUPM    | SLPAK  | INITAK |

| 0x01C2  | CAN2BTR0 | R<br>W | SJW1  | SJW0   | BRP5    | BRP4    | BRP3    | BRP2    | BRP1   | BRP0   |

| 0x01C3  | CAN2BTR1 | R<br>W | SAMP  | TSEG22 | TSEG21  | TSEG20  | TSEG13  | TSEG12  | TSEG11 | TSEG10 |

| 0x01C4  | CAN2RFLG | R<br>W | WUPIF | CSCIF  | RSTAT1  | RSTAT0  | TSTAT1  | TSTAT0  | OVRIF  | RXF    |

| 0x01C5  | CAN2RIER | R<br>W | WUPIE | CSCIE  | RSTATE1 | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE  | RXFIE  |

| 0x01C6  | CAN2TFLG | R      | 0     | 0      | 0       | 0       | 0       | TXE2    | TXE1   | TXE0   |

|         |          | W<br>R | 0     | 0      | 0       | 0       | 0       |         |        |        |

| 0x01C7  | CAN2TIER | w      | •     |        |         | 5       | ,       | TXEIE2  | TXEIE1 | TXEIE0 |

#### 0x0200-0x023F MSCAN (CAN3) (continued)

| Address           | Name      |        | Bit 7                                                                                            | Bit 6                                                                                           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-------------------|-----------|--------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| 0x0216            | CAN3IDMR2 | R<br>W | AM7                                                                                              | AM6                                                                                             | AM5   | AM4   | AM3   | AM2   | AM1   | AM0   |  |

| 0x0217            | CAN3IDMR3 | R<br>W | AM7                                                                                              | AM6                                                                                             | AM5   | AM4   | AM3   | AM2   | AM1   | AM0   |  |

| 0x0218            | CAN3IDAR4 | R<br>W | AC7                                                                                              | AC6                                                                                             | AC5   | AC4   | AC3   | AC2   | AC1   | AC0   |  |

| 0x0219            | CAN3IDAR5 | R<br>W | AC7                                                                                              | AC6                                                                                             | AC5   | AC4   | AC3   | AC2   | AC1   | AC0   |  |

| 0x021A            | CAN3IDAR6 | R<br>W | AC7                                                                                              | AC6                                                                                             | AC5   | AC4   | AC3   | AC2   | AC1   | AC0   |  |

| 0x021B            | CAN3IDAR7 | R<br>W | AC7                                                                                              | AC6                                                                                             | AC5   | AC4   | AC3   | AC2   | AC1   | AC0   |  |

| 0x021C            | CAN3IDMR4 | R<br>W | AM7                                                                                              | AM6                                                                                             | AM5   | AM4   | AM3   | AM2   | AM1   | AM0   |  |

| 0x021D            | CAN3IDMR5 | R<br>W | AM7                                                                                              | AM6                                                                                             | AM5   | AM4   | AM3   | AM2   | AM1   | AM0   |  |

| 0x021E            | CAN3IDMR6 | R<br>W | AM7                                                                                              | AM6                                                                                             | AM5   | AM4   | AM3   | AM2   | AM1   | AM0   |  |

| 0x021F            | CAN3IDMR7 | R<br>W | AM7                                                                                              | AM6                                                                                             | AM5   | AM4   | AM3   | AM2   | AM1   | AM0   |  |

| 0x0220–<br>0x022F | CAN3RXFG  | R<br>W |                                                                                                  | FOREGROUND RECEIVE BUFFER<br>(See Detailed MSCAN Foreground Receive and Transmit Buffer Layout) |       |       |       |       |       |       |  |

| 0x0230–<br>0x023F | CAN3TXFG  | R<br>W | FOREGROUND TRANSMIT BUFFER<br>(See Detailed MSCAN Foreground Receive and Transmit Buffer Layout) |                                                                                                 |       |       |       |       |       |       |  |

#### 0x0240–0x027F Port Integration Module (PIM) Map 5 of 6

| Address | Name     |          | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |   |

|---------|----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---|

| 0x0240  | PTT      | R<br>W   | PTT7  | PTT6  | PTT5  | PTT4  | PTT3  | PTT2  | PTT1  | PTT0  |   |

| 0x0241  | PTIT     | R        | PTIT7 | PTIT6 | PTIT5 | PTIT4 | PTIT3 | PTIT2 | PTIT1 | PTIT0 |   |

| 0702-11 | 1 111    | W        |       |       |       |       |       |       |       |       |   |

| 0x0242  | DDRT     | R<br>W   | DDRT7 | DDRT7 | DDRT5 | DDRT4 | DDRT3 | DDRT2 | DDRT1 | DDRT0 |   |

| 0x0243  | RDRT     | R<br>W   | RDRT7 | RDRT6 | RDRT5 | RDRT4 | RDRT3 | RDRT2 | RDRT1 | RDRT0 |   |

| 0x0244  | PERT     | R<br>W   | PERT7 | PERT6 | PERT5 | PERT4 | PERT3 | PERT2 | PERT1 | PERT0 |   |

| 0x0245  | PPST     | R<br>W   | PPST7 | PPST6 | PPST5 | PPST4 | PPST3 | PPST2 | PPST1 | PPST0 |   |

| 0x0246  | Reserved | Reserved | R     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 |

|         |          |          | W     |       |       |       |       |       |       |       |   |

| 0x0247  | Reserved | R        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |   |

|         |          | W        |       |       |       |       |       |       |       |       |   |