Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 8051                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 33MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, UART/USART                                             |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LQFP                                                                  |

| Supplier Device Package    | 44-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p87c654x2bbd-157 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## P83C654X2/P87C654X2

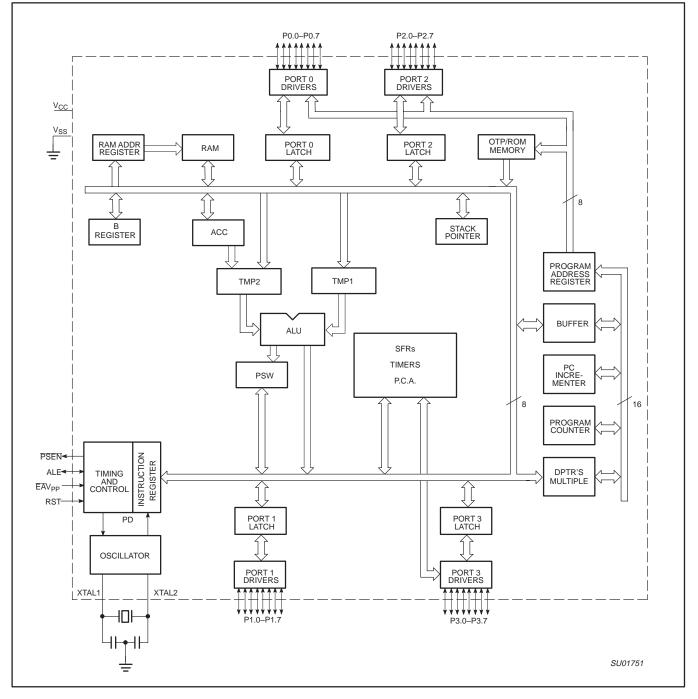

#### **BLOCK DIAGRAM (CPU ORIENTED)**

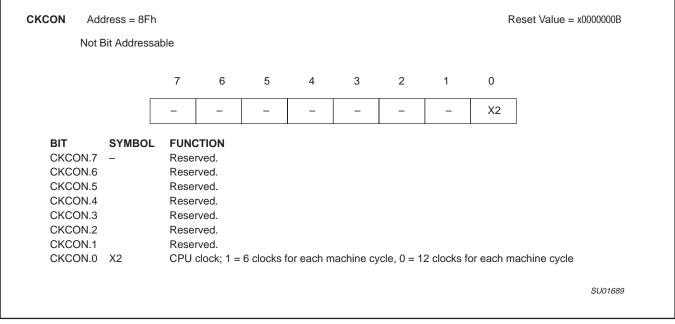

#### **CLOCK CONTROL REGISTER (CKCON)**

This device allows control of the 6-clock/12-clock mode by means of both an SFR bit (X2) and an OTP bit. The OTP clock control bit

OX2, when programmed (6-clock mode), supersedes the X2 bit (CKCON.0). The CKCON register is shown below in Figure 1.

P83C654X2/P87C654X2

Figure 1. Clock control (CKCON) register

Also please note that the clock divider applies to the serial port for modes 0 and 2 (fixed baud rate modes). This is because modes 1 and 3 (variable baud rate modes) use either Timer 1 or Timer 2.

Below is the truth table for the CPU clock mode.

#### Table 1.

| OX2 clock mode bit<br>(can only be set by<br>parallel programmer) | X2 bit<br>(CKCON.0) | CPU clock mode             |

|-------------------------------------------------------------------|---------------------|----------------------------|

| erased                                                            | 0                   | 12-clock mode<br>(default) |

| erased                                                            | 1                   | 6-clock mode               |

| programmed                                                        | Х                   | 6-clock mode               |

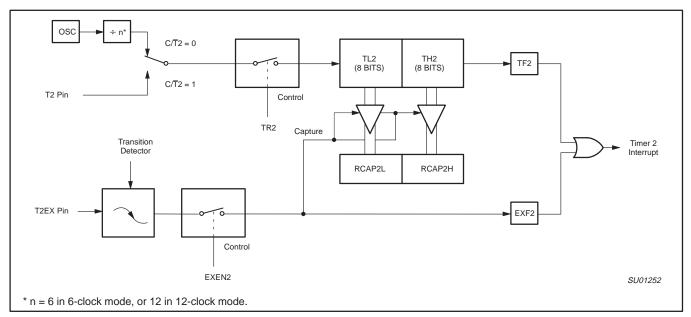

Table 3. Timer 2 Operating Modes

| RCLK + TCLK | CP/RL2 | TR2 | MODE                |

|-------------|--------|-----|---------------------|

| 0           | 0      | 1   | 16-bit Auto-reload  |

| 0           | 1      | 1   | 16-bit Capture      |

| 1           | Х      | 1   | Baud rate generator |

| Х           | Х      | 0   | (off)               |

Figure 8. Timer 2 in Capture Mode

| T2MOD                                                                | Addres      | ss = 0C9H                   |                              |                                |                               |                                |                               |                              | Reset Va                      | lue = XXXX XX00E                                          |

|----------------------------------------------------------------------|-------------|-----------------------------|------------------------------|--------------------------------|-------------------------------|--------------------------------|-------------------------------|------------------------------|-------------------------------|-----------------------------------------------------------|

|                                                                      | Not Bit /   | Addressab                   | ole                          |                                |                               |                                |                               |                              |                               |                                                           |

|                                                                      |             | _                           | _                            | _                              | _                             | _                              | _                             | T2OE                         | DCEN                          |                                                           |

|                                                                      | Bit         | 7                           | 6                            | 5                              | 4                             | 3                              | 2                             | 1                            | 0                             | -                                                         |

| Symbol                                                               | Functi      | on                          |                              |                                |                               |                                |                               |                              |                               |                                                           |

| _                                                                    | Not im      | plemented                   | l, reserved f                | or future use                  | э.*                           |                                |                               |                              |                               |                                                           |

| T2OE                                                                 | Timer 2     | 2 Output E                  | nable bit.                   |                                |                               |                                |                               |                              |                               |                                                           |

| DCEN                                                                 | Down        | Count Ena                   | ble bit. Whe                 | en set, this a                 | llows Timer                   | 2 to be cont                   | figured as a                  | n up/down d                  | counter.                      |                                                           |

| <ul> <li>User soft</li> <li>In that ca</li> <li>indetermi</li> </ul> | se, the res | uld not writ<br>set or inac | e 1s to rese<br>tive value o | rved bits. TI<br>f the new bit | nese bits ma<br>will be 0, ar | ay be used ir<br>nd its active | n future 805<br>value will be | 1 family pro<br>e 1. The val | ducts to invo<br>ue read fron | oke new features.<br>n a reserved bit is<br><i>SU0072</i> |

Figure 9. Timer 2 Mode (T2MOD) Control Register

Product data

#### 80C51 8-bit microcontroller family 16 kB OTP/ROM, 256B RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

#### Write to SBUF RxD P3.0 Alt Output Function S D 0 SBUF ÷ CI Zero Detector Start Shift TX Control S6 TX Clock T1 Send Serial Port TxD Interrupt P3.1 Alt Output Shift Clock R1 RX Clock Receive Function RX Control Shift REN 1 1 1 1 0 Start 1 1 1 RI MSB LSB RxD P3.0 Alt Input Shift Register Input Function Shift Load SBUF LSB SBUF MSB Read SBUF 80C51 Internal Bus S1 . . . . S6 S1 .... S6 S1.... S6 S1 S6 S1. ... S6 S1 S4 . . S6 S1. S6 S1 . . ALE Write to SBUF П S6P2 Send Shift Transmit RxD (Data Out) D0 D1 D2 D3 D4 D5 D6 D7 TxD (Shift Clock) S3P1 S6P1 Write to SCON (Clear RI) Receive Shift П п п Л Л Л П Receive RxD (Data In) D0 D3 D4 S5P2 TxD (Shift Clock) SU00539

80C51 Internal Bus

ΤI

RI

Figure 15. Serial Port Mode 0

### P83C654X2/P87C654X2

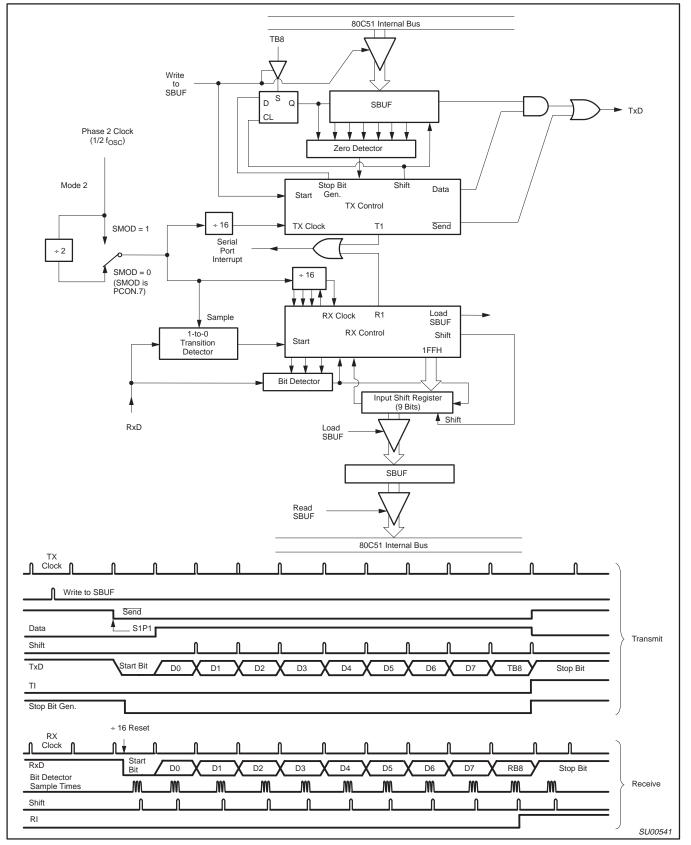

Figure 17. Serial Port Mode 2

## 80C51 8-bit microcontroller family 16 kB OTP/ROM, 256B RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

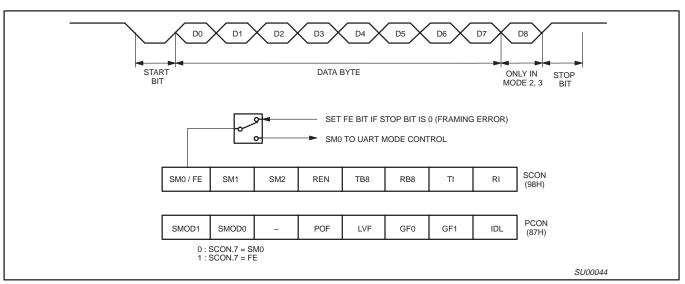

Figure 19. UART Framing Error Detection

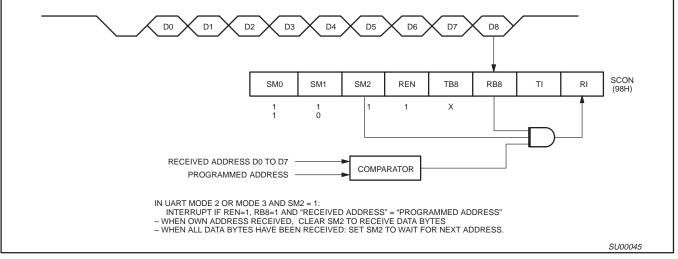

Figure 20. UART Multiprocessor Communication, Automatic Address Recognition

### P83C654X2/P87C654X2

ARBITRATION AND SYNCHRONIZATION LOGIC

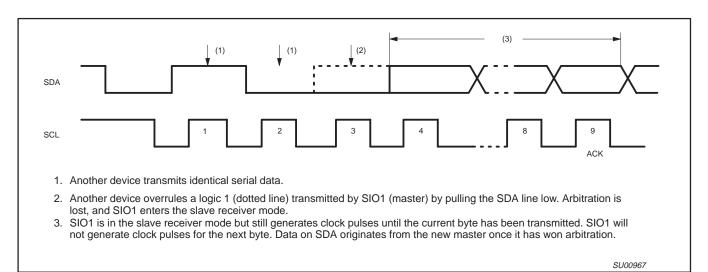

In the master transmitter mode, the arbitration logic checks that every transmitted logic 1 actually appears as a logic 1 on the I<sup>2</sup>C-bus. If another device on the bus overrules a logic 1 and pulls the SDA line LOW, arbitration is lost, and the I<sup>2</sup>C-bus immediately changes from master transmitter to slave receiver. The I<sup>2</sup>C-bus will continue to output clock pulses (on SCL) until transmission of the current serial byte is complete.

Arbitration may also be lost in the master receiver mode. Loss of arbitration in this mode can only occur while the  $l^2$ C-bus is returning a "not acknowledge: (logic 1) to the bus. Arbitration is lost when another device on the bus pulls this signal LOW. Since this can occur only at the end of a serial byte, the  $l^2$ C-bus generates no further clock pulses. Figure 24 shows the arbitration procedure.

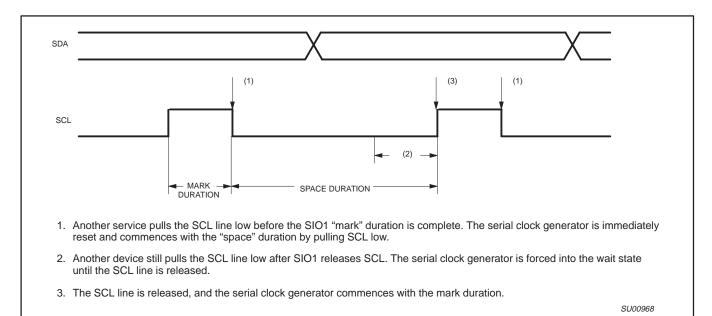

The synchronization logic will synchronize the serial clock generator with the clock pulses on the SCL line from another device. If two or more master devices generate clock pulses, the "mark" duration is determined by the device that generates the shortest "marks," and the "space" duration is determined by the device that generates the longest "spaces." Figure 25 shows the synchronization procedure.

A slave may stretch the space duration to slow down the bus master. The space duration may also be stretched for handshaking purposes. This can be done after each bit or after a complete byte transfer. The  $I^2$ C-bus will stretch the SCL space duration after a byte has been transmitted or received and the acknowledge bit has been transferred. The serial interrupt flag (SI) is set, and the stretching continues until the serial interrupt flag is cleared.

Figure 25. Serial Clock Synchronization

If the STA and STO bits are both set, the a STOP condition is transmitted to the I<sup>2</sup>C-bus if I<sup>2</sup>C is in a master mode (in a slave mode, I<sup>2</sup>C generates an internal STOP condition which is not transmitted). I<sup>2</sup>C then transmits a START condition.

STO = 0: When the STO bit is reset, no STOP condition will be generated.

#### SI, THE SERIAL INTERRUPT FLAG

SI = 1: When the SI flag is set, then, if the EA and ES1 (interrupt enable register) bits are also set, a serial interrupt is requested. SI is set by hardware when one of 25 of the 26 possible  $I^2C$  states is entered. The only state that does not cause SI to be set is state F8H, which indicates that no relevant state information is available.

While SI is set, the LOW period of the serial clock on the SCL line is stretched, and the serial transfer is suspended. A HIGH level on the SCL line is unaffected by the serial interrupt flag. SI must be reset by software.

SI = 0: When the SI flag is reset, no serial interrupt is requested, and there is no stretching of the serial clock on the SCL line.

#### AA, THE ASSERT ACKNOWLEDGE FLAG

AA = 1: If the AA flag is set, an acknowledge (low level to SDA) will be returned during the acknowledge clock pulse on the SCL line when:

- The "own slave address" has been received

- The general call address has been received while the general call bit (GC) in S1ADR is set

- A data byte has been received while I<sup>2</sup>C is in the master receiver mode

- A data byte has been received while I<sup>2</sup>C is in the addressed slave receiver mode

AA = 0: if the AA flag is reset, a not acknowledge (HIGH level to SDA) will be returned during the acknowledge clock pulse on SCL when:

- A data has been received while I<sup>2</sup>C is in the master receiver mode

- A data byte has been received while I<sup>2</sup>C is in the addressed slave receiver mode

When I<sup>2</sup>C is in the addressed slave transmitter mode, state C8H will be entered after the last serial is transmitted (see Figure 31). When SI is cleared, I<sup>2</sup>C leaves state C8H, enters the not addressed slave receiver mode, and the SDA line remains at a HIGH level. In state C8H, the AA flag can be set again for future address recognition.

When I<sup>2</sup>C is in the not addressed slave mode, its own slave address and the general call address are ignored. Consequently, no acknowledge is returned, and a serial interrupt is not requested. Thus, I<sup>2</sup>C can be temporarily released from the I<sup>2</sup>C-bus while the bus status is monitored. While I<sup>2</sup>C is released from the bus, START and STOP conditions are detected, and serial data is shifted in. Address recognition can be resumed at any time by setting the AA flag. If the AA flag is set when the part's own slave address or the general call address has been partly received, the address will be recognized at the end of the byte transmission.

P83C654X2/P87C654X2

#### CR0, CR1, AND CR2, THE CLOCK RATE BITS

These three bits determine the serial clock frequency when  $I^2C$  is in a master mode. The various serial rates are shown in Table 7.

If the I<sup>2</sup>C block is to be used in fast mode, bit 3 in AUXR must be set. The user can read but cannot write (write once) to AUXR after setup.

|               | 7 | 6 | 5 | 4 | 3                                | 2 | 1 | 0  |

|---------------|---|---|---|---|----------------------------------|---|---|----|

| AUXR<br>(8EH) | _ | _ | _ | _ | FAST/<br>STD<br>I <sup>2</sup> C | _ | - | A0 |

A 12.5kHz bit rate may be used by devices that interface to the I<sup>2</sup>C-bus via standard I/O port lines which are software driven and slow. 100kHz is usually the maximum bit rate and can be derived from a 16 MHz, 12 MHz, or a 6 MHz oscillator. A variable bit rate (0.5kHz to 62.5kHz) may also be used if Timer 1 is not required for any other purpose while I<sup>2</sup>C is in a master mode.

The frequencies shown in Table 7 are unimportant when  $I^2C$  is in a slave mode. In the slave modes,  $I^2C$  will automatically synchronize with any clock frequency up to 100kHz.

**The Status Register, S1STA:** S1STA is an 8-bit read-only special function register. The three least significant bits are always zero. The five most significant bits contain the status code. There are 26 possible status codes. When S1STA contains F8H, no relevant state information is available and no serial interrupt is requested. All other S1STA values correspond to defined I<sup>2</sup>C states. When each of these states is entered, a serial interrupt is requested (SI = 1). A valid status code is present in S1STA one machine cycle after SI is set by hardware and is still present one machine cycle after SI has been reset by software.

### P83C654X2/P87C654X2

Product data

#### Table 10. Master Receiver Mode

| STATUS  | STATUS OF THE                                                | APPLICATION S                                               | OFTWA       |             | SPONS       | E           |                                                                                                                                                                                                                 |

|---------|--------------------------------------------------------------|-------------------------------------------------------------|-------------|-------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CODE    | I <sup>2</sup> C-BUS AND                                     | TO/FROM S1DAT                                               |             | TO S        | CON         | -           | NEXT ACTION TAKEN BY I <sup>2</sup> C HARDWARE                                                                                                                                                                  |

| (S1STA) | HARDWARE                                                     | TO/FROM STDAT                                               | STA         | STO         | SI          | AA          |                                                                                                                                                                                                                 |

| 08H     | A START condition has been transmitted                       | Load SLA+R                                                  | Х           | 0           | 0           | Х           | SLA+R will be transmitted;<br>ACK bit will be received                                                                                                                                                          |

| 10H     | A repeated START<br>condition has been<br>transmitted        | Load SLA+R or<br>Load SLA+W                                 | X<br>X      | 0<br>0      | 0<br>0      | X<br>X      | As above<br>SLA+W will be transmitted;<br>I <sup>2</sup> C will be switched to MST/TRX mode                                                                                                                     |

| 38H     | Arbitration lost in<br>NOT ACK bit                           | No S1DAT action or No S1DAT action                          | 0<br>1      | 0<br>0      | 0<br>0      | X<br>X      | I <sup>2</sup> C-bus will be released;<br>I <sup>2</sup> C will enter a slave mode<br>A START condition will be transmitted when the<br>bus becomes free                                                        |

| 40H     | SLA+R has been<br>transmitted; ACK has<br>been received      | No S1DAT action or no S1DAT action                          | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>1      | Data byte will be received;<br>NOT ACK bit will be returned<br>Data byte will be received;<br>ACK bit will be returned                                                                                          |

| 48H     | SLA+R has been<br>transmitted; NOT ACK<br>has been received  | No S1DAT action or<br>no S1DAT action or<br>no S1DAT action | 1<br>0<br>1 | 0<br>1<br>1 | 0<br>0<br>0 | X<br>X<br>X | Repeated START condition will be transmitted<br>STOP condition will be transmitted;<br>STO flag will be reset<br>STOP condition followed by a<br>START condition will be transmitted;<br>STO flag will be reset |

| 50H     | Data byte has been<br>received; ACK has been<br>returned     | Read data byte or read data byte                            | 0<br>0      | 0<br>0      | 0<br>0      | 0<br>1      | Data byte will be received;<br>NOT ACK bit will be returned<br>Data byte will be received;<br>ACK bit will be returned                                                                                          |

| 58H     | Data byte has been<br>received; NOT ACK has<br>been returned | Read data byte or<br>read data byte or<br>read data byte    | 1<br>0<br>1 | 0<br>1<br>1 | 0<br>0<br>0 | x<br>x<br>x | Repeated START condition will be transmitted<br>STOP condition will be transmitted;<br>STO flag will be reset<br>STOP condition followed by a<br>START condition will be transmitted;<br>STO flag will be reset |

Figure 34. Recovering from a Bus Obstruction Caused by a Low Level on SDA

#### Software Examples of I<sup>2</sup>C Service Routines: This section

- consists of a software example for:

- Initialization of I<sup>2</sup>C after a RESET

- Entering the I<sup>2</sup>C interrupt routine

- The 26 state service routines for the

- Master transmitter mode

- Master receiver mode

- Slave receiver mode

- Slave transmitter mode

#### INITIALIZATION

In the initialization routine, I<sup>2</sup>C is enabled for both master and slave modes. For each mode, a number of bytes of internal data RAM are allocated to the SIO to act as either a transmission or reception buffer. In this example, 8 bytes of internal data RAM are reserved for different purposes. The data memory map is shown in Figure 35. The initialization routine performs the following functions:

- S1ADR is loaded with the part's own slave address and the general call bit (GC)

- P1.6 and P1.7 bit latches are loaded with logic 1s

- RAM location HADD is loaded with the high-order address byte of the service routines

- The I<sup>2</sup>C interrupt enable and interrupt priority bits are set

- The slave mode is enabled by simultaneously setting the ENS1 and AA bits in S1CON and the serial clock frequency (for master modes) is defined by loading CR0 and CR1 in S1CON. The master routines must be started in the main program.

The  $I^2C$  hardware now begins checking the  $I^2C$ -bus for its own slave address and general call. If the general call or the own slave address is detected, an interrupt is requested and S1STA is loaded with the appropriate state information. The following text describes a fast method of branching to the appropriate service routine. I<sup>2</sup>C INTERRUPT ROUTINE

When the I<sup>2</sup>C interrupt is entered, the PSW is first pushed on the stack. Then S1STA and HADD (loaded with the high-order address byte of the 26 service routines by the initialization routine) are pushed on to the stack. S1STA contains a status code which is the lower byte of one of the 26 service routines. The next instruction is RET, which is the return from subroutine instruction. When this instruction is executed, the HIGH and LOW order address bytes are popped from stack and loaded into the program counter.

The next instruction to be executed is the first instruction of the state service routine. Seven bytes of program code (which execute in eight machine cycles) are required to branch to one of the 26 state service routines.

| SI | PUSH        | PSW   | Save PSW                                                   |

|----|-------------|-------|------------------------------------------------------------|

|    | PUSH        | S1STA | Push status code                                           |

|    |             |       | (low order address byte)                                   |

|    | PUSH<br>RET | HADD  | Push HIGH order address byte Jump to state service routine |

The state service routines are located in a 256-byte page of program memory. The location of this page is defined in the initialization routine. The page can be located anywhere in program memory by loading data RAM register HADD with the page number. Page 01 is chosen in this example, and the service routines are located between addresses 0100H and 01FFH.

#### THE STATE SERVICE ROUTINES

The state service routines are located 8 bytes from each other. Eight bytes of code are sufficient for most of the service routines. A few of the routines require more than 8 bytes and have to jump to other locations to obtain more bytes of code. Each state routine is part of the I<sup>2</sup>C interrupt routine and handles one of the 26 states. It ends with a RETI instruction which causes a return to the main program.

|                                      |                                    | L                                                                 |                                                  |                                            |                                                                                                                                                                      |

|--------------------------------------|------------------------------------|-------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                                    | ! STATE<br>!                                                      | : A0, A S1<br>while stil<br>: No save<br>Recogni | FOP con<br>Il addre<br>of DAT<br>tion of c | ndition or repeated START has been received,<br>ssed as SLV/REC or SLV/TRX.<br>'A, Enter NOT addressed SLV mode.<br>own SLA. General call recognized, if S1ADR. 0–1. |

|                                      |                                    | .sect<br>.base                                                    | srsA0<br>0x1a0                                   |                                            |                                                                                                                                                                      |

| 01A0                                 | 75D8C5                             |                                                                   |                                                  | mov                                        | S1CON,#ENS1_NOTSTA_NOTSTO_NOTSI_AA_CR0<br>! clr SI, set AA                                                                                                           |

| 01A3<br>01A5                         | D0D0<br>32                         |                                                                   |                                                  | pop<br>reti                                | psw                                                                                                                                                                  |

|                                      |                                    | !*************<br>! SLAVE TF<br>!***************<br>!************ | RANSMITT                                         | ER ST/                                     | ATE SERVICE ROUTINES                                                                                                                                                 |

|                                      |                                    | ! STATE<br>! ACTION                                               | :A8, Own<br>:DATA wi                             | ISLA+F                                     | R received, ACK returned.<br>Insmitted, A bit received.                                                                                                              |

|                                      |                                    | .sect<br>.base                                                    | stsa8<br>0x1a8                                   |                                            |                                                                                                                                                                      |

| 01A8<br>01AB                         | 8548DA<br>75D8C5                   |                                                                   |                                                  | mov<br>mov                                 | S1DAT,STD ! load DATA in S1DAT<br>S1CON,#ENS1_NOTSTA_NOTSTO_NOTSI_AA_CR0<br>! clr SI, set AA                                                                         |

| 01AE                                 | 01E8                               |                                                                   |                                                  | ajmp                                       | INITBASE2                                                                                                                                                            |

| 00E8<br>00EB<br>00ED<br>00EE<br>00F0 | 75D018<br>7948<br>09<br>D0D0<br>32 | .sect<br>.base<br>INITBASE2                                       | ibase2<br>0xe8<br>2:                             | mov<br>mov<br>inc<br>pop<br>reti           | psw,#SELRB3<br>r1, #STD<br>r1<br>psw                                                                                                                                 |

|                                      |                                    | ! STATE                                                           | : B0, Arbit<br>: DATA wi<br>STA is s             | tration I<br>II be tra                     | ost in SLA and R/W as MST. Own SLA+R received, ACK returned.<br>Insmitted, A bit received.<br>start MST mode after the bus is free again.                            |

|                                      |                                    | .sect<br>.base                                                    | stsb0<br>0x1b0                                   |                                            |                                                                                                                                                                      |

| 01B0<br>01B3<br>01B6                 | 8548DA<br>75D8E5<br>01E8           |                                                                   |                                                  | mov<br>mov<br>ajmp                         | S1DAT,STD ! load DATA in S1DAT<br>S1CON,#ENS1_STA_NOTSTO_NOTSI_AA_CR0<br>INITBASE2                                                                                   |

#### **ABSOLUTE MAXIMUM RATINGS1**, 2, 3

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on $\overline{EA}/V_{PP}$ pin to V <sub>SS</sub>                                     | 0 to +13.0             | V    |

| Voltage on any other pin to V <sub>SS</sub> <sup>4</sup>                                     | -0.5 to +6.0           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

NOTES:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied. 1.

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise

noted.

4. Transient voltage only.

#### **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0^{\circ}C$  to +70°C or -40°C to +85°C

|                     |        |                      |                |                         | CLOCK FREG |     |      |

|---------------------|--------|----------------------|----------------|-------------------------|------------|-----|------|

| SYMBOL              | FIGURE | PARAMETER            | OPERATING MODE | POWER SUPPLY<br>VOLTAGE | MIN        | MAX | UNIT |

| 1/t <sub>CLCL</sub> | 46     | Oscillator frequency | 6-clock        | $5$ V $\pm 10$ %        | 0          | 30  | MHz  |

|                     |        |                      | 6-clock        | 2.7 V to 5.5 V          | 0          | 16  | MHz  |

|                     |        |                      | 12-clock       | 5 V ±10 %               | 0          | 33  | MHz  |

|                     |        |                      | 12-clock       | 2.7 V to 5.5 V          | 0          | 16  | MHz  |

### DC ELECTRICAL CHARACTERISTICS

$T_{amb} = 0 \degree C$  to +70  $\degree C$  or -40  $\degree C$  to +85  $\degree C$ ;  $V_{CC} = 2.7 V$  to 5.5 V;  $V_{SS} = 0 V$  (16 MHz max. CPU clock)

| SYMBOL           | PARAMETER                                                                        | TEST<br>CONDITIONS                                  | LIMITS                   |                  |                          | UNIT |  |

|------------------|----------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|------------------|--------------------------|------|--|

|                  |                                                                                  |                                                     | MIN                      | TYP <sup>1</sup> | MAX                      | 1    |  |

| V <sub>IL</sub>  | Input LOW voltage <sup>11</sup> , except P1.6 and P1.7                           | 4.0 V < V <sub>CC</sub> < 5.5 V                     | -0.5                     |                  | 0.2V <sub>CC</sub> - 0.1 | V    |  |

|                  |                                                                                  | 2.7 V < V <sub>CC</sub> < 4.0 V                     | -0.5                     |                  | 0.7V <sub>CC</sub>       | V    |  |

| V <sub>IL1</sub> | Input LOW voltage to EA                                                          |                                                     | -0.5                     |                  | 0.2V <sub>DD</sub> - 0.3 | V    |  |

| V <sub>IL2</sub> | Input LOW voltage to P1.6/SCL, P1.7/SDA <sup>5</sup>                             |                                                     | -0.5                     |                  | 0.3V <sub>DD</sub>       | V    |  |

| VIH              | Input HIGH voltage (ports 0, 1, 2, 3, EA)                                        |                                                     | 0.2V <sub>CC</sub> + 0.9 |                  | V <sub>CC</sub> + 0.5    | V    |  |

| V <sub>IH1</sub> | Input HIGH voltage, XTAL1, RST <sup>11</sup>                                     |                                                     | 0.7V <sub>CC</sub>       |                  | V <sub>CC</sub> + 0.5    | V    |  |

| V <sub>OL</sub>  | Output LOW voltage, ports 1, 2 <sup>8</sup> , except P1.6 and P1.7               | $V_{CC} = 2.7 \text{ V}; I_{OL} = 1.6 \text{ mA}^2$ | -                        |                  | 0.4                      | V    |  |

| V <sub>OL1</sub> | Output LOW voltage, port 0, ALE, PSEN <sup>8, 7</sup>                            | $V_{CC} = 2.7 \text{ V}; I_{OL} = 3.2 \text{ mA}^2$ | -                        |                  | 0.4                      | V    |  |

| V <sub>OL2</sub> | Output LOW voltage, P1.6/SCL, P1.7/SDA                                           | <sup>I</sup> <sub>OL</sub> = 3.0 mA <sup>7</sup>    | -                        |                  | 0.4                      | V    |  |

| V <sub>OH</sub>  | Output HIGH voltage, ports 1, 2, 3 3                                             | V <sub>CC</sub> = 2.7 V; I <sub>OH</sub> = -20 μA   | V <sub>CC</sub> – 0.7    |                  | -                        | V    |  |

|                  |                                                                                  | V <sub>CC</sub> = 4.5 V; I <sub>OH</sub> = -30 μA   | V <sub>CC</sub> – 0.7    | 1                | -                        | V    |  |

| V <sub>OH1</sub> | Output HIGH voltage (port 0 in external bus mode), $ALE^9$ , $\overline{PSEN}^3$ | $V_{CC} = 2.7 \text{ V}; I_{OH} = -3.2 \text{ mA}$  | V <sub>CC</sub> – 0.7    |                  | -                        | V    |  |

| IIL              | Logical 0 input current, ports 1, 2, 3                                           | V <sub>IN</sub> = 0.4 V                             | -1                       |                  | -50                      | μA   |  |

| I <sub>TL</sub>  | Logical 1-to-0 transition current, ports 1, 2, 3 <sup>6</sup>                    | V <sub>IN</sub> = 2.0 V; See note 4                 | -                        |                  | -650                     | μA   |  |

| ILI              | Input leakage current, port 0                                                    | 0.45 < V <sub>IN</sub> < V <sub>CC</sub> – 0.3      | -                        |                  | ±10                      | μA   |  |

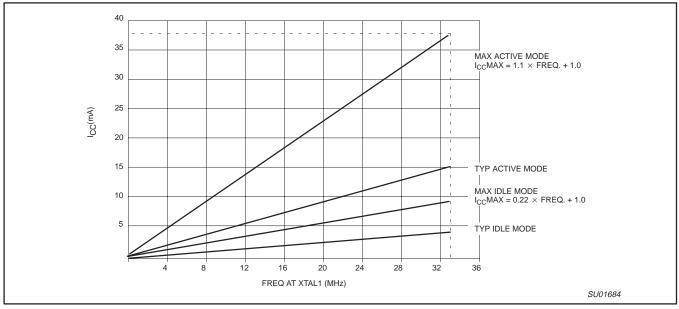

| ICC              | Power supply current (see Figure 49 and Source Code):                            |                                                     |                          |                  |                          |      |  |

|                  | Active mode @ 16 MHz                                                             |                                                     |                          |                  |                          | μA   |  |

|                  | Idle mode @ 16 MHz                                                               |                                                     |                          |                  |                          | μA   |  |

|                  | Power-down mode or clock stopped (see Figure 45 for conditions) <sup>12</sup>    | T <sub>amb</sub> = 0 °C to 70 °C                    |                          | 2                | 30                       | μA   |  |

|                  |                                                                                  | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$       |                          | 3                | 50                       | μA   |  |

| V <sub>RAM</sub> | RAM keep-alive voltage                                                           |                                                     | 1.2                      |                  |                          | V    |  |

| R <sub>RST</sub> | Internal reset pull-down resistor                                                |                                                     | 40                       |                  | 225                      | kΩ   |  |

| C <sub>IO</sub>  | Pin capacitance <sup>10</sup> (except EA)                                        |                                                     | -                        |                  | 15                       | pF   |  |

NOTES:

Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the Vols of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE pin may exceed 0.8 V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. IoL can exceed these conditions provided that no single output sinks more than 5 mA and no more than two outputs exceed the test conditions.

3. Capacitive loading on ports 0 and 2 may cause the  $V_{OH}$  on ALE and  $\overline{PSEN}$  to momentarily fall below the  $V_{CC}$ –0.7 specification when the address bits are stabilizing.

- 4. Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2 V.

- 5. See Figures 51 through 54 for  $I_{CC}$  test conditions and Figure 49 for  $I_{CC}$  vs. Frequency

12-clock mode characteristics:

Active mode (operating):  $I_{CC} = 1.0 \text{ mA} + 1.1 \text{ mA} \times \text{FREQ.[MHz]}$

- Active mode (reset):  $I_{CC} = 7.0 \text{ mA} + 0.6 \text{ mA} \times \text{FREQ}.[\text{MHz}]$

Idle mode:  $I_{CC} = 1.0 \text{ mA} + 0.22 \text{ mA} \times \text{FREQ}[MHz]$ 6. This value applies to  $T_{amb} = 0 \text{ °C}$  to +70 °C. For  $T_{amb} = -40 \text{ °C}$  to +85 °C,  $I_{TL} = -750 \mu$ A. 7. Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

- 8. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

- Maximum IOL per port pin: 15 mA (\*NOTE: This is 85 °C specification.) 26 mA

- Maximum IOL per 8-bit port:

Maximum total I<sub>OL</sub> for all outputs: 71 mA If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 9. ALE is tested to V<sub>OH1</sub>, except when ALE is off then V<sub>OH</sub> is the voltage specification.

- 10. Pin capacitance is characterized but not tested. Pin capacitance is less than 25 pF. Pin capacitance of ceramic package is less than 15 pF (except EA is 25 pF).

### P83C654X2/P87C654X2

<sup>1.</sup> Typical ratings are not guaranteed. Values listed are based on tests conducted on limited number of samples at room temperature.

#### 80C51 8-bit microcontroller family 16 kB OTP/ROM, 256B RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

#### AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE, 5 V ±10 % OPERATION)

$T_{amb} = 0 \degree C$  to +70  $\degree C$  or -40  $\degree C$  to +85  $\degree C$ ;  $V_{CC} = 5 V \pm 10 \%$ ,  $V_{SS} = 0 V^{1,2,3,4,5}$

| Symbol              | Figure | Parameter                                          | Limits                    |                                       | 16 MHz ( | Clock  | Unit |

|---------------------|--------|----------------------------------------------------|---------------------------|---------------------------------------|----------|--------|------|

|                     |        |                                                    | MIN                       | MAX                                   | MIN      | MAX    | 7    |

| 1/t <sub>CLCL</sub> | 46     | Oscillator frequency                               | 0                         | 30                                    | -        | -      | MHz  |

| LHLL                | 41     | ALE pulse width                                    | t <sub>CLCL</sub> – 8     | -                                     | 54.5     | -      | ns   |

| AVLL                | 41     | Address valid to ALE LOW                           | 0.5t <sub>CLCL</sub> – 13 | -                                     | 18.25    | -      | ns   |

| t <sub>LLAX</sub>   | 41     | Address hold after ALE LOW                         | 0.5t <sub>CLCL</sub> – 20 | -                                     | 11.25    | -      | ns   |

| t <sub>LLIV</sub>   | 41     | ALE LOW to valid instruction in                    | -                         | 2t <sub>CLCL</sub> -35                | -        | 90     | ns   |

| t <sub>LLPL</sub>   | 41     | ALE LOW to PSEN LOW                                | 0.5t <sub>CLCL</sub> – 10 | -                                     | 21.25    | -      | ns   |

| t <sub>PLPH</sub>   | 41     | PSEN pulse width                                   | 1.5t <sub>CLCL</sub> – 10 | -                                     | 83.75    | -      | ns   |

| t <sub>PLIV</sub>   | 41     | PSEN LOW to valid instruction in                   | -                         | 1.5t <sub>CLCL</sub> – 35             | -        | 58.75  | ns   |

| t <sub>PXIX</sub>   | 41     | Input instruction hold after PSEN                  | 0                         | -                                     | 0        | -      | ns   |

| t <sub>PXIZ</sub>   | 41     | Input instruction float after PSEN                 | -                         | 0.5t <sub>CLCL</sub> – 10             | -        | 21.25  | ns   |

| t <sub>AVIV</sub>   | 41     | Address to valid instruction in                    | _                         | 2.5t <sub>CLCL</sub> – 35             | -        | 121.25 | ns   |

| t <sub>PLAZ</sub>   | 41     | PSEN LOW to address float                          | _                         | 10                                    | -        | 10     | ns   |

| Data Men            | nory   |                                                    |                           | 1                                     | 1        |        |      |

| t <sub>RLRH</sub>   | 42     | RD pulse width                                     | 3t <sub>CLCL</sub> – 20   | -                                     | 167.5    | -      | ns   |

| t <sub>WLWH</sub>   | 43     | WR pulse width                                     | 3t <sub>CLCL</sub> – 20   | -                                     | 167.5    | -      | ns   |

| RLDV                | 42     | RD LOW to valid data in                            | -                         | 2.5t <sub>CLCL</sub> – 35             | -        | 121.25 | ns   |

| t <sub>RHDX</sub>   | 42     | Data hold after RD                                 | 0                         | _                                     | 0        | -      | ns   |

| t <sub>RHDZ</sub>   | 42     | Data float after RD                                | -                         | t <sub>CLCL</sub> –10                 | -        | 52.5   | ns   |

| tLLDV               | 42     | ALE LOW to valid data in                           | -                         | 4t <sub>CLCL</sub> – 35               | -        | 215    | ns   |

| t <sub>AVDV</sub>   | 42     | Address to valid data in                           | -                         | 4.5t <sub>CLCL</sub> – 35             | -        | 246.25 | ns   |

| tLLWL               | 42, 43 | ALE LOW to RD or WR LOW                            | 1.5t <sub>CLCL</sub> – 15 | 1.5t <sub>CLCL</sub> +15              | 78.75    | 108.75 | ns   |

| t <sub>AVWL</sub>   | 42, 43 | Address valid to WR LOW or RD LOW                  | 2t <sub>CLCL</sub> –15    | -                                     | 110      | -      | ns   |

| t <sub>QVWX</sub>   | 43     | Data valid to WR transition                        | 0.5t <sub>CLCL</sub> – 25 | -                                     | 6.25     | -      | ns   |

| t <sub>WHQX</sub>   | 43     | Data hold after WR                                 | 0.5t <sub>CLCL</sub> – 15 | -                                     | 16.25    | -      | ns   |

| t <sub>QVWH</sub>   | 43     | Data valid to WR HIGH                              | 3.5t <sub>CLCL</sub> – 5  | -                                     | 213.75   | -      | ns   |

| t <sub>RLAZ</sub>   | 42     | RD LOW to address float                            | -                         | 0                                     | -        | 0      | ns   |

| t <sub>WHLH</sub>   | 42, 43 | RD or WR HIGH to ALE HIGH                          | 0.5t <sub>CLCL</sub> – 10 | 0.5t <sub>CLCL</sub> +10              | 21.25    | 41.25  | ns   |

| External (          | Clock  |                                                    | 0101                      | 0101                                  |          |        |      |

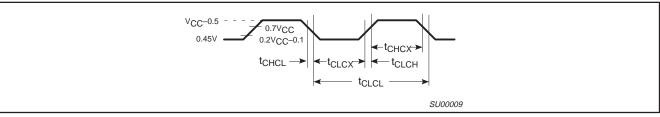

| tCHCX               | 46     | High time                                          | 0.4t <sub>CLCL</sub>      | t <sub>CLCL</sub> - t <sub>CLCX</sub> | -        | -      | ns   |

| t <sub>CLCX</sub>   | 46     | Low time                                           | 0.4t <sub>CLCL</sub>      | t <sub>CLCL</sub> - t <sub>CHCX</sub> | -        | -      | ns   |

| t <sub>CLCH</sub>   | 46     | Rise time                                          | _                         | 5                                     | -        | -      | ns   |

| t <sub>CHCL</sub>   | 46     | Fall time                                          | -                         | 5                                     | -        | -      | ns   |

| Shift regi          | ster   |                                                    |                           |                                       |          |        |      |

| t <sub>XLXL</sub>   | 45     | Serial port clock cycle time                       | 6t <sub>CLCL</sub>        | -                                     | 375      | -      | ns   |

| t <sub>QVXH</sub>   | 45     | Output data setup to clock rising edge             | 5t <sub>CLCL</sub> –25    | -                                     | 287.5    | -      | ns   |

| t <sub>XHQX</sub>   | 45     | Output data hold after clock rising edge           | t <sub>CLCL</sub> – 15    | -                                     | 47.5     | -      | ns   |

| t <sub>XHDX</sub>   | 45     | Input data hold after clock rising edge            | 0                         | -                                     | 0        | -      | ns   |

| t <sub>XHDV</sub>   | 45     | Clock rising edge to input data valid <sup>6</sup> | _                         | 5t <sub>CLCL</sub> – 133              | -        | 179.5  | ns   |

#### NOTES:

1. Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN=100 pF, load capacitance for all outputs = 80 pF

Interfacing the microcontroller to devices with float time up to 45ns is permitted. This limited bus contention will not cause damage to port 0 drivers.

4. Parts are guaranteed by design to operate down to 0 Hz.

5. Data shown in the table are the best mathematical models for the set of measured values obtained in tests. If a particular parameter

calculated at a customer specified frequency has a negative value, it should be considered equal to zero.

6. Below 16 MHz this parameter is 4t<sub>CLCL</sub> - 133

## 80C51 8-bit microcontroller family 16 kB OTP/ROM, 256B RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

Figure 49. I<sub>CC</sub> vs. FREQ for 12-clock operation Valid only within frequency specifications of the specified operating voltage

| /*     |                |                    |                                           |         |

|--------|----------------|--------------------|-------------------------------------------|---------|

| ##     | as31 version   | V2.10              | / *js* /                                  |         |

| ##     |                |                    |                                           |         |

| ##     |                |                    |                                           |         |

| ##     |                | idd_ljmp1.asm      |                                           |         |

| ##     | list file:     | idd_ljmp1.lst      | created Fri Apr 20 15:51:40 2001          |         |

| ##     |                |                    |                                           |         |

|        | ############## |                    |                                           |         |

| #0000  |                | # AUXR equ 08E     |                                           |         |

| #0000  |                | # CKCON equ 08F    | 1                                         |         |

|        |                | #<br>#             |                                           |         |

| #0000  |                | #<br># org 0       |                                           |         |

| 10000  |                | #                  |                                           |         |

|        |                | "<br># LJMP_LABEL: |                                           |         |

| 0000 / | 75;/8E;/01;    | # MOV              | AUXR,#001h ; turn off ALE                 |         |

| 0003 / | 02;/FF;/FD;    | # LJMP             | LJMP_LABEL ; jump to end of address space |         |

| 0005 / | 00;            | # NOP              |                                           |         |

|        |                | #                  |                                           |         |

| #FFFD  |                | # org Offfdh       |                                           |         |

|        |                | #                  |                                           |         |

|        |                | # LJMP_LABEL:      |                                           |         |

|        |                | #                  |                                           |         |

| FFD /  | 02;/FD;FF;     |                    | LJMP_LABEL                                |         |

|        |                | #; NOP             |                                           |         |

|        |                | #<br>#             |                                           |         |

| * / "  |                | π                  |                                           |         |

| /      |                |                    |                                           | SU01499 |

Figure 50. Source code used in measuring  $I_{\text{DD}}$  operational

## P83C654X2/P87C654X2

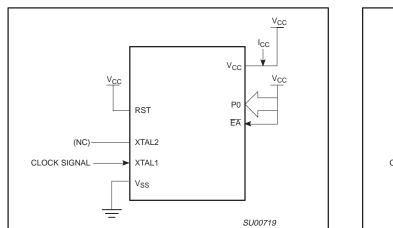

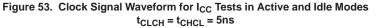

Figure 51. I<sub>CC</sub> Test Condition, Active Mode All other pins are disconnected

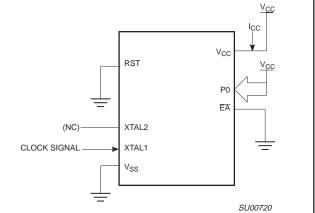

Figure 52. I<sub>CC</sub> Test Condition, Idle Mode All other pins are disconnected

Figure 54.  $I_{CC}$  Test Condition, Power-down mode All other pins are disconnected.  $V_{CC}$  = 2 V to 5.5 V

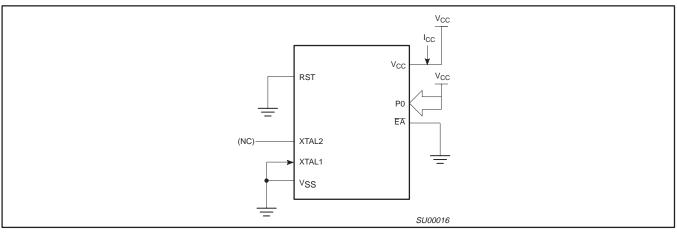

#### EPROM PROGRAMMING AND VERIFICATION CHARACTERISTICS

$T_{amb}$  = 21°C to +27°C,  $V_{CC}$  = 5 V ±10 %,  $V_{SS}$  = 0 V (See Figure 58)

| SYMBOL              | PARAMETER                             | MIN                 | MAX                 | UNIT |

|---------------------|---------------------------------------|---------------------|---------------------|------|

| V <sub>PP</sub>     | Programming supply voltage            | 12.5                | 13.0                | V    |

| I <sub>PP</sub>     | Programming supply current            |                     | 50 <sup>1</sup>     | mA   |

| 1/t <sub>CLCL</sub> | Oscillator frequency                  | 4                   | 6                   | MHz  |

| t <sub>AVGL</sub>   | Address setup to PROG LOW             | 48t <sub>CLCL</sub> |                     |      |

| t <sub>GHAX</sub>   | Address hold after PROG               | 48t <sub>CLCL</sub> |                     |      |

| t <sub>DVGL</sub>   | Data setup to PROG LOW                | 48t <sub>CLCL</sub> |                     |      |

| t <sub>GHDX</sub>   | Data hold after PROG                  | 48t <sub>CLCL</sub> |                     |      |

| t <sub>EHSH</sub>   | P2.7 (ENABLE) HIGH to V <sub>PP</sub> | 48t <sub>CLCL</sub> |                     |      |

| t <sub>SHGL</sub>   | V <sub>PP</sub> setup to PROG LOW     | 10                  |                     | μs   |

| t <sub>GHSL</sub>   | V <sub>PP</sub> hold after PROG       | 10                  |                     | μs   |

| t <sub>GLGH</sub>   | PROG width                            | 90                  | 110                 | μs   |

| t <sub>AVQV</sub>   | Address to data valid                 |                     | 48t <sub>CLCL</sub> |      |

| t <sub>ELQZ</sub>   | ENABLE LOW to data valid              |                     | 48t <sub>CLCL</sub> |      |

| t <sub>EHQZ</sub>   | Data float after ENABLE               | 0                   | 48t <sub>CLCL</sub> |      |

| t <sub>GHGL</sub>   | PROG HIGH to PROG LOW                 | 10                  |                     | μs   |

NOTE:

1. Not tested.

#### NOTES:

\* FOR PROGRAMMING CONFIGURATION SEE FIGURE 55.

FOR VERIFICATION CONDITIONS SEE FIGURE 57.

\*\* SEE TABLE 15.

Figure 58. EPROM Programming and Verification

#### MASK ROM DEVICES

#### **Security Bits**

With none of the security bits programmed the code in the program memory can be verified. If the encryption table is programmed, the code will be encrypted when verified. When only security bit 1 (see Table 17) is programmed, MOVC instructions executed from external program memory are disabled from fetching code bytes from the internal memory,  $\overline{\text{EA}}$  is latched on Reset and all further programming of the EPROM is disabled. When security bits 1 and 2 are programmed, in addition to the above, verify mode is disabled.

P83C654X2/P87C654X2

#### **Encryption Array**

64 bytes of encryption array are initially unprogrammed (all 1s).

#### Table 17. Program Security Bits

|   | PROGRAM LOCK BITS <sup>1, 2</sup> |     |                                                                                                                                                                                                           |

|---|-----------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | SB1                               | SB2 | PROTECTION DESCRIPTION                                                                                                                                                                                    |

| 1 | U                                 | U   | No Program Security features enabled.<br>(Code verify will still be encrypted by the Encryption Array if programmed.)                                                                                     |

| 2 | Р                                 |     | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, EA is sampled and latched on Reset, and further programming of the EPROM is disabled. |

NOTES:

1. P – programmed. U – unprogrammed.

2. Any other combination of the security bits is not defined.

## P83C654X2/P87C654X2

### **ROM CODE SUBMISSION FOR 16K ROM DEVICES**

When submitting ROM code for the 16K ROM devices, the following must be specified:

- 1. 16 kbyte user ROM data

- 2. 64 byte ROM encryption key

- 3. ROM security bits.

| ADDRESS        | CONTENT | BIT(S) | COMMENT                                                           |

|----------------|---------|--------|-------------------------------------------------------------------|

| 0000H to 3FFFH | DATA    | 7:0    | User ROM Data                                                     |

| 4000H to 403FH | KEY     | 7:0    | ROM Encryption Key<br>FFH = no encryption                         |

| 4040H          | SEC     | 0      | ROM Security Bit 1<br>0 = enable security<br>1 = disable security |

| 4040H          | SEC     | 1      | ROM Security Bit 2<br>0 = enable security<br>1 = disable security |

Security Bit 1: When programmed, this bit has two effects on masked ROM parts:

1. External MOVC is disabled, and

2.  $\overline{EA}$  is latched on Reset.

Security Bit 2: When programmed, this bit inhibits Verify User ROM.

**NOTE:** Security Bit 2 cannot be enabled unless Security Bit 1 is enabled.

If the ROM Code file does not include the options, the following information must be included with the ROM code.

For each of the following, check the appropriate box, and send to Philips along with the code:

| Security Bit #1: | □ Enabled | □ Disabled |  |

|------------------|-----------|------------|--|

| Security Bit #2: | Enabled   | Disabled   |  |

## P83C654X2/P87C654X2

#### **REVISION HISTORY**

| Rev | Date     | Description                                                  |

|-----|----------|--------------------------------------------------------------|

| _2  | 20040420 | Product data (9397 750 13173)                                |

|     |          | Modifications:                                               |

|     |          | <ul> <li>Update Special Function Registers table.</li> </ul> |

|     |          | <ul> <li>Remove P3.4 from Figures 55 and 57.</li> </ul>      |

| _1  | 20030213 | Product data (9397 750 10814)                                |