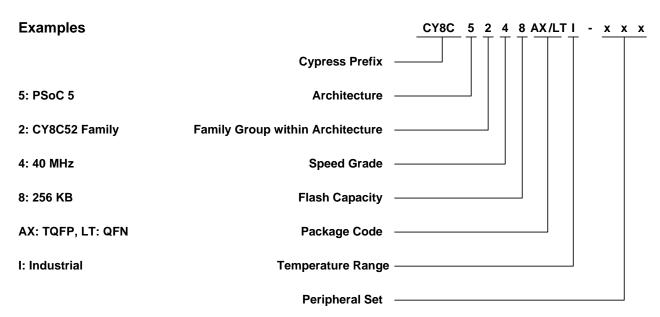

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 1x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5247lti-089 |

PSoC uses a SWD interface for programming, debug, and test. Using this standard interface enables the designer to debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. The Cortex-M3 debug and trace modules include FPB, DWT, and ITM. These modules have many features to help solve difficult debug and trace problems. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 49 of this data sheet.

# 2. Pinouts

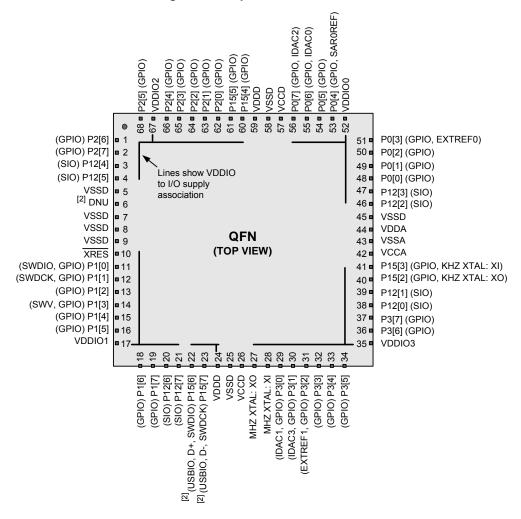

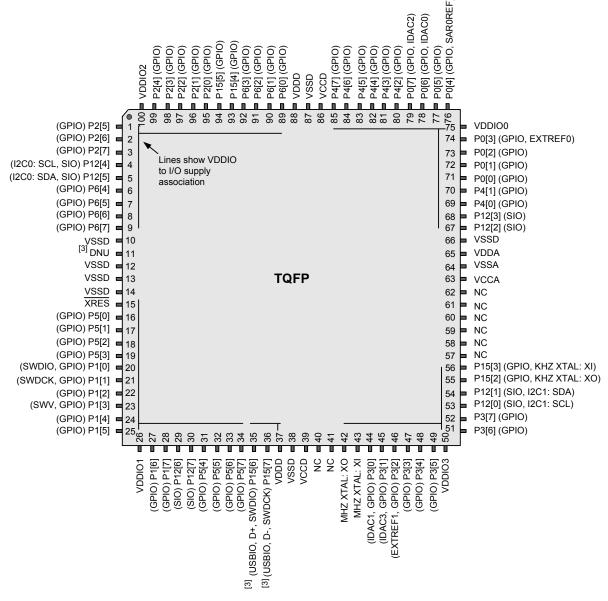

The VDDIO pin that supplies a particular set of pins is indicated by the black lines drawn on the pinout diagrams in Figure 2-1 and Figure 2-2. Using the VDDIO pins, a single PSoC can support multiple interface voltage levels, eliminating the need for off-chip level shifters. Each VDDIO may sink up to 20 mA total to its associated I/O pins and opamps, and each set of VDDIO associated pins may sink up to 100 mA.

Figure 2-1. 68-pin QFN Part Pinout<sup>[1]</sup>

## Notes

- The center pad on the QFN package should be connected to digital ground (V<sub>SSD</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal.

- 2. Pins labeled Do Not Use (DNU) must be left floating. USB pins on devices without USB are DNU.

Figure 2-2. 100-pin TQFP Part Pinout

Figure 2-3 and Figure 2-4 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a 2-layer board.

- The two pins labeled Vddd must be connected together.

- The two pins labeled Vccd must be connected together, with capacitance added, as shown in Figure 2-3 and Power System on page 21. The trace between the two Vccd pins should be as short as possible.

- The two pins labeled Vssd must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note, AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

#### Note

3. Pins labeled Do Not Use (DNU) must be left floating. USB pins on devices without USB are DNU.

- The Thumb<sup>®</sup>-2 instruction set, which offers ARM-level performance at Thumb-level code density. This includes 16-bit and 32-bit instructions. Advanced instructions include:

- Bit-field control

- □ Hardware multiply and divide

- Saturation

- □ If-Then

- Wait for events and interrupts

- Exclusive access and barrier

- Special register access

The Cortex-M3 does not support ARM instructions.

- Bit-band support for the SRAM region. Atomic bit-level write and read operations for SRAM addresses.

- Unaligned data storage and access. Contiguous storage of data of different byte lengths.

- Operation at two privilege levels (privileged and user) and in two modes (thread and handler). Some instructions can only be executed at the privileged level. There are also two stack pointers: Main (MSP) and Process (PSP). These features support a multitasking operating system running one or more user-level processes.

- Extensive interrupt and system exception support.

# 4.1.2 Cortex-M3 Operating Modes

The Cortex-M3 operates at either the privileged level or the user level, and in either the thread mode or the handler mode. Because the handler mode is only enabled at the privileged level, there are actually only three states, as shown in Table 4-1.

Table 4-1. Operational Level

| Condition            | Privileged   | User        |

|----------------------|--------------|-------------|

| Running an exception | Handler mode | Not used    |

| Running main program | Thread mode  | Thread mode |

At the user level, access to certain instructions, special registers, configuration registers, and debugging components is blocked. Attempts to access them cause a fault exception. At the privileged level, access to all instructions and registers is allowed. The processor runs in the handler mode (always at the privileged level) when handling an exception, and in the thread mode when not.

## 4.1.3 CPU Registers

The Cortex-M3 CPU registers are listed in Table 4-2. Registers R0-R15 are all 32 bits wide.

Table 4-2. Cortex M3 CPU Registers

| Register  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0-R12    | General purpose registers R0-R12 have no special architecturally defined uses. Most instructions that specify a general purpose register specify R0-R12.  Low Registers: Registers R0-R7 are accessible by all instructions that specify a general purpose register.  High Registers: Registers R8-R12 are accessible by all 32-bit instructions that specify a general purpose register; they are not accessible by all 16-bit instructions.                                                                                                                                                |

| R13       | R13 is the stack pointer register. It is a banked register that switches between two 32-bit stack pointers: the main stack pointer (MSP) and the process stack pointer (PSP). The PSP is used only when the CPU operates at the user level in thread mode. The MSP is used in all other privilege levels and modes. Bits[0:1] of the SP are ignored and considered to be 0, so the SP is always aligned to a word (4 byte) boundary.                                                                                                                                                         |

| R14       | R14 is the link register (LR). The LR stores the return address when a subroutine is called.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| R15       | R15 is the program counter (PC). Bit 0 of the PC is ignored and considered to be 0, so instructions are always aligned to a half word (2 byte) boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| xPSR      | The program status registers are divided into three status registers, which are accessed either together or separately:  Application program status register (APSR) holds program execution status bits such as zero, carry, negative, in bits[27:31].  Interrupt program status register (IPSR) holds the current exception number in bits[0:8].  Execution program status register (EPSR) holds control bits for interrupt continuable and IF-THEN instructions in bits[10:15] and [25:26]. Bit 24 is always set to 1 to indicate Thumb mode. Trying to clear it causes a fault exception. |

| PRIMASK   | A 1-bit interrupt mask register. When set, it allows only the nonmaskable interrupt (NMI) and hard fault exception. All other exceptions and interrupts are masked.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FAULTMASK | A 1-bit interrupt mask register. When set, it allows only the NMI. All other exceptions and interrupts are masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BASEPRI   | A register of up to nine bits that define the masking priority level. When set, it disables all interrupts of the same or higher priority value. If set to 0 then the masking function is disabled.                                                                                                                                                                                                                                                                                                                                                                                          |

## 4.4 Interrupt Controller

The Cortex-M3 NVIC supports 16 system exceptions and 32 interrupts from peripherals, as shown in Table 4-5.

Table 4-5. Cortex-M3 Exceptions and Interrupts

| Exception<br>Number | Exception Type | Priority     | Exception Table<br>Address Offset | Function                                                                                                                  |

|---------------------|----------------|--------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                     |                |              | 0x00                              | Starting value of R13 / MSP                                                                                               |

| 1                   | Reset          | -3 (highest) | 0x04                              | Reset                                                                                                                     |

| 2                   | NMI            | -2           | 0x08                              | Non maskable interrupt                                                                                                    |

| 3                   | Hard fault     | -1           | 0x0C                              | All classes of fault, when the corresponding fault handler cannot be activated because it is currently disabled or masked |

| 4                   | MemManage      | Programmable | 0x10                              | Memory management fault, for example, instruction fetch from a nonexecutable region                                       |

| 5                   | Bus fault      | Programmable | 0x14                              | Error response received from the bus system; caused by an instruction prefetch abort or data access error                 |

| 6                   | Usage fault    | Programmable | 0x18                              | Typically caused by invalid instructions or trying to switch to ARM mode                                                  |

| 7 – 10              | -              | _            | 0x1C - 0x28                       | Reserved                                                                                                                  |

| 11                  | SVC            | Programmable | 0x2C                              | System service call via SVC instruction                                                                                   |

| 12                  | Debug monitor  | Programmable | 0x30                              | Debug monitor                                                                                                             |

| 13                  | _              | _            | 0x34                              | Reserved                                                                                                                  |

| 14                  | PendSV         | Programmable | 0x38                              | Deferred request for system service                                                                                       |

| 15                  | SYSTICK        | Programmable | 0x3C                              | System tick timer                                                                                                         |

| 16 – 47             | IRQ            | Programmable | 0x40 - 0x3FC                      | Peripheral interrupt request #0 – #31                                                                                     |

Bit 0 of each exception vector indicates whether the exception is executed using ARM or Thumb instructions. Because the Cortex-M3 only supports Thumb instructions, this bit must always be 1. The Cortex-M3 non maskable interrupt (NMI) input can be routed to any pin, via the DSI, or disconnected from all pins. See "DSI Routing Interface Description" section on page 39.

The Nested Vectored Interrupt Controller (NVIC) handles interrupts from the peripherals, and passes the interrupt vectors to the CPU. It is closely integrated with the CPU for low latency interrupt handling. Features include:

- 32 interrupts. Multiple sources for each interrupt.

- Configurable number of priority levels: from 3 to 8.

- Dynamic reprioritization of interrupts.

- Priority grouping. This allows selection of preempting and non preempting interrupt levels.

- Support for tail-chaining, and late arrival, of interrupts. This enables back-to-back interrupt processing without the overhead of state saving and restoration between interrupts.

- Processor state automatically saved on interrupt entry, and restored on interrupt exit, with no instruction overhead.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. All interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

Page 14 of 97

Table 4-6. Interrupt Vector Table

| Interrupt # | Cortex-M3 Exception # | Fixed Function           | DMA              | UDB         |

|-------------|-----------------------|--------------------------|------------------|-------------|

| 0           | 16                    | Low voltage detect (LVD) | phub_termout0[0] | udb_intr[0] |

| 1           | 17                    | Cache                    | phub_termout0[1] | udb_intr[1] |

| 2           | 18                    | Reserved                 | phub_termout0[2] | udb_intr[2] |

| 3           | 19                    | Pwr Mgr                  | phub_termout0[3] | udb_intr[3] |

| 4           | 20                    | PICU[0]                  | phub_termout0[4] | udb_intr[4] |

| 5           | 21                    | PICU[1]                  | phub_termout0[5] | udb_intr[5] |

| 6           | 22                    | PICU[2]                  | phub_termout0[6] | udb_intr[6] |

| 7           | 23                    | PICU[3]                  | phub_termout0[7] | udb_intr[7] |

| 8           | 24                    | PICU[4]                  | phub_termout0[8] | udb_intr[8] |

Document Number: 001-66236 Rev. \*D

# 5. Memory

#### 5.1 Static RAM

CY8C52 Static RAM (SRAM) is used for temporary data storage. Code can be executed at full speed from the portion of SRAM that is located in the code space. This process is slower from SRAM above 0x20000000. The device provides up to 64 KB of SRAM. The CPU or the DMA controller can access all of SRAM. The SRAM can be accessed simultaneously by the Cortex-M3 CPU and the DMA controller if accessing different 32-KB blocks.

## 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data and bulk data storage. The main flash memory area contains up to 256 KB of user program space.

Up to an additional 32 KB of flash space is available for storing device configuration data and bulk user data. User code may not be run out of this flash memory section. The flash output is 9 bytes wide with 8 bytes of data and 1 additional byte.

The flash programming interface performs flash erasing, programming and setting code protection levels. Flash In System Serial Programming (ISSP), typically used for production programming, is possible through the SWD interface. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

## 5.3 Flash Security

All PSoC devices include a flexible flash protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of configuration or general-purpose data.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a boot loader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports, protecting your application from external access (see the

"Device Security" section on page 51). For more information on how to take full advantage of the security features in PSoC, see the PSoC 5 TRM.

Table 5-1. Flash Protection

| Protection Setting | Allowed                                           | Not Allowed                              |

|--------------------|---------------------------------------------------|------------------------------------------|

| Unprotected        | External read and write + internal read and write | _                                        |

| Factory<br>Upgrade | External write + internal read and write          | External read                            |

| Field Upgrade      | Internal read and write                           | External read and write                  |

| Full Protection    | Internal read                                     | External read and write + internal write |

#### **Disclaimer**

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

## 5.4 EEPROM

PSoC EEPROM memory is a byte addressable nonvolatile memory. The CY8C52 has 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into two sections, each containing 64 rows of 16 bytes each.

The CPU cannot execute out of EEPROM.

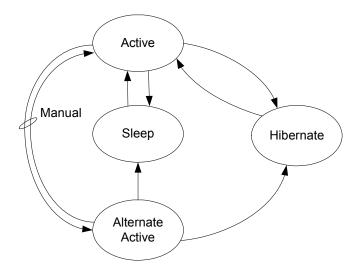

Figure 6-5. Power Mode Transitions

#### 6.2.1.1 Active Mode

Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled or disabled. When a resource is disabled, the digital clocks are gated, analog bias currents are disabled, and leakage currents are reduced as appropriate. User firmware can dynamically control subsystem power by setting and clearing bits in the active configuration template. The CPU can disable itself, in which case the CPU is automatically reenabled at the next wakeup event.

When a wakeup event occurs, the global mode is always returned to active, and the CPU is automatically enabled, regardless of its template settings. Active mode is the default global power mode upon boot.

## 6.2.1.2 Alternate Active Mode

Alternate Active mode is very similar to Active mode. In alternate active mode, fewer subsystems are enabled, to reduce power consumption. One possible configuration is to turn off the CPU and flash, and run peripherals at full speed.

## 6.2.1.3 Sleep Mode

Sleep mode powers down the CPU and other internal circuitry to reduce power consumption. However, supervisory services such as the central timewheel (CTW) remain available in this mode. The device can wake up using CTW or system reset. The wake up time from sleep mode is 125 µs (typical).

## 6.2.1.4 Hibernate Mode

In hibernate mode nearly all of the internal functions are disabled. Internal voltages are reduced to the minimal level to keep vital systems alive. Configuration state is preserved in hibernate mode and SRAM memory is retained. GPIOs configured as digital outputs maintain their previous values and external GPIO pin interrupt settings are preserved. The device can only return from hibernate mode in response to an external reset (XRES).

#### 6.2.1.5 Wakeup Events

Wakeup events can come from the central timewheel or device reset. A wakeup event restores the system to active mode. The central timewheel allows the system to periodically wake up, poll peripherals, do voltage monitoring, or perform real-time functions. Reset event sources include the external reset pin (XRES).

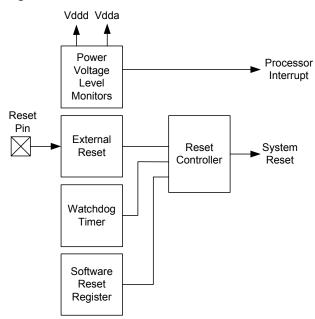

#### 6.3 Reset

CY8C52 has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring: The analog and digital power voltages, V<sub>DDA</sub>, V<sub>DDD</sub>, V<sub>CCA</sub>, and V<sub>CCD</sub> are monitored in several different modes during power up and active mode. The monitors are programmable to generate an interrupt to the processor under certain conditions.

- External: The device can be reset from an external source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull up to V<sub>DDIO1</sub>. V<sub>DDD</sub>, V<sub>DDA</sub>, and V<sub>DDIO1</sub> must all have voltage applied before the part comes out of reset.

- Watchdog timer: A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset. The watchdog timer can be used only when the part remains in active mode.

- Software: The device can be reset under program control.

## Figure 6-6. Resets

**Digital Input Path** Naming Convention 'x' = Port Number 'y' = Pin Number PRT[x]CTL PRT[x]DBL\_SYNC\_IN PRT[x]PS Digital System Input PICU[x]INTTYPE[y] Input Buffer Disable PICU[x]INTSTAT Interrupt Pin Interrupt Signal Logic PICU[x]INTSTAT **Digital Output Path** PRT[x]SLW

PRT[x]SYNC\_OUT Vddio Vddio PRT[x]DR Digital System Output PRT[x]BYP PRT[x]DM2 Drive Slew PIN Logic Cntl PRT[x]DM1 PRT[x]DM0 **Bidirectional Control** OE PRT[x]BIE Analog Capsense Global Control CAPS[x]CFG1 Switches PRT[x]AG Analog Global PRT[x]AMUX Analog Mux  $\sim$ LCD Display Data PRT[x]LCD COM SEG Logic & MUX PRT[x]LCD\_EN LCD Bias Bus

Figure 6-7. GPIO Block Diagram

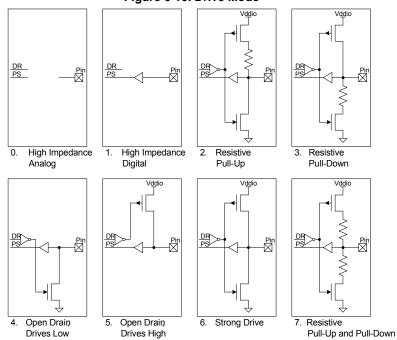

#### 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-5. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-10 depicts a simplified pin view based on each of the eight drive modes. Table 6-5 shows the I/O pin's drive state based on the port data register value or digital array signal

if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

Figure 6-10. Drive Mode

Table 6-5. Drive Modes

| Diagram | Drive Mode                                     | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedence analog                          | 0       | 0       | 0       | High-Z        | High-Z       |

| 1       | High Impedance digital                         | 0       | 0       | 1       | High-Z        | High-Z       |

| 2       | Resistive pull-up <sup>[9]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[9]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                         | 1       | 0       | 0       | High-Z        | Strong Low   |

| 5       | Open drain, drive high                         | 1       | 0       | 1       | Strong High   | High-Z       |

| 6       | Strong drive                                   | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[9]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

# ■ High Impedance Analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

#### ■ High Impedance Digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

#### Note

<sup>9.</sup> Resistive pull up and pull down are not available with SIO in regulated output mode.

## 7.1.4.2 Component Catalog

## Figure 7-3. Component Catalog

The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device. It is populated with an impressive selection of content; from simple primitives such as logic gates and device registers, through the digital timers, counters and PWMs, plus analog components such as ADC and DAC, and communication protocols such as I<sup>2</sup>C and USB. See "Example Peripherals" section on page 32 for more details about available peripherals. All content is fully characterized and carefully documented in data sheets with code examples, AC/DC specifications, and user code ready APIs.

#### 7.1.4.3 Design Reuse

The symbol editor gives you the ability to develop reusable components that can significantly reduce future design time. Just draw a symbol and associate that symbol with your proven design. PSoC Creator allows for the placement of the new symbol anywhere in the component catalog along with the content provided by Cypress. You can then reuse your content as many times as you want, and in any number of projects, without ever having to revisit the details of the implementation.

## 7.1.4.4 Software Development

Figure 7-4. Code Editor

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM<sup>®</sup> Limited, Keil™, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView™ compiler.

## 7.1.4.5 Nonintrusive Debugging

Figure 7-5. PSoC Creator Debugger

With SWD debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals – make for an unparalleled level of visibility into the system.

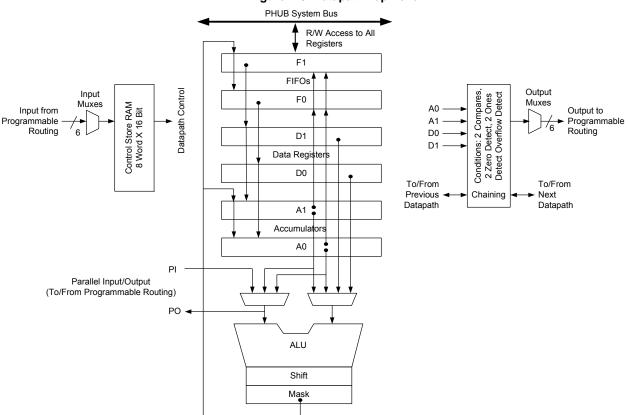

Figure 7-8. Datapath Top Level

#### 7.2.2.6 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

Table 7-1. Working Datapath Registers

| Name      | Function       | Description                                                                                                                                                                                               |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                               |

| F0 and F1 | FIFOs          | These are the primary interface to the system bus. They can be a data source for the data registers and accumulators or they can capture data from the accumulators or ALU. Each FIFO is four bytes deep. |

## 7.2.2.7 Dynamic Datapath Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word × 16-bit configuration RAM, which stores eight unique 16-bit wide configurations. The address input to this RAM controls the sequence, and can be routed from any block connected to the

UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

#### ALU

The ALU performs eight general purpose functions. They are:

- Increment

- Decrement

- Add

- Subtract

- Logical AND

- Logical OR

- Logical XOR

- Pass, used to pass a value through the ALU to the shift register, mask, or another UDB register

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

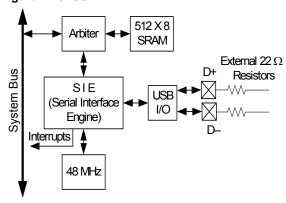

## 7.5 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 25.

When using USB, either a crystal must be used (24 MHz with MHzECO) or a similar high-accuracy clock source must be provided externally through a pin and the DSI. Also, bus clock must be equal to 33 MHz. See Section 6.1 on page 18 for details.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Two memory modes

□ Manual Memory Management with No DMA Access

□ Manual Memory Management with Manual DMA Access

- Internal 3.3 V regulator for transceiver

- Interrupts on bus and each endpoint event

- USB Reset, Suspend, and Resume operations

- Bus powered and self powered modes

#### Figure 7-18, USB

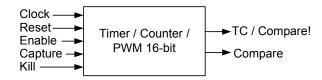

## 7.6 Timers, Counters, and PWMs

The Timer/Counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in Universal Digital Blocks (UDBs) as required. PSoC Creator allows designers to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The Timer/Counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output and terminal count output (optional complementary compare output). The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit timer/counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-19. Timer/Counter/PWM

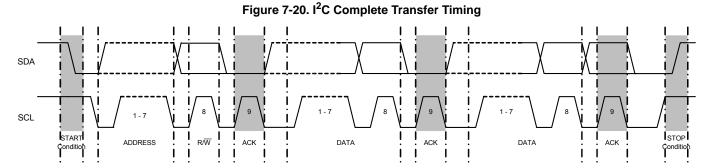

# 7.7 I<sup>2</sup>C

The I<sup>2</sup>C peripheral provides a synchronous two wire interface designed to interface the PSoC device with a two wire I<sup>2</sup>C serial communication bus. The bus is compliant with Philips 'The I<sup>2</sup>C Specification' version 2.1. Additional I<sup>2</sup>C interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

To eliminate the need for excessive CPU intervention and overhead, I<sup>2</sup>C specific support is provided for status detection and generation of framing bits. I<sup>2</sup>C operates as a slave, a master, or multimaster (Slave and Master)[10]. In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions. I<sup>2</sup>C interfaces through the DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 400 Kbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

Data transfers follow the format shown in Figure 7-20. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition. Various combinations of read/write formats are then possible within such a transfer.

#### Note

<sup>10.</sup> Fixed-block I2C does not support undefined bus conditions. These conditions should be avoided, or the UDB-based I2C component should be used instead.

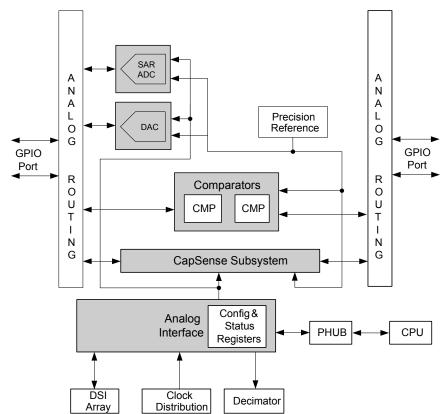

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

■ Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses

- Successive approximation (SAR) ADC

- One 8-bit DAC that provides either voltage or current output

- Two comparators with optional connection to configurable LUT outputs

- CapSense subsystem to enable capacitive touch sensing

- Precision reference for generating an accurate analog voltage for internal analog blocks

Figure 8-1. Analog Subsystem Block Diagram

#### 11.4.2 SIO

Note that under certain conditions an SIO pin may cause up to 1 mA of additional current to be drawn from the related  $V_{DDIO}$  pin. If an SIO pin's voltage exceeds its  $V_{DDIO}$  supply by 0.5 V, the trigger condition is set. After the trigger condition is set, the SIO pin causes increased current when its voltage is between  $V_{SSD}$  + 0.5 V and  $V_{DDIO}$  – 0.5 V. The trigger condition is reset when the SIO pin is brought within the range of  $V_{SSD}$  to  $V_{SSD}$  + 0.5 V. The trigger condition may unknowingly be met during device power-up due to differences in supply ramps.

Table 11-8. SIO DC Specifications

| Parameter       | Description                                                | Conditions                                               | Min                     | Тур | Max                                                                                                                                                                         | Units |

|-----------------|------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Vinmax          | Maximum input voltage                                      | All allowed values of Vddio and Vddd, see Section 11.2.1 | -                       | _   | 5.5                                                                                                                                                                         | V     |

| Vinref          | Input voltage reference (Differential input mode)          |                                                          | 0.5                     | _   | $0.52 \times V_{DDIO}$                                                                                                                                                      | V     |

|                 | Output voltage reference (Regulate                         | d output mode)                                           |                         |     |                                                                                                                                                                             |       |

| Voutref         |                                                            | V <sub>DDIO</sub> > 3.7                                  | 1                       | _   | V <sub>DDIO</sub> – 1                                                                                                                                                       | V     |

|                 |                                                            | V <sub>DDIO</sub> < 3.7                                  | 1                       | -   | $V_{\rm DDIO} - 0.5$                                                                                                                                                        | V     |

|                 | Input voltage high threshold                               |                                                          |                         |     |                                                                                                                                                                             |       |

| $V_{IH}$        | GPIO mode                                                  | CMOS input                                               | $0.7 \times V_{DDIO}$   | _   | _                                                                                                                                                                           | V     |

|                 | Differential input mode <sup>[24]</sup>                    | Hysteresis disabled                                      | SIO_ref + 0.2           | _   | _                                                                                                                                                                           | V     |

|                 | Input voltage low threshold                                |                                                          |                         |     |                                                                                                                                                                             |       |

| $V_{IL}$        | GPIO mode                                                  | CMOS input                                               | _                       | -   | $0.3 \times V_{DDIO}$                                                                                                                                                       | V     |

|                 | Differential input mode <sup>[24]</sup>                    | Hysteresis disabled                                      | _                       | -   | SIO_ref - 0.2                                                                                                                                                               | V     |

| V <sub>OH</sub> | Output voltage high                                        |                                                          |                         |     | 1                                                                                                                                                                           |       |

|                 | Unregulated mode                                           | I <sub>OH</sub> = 4 mA, V <sub>DDIO</sub> = 3.3 V        | V <sub>DDIO</sub> – 0.4 | -   | _                                                                                                                                                                           | V     |

| VОН             | Regulated mode <sup>[24]</sup>                             | I <sub>OH</sub> = 1 mA                                   | SIO_ref - 0.65          | -   | SIO_ref + 0.2                                                                                                                                                               | V     |

|                 | Regulated mode <sup>[24]</sup>                             | I <sub>OH</sub> = 0.1 mA                                 | SIO_ref - 0.3           | -   | SIO_ref + 0.2                                                                                                                                                               | V     |

| $V_{OL}$        | Output voltage low                                         | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 25 mA      | _                       | -   | 8.0                                                                                                                                                                         | V     |

| Rpullup         | Pull up resistor                                           |                                                          | 3.5                     | 5.6 | 8.5                                                                                                                                                                         | kΩ    |

| Rpulldown       | Pull down resistor                                         |                                                          | 3.5                     | 5.6 | 8.5                                                                                                                                                                         | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value) <sup>[25]</sup>     |                                                          |                         |     |                                                                                                                                                                             |       |

|                 | V <sub>IH</sub> ≤ Vddsio                                   | 25 °C, Vddsio = 3.0 V,<br>V <sub>IH</sub> = 3.0 V        | -                       | _   | 14                                                                                                                                                                          | nA    |

|                 | V <sub>IH</sub> > Vddsio                                   | 25 °C, Vddsio = 0 V, V <sub>IH</sub> = 3.0 V             | _                       | -   | 10                                                                                                                                                                          | μΑ    |

| C <sub>IN</sub> | Input Capacitance <sup>[25]</sup>                          |                                                          | _                       | -   | 7                                                                                                                                                                           | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger) <sup>[25]</sup> | Single ended mode (GPIO mode)                            | -                       | 150 | _                                                                                                                                                                           | mV    |

|                 |                                                            | Differential mode                                        | _                       | 35  | 5.5  0.52 × V <sub>DDIO</sub> V <sub>DDIO</sub> - 1  V <sub>DDIO</sub> - 0.5  0.3 × V <sub>DDIO</sub> SIO_ref - 0.2  SIO_ref + 0.2  SIO_ref + 0.2  0.8  8.5  8.5  14  10  7 | mV    |

| Idiode          | Current through protection diode to V <sub>SSIO</sub>      |                                                          | -                       | _   | 100                                                                                                                                                                         | μΑ    |

### Notes

<sup>24.</sup> See Figure 6-8 on page 28 and Figure 6-11 on page 31 for more information on SIO reference.

<sup>25.</sup> Based on device characterization (Not production tested).

# 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 54.

Table 11-10. USBIO DC Specifications

| Parameter                       | Description                                 | Conditions                                         | Min            | Тур | Max            | Units |

|---------------------------------|---------------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                           | USB D+ pull-up resistance                   | With idle bus                                      | 0.900          | _   | 1.575          | kΩ    |

| Rusba                           | USB D+ pull-up resistance                   | While receiving traffic                            | 1.425          | -   | 3.090          | kΩ    |

| Vohusb                          | Static output high                          | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb                          | Static output low                           | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | -              | _   | 0.3            | V     |

| Vihgpio                         | Input voltage high, GPIO mode               | $V_{DDD} \ge 3 \text{ V}$                          | 2              | _   | _              | V     |

| Vilgpio                         | Input voltage low, GPIO mode                | $V_{DDD} \ge 3 \text{ V}$                          | _              | _   | 0.8            | V     |

| Vohgpio                         | Output voltage high, GPIO mode              | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | 2.4            | _   | _              | V     |

| Volgpio                         | Output voltage low, GPIO mode               | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | _              | _   | 0.3            | V     |

| Vdi                             | Differential input sensitivity              | (D+)-(D-)                                          | -              | _   | 0.2            | V     |

| Vcm                             | Differential input common mode range        |                                                    | 8.0            | -   | 2.5            | V     |

| Vse                             | Single ended receiver threshold             |                                                    | 8.0            | -   | 2              | V     |

| Rps2                            | PS/2 pull-up resistance                     | In PS/2 mode, with PS/2 pull-up enabled            | 3              | _   | 7              | kΩ    |

| Rext                            | External USB series resistor                | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                              | USB driver output impedance <sup>[27]</sup> | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub>                 | USB transceiver input capacitance           |                                                    | _              | _   | 20             | pF    |

| I <sub>IL</sub> <sup>[28]</sup> | Input leakage current (absolute value)      | 25 °C, V <sub>DDD</sub> = 3.0 V                    | -              | _   | 2              | nA    |

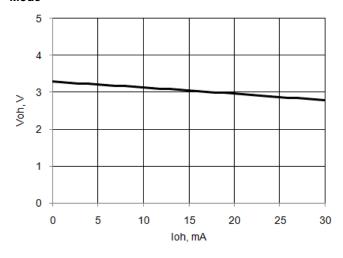

Figure 11-14. USBIO Output High Voltage and Current, GPIO Mode

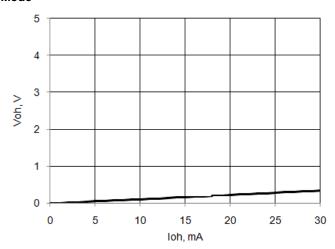

Figure 11-15. USBIO Output Low Voltage and Current, GPIO Mode

- 27. This parameter is not production tested and cannot be guaranteed over all temperatures.

28. Based on device characterization (Not production tested).

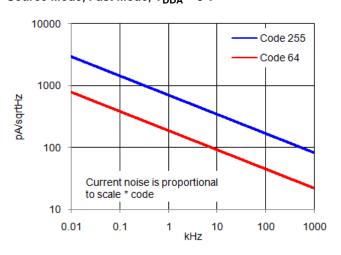

Table 11-22. IDAC AC Specifications

| Parameter           | Description              | Conditions                                                                                       | 55<br>Min | Тур | Max | Units     |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------|-----------|-----|-----|-----------|

| F <sub>DAC</sub>    | Update rate              |                                                                                                  | _         | _   | 5.5 | Msps      |

| T <sub>SETTLE</sub> | Settling time to 0.5 LSB | Range = 31.875 $\mu$ A or 255 $\mu$ A, full scale transition, fast mode, 600 $\Omega$ 15-pF load | -         | -   | 180 | ns        |

|                     | Current noise            | Range = 255 μA, source mode, fast mode, Vdda = 5 V, 10 kHz                                       | _         | 340 | _   | pA/sqrtHz |

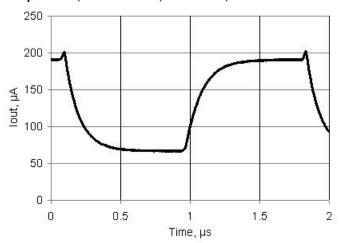

Figure 11-33. IDAC Step Response, Codes 0x40 - 0xC0, 255 μA Mode, Source Mode, Fast Mode, Vdda = 5 V

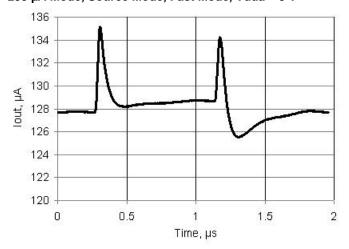

Figure 11-35. IDAC Glitch Response, Codes 0x7F - 0x80, 255  $\mu A$  Mode, Source Mode, Fast Mode, Vdda = 5 V

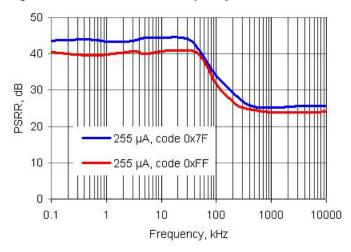

Figure 11-34. IDAC PSRR vs Frequency

Figure 11-36. IDAC Current Noise, 255  $\mu$ A Mode, Source Mode, Fast Mode,  $V_{DDA}$  = 5 V

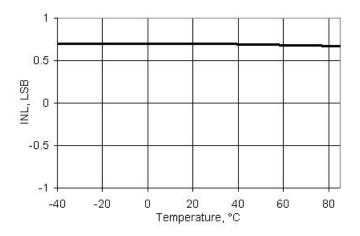

Figure 11-39. VDAC INL vs Temperature, 1 V Mode

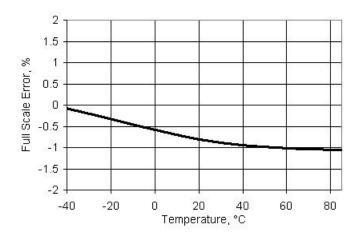

Figure 11-40. VDAC Full Scale Error vs Temperature, 1 V Mode

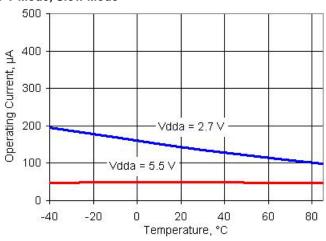

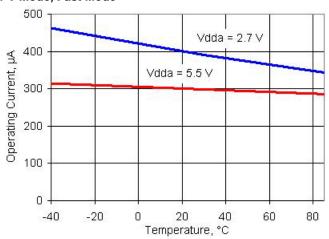

Figure 11-41. VDAC Operating Current vs Temperature, 1 V Mode, Slow Mode

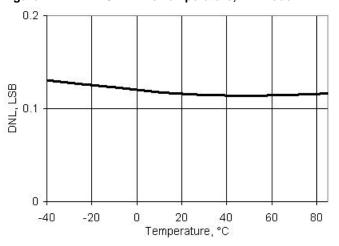

Figure 11-42. VDAC DNL vs Temperature, 1 V Mode

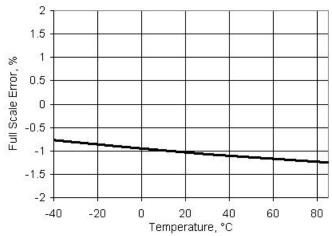

Figure 11-43. VDAC Full Scale Error vs Temperature, 4 V Mode

Figure 11-44. VDAC Operating Current vs Temperature, 1 V Mode, Fast Mode

# 11.6.5 USB

# Table 11-35. USB DC Specifications

| Parameter                   | Description                            | Conditions                                      | Min  | Тур | Max  | Units |

|-----------------------------|----------------------------------------|-------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>          | Device supply for USB operation        | USB configured, USB regulator enabled           | 4.35 | _   | 5.25 | V     |

| V <sub>USB_3.3</sub>        |                                        | USB configured, USB regulator bypassed          | 3.15 | _   | 3.6  | V     |

| I <sub>USB_Configured</sub> | Device supply current in device active | V <sub>DDD</sub> = 5 V, bus clock ≥ 33 MHz      | _    | 55  | _    | mA    |

|                             | mode                                   | V <sub>DDD</sub> = 3.3 V, bus clock ≥ 33 MHz    | _    | 40  | _    | mA    |

| I <sub>USB_Suspended</sub>  | Device supply current in device sleep  | $V_{DDD}$ = 5 V, connected to USB host          | _    | 0.5 | _    | mA    |

|                             | mode                                   | V <sub>DDD</sub> = 3.3 V, connected to USB host | _    | 0.5 | -    | mA    |

# 11.6.6 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of pre-built and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component data sheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

Table 11-36. UDB AC Specifications

| Douglas                |                                                               |                                                  |     |     |       |       |

|------------------------|---------------------------------------------------------------|--------------------------------------------------|-----|-----|-------|-------|

| Parameter              | Description                                                   | Conditions                                       | Min | Тур | Max   | Units |

| Datapath Per           | formance                                                      |                                                  |     |     |       |       |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                  | _   | _   | 40.01 | MHz   |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                  | _   | _   | 40.01 | MHz   |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit CRC/PRS in a UDB pair             |                                                  | -   | _   | 40.01 | MHz   |

| PLD Perform            | ance                                                          |                                                  |     |     |       |       |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass PLD function in a UDB pair    |                                                  | _   | _   | 40.01 | MHz   |

| Clock to Outp          | out Performance                                               |                                                  |     |     |       |       |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-49. | 25 °C                                            | _   | 20  | 28    | ns    |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-49. | Worst-case placement, routing, and pin selection | _   | _   | 55    | ns    |

All devices in the PSoC 5 CY8C52 family comply to RoHS-6 specifications, demonstrating the commitment by Cypress to lead-free products. Lead (Pb) is an alloying element in solders that has resulted in environmental concerns due to potential toxicity. Cypress uses nickel-palladium-gold (NiPdAu) technology for the majority of leadframe-based packages.

A high level review of the Cypress Pb-free position is available on our website. Specific package information is also available. Package Material Declaration data sheets (PMDDs) identify all substances contained within Cypress packages. PMDDs also confirm the absence of many banned substances. The information in the PMDDs will help Cypress customers plan for recycling or other "end of life" requirements.

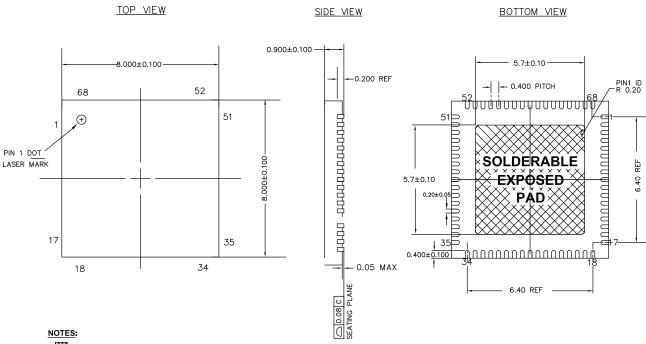

# 13. Packaging

**Table 13-1. Package Characteristics**

| Parameter      | Description                    | Conditions | Min | Тур | Max | Units   |

|----------------|--------------------------------|------------|-----|-----|-----|---------|

| T <sub>A</sub> | Operating ambient temperature  |            | -40 | 25  | 85  | °C      |

| $T_J$          | Operating junction temperature |            | -40 | _   | 100 | °C      |

| Tja            | Package θJA (68-pin QFN)       |            | _   | 15  | 1   | °C/Watt |

| Tja            | Package θJA (100-pin TQFP)     |            | _   | 34  | 1   | °C/Watt |

| Tjc            | Package θJC (68-pin QFN)       |            | _   | 13  | 1   | °C/Watt |

| Tjc            | Package θJC (100-pin TQFP)     |            | _   | 10  | -   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at<br>Peak Temperature |

|--------------|-----------------------------|-------------------------------------|

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

Figure 13-1. 68-pin QFN 8x8 with 0.4 mm Pitch Package Outline (Sawn Version)

- 1. XX HATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: 0.17g

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

Figure 13-2. 100-pin TQFP (14 x 14 x 1.4 mm) Package Outline

001-09618 \*D