Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 60                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 64K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 1x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5248axi-047 |

Table 4-6. Interrupt Vector Table (continued)

| Interrupt # | Cortex-M3 Exception # | Fixed Function       | DMA               | UDB          |

|-------------|-----------------------|----------------------|-------------------|--------------|

| 9           | 25                    | PICU[5]              | phub_termout0[9]  | udb_intr[9]  |

| 10          | 26                    | PICU[6]              | phub_termout0[10] | udb_intr[10] |

| 11          | 27                    | PICU[12]             | phub_termout0[11] | udb_intr[11] |

| 12          | 28                    | PICU[15]             | phub_termout0[12] | udb_intr[12] |

| 13          | 29                    | Comparators Combined | phub_termout0[13] | udb_intr[13] |

| 14          | 30                    | Reserved             | phub_termout0[14] | udb_intr[14] |

| 15          | 31                    | I <sup>2</sup> C     | phub_termout0[15] | udb_intr[15] |

| 16          | 32                    | Reserved             | phub_termout1[0]  | udb_intr[16] |

| 17          | 33                    | Reserved             | phub_termout1[1]  | udb_intr[17] |

| 18          | 34                    | Reserved             | phub_termout1[2]  | udb_intr[18] |

| 19          | 35                    | Reserved             | phub_termout1[3]  | udb_intr[19] |

| 20          | 36                    | Reserved             | phub_termout1[4]  | udb_intr[20] |

| 21          | 37                    | USB SOF Int          | phub_termout1[5]  | udb_intr[21] |

| 22          | 38                    | USB Arb Int          | phub_termout1[6]  | udb_intr[22] |

| 23          | 39                    | USB Bus Int          | phub_termout1[7]  | udb_intr[23] |

| 24          | 40                    | USB Endpoint[0]      | phub_termout1[8]  | udb_intr[24] |

| 25          | 41                    | USB Endpoint Data    | phub_termout1[9]  | udb_intr[25] |

| 26          | 42                    | Reserved             | phub_termout1[10] | udb_intr[26] |

| 27          | 43                    | Reserved             | phub_termout1[11] | udb_intr[27] |

| 28          | 44                    | Reserved             | phub_termout1[12] | udb_intr[28] |

| 29          | 45                    | Decimator Int        | phub_termout1[13] | udb_intr[29] |

| 30          | 46                    | phub_err_int         | phub_termout1[14] | udb_intr[30] |

| 31          | 47                    | eeprom_fault_int     | phub_termout1[15] | udb_intr[31] |

# 5.5 Memory Map

The Cortex-M3 has a fixed address map, which allows peripherals to be accessed by simple memory access instructions.

### 5.5.1 Address Map

The 4-GB address space is divided into the ranges shown in Table 5-2:

Table 5-2. Address Map

| Address Range              | Size   | Use                                                                                                                                     |

|----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000000 –<br>0x1FFFFFF  | 0.5 GB | Program code. This includes<br>the exception vector table at<br>power up, which starts at<br>address 0.                                 |

| 0x20000000 –<br>0x3FFFFFF  | 0.5 GB | Static RAM. This includes a 1 MByte bit-band region starting at 0x20000000 and a 32 Mbyte bit-band alias region starting at 0x22000000. |

| 0x40000000 –<br>0x5FFFFFFF | 0.5 GB | Peripherals.                                                                                                                            |

| 0x60000000 –<br>0x9FFFFFF  | 1 GB   | External RAM.                                                                                                                           |

| 0xA0000000 –<br>0xDFFFFFFF | 1 GB   | External peripherals.                                                                                                                   |

| 0xE0000000 -<br>0xFFFFFFF  | 0.5 GB | Internal peripherals, including the NVIC and debug and trace modules.                                                                   |

Table 5-3. Peripheral Data Address Map

| Address Range           | Purpose                         |

|-------------------------|---------------------------------|

| 0x00000000 – 0x0003FFFF | 256 K Flash                     |

| 0x1FFF8000 – 0x1FFFFFF  | 32 K SRAM in Code region        |

| 0x20000000 - 0x20007FFF | 32 K SRAM in SRAM region        |

| 0x40004000 - 0x400042FF | Clocking, PLLs, and oscillators |

| 0x40004300 - 0x400043FF | Power management                |

| 0x40004500 - 0x400045FF | Ports interrupt control         |

Table 5-3. Peripheral Data Address Map (continued)

| Address Range           | Purpose                                                   |

|-------------------------|-----------------------------------------------------------|

| 0x40004700 - 0x400047FF | Flash programming interface                               |

| 0x40004800 - 0x400048FF | Cache controller                                          |

| 0x40004900 - 0x400049FF | I <sup>2</sup> C controller                               |

| 0x40004E00 - 0x40004EFF | Decimator                                                 |

| 0x40004F00 - 0x40004FFF | Fixed timer/counter/PWMs                                  |

| 0x40005000 - 0x400051FF | I/O ports control                                         |

| 0x40005800 - 0x40005FFF | Analog Subsystem Interface                                |

| 0x40006000 - 0x400060FF | USB Controller                                            |

| 0x40006400 - 0x40006FFF | UDB Configuration                                         |

| 0x40007000 - 0x40007FFF | PHUB Configuration                                        |

| 0x40008000 - 0x400087FF | EEPROM                                                    |

| 0x40010000 - 0x4001FFFF | Digital Interconnect Configuration                        |

| 0xE0000000 – 0xE00FFFFF | Cortex-M3 PPB Registers, including NVIC, debug, and trace |

The bit-band feature allows individual bits in SRAM to be read or written as atomic operations. This is done by reading or writing bit 0 of corresponding words in the bit-band alias region. For example, to set bit 3 in the word at address 0x20000000, write a 1 to address 0x2200000C. To test the value of that bit, read address 0x2200000C and the result is either 0 or 1 depending on the value of the bit.

Most memory accesses done by the Cortex-M3 are aligned, that is, done on word (4-byte) boundary addresses. Unaligned accesses of words and 16-bit half-words on nonword boundary addresses can also be done, although they are less efficient.

### 5.5.2 Address Map and Cortex-M3 Buses

The ICode and DCode buses are used only for accesses within the Code address range, 0 - 0x1FFFFFF.

The system bus is used for data accesses and debug accesses within the ranges 0x20000000 - 0xDFFFFFFF and 0xE0100000 - 0xFFFFFFF. Instruction fetches can also be done within the range 0x20000000 - 0x3FFFFFFF, although these can be slower than instruction fetches via the ICode bus.

The private peripheral bus (PPB) is used within the Cortex-M3 to access system control registers and debug and trace module registers.

### 6.2.1 Power Modes

PSoC 5 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low power and portable devices.

PSoC 5 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from reset. Figure 6-5 on page 24 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all V<sub>DDIO</sub> supplies are at valid voltage levels and interrupts are enabled.

Active is the main processing mode. Its functionality is

disabled by using separate power configuration template

configurable. Each power controllable subsystem is enabled or

Table 6-2. Power Modes

| <b>Power Modes</b>  | Description                                                                                                                                                                                                   | <b>Entry Condition</b>                     | Wakeup Source      | Active Clocks           | Regulator                        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|-------------------------|----------------------------------|

| Active              | Primary mode of operation, all peripherals available (programmable)                                                                                                                                           | Wakeup, reset,<br>manual register<br>entry | Any interrupt      | Any (program-<br>mable) | All regulators available.        |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off | Manual register<br>entry                   | Any interrupt      | Any (program-<br>mable) | All regulators available.        |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                         | Manual register entry                      | CTW <sup>[8]</sup> | ILO                     | All regulators available.        |

| Hibernate           | All subsystems automatically disabled Lowest power consuming mode with all peripherals and internal regulators disabled, except hibernate regulator is enabled Configuration and memory contents retained     | Manual register<br>entry                   |                    |                         | Only hibernate regulator active. |

### Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(Typ)    | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources | Reset<br>Sources |

|---------------------|----------------|---------------------|-------------------|----------------------|---------------------|----------------------------|----------------|------------------|

| Active              | -              | 6 mA <sup>[7]</sup> | Yes               | All                  | All                 | All                        | _              | All              |

| Alternate<br>Active | -              | _                   | User<br>defined   | All                  | All                 | All                        | -              | All              |

| Sleep               | 125 µs typ     | 2 μA <sup>[8]</sup> | No                | None                 | None                | ILO                        | CTW            | XRES             |

| Hibernate           | -              | 300 nA              | No                | None                 | None                | None                       | _              | XRES             |

### Notes

- 7. Bus clock off. Execute from CPU instruction buffer at 6 MHz. See Table 11-2 on page 54

- Busing sleep mode, the CTW generates periodic interrupts to wake up the device. This affects the average current, which is a composite of the sleep mode current and active mode current, and the time spent in each mode. With the maximum wakeup interval of 128 ms, and at wakeup the CPU executes only the standard PSoC Creator sleep API (for a duty cycle of 0.2%), the average current draw is typically 35 μA.

Document Number: 001-66236 Rev. \*D

The term **system reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register shows some of the resets or power voltage monitoring interrupts. The program may examine this register to detect and report certain exception conditions. This register is cleared after a power-on reset. For details see the Technical Reference Manual.

### 6.3.1 Power Voltage Level Monitors

### ■ IPOR - Initial Power on Reset

At initial power on, IPOR monitors the power voltages  $V_{DDD}$  and  $V_{DDA}$ , both directly at the pins and at the outputs of the corresponding internal regulators. The trip level is not precise. It is set to approximately 1 volt, which is below the lowest specified operating voltage but high enough for the internal circuits to be reset and to hold their reset state. The monitor generates a reset pulse that is at least 100 ns wide. It may be much wider if one or more of the voltages ramps up slowly. To save power the IPOR circuit is disabled when the internal digital supply is stable. When the voltage is high enough, the IMO starts.

ALVI, DLVI, AHVI - Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

Interrupt circuits are available to detect when  $V_{DDA}$  and  $V_{DDD}$  go outside a voltage range. For AHVI,  $V_{DDA}$  is compared to a fixed trip level. For ALVI and DLVI,  $V_{DDA}$  and  $V_{DDD}$  are compared to trip levels that are programmable, as listed in Table 6-4.

Table 6-4. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply           | Normal<br>Voltage<br>Range | Available Trip<br>Settings                                              |

|-----------|------------------|----------------------------|-------------------------------------------------------------------------|

| DLVI      | V <sub>DDD</sub> | 2.7 V-5.5 V                | 2.45 V-5.45 V in 250 mV increments. The 2.45 V setting is used for LVD. |

| ALVI      | V <sub>DDA</sub> | 2.7 V-5.5 V                | 2.45 V-5.45 V in 250 mV increments. The 2.45 V setting is used for LVD. |

| AHVI      | $V_{DDA}$        | 2.7 V-5.5 V                | 5.75 V                                                                  |

The monitors are disabled until after IPOR. The monitors are not available in low-power modes. To monitor voltages in sleep mode, wake up periodically using the CTW. After wakeup, the 2.45 V LVI interrupt may trigger. Voltage monitoring is not available in hibernate mode.

### 6.3.2 Other Reset Sources

# ■ XRES - External Reset

CY8C52 has a dedicated XRES pin which holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull up resistor. XRES is active during sleep and hibernate modes.

### ■ SRES - Software Reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

### ■ WRES - Watchdog Timer Reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event. The watchdog timer can be used only when the part remains in active mode.

# 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the  $V_{\rm DDIO}$  pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense, and LCD segment drive, while SIO pins are used for voltages in excess of V<sub>DDA</sub> and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ Separate I/O supplies and voltages for up to four groups of I/O

- □ Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- □ Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- □ Special functionality on a pin by pin basis

### 6.4.1 Drive Modes

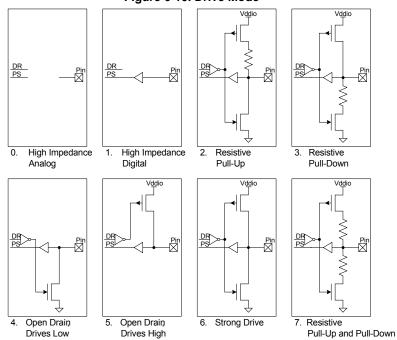

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-5. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-10 depicts a simplified pin view based on each of the eight drive modes. Table 6-5 shows the I/O pin's drive state based on the port data register value or digital array signal

if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

Figure 6-10. Drive Mode

Table 6-5. Drive Modes

| Diagram | Drive Mode                                     | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedence analog                          | 0       | 0       | 0       | High-Z        | High-Z       |

| 1       | High Impedance digital                         | 0       | 0       | 1       | High-Z        | High-Z       |

| 2       | Resistive pull-up <sup>[9]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[9]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                         | 1       | 0       | 0       | High-Z        | Strong Low   |

| 5       | Open drain, drive high                         | 1       | 0       | 1       | Strong High   | High-Z       |

| 6       | Strong drive                                   | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[9]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

# ■ High Impedance Analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

### ■ High Impedance Digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

### Note

<sup>9.</sup> Resistive pull up and pull down are not available with SIO in regulated output mode.

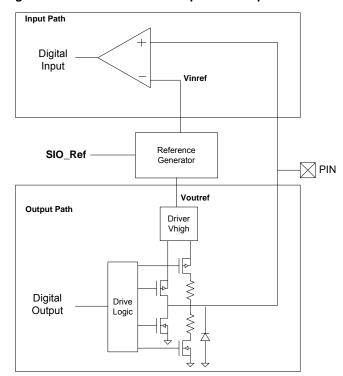

### 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective  $V_{\rm DDIO}.$  SIO pins are individually configurable to output either the standard  $V_{\rm DDIO}$  level or the regulated output, which is based on an internally generated reference. Typically the voltage DAC (VDAC) is used to generate the reference (see Figure 6-11). The DAC on page 48 has more details on VDAC use and reference routing to the SIO pins. Resistive pull up and pull down drive modes are not available with SIO in regulated output mode.

### 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from V<sub>DDIO</sub>. The reference sets the pins voltage threshold for a high logic level (see Figure 6-11). Available input thresholds are:

- 0.5 × V<sub>DDIO</sub>

- 0.4 × V<sub>DDIO</sub>

- 0.5 × V<sub>RFF</sub>

- V<sub>RFF</sub>

Typically the voltage DAC (VDAC) generates the  $V_{REF}$  reference. The DAC on page 48 has more details on VDAC use and reference routing to the SIO pins.

Figure 6-11. SIO Reference for Input and Output

### 6.4.13 SIO as Comparator

This section applies only to SIO pins. The adjustable input level feature of the SIOs as explained in the Adjustable Input Level section can be used to construct a comparator. The threshold for the comparator is provided by the SIO's reference generator. The reference generator has the option to set the analog signal routed through the analog global line as threshold for the comparator. Note that a pair of SIO pins share the same threshold.

The digital input path in Figure 6-8 on page 28 illustrates this functionality. In the figure, 'Reference level' is the analog signal routed through the analog global. The hysteresis feature can also be enabled for the input buffer of the SIO, which increases noise immunity for the comparator.

### 6.4.14 Hot Swap

This section applies only to SIO pins. SIO pins support 'hot swap' capability to plug into an application without loading the signals that are connected to the SIO pins even when no power is applied to the PSoC device. This allows the unpowered PSoC to maintain a high impedance load to the external device while also preventing the PSoC from being powered through a GPIO pin's protection diode.

## 6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage ( $V_{DDIO} < V_{IN} < V_{DDA}$ ) tolerance feature at any operating  $V_{DD}$ .

- There are no current limitations for the SIO pins as they present a high impedance load to the external circuit.

- The GPIO pins must be limited to 100 µA using a current limiting resistor. GPIO pins clamp the pin voltage to approximately one diode above the V<sub>DDIO</sub> supply.

- In case of a GPIO pin configured for analog input/output, the analog voltage on the pin must not exceed the V<sub>DDIO</sub> supply voltage to which the GPIO belongs.

A common application for this feature is connection to a bus such as  $\rm I^2C$  where different devices are running from different supply voltages. In the  $\rm I^2C$  case, the PSoC chip is configured into the Open Drain, Drives Low mode for the SIO pin. This allows an external pull up to pull the  $\rm I^2C$  bus voltage above the PSoC pin supply. For example, the PSoC chip could operate at 2.7 V, and an external device could run from 5 V. Note that the SIO pin's  $\rm V_{IH}$  and  $\rm V_{IL}$  levels are determined by the associated  $\rm V_{DDIO}$  supply pin

The I/O pin must be configured into a high impedance drive mode, open drain low drive mode, or pull down drive mode, for over voltage tolerance to work properly. Absolute maximum ratings for the device must be observed for all I/O pins.

### 6.4.16 Reset Configuration

At reset, all I/Os are reset to the High Impedance Analog state.

### 6.4.17 Low Power Functionality

In all low power modes the I/O pins retain their state until the part is awakened and changed or reset.

## 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in "Pinouts" on page 5. The special features are:

- Digital

- □ 32.768 kHz crystal oscillator

- □ SWD and SWV interface pins

- External reset

- Analog

- □ High current IDAC output

- □ External reference inputs

# 7. Digital Subsystem

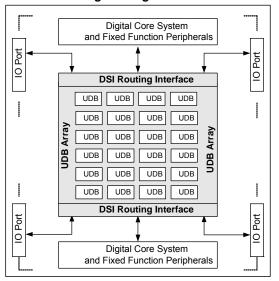

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

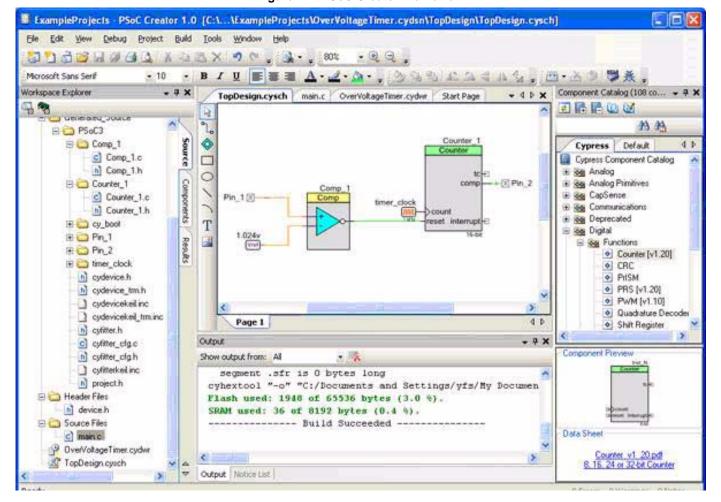

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. Designers do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

The main components of the digital programmable system are:

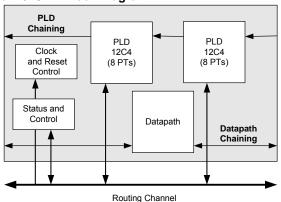

- Universal digital blocks (UDB) These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal digital block array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the digital system interconnect.

- Digital system interconnect (DSI) Digital signals from UDBs, fixed function peripherals, I/O pins, interrupts, DMA, and other system core signals are attached to the DSI to implement full featured device connectivity. The DSI allows any digital function to any pin or other feature routability when used with the UDB array.

Figure 7-1. CY8C52 Digital Programmable Architecture

# 7.1 Example Peripherals

The flexibility of the CY8C52 family's UDBs and analog blocks allow you to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog. However, you may also create your own custom components using PSoC Creator. Using PSoC Creator, you may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the data sheet, and the list is always growing. An example of a component available for use in CY8C52 family, but, not explicitly called out in this data sheet is the UART component.

## 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C52 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- □ I<sup>2</sup>C (1 to 3 UDBs)

- uART (1 to 3 UDBs)

- Functions

- PWM (1 to 2 UDBs)

- Logic (x CPLD product terms per logic function)

- □ NOT

- OR

- XOR

- AND

Figure 7-2. PSoC Creator Framework

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

### 7.2 Universal Digital Block

The universal digital block (UDB) represents an evolutionary step to the next generation of PSoC embedded digital peripheral functionality. The architecture in first generation PSoC digital blocks provides coarse programmability in which a few fixed functions with a small number of options are available. The new UDB architecture is the optimal balance between configuration granularity and efficient implementation. A cornerstone of this approach is to provide the ability to customize the devices digital operation to match application requirements.

To achieve this, UDBs consist of a combination of uncommitted logic (PLD), structured logic (datapath), and a flexible routing scheme to provide interconnect between these elements, I/O connections, and other peripherals. UDB functionality ranges from simple self contained functions that are implemented in one UDB, or even a portion of a UDB (unused resources are available for other functions), to more complex functions that require multiple UDBs. Examples of basic functions are timers, counters, CRC generators, PWMs, dead band generators, and communications functions, such as UARTs, SPI, and I<sup>2</sup>C. Also, the PLD blocks and connectivity provide full featured general purpose programmable logic within the limits of the available resources.

Figure 7-6. UDB Block Diagram

The main component blocks of the UDB are:

- PLD blocks: There are two small PLDs per UDB. These blocks take inputs from the routing array and form registered or combinational sum-of-products logic. PLDs are used to implement state machines, state bits, and combinational logic equations. PLD configuration is automatically generated from graphical primitives.

- Datapath module: This 8-bit wide datapath contains structured logic to implement a dynamically configurable ALU, a variety of compare configurations and condition generation. This block also contains input/output FIFOs, which are the primary parallel data interface between the CPU/DMA system and the UDB.

- Status and control module: The primary role of this block is to provide a way for CPU firmware to interact and synchronize with UDB operation.

- Clock and reset module: This block provides the UDB clocks and reset selection and control.

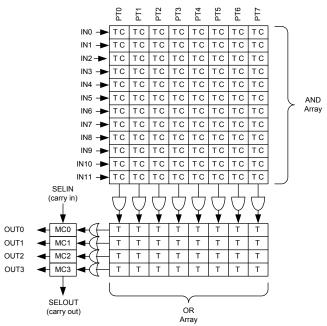

### 7.2.1 PLD Module

The primary purpose of the PLD blocks is to implement logic expressions, state machines, sequencers, look up tables, and decoders. In the simplest use model, consider the PLD blocks as a standalone resource onto which general purpose RTL is synthesized and mapped. The more common and efficient use model is to create digital functions from a combination of PLD and datapath blocks, where the PLD implements only the random logic and state portion of the function while the datapath (ALU) implements the more structured elements.

Figure 7-7. PLD 12C4 Structure

One 12C4 PLD block is shown in Figure 7-7. This PLD has 12 inputs, which feed across eight product terms. Each product term (AND function) can be from 1 to 12 inputs wide, and in a given product term, the true (T) or complement (C) of each input can be selected. The product terms are summed (OR function) to create the PLD outputs. A sum can be from 1 to 8 product terms wide. The 'C' in 12C4 indicates that the width of the OR gate (in this case 8) is constant across all outputs (rather than variable as in a 22V10 device). This PLA like structure gives maximum flexibility and insures that all inputs and outputs are permutable for ease of allocation by the software tools. There are two 12C4 PLDs in each UDB.

### 7.2.2 Datapath Module

The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators and many others.

# PSoC® 5: CY8C52 Family Datasheet

The PSoC Creator software program provides a user-friendly interface to configure the analog connections between the GPIO and various analog resources and also connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to configure the various analog blocks to perform application specific functions. The tool also generates API interface libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

# 8.1 Analog Routing

The PSoC 5 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks. All analog routing switches are open when the device is in sleep or hibernate mode.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 Analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- 8 Analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the PSoC 5 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in PSoC 5, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2.

Table 11-6. GPIO DC Specifications (continued)

| Parameter | Description                                                                 | Conditions                       | Min | Тур | Max | Units |

|-----------|-----------------------------------------------------------------------------|----------------------------------|-----|-----|-----|-------|

| Idiode    | Current through protection diode to V <sub>DDIO</sub> and V <sub>SSIO</sub> |                                  | _   | _   | 100 | μA    |

| Rglobal   | Resistance pin to analog global bus                                         | 25 °C, V <sub>DDIO</sub> = 3.0 V | _   | 320 | _   | Ω     |

| Rmux      | Resistance pin to analog mux bus                                            | 25 °C, V <sub>DDIO</sub> = 3.0 V | _   | 220 | _   | Ω     |

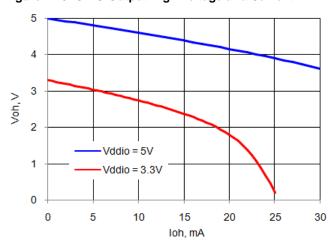

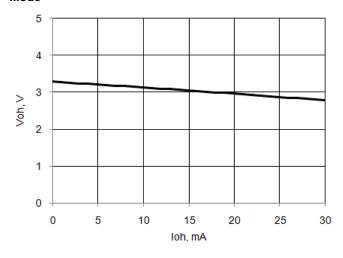

Figure 11-5. GPIO Output High Voltage and Current

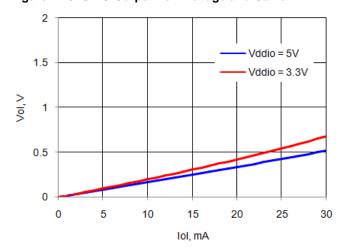

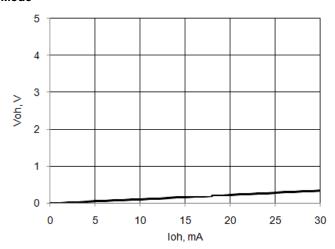

Figure 11-6. GPIO Output Low Voltage and Current

# 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 54.

Table 11-10. USBIO DC Specifications

| Parameter                       | Description                                 | Conditions                                         | Min            | Тур | Max            | Units |

|---------------------------------|---------------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                           | USB D+ pull-up resistance                   | With idle bus                                      | 0.900          | _   | 1.575          | kΩ    |

| Rusba                           | USB D+ pull-up resistance                   | While receiving traffic                            | 1.425          | -   | 3.090          | kΩ    |

| Vohusb                          | Static output high                          | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb                          | Static output low                           | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | -              | _   | 0.3            | V     |

| Vihgpio                         | Input voltage high, GPIO mode               | $V_{DDD} \ge 3 \text{ V}$                          | 2              | _   | _              | V     |

| Vilgpio                         | Input voltage low, GPIO mode                | $V_{DDD} \ge 3 \text{ V}$                          | _              | _   | 0.8            | V     |

| Vohgpio                         | Output voltage high, GPIO mode              | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | 2.4            | _   | _              | V     |

| Volgpio                         | Output voltage low, GPIO mode               | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | _              | _   | 0.3            | V     |

| Vdi                             | Differential input sensitivity              | (D+)-(D-)                                          | -              | _   | 0.2            | V     |

| Vcm                             | Differential input common mode range        |                                                    | 8.0            | -   | 2.5            | V     |

| Vse                             | Single ended receiver threshold             |                                                    | 8.0            | -   | 2              | V     |

| Rps2                            | PS/2 pull-up resistance                     | In PS/2 mode, with PS/2 pull-up enabled            | 3              | _   | 7              | kΩ    |

| Rext                            | External USB series resistor                | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                              | USB driver output impedance <sup>[27]</sup> | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub>                 | USB transceiver input capacitance           |                                                    | _              | _   | 20             | pF    |

| I <sub>IL</sub> <sup>[28]</sup> | Input leakage current (absolute value)      | 25 °C, V <sub>DDD</sub> = 3.0 V                    | -              | _   | 2              | nA    |

Figure 11-14. USBIO Output High Voltage and Current, GPIO Mode

Figure 11-15. USBIO Output Low Voltage and Current, GPIO Mode

- 27. This parameter is not production tested and cannot be guaranteed over all temperatures.

28. Based on device characterization (Not production tested).

# 11.5.3 Analog Globals

# Table 11-18. Analog Globals DC Specifications

| Parameter | Description                                  | Conditions               | Min | Тур  | Max  | Units |

|-----------|----------------------------------------------|--------------------------|-----|------|------|-------|

| 110       | Resistance pin-to-pin through analog global  | V <sub>DDA</sub> = 3.0 V | 1   | 1200 | 1500 | Ω     |

|           | Resistance pin-to-pin through analog mux bus | V <sub>DDA</sub> = 3.0 V | _   | 700  | 1000 | Ω     |

# 11.5.4 Comparator

# Table 11-19. Comparator DC Specifications

| Parameter         | Description                                  | Conditions                            | Min              | Тур | Max                    | Units |

|-------------------|----------------------------------------------|---------------------------------------|------------------|-----|------------------------|-------|

| V                 | Input offset voltage in fast mode            | Factory trim, V <sub>IN</sub> ≥ 0.5 V | _                |     | 15                     | mV    |

| V <sub>OS</sub>   | Input offset voltage in slow mode            | Factory trim, V <sub>IN</sub> ≥ 0.5 V | -                |     | 15                     | mV    |

| V <sub>OS</sub>   | Input offset voltage in ultra low power mode |                                       | -                | ±12 | -                      | mV    |

| V <sub>HYST</sub> | Hysteresis                                   | Hysteresis enable mode                | -                | 10  | 32                     | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                    | High current / fast mode              | V <sub>SSA</sub> | _   | V <sub>DDA</sub> – 0.1 | V     |

|                   |                                              | Low current / slow mode               | V <sub>SSA</sub> | -   | $V_{DDA}$              | V     |

|                   |                                              | Ultra low power mode                  | V <sub>SSA</sub> | _   | V <sub>DDA</sub> – 0.9 |       |

| CMRR              | Common mode rejection ratio                  |                                       | _                | 50  | _                      | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode <sup>[31]</sup>  |                                       | -                | -   | 400                    | μA    |

|                   | Low current mode/slow mode <sup>[31]</sup>   |                                       | -                | _   | 100                    | μA    |

|                   | Ultra low power mode <sup>[31]</sup>         |                                       | _                | 6   | _                      | μA    |

# Table 11-20. Comparator AC Specifications

| Parameter         | Description                                         | Conditions                           | Min | Тур | Max | Units |

|-------------------|-----------------------------------------------------|--------------------------------------|-----|-----|-----|-------|

|                   | Response time, high current mode <sup>[31]</sup>    | 50 mV overdrive, measured pin-to-pin | -   | 75  | 110 | ns    |

| T <sub>RESP</sub> | Response time, low current mode <sup>[31]</sup>     | 50 mV overdrive, measured pin-to-pin | _   | 155 | 200 | ns    |

|                   | Response time, ultra low power mode <sup>[31]</sup> | 50 mV overdrive, measured pin-to-pin | _   | 55  | _   | μs    |

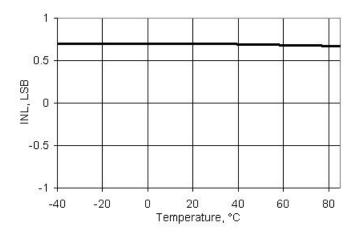

Figure 11-39. VDAC INL vs Temperature, 1 V Mode

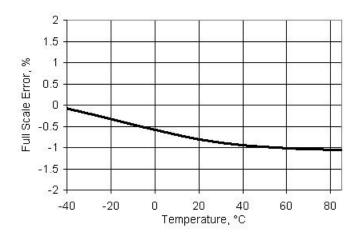

Figure 11-40. VDAC Full Scale Error vs Temperature, 1 V Mode

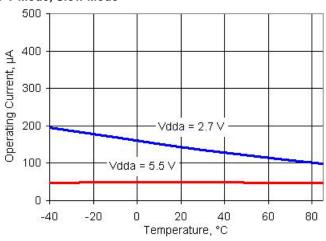

Figure 11-41. VDAC Operating Current vs Temperature, 1 V Mode, Slow Mode

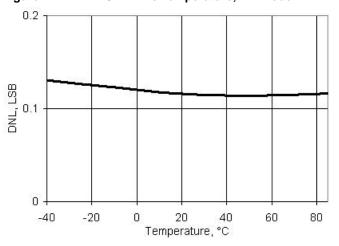

Figure 11-42. VDAC DNL vs Temperature, 1 V Mode

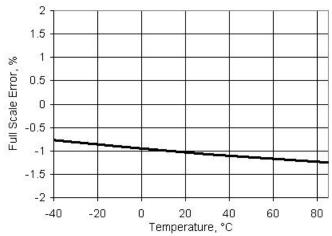

Figure 11-43. VDAC Full Scale Error vs Temperature, 4 V Mode

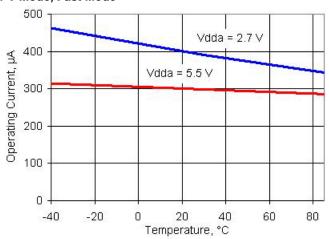

Figure 11-44. VDAC Operating Current vs Temperature, 1 V Mode, Fast Mode

# 11.5.7 LCD Direct Drive

# Table 11-25. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                          | Min  | Тур  | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Icc                 | LCD system operating current                                                        | Bus clock = 3 MHz, Vddio = Vdda = 3 V, 4 commons, 16 segments, 1/4 duty cycle, 50 Hz frame rate, no glass connected | -    | 63   | I    | μА    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          |                                                                                                                     | -    | 148  | _    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | 3 V $\leq$ V <sub>BIAS</sub> $\leq$ V <sub>DDIO</sub> for the drive pin                                             | 2.09 | _    | 5.2  | V     |

|                     | LCD bias step size                                                                  | $3 \text{ V} \le V_{BIAS} \le V_{DDIO}$ for the drive pin                                                           | _    | 25.8 | _    | mV    |

|                     | LCD capacitance per segment/common driver                                           | Drivers may be combined                                                                                             | _    | 500  | 5000 | pF    |

|                     | Long term segment offset                                                            | $V_{BIAS} \le V_{DDA} - 0.5 V$                                                                                      | _    | _    | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver                                             | Vddio = 5.5V                                                                                                        | 90   | _    | 165  | μA    |

# Table 11-26. LCD Direct Drive AC Specifications

| Parameter | Description    | Conditions | Min | Тур | Max | Units |

|-----------|----------------|------------|-----|-----|-----|-------|

| $f_{LCD}$ | LCD frame rate |            | 10  | 50  | 150 | Hz    |

# 11.6 Digital Peripherals

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 2.7 V to 5.5 V, except where noted.

### 11.6.1 Timer

The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; for more information, see the Timer component data sheet in PSoC Creator.

Table 11-27. Timer DC Specifications

| Parameter | Description | Conditions                     | Min | Тур | Max | Units |

|-----------|-------------|--------------------------------|-----|-----|-----|-------|

|           |             | Input clock frequency – 3 MHz  | _   | 65  | _   | μΑ    |

|           | consumption | Input clock frequency –12 MHz  | _   | 170 | -   | μA    |

|           |             | Input clock frequency – 40 MHz | -   | 650 | -   | μA    |

# Table 11-28. Timer AC Specifications

| Parameter | Description                    | Conditions | Min | Тур | Max   | Units |

|-----------|--------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency            |            | DC  | _   | 40.01 | MHz   |

|           | Capture pulse width (Internal) |            | 25  | _   | _     | ns    |

|           | Capture pulse width (external) |            | 30  | _   | -     | ns    |

|           | Timer resolution               |            | 25  | _   | _     | ns    |

|           | Enable pulse width             |            | 25  | _   | _     | ns    |

|           | Enable pulse width (external)  |            | 30  | _   | -     | ns    |

|           | Reset pulse width              |            | 25  | _   | -     | ns    |

|           | Reset pulse width (external)   |            | 30  | _   | _     | ns    |

### 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component data sheet in PSoC Creator.

Table 11-29. Counter DC Specifications

| Parameter | Description | Conditions                                      | Min | Тур | Max | Units |

|-----------|-------------|-------------------------------------------------|-----|-----|-----|-------|

|           | •           | 16-bit counter, at listed input clock frequency | _   | _   | -   | μA    |

|           | 3 MHz       |                                                 | _   | 15  | _   | μA    |

|           | 12 MHz      |                                                 | _   | 60  | _   | μA    |

|           | 40 MHz      |                                                 | _   | 260 | _   | μA    |

# Table 11-30. Counter AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | _   | 40.01 | MHz   |

|           | Capture pulse                 |            | 25  | -   | _     | ns    |

|           | Resolution                    |            | 25  | -   | _     | ns    |

|           | Pulse width                   |            | 25  | -   | _     | ns    |

|           | Pulse width (external)        |            | 30  |     |       | ns    |

|           | Enable pulse width            |            | 25  | -   | _     | ns    |

|           | Enable pulse width (external) |            | 30  | -   | _     | ns    |

|           | Reset pulse width             |            | 25  | _   | -     | ns    |

|           | Reset pulse width (external)  |            | 30  | _   | _     | ns    |

Document Number: 001-66236 Rev. \*D Page 78 of 97

# 11.6.3 Pulse Width Modulation

The following specifications apply to the Timer/Counter/PWM peripheral, in PWM mode. PWM components can also be implemented in UDBs; for more information, see the PWM component data sheet in PSoC Creator.

# Table 11-31. PWM DC Specifications

| Parameter | Description                          | Conditions                     | Min | Тур | Max | Units |

|-----------|--------------------------------------|--------------------------------|-----|-----|-----|-------|

|           | 16-bit PWM block current consumption | Input clock frequency – 3 MHz  | -   | 65  | _   | μA    |

|           |                                      | Input clock frequency –12 MHz  | _   | 170 | _   | μA    |

|           |                                      | Input clock frequency – 40 MHz | -   | 650 | -   | μA    |

# Table 11-32. PWM AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | _   | 40.01 | MHz   |

|           | Pulse width                   |            | 25  | -   | -     | ns    |

|           | Pulse width (external)        |            | 30  | _   | _     | ns    |

|           | Kill pulse width              |            | 25  | _   | _     | ns    |

|           | Kill pulse width (external)   |            | 30  | -   | -     | ns    |

|           | Enable pulse width            |            | 25  | _   | _     | ns    |

|           | Enable pulse width (external) |            | 30  | _   | _     | ns    |

|           | Reset pulse width             |            | 25  | _   | _     | ns    |

|           | Reset pulse width (external)  |            | 30  | _   | _     | ns    |

# 11.6.4 PC

# Table 11-33. Fixed I<sup>2</sup>C DC Specifications

| Parameter | Description               | Conditions                       | Min | Тур | Max | Units |

|-----------|---------------------------|----------------------------------|-----|-----|-----|-------|

|           | Block current consumption | Enabled, configured for 100 kbps | _   | 90  | 250 | μΑ    |

|           |                           | Enabled, configured for 400 kbps | -   | 100 | 250 | μΑ    |

# Table 11-34. Fixed I<sup>2</sup>C AC Specifications

| Parameter | Description | Conditions | Min | Тур | Max | Units |

|-----------|-------------|------------|-----|-----|-----|-------|

|           | Bit rate    |            | -   | _   | 400 | Kbps  |

Document Number: 001-66236 Rev. \*D Page 79 of 97

# 11.9.5 External Clock Reference

# Table 11-55. External Clock Reference AC Specifications [42]

| Parameter | Description              | Conditions                         | Min | Тур | Max | Units |

|-----------|--------------------------|------------------------------------|-----|-----|-----|-------|

|           | External frequency range |                                    | 0   | _   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30  | 50  | 70  | %     |

|           | Input edge rate          | V <sub>IL</sub> to V <sub>IH</sub> | 0.5 | -   | -   | V/ns  |

### 11.9.6 Phase-Locked Loop

# Table 11-56. PLL DC Specifications

| Parameter | Description           | Conditions               | Min | Тур | Max | Units |

|-----------|-----------------------|--------------------------|-----|-----|-----|-------|

| $I_{DD}$  | PLL operating current | In = 3 MHz, Out = 24 MHz | 1   | 200 | 1   | μΑ    |

# Table 11-57. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Max | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[43]</sup>        |                     | 1   | _   | 40  | MHz   |

|             | PLL intermediate frequency <sup>[44]</sup> | Output of prescaler | 1   | _   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[43]</sup>       |                     | 24  | -   | 40  | MHz   |

|             | Lock time at startup                       |                     | _   | _   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[42]</sup>               |                     | -   | _   | 400 | ps    |

# Notes

42. Based on device characterization (Not production tested).

43. This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL.

44. PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16.

# 12. Ordering Information

In addition to the features listed in Table 12-1, every CY8C52 device includes: up to 256 KB flash, 64 KB SRAM, 2 KB EEPROM, a precision on-chip voltage reference, precision oscillators, flash, DMA, a fixed function I<sup>2</sup>C, SWD programming and debug, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C52 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

Table 12-1. CY8C52 Family with ARM Cortex-M3 CPU

|                 |                 | MCU        | Core      |             |                   | ,            | Anal | og          |                     |        |     |          | D                    | igita            | ıl     |           | I/O[ | 46] |       |              |                           |

|-----------------|-----------------|------------|-----------|-------------|-------------------|--------------|------|-------------|---------------------|--------|-----|----------|----------------------|------------------|--------|-----------|------|-----|-------|--------------|---------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC          | DAC  | Comparators | SC/CT Analog Blocks | Opamps | DFB | CapSense | UDBS <sup>[45]</sup> | 16-bit Timer/PWM | FS USB | Total I/O | GPIO | SIO | USBIO | Package      | Device ID <sup>[47]</sup> |

| CY8C5248LTI-030 | 40              | 256        | 64        | 2           | ~                 | 1x12-bit SAR | 1    | 2           | -                   | -      | -   | ~        | 24                   | 4                | ~      | 46        | 36   | 8   | 2     | 68-pin QFN   | 0x0E11E069                |

| CY8C5248AXI-047 | 40              | 256        | 64        | 2           | ~                 | 1x12-bit SAR | 1    | 2           | -                   | -      | _   | ~        | 24                   | 4                | ~      | 70        | 60   | 8   | 2     | 100-pin TQFP | 0x0E12F069                |

| CY8C5247LTI-089 | 40              | 128        | 32        | 2           | >                 | 1x12-bit SAR | 1    | 2           | -                   | -      | _   | ~        | 24                   | 4                | ~      | 46        | 36   | 8   | 2     | 68-pin QFN   | 0x0E159069                |

| CY8C5247AXI-051 | 40              | 128        | 32        | 2           | ~                 | 1x12-bit SAR | 1    | 2           | -                   | -      | _   | ~        | 24                   | 4                | ~      | 70        | 60   | 8   | 2     | 100-pin TQFP | 0x0E133069                |

| CY8C5246LTI-029 | 40              | 64         | 16        | 2           | ~                 | 1x12-bit SAR | 1    | 2           | _                   | _      | _   | ~        | 24                   | 4                | ~      | 46        | 36   | 8   | 2     | 68-pin QFN   | 0x0E11D069                |

| CY8C5246AXI-054 | 40              | 64         | 16        | 2           | >                 | 1x12-bit SAR | 1    | 2           | _                   | _      | _   | >        | 24                   | 4                | ~      | 70        | 60   | 8   | 2     | 100-pin TQFP | 0x0E136069                |

## 12.1 Part Numbering Conventions

PSoC 5 devices follow the part numbering convention described here. All fields are single character alphanumeric (0, 1, 2, ..., 9, A, B, ..., Z) unless stated otherwise.

CY8Cabcdefg-xxx

- a: Architecture

- □ 3: PSoC 3

- □ 5: PSoC 5

- b: Family group within architecture

- □ 2: CY8C52 family

- □ 3: CY8C53 family

- 4: CY8C54 family

- □ 5: CY8C55 family

- c: Speed grade

- □ 4: 40 MHz

- □ 6: 67 MHz

- d: Flash capacity

- □ 5: 32 KB

- □ 6: 64 KB

- □ 7: 128 KB

- 8: 256 KB

- ef: Package code

- Two character alphanumeric

- AX: TQFP

- LT: QFN

- g: Temperature range

- □ C: commercial

- I: industrial

- A: automotive

- xxx: Peripheral set

- □ Three character numeric

- No meaning is associated with these three characters

- 45. UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or

- multiple UDBs. Multiple functions can share a single UDB. See Example Peripherals on page 32 for more information on how UDBs can be used.

46. The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See I/O System and Routing on page 25 for details on the functionality of each of these types of I/O.

- 47. The device ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

Table 14-1. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |

|-------------------|--------------------------------------------------------------|

| PLD               | programmable logic device, see also PAL                      |

| PLL               | phase-locked loop                                            |

| PMDD              | package material declaration data sheet                      |

| POR               | power-on reset                                               |

| PRS               | pseudo random sequence                                       |

| PS                | port read data register                                      |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |

| PSRR              | power supply rejection ratio                                 |

| PWM               | pulse-width modulator                                        |

| RAM               | random-access memory                                         |

| RISC              | reduced-instruction-set computing                            |

| RMS               | root-mean-square                                             |

| RSVD              | reserved                                                     |

| RTC               | real-time clock                                              |

| RTL               | register transfer language                                   |

| RTR               | remote transmission request                                  |

| RX                | receive                                                      |

| SAR               | successive approximation register                            |

| SC/CT             | switched capacitor/continuous time                           |

| SCL               | I <sup>2</sup> C serial clock                                |

| SDA               | I <sup>2</sup> C serial data                                 |

| S/H               | sample and hold                                              |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |

| SNR               | signal-to-noise ratio                                        |

| SOC               | start of conversion                                          |

| SOF               | start of frame                                               |

Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                            |

|---------|------------------------------------------------------------------------|

| SPI     | Serial Peripheral Interface, a communications protocol                 |

| SR      | slew rate                                                              |

| SRAM    | static random access memory                                            |

| SRES    | software reset                                                         |

| SWD     | serial wire debug, a test protocol                                     |

| SWV     | single-wire viewer                                                     |

| TD      | transaction descriptor, see also DMA                                   |

| THD     | total harmonic distortion                                              |

| TIA     | transimpedance amplifier                                               |

| TRM     | technical reference manual                                             |

| TTL     | transistor-transistor logic                                            |

| TX      | transmit                                                               |

| UART    | Universal Asynchronous Transmitter Receiver, a communications protocol |

| UDB     | universal digital block                                                |

| USB     | Universal Serial Bus                                                   |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port              |

| VDAC    | voltage DAC, see also DAC, IDAC                                        |

| WDT     | watchdog timer                                                         |

| WOL     | write once latch, see also NVL                                         |

| WRES    | watchdog timer reset                                                   |

| XRES    | external reset I/O pin                                                 |

| XTAL    | crystal                                                                |

# 15. Reference Documents

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 5 Registers TRM