Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 14                                                                              |

| Program Memory Size        | 2KB (2K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | 20-LSSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10266gsp-x0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

<R>

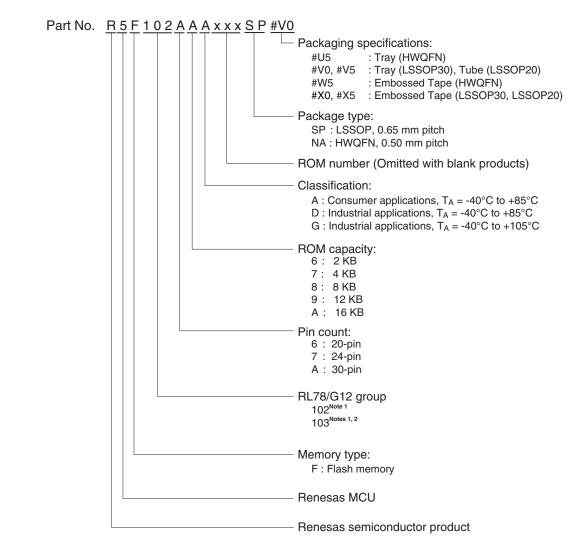

## 1.3 List of Part Numbers

Figure 1-1. Part Number, Memory Size, and Package of RL78/G12

- Notes 1. For details about the differences between the R5F102 products and the R5F103 products of RL78/G12, see 1.1 Differences between the R5F102 Products and the R5F103 Products.

- 2. Products only for "A: Consumer applications ( $T_A = -40$  to  $+85^{\circ}C$ )" and "D: Industrial applications ( $T_A = -40$  to  $+85^{\circ}C$ )"

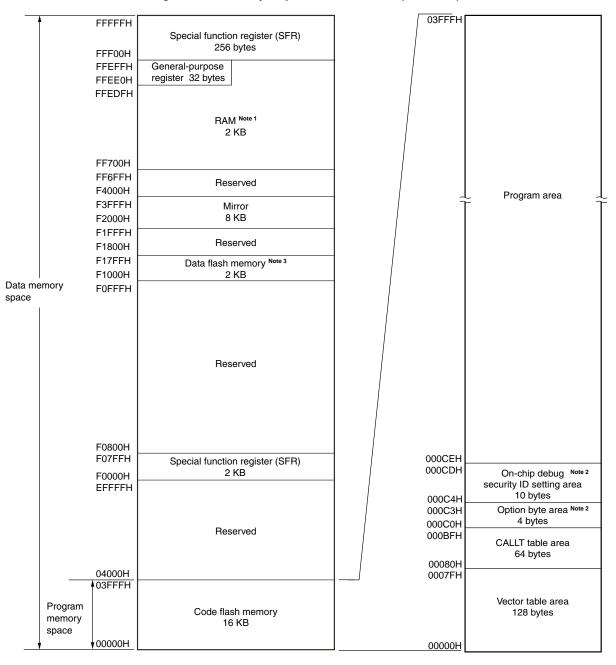

Figure 3-6. Memory Map for the R5F10xAA (x = 2 or 3)

- <R> Notes 1. Do not allocate the stack area, data buffers for use by the flash library, arguments of library functions, branch destinations in the processing of vectored interrupts, or destinations or sources for DMA transfer to the area from FFE20H to FFEDFH when performing self-programming or rewriting of the data flash memory.

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- 3. Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- 4. The areas are reserved in the R5F103AA.

- **Caution** While RAM parity error resets are enabled (RPERDIS = 0), be sure to initialize RAM areas where data access is to proceed and the RAM area +10 bytes when instructions are fetched from RAM areas, respectively. Reset signal generation sets RAM parity error resets to enabled (RPERDIS = 0). For details, see 21.3.2 RAM parity error detection.

| Address          | Special Function Register (SFR) Name                   | Syn            | Symbol R/W |     | Manipulable Bit Range |              |              | After Reset               |

|------------------|--------------------------------------------------------|----------------|------------|-----|-----------------------|--------------|--------------|---------------------------|

|                  |                                                        |                |            |     | 1-bit                 | 8-bit        | 16-bit       |                           |

| FFF44H           | Serial data register 02                                | TXD1/<br>SIO10 | SDR02      | R/W | -                     | V            | V            | 0000H                     |

| FFF45H           |                                                        | -              |            |     | =                     | -            |              |                           |

| FFF46H           | Serial data register 03                                | RXD1/<br>SIO11 | SDR03      | R/W | -                     | $\checkmark$ | $\checkmark$ | 0000H                     |

| FFF47H           |                                                        | _              |            |     | _                     | _            |              |                           |

| FFF48H           | Serial data register 10                                | TXD2/<br>SIO20 | SDR10      | R/W | -                     | $\checkmark$ | $\checkmark$ | 0000H                     |

| FFF49H           |                                                        | -              |            |     | -                     | -            |              |                           |

| FFF4AH           | Serial data register 11                                | RXD2/<br>SIO21 | SDR11      | R/W | -                     | $\checkmark$ | $\checkmark$ | 0000H                     |

| FFF4BH           |                                                        | _              |            |     | _                     | -            |              |                           |

| FFF50H           | IICA shift register 0                                  | IICA0          |            | R/W | _                     |              | -            | 00H                       |

| FFF51H           | IICA status register 0                                 | IICS0          |            | R   | $\checkmark$          | $\checkmark$ | _            | 00H                       |

| FFF52H           | IICA flag register 0                                   | IICF0          |            | R/W | $\checkmark$          | $\checkmark$ | -            | 00H                       |

| FFF64H           | Timer data register 02                                 | TDR02          |            | R/W | -                     | -            | $\checkmark$ | 0000H                     |

| FFF65H           |                                                        |                |            |     |                       |              |              |                           |

| FFF66H           | Timer data register 03                                 | TDR03L         | TDR03      | R/W | _                     | $\checkmark$ | $\checkmark$ | 00H                       |

| FFF67H           |                                                        | TDR03H         |            |     | _                     | $\checkmark$ |              | 00H                       |

| FFF68H<br>FFF69H | Timer data register 04                                 | TDR04          |            | R/W | -                     | -            | $\checkmark$ | 0000H                     |

| FFF6AH           | Timer data register 05                                 | TDR05          |            | R/W |                       |              | √            | 0000H                     |

| FFF6BH           |                                                        | TEHIOS         | 1000       |     |                       |              | v            | 000011                    |

| FFF6CH           | Timer data register 06                                 | TDR06          |            | R/W |                       | _            |              | 0000H                     |

| FFF6DH           |                                                        | 1 Bride        |            |     |                       |              |              | 000011                    |

| FFF6EH           | Timer data register 07                                 | TDR07          |            | R/W |                       | _            | √            | 0000H                     |

| FFF6FH           |                                                        |                |            |     |                       |              |              |                           |

| FFF90H           | Interval timer control register                        | ITMC           |            | R/W | _                     | _            |              | 0FFFH                     |

| FFF91H           |                                                        |                |            |     |                       |              |              |                           |

| FFFA0H           | Clock operation mode control register                  | СМС            |            | R/W | -                     | $\checkmark$ | _            | 00H                       |

| FFFA1H           | Clock operation status control register                | CSC            |            | R/W |                       | $\checkmark$ | _            | C0H                       |

| FFFA2H           | Oscillation stabilization time counter status register | OSTC           |            | R   | $\checkmark$          | V            | -            | 00H                       |

| FFFA3H           | Oscillation stabilization time select register         | OSTS           |            | R/W | _                     | V            | -            | 07H                       |

| FFFA4H           | System clock control register                          | СКС            |            | R/W | $\checkmark$          | $\checkmark$ | _            | 00H                       |

| FFFA5H           | Clock output select register 0                         | CKS0           |            | R/W | $\checkmark$          | $\checkmark$ | -            | 00H                       |

| FFFA6H           | Clock output select register 1                         | CKS1           |            | R/W | $\checkmark$          |              | -            | 00H                       |

| FFFA8H           | Reset control flag register                            | RESF           |            | R   | _                     | $\checkmark$ | -            | Undefined <sup>Note</sup> |

| FFFA9H           | Voltage detection register                             | LVIM           |            | R/W | $\checkmark$          |              | -            | 00H Note 1                |

| FFFAAH           | Voltage detection level register                       | LVIS           |            | R/W | $\checkmark$          |              | -            | 00H/01H/81H <sup>№</sup>  |

| FFFABH           | Watchdog timer enable register                         | WDTE           |            | R/W | -                     |              | -            | 1A/9A Note 2              |

| FFFACH           | CRC input register                                     | CRCIN          |            | R/W | _                     |              | _            | 00H                       |

## Table 3-6. SFR List (2/4)

#### 4.5.3 Register setting examples for using the port and alternate functions

Table 4-7 shows register setting examples for used port and alternate functions. Set the registers used to control the port function as shown in Table 4-7. See the following remark for legends used in Table 4-7.

| Remark | -: Not applie | -: Not applicable                                                                           |  |  |  |

|--------|---------------|---------------------------------------------------------------------------------------------|--|--|--|

|        | ×: don't ca   | are                                                                                         |  |  |  |

|        | PIORx:        | Peripheral I/O redirection register                                                         |  |  |  |

|        | POMxx:        | Port output mode register                                                                   |  |  |  |

|        | PMCxx:        | Port mode control register                                                                  |  |  |  |

|        | PMxx:         | Port mode register                                                                          |  |  |  |

|        | Pxx:          | Port output latch                                                                           |  |  |  |

|        | Functions in  | parentheses can be assigned via settings in the peripheral I/O redirection register (PIOR). |  |  |  |

# Table 4-7. Setting Examples of Registers and Output Latches When Using Alternate Function (20-, 24-Pin Products) (1/5)

| Pin Name              | Used Fu                   | unction                   | PIORx     | POMxx | PMCxx | PMxx | Pxx | Alternate Fund      | tion Output    |

|-----------------------|---------------------------|---------------------------|-----------|-------|-------|------|-----|---------------------|----------------|

|                       | Function Name             | I/O                       |           |       |       |      |     | SAU                 | Other than SAU |

| P00 <sup>Note 1</sup> | P00                       | Input                     | -         | -     | -     | 1    | ×   | -                   | —              |

|                       |                           | Output                    | -         | -     | _     | 0    | 0/1 | _                   | _              |

|                       | KR6                       | Input                     | -         | -     | -     | 1    | ×   | -                   | _              |

|                       | (SI01) <sup>Note 2</sup>  | Input                     | PIOR3 = 1 | -     | -     | 1    | ×   | -                   | —              |

| P01 <sup>Note 1</sup> | P01                       | Input                     | -         | ×     | -     | 1    | ×   | ×                   | _              |

|                       |                           | Output                    | _         | 0     | _     | 0    | 0/1 | (SO01)/(SDA01) = 1  | _              |

|                       |                           | N-ch open<br>drain output | _         | 1     | -     | 0    | 0/1 |                     | _              |

|                       | KR7                       | Input                     | -         | ×     | -     | 1    | ×   | ×                   | -              |

|                       | (SO01) <sup>Note 2</sup>  | Output                    | PIOR3 = 1 | 0/1   | -     | 0    | 1   | ×                   | —              |

|                       | (SDA01) <sup>Note 2</sup> | I/O                       | PIOR3 = 1 | 1     | -     | 0    | 1   | ×                   | —              |

| P02 <sup>Note 1</sup> | P02                       | Input                     | 1         | -     | -     | 1    | ×   | ×                   | —              |

|                       |                           | Output                    | 1         | -     | -     | 0    | 0/1 | (SCK01)/(SCL01) = 1 | —              |

|                       | KR8                       | Input                     | -         | -     | -     | 1    | ×   | ×                   | -              |

|                       | (SCK01) <sup>Note 2</sup> | Input                     | PIOR3 = 1 | -     | _     | 1    | ×   | ×                   | -              |

|                       |                           | Output                    | PIOR3 = 1 | -     | -     | 0    | 1   | ×                   | —              |

|                       | (SCL01) <sup>Note 2</sup> | Output                    | PIOR3 = 1 | -     | _     | 0    | 1   | ×                   | -              |

| P03 <sup>Note 1</sup> | P03                       | Input                     | -         | -     | -     | 1    | ×   | _                   | _              |

|                       |                           | Output                    | -         | -     | -     | 0    | 0/1 | -                   | —              |

|                       | KR9                       | Input                     | -         | -     | -     | 1    | ×   | -                   | _              |

| P10                   | P10                       | Input                     | -         | ×     | 0     | 1    | ×   | ×                   | ×              |

|                       |                           | Output                    | -         | 0     | 0     | 0    | 0/1 | SCK00/ SCL00 = 1    | PCLBZ0 = 0     |

|                       |                           | N-ch open<br>drain output | -         | 1     | 0     | 0    | 0/1 |                     |                |

|                       | ANI16                     | Input                     | -         | ×     | 1     | 1    | ×   | ×                   | ×              |

|                       | PCLBZ0                    | Output                    | -         | 0     | 0     | 0    | 0   | SCK00/SCL00 = 1     | ×              |

|                       | SCK00                     | Input                     | -         | ×     | 0     | 1    | ×   | ×                   | PCLBZ0 = 0     |

|                       |                           | Output                    | -         | 0/1   | 0     | 0    | 1   | ×                   | PCLBZ0 = 0     |

|                       | SCL00 <sup>Note 2</sup>   | Output                    | -         | 0/1   | 0     | 0    | 1   | ×                   | PCLBZ0 = 0     |

**Notes 1.** Provided only in 24-pin products.

2. Provided only in the R5F102 products.

## 6.2 Configuration of Timer Array Unit

Timer array unit includes the following hardware.

| Table 6-1 | Configuration | of Timer | Array Unit |

|-----------|---------------|----------|------------|

|           | Configuration |          | Anay Onit  |

| Item              | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer/counter     | Timer/counter register 0n (TCR0n)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Register          | Timer data register 0n (TDR0n)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Timer input       | TI00 to TI07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Timer output      | TO00 to TO07 pins, output controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Control registers | <registers block="" of="" setting="" unit=""> <ul> <li>Peripheral enable register 0 (PER0)</li> <li>Timer clock select register 0 (TPS0)</li> <li>Timer channel enable status register 0 (TE0)</li> <li>Timer channel start register 0 (TS0)</li> <li>Timer channel stop register 0 (TT0)</li> <li>Timer input select register 0 (TIS0)</li> <li>Timer output enable register 0 (TOE0)</li> <li>Timer output engister 0 (TO0)</li> <li>Timer output level register 0 (TOL0)</li> <li>Timer output mode register 0 (TOM0)</li> <li></li></ul> <registers channel="" each="" of=""> <ul> <li>Timer status register 0n (TSR0n)</li> <li>Noise filter enable register 1 (NFEN1)</li> </ul></registers></registers> |

|                   | <ul> <li>Port mode control register (PMCxx)<sup>Note</sup></li> <li>Port mode register (PMxx)<sup>Note</sup></li> <li>Port register (Pxx)<sup>Note</sup></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Note The Port mode control register (PMCxx), port mode registers (PMxx), and port registers (Pxx) to be set differ depending on the product. For details, see **4.5.3 Register setting examples for using the port and alternate functions**.

**Remark** n: Channel number (n = 0 to 7)

Alternate port for timer I/O of the timer array unit channels varies depending on products.

| Table 6-2. Timer I/O Pins in the Products |

|-------------------------------------------|

|-------------------------------------------|

| Timer array unit channel | 30-pin products | 20, 24-pin products |

|--------------------------|-----------------|---------------------|

| Channel 0                | TI00/TO00       | Т100/ТО00           |

| Channel 1                | TI01/TO01       | TI01/TO01           |

| Channel 2                | TI02/TO02       | TI02/TO02           |

| Channel 3                | TI03/TO03       | TI03/TO03           |

| Channel 4                | (TI04/TO04)     | ×                   |

| Channel 5                | (TI05/TO05)     | ×                   |

| Channel 6                | (TI06/TO06)     | ×                   |

| Channel 7                | (TI07/TO07)     | ×                   |

**Remarks** 1. If a pin is to be used for both timer input and timer output, it can be used only for timer input or timer output.

- **2.**  $\times$ : The channel is not available

- 3. Pins in the parentheses indicate an alternate port when the bit 0 (PIOR0) of the peripheral I/O redirection register (PIOR) is set to "1" in 30-pin products.

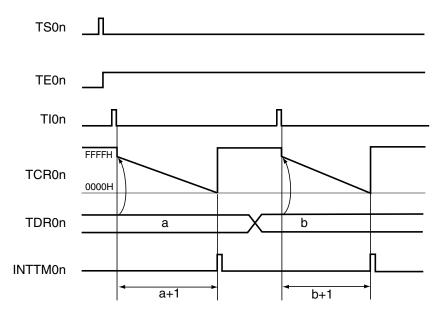

Figure 6-59. Example of Basic Timing of Operation as Delay Counter

```

Remarks 1. n: Channel number (n = 0 to 7)

```

| 2. | TS0n: | Bit n of timer channel start register 0 (TS0)         |

|----|-------|-------------------------------------------------------|

|    | TE0n: | Bit n of timer channel enable status register 0 (TE0) |

- TIOn: TIOn pin input signal

- TCR0n: Timer count register 0n (TCR0n)

- TDR0n: Timer data register 0n (TDR0n)

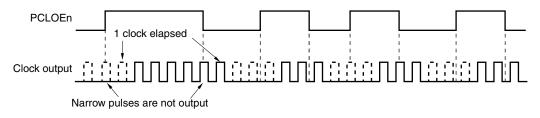

## 8.4 Operations of Clock Output/Buzzer Output Controller

One pin can be used to output a clock or buzzer sound.

The PCLBUZ0 pin outputs a clock/buzzer selected by the clock output select register 0 (CKS0).

The PCLBUZ1 pin outputs a clock/buzzer selected by the clock output select register 1 (CKS1).

#### 8.4.1 Operation as output pin

The PCLBUZn pin is output as the following procedure.

- <1> Set 0 in the bit of the port mode register (PMxx) and port register (Px) which correspond to the port which has a pin used as the PCLBUZn pin.

- <2> Select the output frequency with bits 0 to 2 (CCSn0 to CCSn2) of the clock output select register (CKSn) of the PCLBUZn pin (output in disabled).

- <3> Set bit 7 (PCLOEn) of the CKSn register to 1 to enable clock/buzzer output.

- Remarks 1. The controller used for outputting the clock starts or stops outputting the clock one clock after enabling or disabling clock output (PCLOEn bit) is switched. At this time, pulses with a narrow width are not output. Figure 8-3 shows enabling or stopping output using the PCLOEn bit and the timing of outputting the clock.

- **2.** n = 0 or 1

## 8.5 Cautions of Clock Output/Buzzer Output Controller

If STOP mode is entered within 1.5 clock cycles output from the PCLBUZn pin after the output is disabled (PCLOEn = 0), the PCLBUZn output width becomes shorter.

## CHAPTER 10 A/D CONVERTER

The number of analog input channels of the A/D converter differs depending on the product.

|                       | 20- and 24-pin                | 30-pin                         |

|-----------------------|-------------------------------|--------------------------------|

| Analog input channels | 11 ch                         | 8 ch                           |

|                       | (ANI0 to ANI3, ANI6 to ANI22) | (ANI0 to ANI3, ANI16 to ANI19) |

## 10.1 Function of A/D Converter

The A/D converter converts analog input signals into digital values, and is configured to control analog inputs, including up to 11 channels of A/D converter analog inputs (ANI0 to ANI3 and ANI16 to ANI22). 10-bit or 8-bit resolution can be selected by using the ADTYP bit of the A/D converter mode register 2 (ADM2).

The A/D converter has the following function.

#### • 10-bit/8-bit resolution A/D conversion

10-bit or 8-bit resolution A/D conversion is carried out repeatedly for one analog input channel selected from ANI0 to ANI3 and ANI16 to ANI22 (ANI0 to ANI3 and ANI16 to ANI19 for 30-pin products). Each time an A/D conversion operation ends, an interrupt request (INTAD) is generated (when in the select mode).

Various A/D conversion modes can be specified by using the mode combinations below.

| Trigger mode           | Software trigger                    | Conversion is started by software.                                                                                                                                                                                                                                                                 |

|------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Hardware trigger no-wait mode       | Conversion is started by detecting a hardware trigger.                                                                                                                                                                                                                                             |

|                        | Hardware trigger wait mode          | The power is turned on by detecting a hardware trigger while the system is off and in the conversion standby state, and conversion is then started automatically after the A/D power supply stabilization wait time passes. Select hardware trigger wait mode when using the SNOOZE mode function. |

| Channel                | Select mode                         | A/D conversion is performed on the analog input of one channel.                                                                                                                                                                                                                                    |

| selection mode         | Scan mode                           | A/D conversion is performed on the analog input of four channels in order. ANI0 to ANI3 can be selected as analog input.                                                                                                                                                                           |

| Conversion             | One-shot conversion mode            | A/D conversion is performed on the selected channel once.                                                                                                                                                                                                                                          |

| operation mode         | Sequential conversion mode          | A/D conversion is sequentially performed on the selected channels until it is stopped by software.                                                                                                                                                                                                 |

| Operation              | Normal 1 or normal 2 mode           | Conversion is done in the operation voltage range of 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V.                                                                                                                                                                                                    |

| voltage mode           | Low-voltage 1 or low-voltage 2 mode | Conversion is done in the operation voltage range of $1.8 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ .<br>Select this mode for conversion at a low voltage. Because the operation voltage is                                                                                            |

| Sapling time selection | Sampling clock cycles: 7 fAD        | low, it is internally boosted during conversion.<br>The sampling time in normal 1 or low-voltage 1 mode is seven cycles of the conversion clock (fAD). Select this mode when the output impedance of the analog input source is high and a longer sampling time is required.                       |

|                        | Sampling clock cycles: 5 fab        | The sampling time in normal 2 or low-voltage 2 mode is five cycles of the conversion clock ( $f_{AD}$ ). Select this mode when enough sampling time is ensured (for example, when the output impedance of the analog input source is low).                                                         |

#### 11.3.14 Serial standby control register 0 (SSC0)

The SSC0 register is used to control the startup of reception (the SNOOZE mode) while in the STOP mode when receiving CSI00 or UART0 serial data.

The SSC0 register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the SSC0 register can be set with an 8-bit memory manipulation instruction as SSC0L.

Reset signal generation clears the SSC0 register to 0000H.

Caution The maximum transfer rate in the SNOOZE mode is as follows.

- When using CSI00: Up to 1 Mbps

- When using UART0: 4800 bps only

#### Figure 11-20. Format of Serial Standby Control Register 0 (SSC0)

Address: F0138H, F0139H After reset: 0000H R/W Symbol 15 13 12 10 0 14 11 9 8 7 6 5 3 2 1 4 SSCm 0 0 0 0 0 0 0 0 0 0 0 SSEC SWC 0 0 0 0 0

| SSEC0                                                                                                                                                                        | Selection of whether to enable or disable the generation of communication error interrupts in the SNOOZE |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                              | mode                                                                                                     |  |  |

| 0                                                                                                                                                                            | Enable the generation of error interrupts (INTSRE0).                                                     |  |  |

| 1                                                                                                                                                                            | Stop the generation of error interrupts (INTSRE0).                                                       |  |  |

| • The SSEC0 bit can be set to 1 or 0 only when both the SWC0 and EOC01 bits are set to 1 during UART reception in the SNOOZE mode. In other cases, clear the SSEC0 bit to 0. |                                                                                                          |  |  |

| - Cottin                                                                                                                                                                     | $\sim$ Softing SSEC0. SWC0 - 1. 0 is prohibited                                                          |  |  |

• Setting SSEC0, SWC0 = 1, 0 is prohibited.

| SWC0 | Setting the SNOOZE mode                                                                                                                                                                                                     |  |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0    | Do not use the SNOOZE mode function.                                                                                                                                                                                        |  |  |  |  |  |

| 1    | Use the SNOOZE mode function.                                                                                                                                                                                               |  |  |  |  |  |

|      | <ul> <li>When there is a hardware trigger signal in the STOP mode, the STOP mode is exited, and A/D conversion is performed without operating the CPU (the SNOOZE mode).</li> </ul>                                         |  |  |  |  |  |

|      | • The SNOOZE mode function can only be specified when the high-speed on-chip oscillator clock is selected for the CPU/peripheral hardware clock (fcLk). If any other clock is selected, specifying this mode is prohibited. |  |  |  |  |  |

|      | • Even when using SNOOZE mode, be sure to set the SWC0 bit to 0 in normal operation and change it to 1 just before shifting to STOP mode.                                                                                   |  |  |  |  |  |

Also, be sure to change the SWC0 bit to 0 after returning from STOP mode to normal operation.

#### Figure 11-21. Interrupt in UART Reception Operation in SNOOZE Mode

| EOC01 Bit | SSEC0 Bit | Reception Ended Successfully | Reception Ended in an Error |

|-----------|-----------|------------------------------|-----------------------------|

| 0         | 0         | INTSR0 is generated.         | INTSR0 is generated.        |

| 0         | 1         | INTSR0 is generated.         | INTSR0 is generated.        |

| 1         | 0         | INTSR0 is generated.         | INTSRE0 is generated.       |

| 1         | 1         | INTSR0 is generated.         | No interrupt is generated.  |

<R>

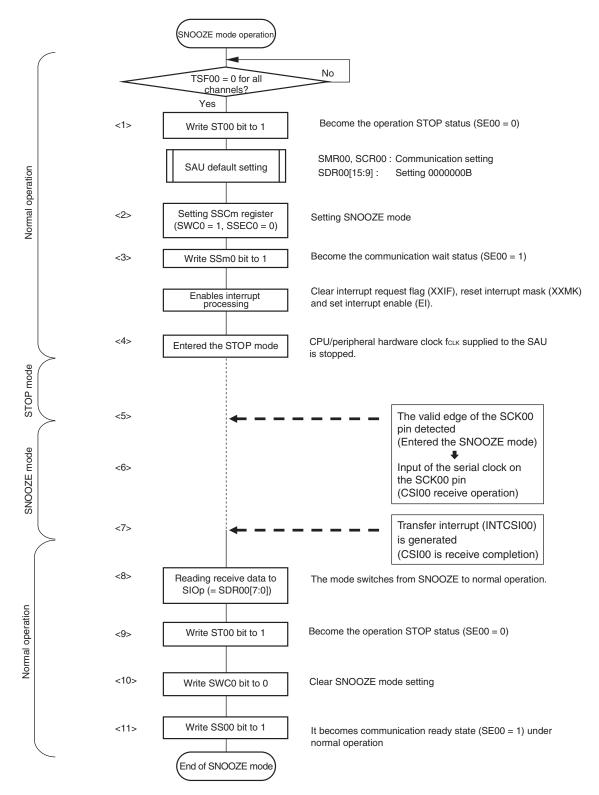

# **Remark** <1> to <11> in the figure correspond to <1> to <11> in **Figure 11-72** Flowchart of SNOOZE Mode Operation (once startup).

#### Figure 11-72. Flowchart of SNOOZE Mode Operation (once startup)

Remark <1> to <11> in the figure correspond to <1> to <11> in Figure 11-71 Timing Chart of SNOOZE Mode Operation (once startup).

RENESAS

#### 11.7.3 Data reception

Data reception is an operation to receive data to the target for transfer (slave) after transmission of an address field. After all data are received to the slave, a stop condition is generated and the bus is released.

| Simplified I <sup>2</sup> C     | IIC00                                                                                                                                                                                                                                                   | IIC01                          | IIC11                          | IIC20                          |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|--|--|

| Target channel                  | Channel 0 of SAU0                                                                                                                                                                                                                                       | Channel 1 of SAU0              | Channel 3 of SAU0              | Channel 0 of SAU1              |  |  |

| Pins used                       | SCL00, SDA00 <sup>Note 1</sup>                                                                                                                                                                                                                          | SCL01, SDA01 <sup>Note 1</sup> | SCL11, SDA11 <sup>Note 1</sup> | SCL20, SDA20 <sup>Note 1</sup> |  |  |

| Interrupt                       | INTIIC00                                                                                                                                                                                                                                                | INTIIC01                       | INTIIC11                       | INTIIC20                       |  |  |

|                                 | Transfer end interrupt of                                                                                                                                                                                                                               | only (Setting the buffer em    | pty interrupt is prohibited    | .)                             |  |  |

| Error detection flag            | ACK error detection flag                                                                                                                                                                                                                                | g (OVFmn)                      |                                |                                |  |  |

| Transfer data length            | 8 bits                                                                                                                                                                                                                                                  |                                |                                |                                |  |  |

| Transfer rate <sup>Note 2</sup> | Max. fмск/4 [Hz] (SDRmn[15:9] = 1 or more) fмск: Operation clock frequency of target<br>channel<br>However, the following condition must be satisfied in each mode of I <sup>2</sup> C.<br>• Max. 400 kHz (fast mode)<br>• Max. 100 kHz (standard mode) |                                |                                |                                |  |  |

| Data level                      | Non-inversion output (default: high level)                                                                                                                                                                                                              |                                |                                |                                |  |  |

| Parity bit                      | Parity bit No parity bit                                                                                                                                                                                                                                |                                |                                |                                |  |  |

| Stop bit                        | Appending 1 bit (ACK t                                                                                                                                                                                                                                  | ransmission)                   |                                |                                |  |  |

| Data direction                  | MSB first                                                                                                                                                                                                                                               |                                |                                |                                |  |  |

Notes 1. To perform communication via simplified I<sup>2</sup>C, set the N-ch open-drain output (Vbb tolerance) mode (POMxx = 1 (POM11, POM41 = 1 for 20- or 24- pin products, POM11, POM14, POM50 = 1 for 30-pin products)) for the port output mode registers (POMxx). For details, see 4.3 Registers Controlling Port Function and 4.5 Register Settings When Using Alternate Function.

When IIC00 and IIC20 is communicating with an external device with a different potential, set the N-ch opendrain output (V<sub>DD</sub> tolerance) mode (POMxx = 1 (POM10 = 1 for 20- or 24- pin products, POM10, POM15 = 1 for 30-pin products)) also for the clock input/output pins (SCL00, SCL20). For details, see **4.4.4 Handling different potentials (1.8 V, 2.5 V, and 3 V) by using I/O buffers**.

Use this operation within a range that satisfies the conditions above and the peripheral functions characteristics in the electrical specifications (see CHAPTER 28 ELECTRICAL SPECIFICATIONS (A, D: TA = -40 to +85°C) or CHAPTER 29 ELECTRICAL SPECIFICATIONS (G: TA = -40 to +105°C)).

**Remark** m: Unit number, n: Channel number (mn = 00, 01, 03, 10)

#### 12.3.2 IICA control register 00 (IICCTL00)

This register is used to enable/stop I<sup>2</sup>C operations, set wait timing, and set other I<sup>2</sup>C operations.

The IICCTL00 register can be set by a 1-bit or 8-bit memory manipulation instruction. However, set the SPIE0, WTIM0, and ACKE0 bits while IICE0 = 0 or during the wait period. These bits can be set at the same time when the IICE0 bit is set from "0" to "1".

Reset signal generation clears this register to 00H.

#### Figure 12-6. Format of IICA Control Register 00 (IICCTL00) (1/4)

| : F02     | 30H Af                                                                         | ter reset: 00                                                                                        | H R/W                                                                                    |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|-----------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------|----------------|---------------|-----------------|--|--|

| lool      | <7>                                                                            | <6>                                                                                                  | <5>                                                                                      | <4>                                                                                        | <3>                                                                   | <2>                                          | <1>            | <0>           |                 |  |  |

| _00       | IICE0                                                                          | LREL0                                                                                                | WREL0                                                                                    | SPIE0                                                                                      | WTIM0                                                                 | ACKE0                                        | STT0           | SPT0          |                 |  |  |

|           | IICE0                                                                          |                                                                                                      | l <sup>2</sup> C operation enable                                                        |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|           | 0                                                                              | Stop operat                                                                                          | top operation. Reset the IICA status register 0 (IICS0) Note 1. Stop internal operation. |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|           | 1                                                                              | Enable oper                                                                                          | ation.                                                                                   |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

| В         | e sure to s                                                                    | et this bit (1)                                                                                      | while the SO                                                                             | CLA0 and SI                                                                                | DAA0 lines                                                            | are at high lev                              | el.            |               |                 |  |  |

| С         | ondition fo                                                                    | r clearing (II                                                                                       | CE0 = 0)                                                                                 |                                                                                            |                                                                       | Condition for s                              | etting (IICE0  | = 1)          |                 |  |  |

|           | Cleared by<br>Reset                                                            | instruction                                                                                          |                                                                                          |                                                                                            |                                                                       | <ul> <li>Set by instruct</li> </ul>          | ction          |               |                 |  |  |

| Γ         | LRELO<br>Notes 2, 3                                                            |                                                                                                      |                                                                                          |                                                                                            | Exit fro                                                              | m communicat                                 | ions           |               |                 |  |  |

|           | 0                                                                              | Normal ope                                                                                           | ration                                                                                   |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

| сс<br>• . | onditions a<br>After a sto                                                     | The SCLA0<br>The followin<br>cleared to 0<br>• STT0 • S<br>y mode follo<br>re met.<br>p condition is | ude cases in<br>and SDAA0<br>g flags of IIC<br>PTO • MST<br>wing exit fro                | which a loca<br>lines are set<br>A control reg<br>S0 • EXCO<br>om commun<br>estart is in m | t to high im<br>gister 00 (I<br>• COI0 •<br>ications re<br>aster mode | ICCTL00) and<br>TRC0 • ACK<br>mains in effec | the IICA state | us register 0 | (IICS0) are     |  |  |

|           | An address match or extension code reception occurs after the start condition. |                                                                                                      |                                                                                          |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|           |                                                                                | r clearing (Ll                                                                                       |                                                                                          |                                                                                            |                                                                       | Condition for s                              | 0 (            | 0 = 1)        |                 |  |  |

|           | Automatic<br>Reset                                                             | Set by instruction     Set by instruction                                                            |                                                                                          |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|           | WREL0<br>Notes 2, 3                                                            | Wait cancellation                                                                                    |                                                                                          |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|           | 0                                                                              | Do not cancel wait                                                                                   |                                                                                          |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|           | 1                                                                              | Cancel wait. This setting is automatically cleared after wait is canceled.                           |                                                                                          |                                                                                            |                                                                       |                                              |                |               |                 |  |  |

|           |                                                                                |                                                                                                      |                                                                                          | ,                                                                                          |                                                                       | period at the nin<br>tate (TRC0 = 0          |                | e in the tran | smission status |  |  |

| С         | ondition fo                                                                    | r clearing (N                                                                                        | 'REL0 = 0)                                                                               |                                                                                            |                                                                       | Condition for setting (WREL0 = 1)            |                |               |                 |  |  |

|           | Automatica<br>Reset                                                            | ally cleared a                                                                                       | after executio                                                                           | n                                                                                          |                                                                       | <ul> <li>Set by instruct</li> </ul>          | ction          |               |                 |  |  |

|           |                                                                                | <b>•</b> · ·                                                                                         | ra lictad an                                                                             |                                                                                            | ``                                                                    |                                              |                |               |                 |  |  |

(Notes and Caution are listed on the next page.)

| SPT0 Note                                                                  | Stop condition trigger |                                                                             |                                                                              |  |  |  |

|----------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| 0                                                                          | Stop condition         | is not generated.                                                           |                                                                              |  |  |  |

| 1                                                                          | Stop condition         | is generated (termination of mas                                            | ter device's transfer).                                                      |  |  |  |

| Cautions co                                                                | ncerning set tir       | ning                                                                        |                                                                              |  |  |  |

| • For maste                                                                | r reception:           | Cannot be set to 1 during transfe                                           | er.                                                                          |  |  |  |

|                                                                            |                        | Can be set to 1 only in the waiting slave has been notified of final r      | ng period when the ACKE0 bit has been cleared to 0 and eception.             |  |  |  |

| • For maste                                                                | r transmission:        | A stop condition cannot be gene                                             | erated normally during the acknowledge period.                               |  |  |  |

|                                                                            |                        | Therefore, set it during the wait                                           | period that follows output of the ninth clock.                               |  |  |  |

| Cannot be                                                                  | set to 1 at the        | same time as start condition trigg                                          | jer (STT0).                                                                  |  |  |  |

| • The SPT0                                                                 | bit can be set         | to 1 only when in master mode.                                              |                                                                              |  |  |  |

| When the                                                                   | WTIM0 bit has          | been cleared to 0, if the SPT0 bit                                          | t is set to 1 during the wait period that follows output of                  |  |  |  |

| eight clock                                                                | s, note that a s       | stop condition will be generated du                                         | uring the high-level period of the ninth clock. The WTIM0                    |  |  |  |

|                                                                            | 0                      | om 0 to 1 during the wait period fo<br>it period that follows the output of | llowing the output of eight clocks, and the SPT0 bit should the ninth clock. |  |  |  |

|                                                                            | 0                      | and then setting it again before it                                         |                                                                              |  |  |  |

| Condition for clearing (SPT0 = 0)                                          |                        |                                                                             | Condition for setting (SPT0 = 1)                                             |  |  |  |

| Cleared by loss in arbitration                                             |                        |                                                                             | Set by instruction                                                           |  |  |  |

| <ul> <li>Automatically cleared after stop condition is detected</li> </ul> |                        |                                                                             |                                                                              |  |  |  |

| Cleared by                                                                 | y LREL0 = 1 (e         | xit from communications)                                                    |                                                                              |  |  |  |

|                                                                            | E0 = 0 (operatio       |                                                                             |                                                                              |  |  |  |

| Reset                                                                      |                        |                                                                             |                                                                              |  |  |  |

## Figure 12-6. Format of IICA Control Register 00 (IICCTL00) (4/4)

**Note** The value read from the STT0 bit is always 0.

**Caution** When bit 3 (TRC0) of the IICA status register 0 (IICS0) is set to 1 (transmission status), bit 5 (WREL0) of IICA control register 00 (IICCTL00) is set to 1 during the ninth clock and wait is canceled, after which the TRC0 bit is cleared (reception status) and the SDAA0 line is set to high impedance. Release the wait performed while the TRC0 bit is 1 (transmission status) by writing to the IICA shift register 0.

Remark Bit 0 (SPT0) becomes 0 when it is read after data setting.

The meanings of <1> to <7> in (1) Start condition ~ address ~ data in Figure 12-33 are explained below.

- <1> The start condition trigger is set by the master device (STT0 = 1) and a start condition (i.e. SCLA0 =1 changes SDAA0 from 1 to 0) is generated once the bus data line goes low (SDAA0). When the start condition is subsequently detected, the master device enters the master device communication status (MSTS0 = 1). The master device is ready to communicate once the bus clock line goes low (SCLA0 = 0) after the hold time has elapsed.

- <2> The master device writes the address + R (reception) to the IICA shift register 0 (IICA0) and transmits the slave address.

- <3> In the slave device if the address received matches the address (SVA0 value) of a slave device <sup>Note</sup>, that slave device sends an ACK by hardware to the master device. The ACK is detected by the master device (ACKD0 = 1) at the rising edge of the 9th clock.

- <4> The master device issues an interrupt (INTIICA0: end of address transmission) at the falling edge of the 9th clock. The slave device whose address matched the transmitted slave address sets a wait status (SCLA0 = 0) and issues an interrupt (INTIICA0: address match)<sup>Note</sup>.

- <5> The timing at which the master device sets the wait status changes to the 8th clock (WTIM0 = 0).

- <6> The slave device writes the data to transmit to the IICA0 register and releases the wait status that it set by the slave device.

- <7> The master device releases the wait status (WREL0 = 1) and starts transferring data from the slave device to the master device.

- **Note** If the transmitted address does not match the address of the slave device, the slave device does not return an ACK to the master device (NACK: SDAA0 = 1). The slave device also does not issue the INTIICA0 interrupt (address match) and does not set a wait status. The master device, however, issues the INTIICA0 interrupt (end of address transmission) regardless of whether it receives an ACK or NACK.

- **Remark** <1> to <19> in Figure 12-33 show descriptions the entire procedure for communicating data using the I<sup>2</sup>C bus.

Figure 12-33 (1) Start condition  $\sim$  address  $\sim$  data shows the processing from <1> to <7>, Figure 12-33 (2) Address  $\sim$  data  $\sim$  data shows the processing from <3> to <12>, and Figure 12-33 (3) Data  $\sim$  data  $\sim$  stop condition shows the processing from <8> to <19>.

## 14.2 Configuration of DMA Controller

The DMA controller includes the following hardware.

| Item              | Configuration                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| Address registers | <ul> <li>DMA SFR address registers 0, 1 (DSA0, DSA1)</li> <li>DMA RAM address registers 0, 1 (DRA0, DRA1)</li> </ul>       |

| Count register    | DMA byte count registers 0, 1 (DBC0, DBC1)                                                                                 |

| Control registers | <ul> <li>DMA mode control registers 0, 1 (DMC0, DMC1)</li> <li>DMA operation control register 0, 1 (DRC0, DRC1)</li> </ul> |

#### 14.2.1 DMA SFR address register n (DSAn)

This is an 8-bit register that is used to set an SFR address that is the transfer source or destination of DMA channel n. Set the lower 8 bits of the SFR addresses FFF00H to FFFFFH.

This register is not automatically incremented but fixed to a specific value.

In the 16-bit transfer mode, the least significant bit is ignored and is treated as an even address.

The DSAn register can be read or written in 8-bit units. However, it cannot be written during DMA transfer. Reset signal generation clears this register to 00H.

#### Figure 14-1. Format of DMA SFR Address Register n (DSAn)

Address: FFFB0H (DSA0), FFFB1H (DSA1) After reset: 00H R/W

|      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

| DSAn |   |   |   |   |   |   |   |   |

Remark n: DMA channel number (n = 0, 1)

## 16.2 Configuration of Key Interrupt

The key interrupt includes the following hardware.

| Item             | Configuration                                  |

|------------------|------------------------------------------------|

| Control register | Key return control register (KRCTL)            |

|                  | Key return mode control registers (KRM0, KRM1) |

|                  | Key return flag register (KRF)                 |

|                  | Port mode registers 0, 4, 6 (PM0, PM4, PM6)    |

## Table 16-2. Configuration of Key Interrupt

## 16.3 Register Controlling Key Interrupt

The key interrupt function is controlled by the following registers:

- Key return control register (KRCTL)

- Key return mode control registers (KRM0, KRM1)

- Key return flag register (KRF)

- Port mode registers 0, 4, 6 (PM0, PM4, PM6)

#### 16.3.1 Key return control register (KRCTL)

This register controls the usage of the key interrupt flags (KRF0 to KRF5) and sets the detection edge. The KRCTL register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 16-2. Format of Key Return Control Register (KRCTL)

Address: FFF34H After reset: 00H R/W

| Symbol | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|------|---|---|---|---|---|---|------|

| KRCTL  | KRMD | 0 | 0 | 0 | 0 | 0 | 0 | KREG |

| KRMD | Usage of Key Interrupt Flags (KRF0 to KRF5) |

|------|---------------------------------------------|

| 0    | Does not use key interrupt flags            |

| 1    | Uses key interrupt flags                    |

| KRRG | Selection of Detection Edge (KR0 to KR9) |

|------|------------------------------------------|

| 0    | Falling edge                             |

| 1    | Rising edge                              |

| KRMD | KREG | Interrupt Function                                                      |

|------|------|-------------------------------------------------------------------------|

| 0    | 0    | Generates a key interrupt (INTKR) when detecting a falling edge.        |

|      |      | (Identify the channel by checking the port level).                      |

| 0    | 1    | Generates a key interrupt (INTKR) when detecting a rising edge.         |

|      |      | (Identify the channel by checking the port level).                      |

| 1    | 0    | Generates a key interrupt (INTKR) when detecting a falling edge.        |

|      |      | (Identify the channel by using the key interrupt flags (KRF0 to KRF5)). |

| 1    | 1    | Generates a key interrupt (INTKR) when detecting a rising edge.         |

|      |      | (Identify the channel by using the key interrupt flags (KRF0 to KRF5)). |

#### 24.4.3 Selecting communication mode

Communication modes of the RL78 microcontroller are as follows.

| Communication                                                                                         |      | Pins Used                                           |           |               |                     |

|-------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------|-----------|---------------|---------------------|

| Mode                                                                                                  | Port | Speed Note 2                                        | Frequency | Multiply Rate |                     |

| 1-line UART<br>(when flash<br>memory<br>programmer is<br>used, or when<br>external device<br>is used) | UART | 115200 bps,<br>250000 bps,<br>500000 bps,<br>1 Mbps | _         | _             | TOOLO               |

| Dedicated UART<br>(when external<br>device is used)                                                   | UART | 115200 bps,<br>250000 bps,<br>500000 bps,<br>1 Mbps | _         | _             | TOOLTxD,<br>TOOLRxD |

Notes 1. Selection items for standard settings on GUI of the flash memory programmer.

2. Because factors other than the baud rate error, such as the signal waveform slew, also affect UART communication, thoroughly evaluate the slew as well as the baud rate error.

#### 24.4.4 Communication commands

The RL78 microcontroller executes serial programming through the commands listed in Table 24-7.

The signals sent from the dedicated flash memory programmer or external device to the RL78 microcontroller are called commands, and programming functions corresponding to the commands are executed. For details, refer to the **RL78 Microcontrollers (RL78 Protocol A) Programmer Edition Application Note (R01AN0815)**.

| Classification      | Command Name      | Function                                                                                                              |  |  |  |

|---------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Verify              | Verify            | Compares the contents of a specified area of the flash memory with data transmitted from the programmer.              |  |  |  |

| Erase               | Block Erase       | Erases a specified area in the flash memory.                                                                          |  |  |  |

| Blank check         | Block Blank Check | Checks if a specified block in the flash memory has been correctly erased.                                            |  |  |  |

| Write               | Programming       | Writes data to a specified area in the flash memory. Note                                                             |  |  |  |

| Getting information | Silicon Signature | Gets the RL78 microcontroller information (such as the part number and flash memory configuration, firmware version). |  |  |  |

|                     | Checksum          | Gets the checksum data for a specified area.                                                                          |  |  |  |

| Security            | Security Set      | Sets security information.                                                                                            |  |  |  |

|                     | Security Get      | Gets security information.                                                                                            |  |  |  |

|                     | Security Release  | Releases the write prohibition setting.                                                                               |  |  |  |

| Others              | Reset             | Used to detect synchronization status of communication.                                                               |  |  |  |

|                     | Baud Rate Set     | Sets baud rate when UART communication mode is selected.                                                              |  |  |  |

| Table 24-7. | Flash Memory | Control | Commands |

|-------------|--------------|---------|----------|

|-------------|--------------|---------|----------|

**Note** Confirm that no data has been written to the write area. Because data cannot be erased after block erase is prohibited, do not write data if the data has not been erased.

| Instruction Mnemoni<br>Group |      | Operands          | Bytes | Bytes Clo |        | Clocks             |   | Flag | I  |  |

|------------------------------|------|-------------------|-------|-----------|--------|--------------------|---|------|----|--|

|                              |      |                   |       | Note 1    | Note 2 |                    | z | AC   | CY |  |

| 8-bit                        | CMP  | A, #byte          | 2     | 1         | -      | A – byte           | × | ×    | ×  |  |

| operation                    |      | !addr16, #byte    | 4     | 1         | 4      | (addr16) – byte    | × | ×    | ×  |  |

|                              |      | ES:laddr16, #byte | 5     | 2         | 5      | (ES:addr16) – byte | × | ×    | ×  |  |