Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 14                                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 512 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | 20-LSSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10267dsp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Code flash | Data flash | RAM    | 20 pins         | 24 pins                    | 30 pins  |

|------------|------------|--------|-----------------|----------------------------|----------|

| 16 KB      | 2 KB       | 2 KB   | _               | _                          | R5F102AA |

|            | _          |        |                 |                            | R5F103AA |

|            | 2 KB       | 1.5 KB | R5F1026A Note 1 | R5F1027A <sup>Note 1</sup> | _        |

|            |            |        | R5F1036A Note 1 | R5F1037A Note 1            | _        |

| 12 KB      | 2KB        | 1 KB   | R5F10269 Note 1 | R5F10279 Note 1            | R5F102A9 |

|            |            |        | R5F10369 Note 1 | R5F10379 Note 1            | R5F103A9 |

| 8 KB       | 2 KB       | 768 B  | R5F10268 Note 1 | R5F10278 Note 1            | R5F102A8 |

|            | —          |        | R5F10368 Note 1 | R5F10378 Note 1            | R5F103A8 |

| 4 KB       | 2KB        | 512 B  | R5F10267        | R5F10277                   | R5F102A7 |

|            | _          |        | R5F10367        | R5F10377                   | R5F103A7 |

| 2 KB       | 2 KB       | 256 B  | R5F10266 Note 2 |                            |          |

|            |            |        | R5F10366 Note 2 |                            |          |

O ROM, RAM capacities

Notes 1. This is 640 bytes when the self-programming function or data flash function is used. (For details, see CHAPTER 3 CPU ARCHITECTURE.)

2. The self-programming function cannot be used for R5F10266 and R5F10366.

Caution When the flash memory is rewritten via a user program, the code flash area and RAM area are used because each library is used. When using the library, refer to RL78 Family Flash Self Programming Library Type01 User's Manual and RL78 Family Data Flash Library Type04 User's Manual.

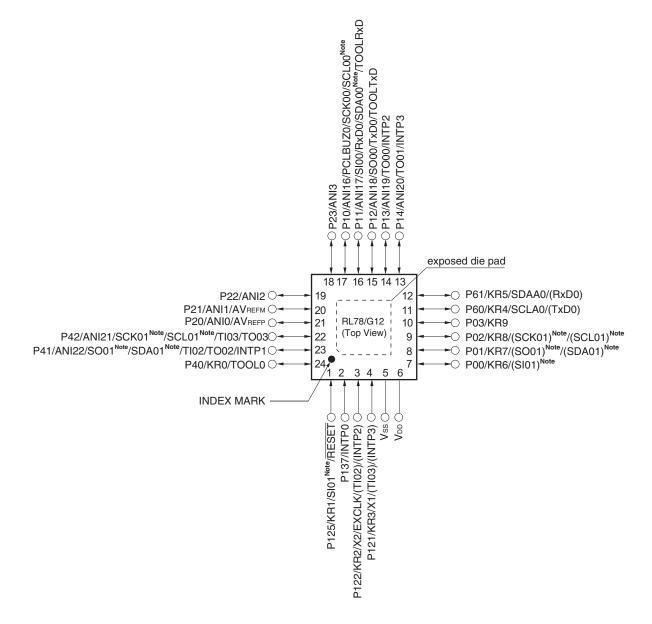

## 1.4.2 24-pin products

<R> • 24-pin plastic HWQFN (4 × 4 mm, 0.5 mm pitch)

Note Provided only in the R5F102 products.

Remarks 1. For pin identification, see 1.5 Pin Identification.

- 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR).

- 3. It is recommended to connect an exposed die pad to Vss.

| Address | Special Function Register (SFR) Name     | Syr      | nbol | R/W | Manip        | ulable Bit I | Range        | After Reset |

|---------|------------------------------------------|----------|------|-----|--------------|--------------|--------------|-------------|

|         |                                          |          |      |     | 1-bit        | 8-bit        | 16-bit       |             |

| F01B0H  | Timer channel enable status register 0   | TE0L     | TE0  | R   | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       |

| F01B1H  |                                          | _        |      |     | _            | _            |              |             |

| F01B2H  | Timer channel start register 0           | TS0L     | TS0  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       |

| F01B3H  |                                          | -        |      |     | _            | -            |              |             |

| F01B4H  | Timer channel stop register 0            | TTOL     | TT0  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       |

| F01B5H  |                                          | -        |      |     | _            | -            |              |             |

| F01B6H  | Timer clock select register 0            | TPS0     |      | R/W | _            | -            | $\checkmark$ | 0000H       |

| F01B7H  |                                          |          |      |     |              |              |              |             |

| F01B8H  | Timer output register 0                  | TO0L     | TO0  | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       |

| F01B9H  |                                          | -        | ]    |     | -            | _            |              |             |

| F01BAH  | Timer output enable register 0           | TOE0L    | TOE0 | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       |

| F01BBH  |                                          | -        |      |     | -            | _            |              |             |

| F01BCH  | Timer output level register 0            | TOLOL    | TOL0 | R/W | _            | $\checkmark$ | $\checkmark$ | 0000H       |

| F01BDH  |                                          | -        |      |     | -            | -            |              |             |

| F01BEH  | Timer output mode register 0             | TOM0L    | TOM0 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       |

| F01BFH  |                                          | -        | ]    |     | -            | _            |              |             |

| F0230H  | IICA control register 00                 | IICCTL00 | )    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0231H  | IICA control register 01                 | IICCTL01 |      | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0232H  | IICA low-level width setting register 0  | IICWL0   |      | R/W | _            | $\checkmark$ | -            | FFH         |

| F0233H  | IICA high-level width setting register 0 | IICWH0   |      | R/W | _            | $\checkmark$ | -            | FFH         |

| F0234H  | Slave address register 0                 | SVA0     |      | R/W | _            | $\checkmark$ | -            | 00H         |

| F02FAH  | CRC data register                        | CRCD     |      | R/W | _            | _            | $\checkmark$ | 0000H       |

Remark For SFRs in the SFR area, see Table 3-6 SFR List.

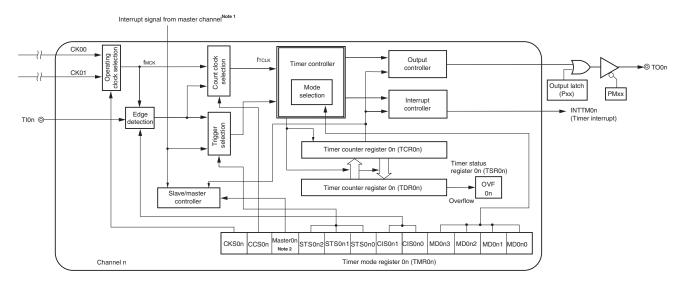

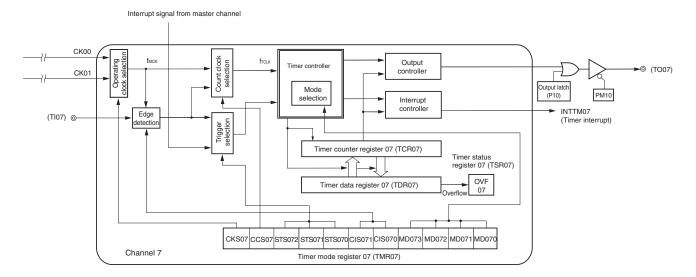

# Figure 6-3. Internal Block Diagram of Channel of Timer Array Unit

# (a) Channel 0, 2, 4, 6

**Notes 1.** Channels 2, 4, and 6 only **2.** n = 2, 4, 6 only

-

- **Remarks 1.** n = 0, 2, 4, or 6

- 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR).

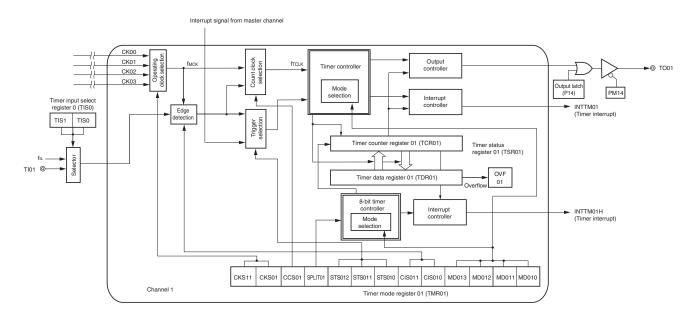

#### (b) Channel 1 for 20-pin and 24-pin product

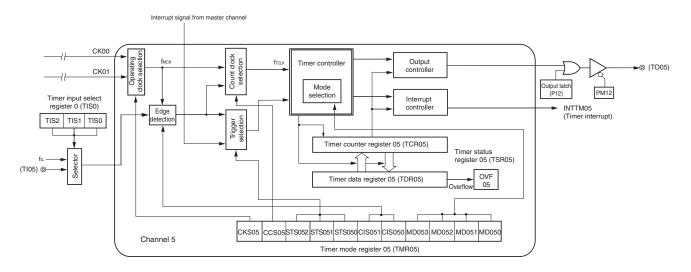

## (e) Channel 5 for 30-Pin product

(f) Channel 7 for 30-Pin product

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR).

<R>

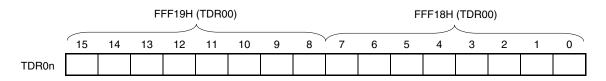

#### 6.2.2 Timer data register 0n (TDR0n)

This is a 16-bit register from which a capture function and a compare function can be selected.

The capture or compare function can be switched by selecting an operation mode by using the MD0n3 to MD0n0 bits of timer mode register 0n (TMR0n).

The value of the TDR0n register can be changed at any time.

This register can be read or written in 16-bit units.

In addition, for the TDR01, TDR03 registers, while in the 8-bit timer mode (when the SPLIT01, SPLIT03 bits of timer mode register m1, m3 (TMR01, TMR03) is 1), it is possible to read and write the data in 8-bit units, with TDR01H, TDR03H used as the higher 8 bits, and TDR01L, TDR03L used as the lower 8 bits.

Reset signal generation clears this register to 0000H.

#### Figure 6-5. Format of Timer Data Register 0n (TDR0n) (n = 0, 2, 4 to 7)

Address: FFF18H, FFF19H (TDR00), FFF64H, FFF65H (TDR02), After reset: 0000H R/W FFF68H, FFF69H (TDR04) to FFF6EH, FFF6FH (TDR07)

#### Figure 6-6. Format of Timer Data Register 01, 03 (TDR01, TDR03)

Address: FFF1AH, FFF1BH (TDR01), FFF66H, FFF67H (TDR03) After reset: 0000H R/W

|       | FFF1BH (TDR01)          |  |  |  |  |  |  |  |  |  | FI | F1AH | (TDR0 | 1) |   |   |

|-------|-------------------------|--|--|--|--|--|--|--|--|--|----|------|-------|----|---|---|

|       | 15 14 13 12 11 10 9 8 7 |  |  |  |  |  |  |  |  |  | 5  | 4    | 3     | 2  | 1 | 0 |

| TDR0n |                         |  |  |  |  |  |  |  |  |  |    |      |       |    |   |   |

#### (i) When timer data register 0n (TDR0n) is used as compare register

Counting down is started from the value set to the TDR0n register. When the count value reaches 0000H, an interrupt signal (INTTM0n) is generated. The TDR0n register holds its value until it is rewritten.

#### (ii) When timer data register 0n (TDR0n) is used as capture register

The count value of timer/counter register 0n (TCR0n) is captured to the TDR0n register when the capture trigger is input.

A valid edge of the TIOn pin can be selected as the capture trigger. This selection is made by timer mode register 0n (TMR0n).

**Remark** n: Channel number (n = 0 to 7)

**Caution** The TDR0n register does not perform a capture operation even if a capture trigger is input, when it is set to the compare function.

Notes 1. Bit 11 is a read-only bit and fixed to 0. Writing to this bit is ignored.

- 2. In one-count mode, interrupt output (INTTM0n) when starting a count operation and TO0n output are not controlled.

- If the start trigger (TS0n = 1) is issued during operation, the counter is initialized, and recounting is started (interrupt request is not generated).

**Remark** n: Channel number (n = 0 to 7)

#### 6.3.4 Timer status register 0n (TSR0n)

The TSR0n register indicates the overflow status of the counter of channel n.

The TSR0n register is valid only in the capture mode (MD0n3 to MD0n1 = 010B) and capture & one-count mode (MD0n3 to MD0n1 = 110B). It will not be set in any other mode. See Table 6-4 for the operation of the OVF bit in each operation mode and set/clear conditions.

The TSR0n register can be read by a 16-bit memory manipulation instruction.

The lower 8 bits of the TSR0n register can be set with an 8-bit memory manipulation instruction with TSR0nL. Reset signal generation clears this register to 0000H.

#### Figure 6-10. Format of Timer Status Register 0n (TSR0n)

Address: F01A0H, F01A1H (TSR00) to F01AEH, F01AFH (TSR07) After reset: 0000H R

| Symbol | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----|

| TSR0n  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | OVF |

| OVF  | Counter overflow status of channel n                                                                  |  |  |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 0    | Overflow does not occur.                                                                              |  |  |  |  |  |  |  |  |  |

| 1    | Overflow occurs.                                                                                      |  |  |  |  |  |  |  |  |  |

| When | When $OVF = 1$ , this flag is cleared ( $OVF = 0$ ) when the next value is captured without overflow. |  |  |  |  |  |  |  |  |  |

**Remark** n: Channel number (n = 0 to 7)

#### Table 6-5. OVF Bit Operation and Set/Clear Conditions in Each Operation Mode

| Timer operation mode     | OVF bit | Set/clear conditions                         |  |  |  |  |  |  |

|--------------------------|---------|----------------------------------------------|--|--|--|--|--|--|

| Capture mode             | clear   | When no overflow has occurred upon capturing |  |  |  |  |  |  |

| Capture & one-count mode | set     | When an overflow has occurred upon capturing |  |  |  |  |  |  |

| Interval timer mode      | clear   |                                              |  |  |  |  |  |  |

| Event counter mode       |         | - (Use prohibited)                           |  |  |  |  |  |  |

| One-count mode           | set     |                                              |  |  |  |  |  |  |

**Remark** The OVF bit does not change immediately after the counter has overflowed, but changes upon the subsequent capture.

## 11.3.13 Serial output level register m (SOLm)

The SOLm register is used to set inversion of the data output level of each channel.

This register can be set only in the UART mode. Be sure to set 0 to corresponding bit in the CSI mode and simplified I<sup>2</sup>C mode.

Inverting channel n by using this register is reflected on pin output only when serial output is enabled (SOEmn = 1). When serial output is disabled (SOEmn = 0), the value of the SOmn bit is output as is.

Rewriting the SOLm register is prohibited during operation (SEmn = 1).

The SOLm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the SOLm register can be set with an 8-bit memory manipulation instruction as SOLmL.

Reset signal generation clears the SOLm register to 0000H.

## Figure 11-18. Format of Serial Output Level Register m (SOLm)

| Address: F01                                          | 34H, F0 | 0135H ( | SOL0) | After | reset: C | 000H | R/W |   |   |   |   |   |   |                           |   |           |

|-------------------------------------------------------|---------|---------|-------|-------|----------|------|-----|---|---|---|---|---|---|---------------------------|---|-----------|

| Symbol                                                | 15      | 14      | 13    | 12    | 11       | 10   | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2                         | 1 | 0         |

| SOL0                                                  | 0       | 0       | 0     | 0     | 0        | 0    | 0   | 0 | 0 | 0 | 0 | 0 | 0 | SOL<br>02 <sup>Note</sup> | 0 | SOL<br>00 |

| Address: F0174H, F0175H (SOL1) After reset: 0000H R/W |         |         |       |       |          |      |     |   |   |   |   |   |   |                           |   |           |

| Symbol                                                | 15      | 14      | 13    | 12    | 11       | 10   | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2                         | 1 | 0         |

| SOL1 <sup>Note</sup>                                  | 0       | 0       | 0     | 0     | 0        | 0    | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0                         | 0 | SOL<br>10 |

|                                                       |         |         |       |       |          |      |     |   |   |   |   |   |   |                           |   |           |

| SOLmn | Selects inversion of the level of the transmit data of channel n in UART mode |

|-------|-------------------------------------------------------------------------------|

| 0     | Communication data is output as is.                                           |

| 1     | Communication data is inverted and output.                                    |

**Note** 30-pin product only.

**Caution** Be sure to clear bits 15 to 1 of the SOL0 register for 20- or 24-pin products, bits 15 to 3, and 1 of the SOL0 register for 30-pin products, and bits 15 to 1 of the SOL1 register to "0".

(Remark is listed on the next page.)

Figure 11-19 shows examples in which the level of transmit data is reversed during UART transmission.

# 11.5.3 Master transmission/reception

Master transmission/reception is that the RL78 microcontroller outputs a transfer clock and transmits/receives data to/from other device.

| 3-Wire Serial I/O             | CSI00                                                                                                                     | CSI01                        | CSI11                          | CSI20             |  |  |  |  |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|-------------------|--|--|--|--|--|--|--|--|

| Target channel                | Channel 0 of SAU0                                                                                                         | Channel 1 of SAU0            | Channel 3 of SAU0              | Channel 0 of SAU1 |  |  |  |  |  |  |  |  |

| Pins used                     | SCK00, SI00, SO00                                                                                                         | SCK01, SI01, SO01            | SCK11, SI11, SO11              | SCK20, SI20, SO20 |  |  |  |  |  |  |  |  |

| Interrupt                     | INTCSI00                                                                                                                  | INTCSI01                     | INTCSI11                       | INTCSI20          |  |  |  |  |  |  |  |  |

|                               | Transfer end interrupt (in single-transfer mode) or buffer empty interrupt (in continuous transfer mode) can be selected. |                              |                                |                   |  |  |  |  |  |  |  |  |

| Error detection flag          | Overrun error detection flag (OVFmn) only                                                                                 |                              |                                |                   |  |  |  |  |  |  |  |  |

| Transfer data length          | 7 or 8 bits                                                                                                               | 7 or 8 bits                  |                                |                   |  |  |  |  |  |  |  |  |

| Transfer rate <sup>Note</sup> | Max. fclк/2 [Hz] (CSI00                                                                                                   | ) only), fcьк/4 [Hz]         |                                |                   |  |  |  |  |  |  |  |  |

|                               | Min. fcLk/( $2 \times 2^{15} \times 128$                                                                                  | ) [Hz] fcьк: System clo      | ck frequency                   |                   |  |  |  |  |  |  |  |  |

| Data phase                    | Selectable by the DAP                                                                                                     | mn bit of the SCRmn reg      | ister                          |                   |  |  |  |  |  |  |  |  |

|                               | • DAPmn = 0: Data I/C                                                                                                     | ) starts at the start of the | operation of the serial cloo   | ck.               |  |  |  |  |  |  |  |  |

|                               | • DAPmn = 1: Data I/C                                                                                                     | ) starts half a clock before | e the start of the serial cloo | ck operation.     |  |  |  |  |  |  |  |  |

| Clock phase                   | Selectable by the CKP                                                                                                     | mn bit of the SCRmn reg      | ister                          |                   |  |  |  |  |  |  |  |  |

|                               | • CKPmn = 0: Non-inv                                                                                                      | • CKPmn = 0: Non-inversion   |                                |                   |  |  |  |  |  |  |  |  |

|                               | • CKPmn = 1: Inverted                                                                                                     |                              |                                |                   |  |  |  |  |  |  |  |  |

| Data direction                | MSB or LSB first                                                                                                          |                              |                                |                   |  |  |  |  |  |  |  |  |

Note Use this operation within a range that satisfies the conditions above and the peripheral functions characteristics in the electrical specifications (see CHAPTER 28 ELECTRICAL SPECIFICATIONS (A, D: TA = -40 to +85°C) or CHAPTER 29 ELECTRICAL SPECIFICATIONS (G: TA = -40 to +105°C)).

**Remarks** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), mn = 00 to 03, 10 to 13

#### 12.3.2 IICA control register 00 (IICCTL00)

This register is used to enable/stop I<sup>2</sup>C operations, set wait timing, and set other I<sup>2</sup>C operations.

The IICCTL00 register can be set by a 1-bit or 8-bit memory manipulation instruction. However, set the SPIE0, WTIM0, and ACKE0 bits while IICE0 = 0 or during the wait period. These bits can be set at the same time when the IICE0 bit is set from "0" to "1".

Reset signal generation clears this register to 00H.

## Figure 12-6. Format of IICA Control Register 00 (IICCTL00) (1/4)

| F02 | 230H Af                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | fter reset: 00   | H R/W          |               |             |                                      |               |                |                 |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|---------------|-------------|--------------------------------------|---------------|----------------|-----------------|--|--|--|--|--|

|     | <7>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <6>              | <5>            | <4>           | <3>         | <2>                                  | <1>           | <0>            |                 |  |  |  |  |  |

| 00  | IICE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LREL0            | WREL0          | SPIE0         | WTIM0       | ACKE0                                | STT0          | SPT0           |                 |  |  |  |  |  |

| Γ   | IICE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                |               | l²C c       | peration enabl                       | e             |                |                 |  |  |  |  |  |

| F   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Stop operat      | ion. Reset tl  | ne IICA statu |             | 0 (IICS0) <sup>Note 1</sup> .        |               | operation.     |                 |  |  |  |  |  |

|     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Enable ope       | ration.        |               |             |                                      |               |                |                 |  |  |  |  |  |

| E   | Be sure to s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | set this bit (1) | while the So   | CLA0 and SI   | DAA0 lines  | are at high lev                      | el.           |                |                 |  |  |  |  |  |

| C   | Condition fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | or clearing (II  | CE0 = 0)       |               |             | Condition for s                      | etting (IICE0 | = 1)           |                 |  |  |  |  |  |

|     | Cleared by<br>Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | y instruction    |                |               |             | Set by instru                        | ction         |                |                 |  |  |  |  |  |

|     | LRELO<br>Notes 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                |               | Exit fro    | m communicat                         | ions          |                |                 |  |  |  |  |  |

|     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Normal ope       | rmal operation |               |             |                                      |               |                |                 |  |  |  |  |  |

| •   | to 0 after being executed.<br>Its uses include cases in which a locally irrelevant extension code has been received.<br>The SCLA0 and SDAA0 lines are set to high impedance.<br>The following flags of IICA control register 00 (IICCTL00) and the IICA status register 0 (IICS0) are<br>cleared to 0.<br>• STT0 • SPT0 • MSTS0 • EXC0 • COI0 • TRC0 • ACKD0 • STD0<br>The standby mode following exit from communications remains in effect until the following communications entry<br>conditions are met.<br>• After a stop condition is detected, restart is in master mode. |                  |                |               |             |                                      |               |                |                 |  |  |  |  |  |

| -   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | or clearing (L   |                |               |             | er the start cone<br>Condition for s |               | 0 = 1)         |                 |  |  |  |  |  |

| •   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ally cleared a   |                | on            |             | Set by instru                        | 0 (           | ,              |                 |  |  |  |  |  |

|     | WRELO<br>Notes 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                |               | Wa          | ait cancellation                     |               |                |                 |  |  |  |  |  |

|     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Do not cano      | el wait        |               |             |                                      |               |                |                 |  |  |  |  |  |

|     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cancel wait      | . This setting | g is automati | cally clear | ed after wait is                     | canceled.     |                |                 |  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                | , ,           |             | period at the nin<br>tate (TRC0 = 0  |               | se in the tran | smission status |  |  |  |  |  |

| C   | Condition fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | or clearing (W   | /REL0 = 0)     |               |             | Condition for setting (WREL0 = 1)    |               |                |                 |  |  |  |  |  |

|     | <ul><li>Automatic</li><li>Reset</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ally cleared a   | after executio | n             |             | <ul> <li>Set by instruct</li> </ul>  | ction         |                |                 |  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | ra liatad an   |               | ``          |                                      |               |                |                 |  |  |  |  |  |

(Notes and Caution are listed on the next page.)

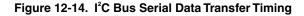

# 12.5 I<sup>2</sup>C Bus Definitions and Control Methods

The following section describes the I<sup>2</sup>C bus's serial data communication format and the signals used by the I<sup>2</sup>C bus. Figure 12-14 shows the transfer timing for the "start condition", "address", "data", and "stop condition" output via the I<sup>2</sup>C bus's serial data bus.

The master device generates the start condition, slave address, and stop condition.

The acknowledge (ACK) can be generated by either the master or slave device (normally, it is output by the device that receives 8-bit data).

The serial clock (SCLA0) is continuously output by the master device. However, in the slave device, the SCLA0 pin low level period can be extended and a wait can be inserted.

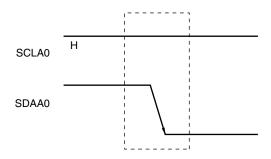

#### 12.5.1 Start conditions

A start condition is met when the SCLA0 pin is at high level and the SDAA0 pin changes from high level to low level. The start conditions for the SCLA0 pin and SDAA0 pin are signals that the master device generates to the slave device when starting a serial transfer. When the device is used as a slave, start conditions can be detected.

A start condition is output when bit 1 (STT0) of IICA control register 00 (IICCTL00) is set (1) after a stop condition has been detected (SPD0: Bit 0 of the IICA status register 0 (IICS0) = 1). When a start condition is detected, bit 1 (STD0) of the IICS0 register is set (1).

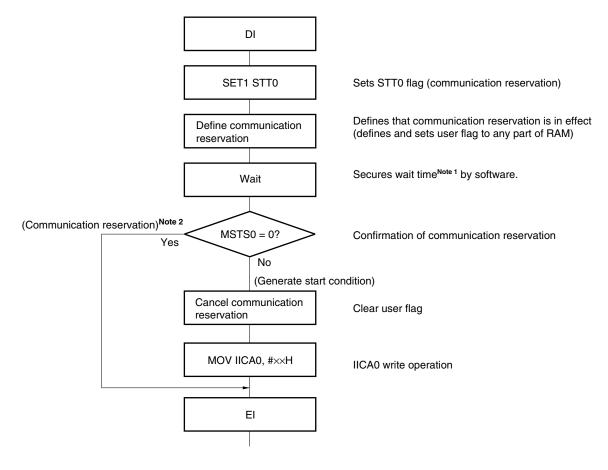

Figure 12-27. Communication Reservation Protocol

<R> Notes 1. The wait time is calculated as follows.

(IICWL0 setting value + IICWH0 setting value + 4) / fmck + tF  $\times\,2$

**2.** The communication reservation operation executes a write to the IICA shift register 0 (IICA0) when a stop condition interrupt request occurs.

| Remark | STT0:  | Bit 1 of IICA control register 00 (IICCTL00) |

|--------|--------|----------------------------------------------|

|        | MSTSC  | ): Bit 7 of IICA status register 0 (IICS0)   |

|        | IICA0: | IICA shift register 0                        |

|        | IICWLC | : IICA low-level width setting register 0    |

|        | IICWH  | D: IICA high-level width setting register 0  |

|        | t⊧:    | SDAA0 and SCLA0 signal falling times         |

|        | fмск:  | IICA operation clock frequency               |

|        |        |                                              |

<R>

## (h) When arbitration loss occurs due to low-level data when attempting to generate a stop condition

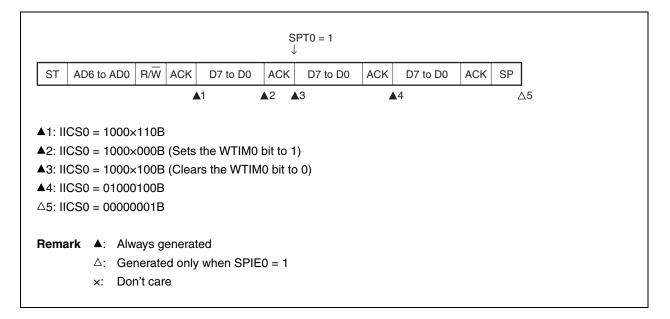

## (i) When WTIM0 = 0

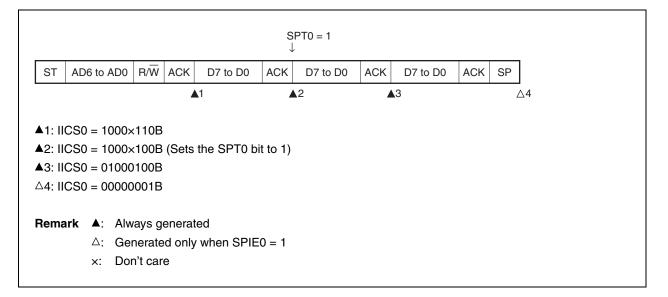

(ii) When WTIM0 = 1

# CHAPTER 14 DMA CONTROLLER

The R5F102 products of the RL78/G12 have an internal DMA (Direct Memory Access) controller.

Data can be automatically transferred between the peripheral hardware supporting DMA, SFRs, and internal RAM without via CPU.

As a result, the normal internal operation of the CPU and data transfer can be executed in parallel with transfer between the SFR and internal RAM, and therefore, a large capacity of data can be processed. In addition, real-time control using communication, timer, and A/D can also be realized.

## 14.1 Functions of DMA Controller

- O Number of DMA channels: 2 channels (R5F102 products)

- O Transfer unit: 8 or 16 bits

- O Maximum transfer unit: 1024 times

- O Transfer type: 2-cycle transfer (One transfer is processed in 2 clocks and the CPU stops during that processing.)

- O Transfer mode: Single-transfer mode

- O Transfer request: Selectable from the following peripheral hardware interrupts

- A/D converter

- Serial interface (CSI00, CSI01, CSI11, CSI20, UART0 to UART2)

- Timer (channel 0, 1, 2, 3)

- O Transfer target: Between SFR and internal RAM

Here are examples of functions using DMA.

- Successive transfer of serial interface

- Consecutive capturing of A/D conversion results

- Capturing A/D conversion result at fixed interval

- Capturing port value at fixed interval

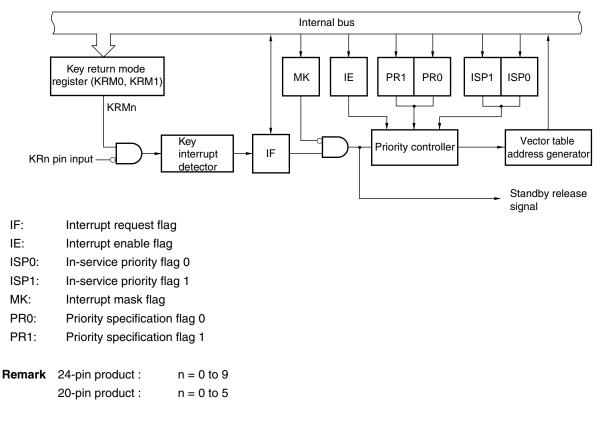

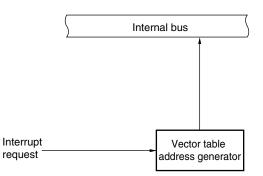

# Figure 15-1. Basic Configuration of Interrupt Function (2/2)

# (c) External maskable interrupt (INTKR)

#### (d) Software interrupt

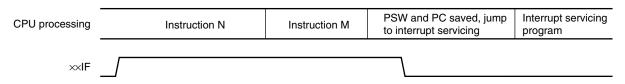

# 15.4.4 Interrupt request hold

There are instructions where, even if an interrupt request is issued while the instructions are being executed, interrupt request acknowledgment is held pending until the end of execution of the next instruction. These instructions (interrupt request hold instructions) are listed below.

- MOV PSW, #byte

- MOV PSW, A

- MOV1 PSW. bit, CY

- SET1 PSW. bit

- CLR1 PSW. bit

- RETB

- RETI

- POP PSW

- BTCLR PSW. bit, \$addr20

- El

- DI

- SKC

- SKNC

- SKZ

- SKNZ

- SKH

- SKNH

- Write instructions for the IF0L, IF0H, IF1L, IF1H, IF2L, IF2H, MK0L, MK0H, MK1L, MK1H, MK2L, MK2H, PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, and PR12H registers

Figure 15-14 shows the timing at which interrupt requests are held pending.

# Figure 15-14. Interrupt Request Hold

Remarks 1. Instruction N: Interrupt request hold instruction

2. Instruction M: Instruction other than interrupt request hold instruction

#### 16.3.2 Key return mode control registers (KRM0, KRM1)

These registers set the key interrupt mode.

The KRM0 and KRM1 registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

## Figure 16-3. Format of Key Return Control Registers (KRM0, KRM1)

## 20-pin products

Address: FFF37H After reset: 00H R/W

| Symbol | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|---|---|-------|-------|-------|-------|-------|-------|

| KRM0   | 0 | 0 | KRM05 | KRM04 | KRM03 | KRM02 | KRM01 | KRM00 |

## 24-pin products

Address: FFF37H After reset: 00H R/W

| Symbol | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| KRM0   | KRM07 | KRM06 | KRM05 | KRM04 | KRM03 | KRM02 | KRM01 | KRM00 |

#### Address: FFF36H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0     |

|--------|---|---|---|---|---|---|-------|-------|

| KRM1   | 0 | 0 | 0 | 0 | 0 | 0 | KRM09 | KRM08 |

| KRM0n | Key interrupt mode control $(n = 0 \text{ to } 9)$ |  |  |  |  |  |  |

|-------|----------------------------------------------------|--|--|--|--|--|--|

| 0     | oes not detect key interrupt signal                |  |  |  |  |  |  |

| 1     | Detects key interrupt signal                       |  |  |  |  |  |  |

- Cautions 1. When a falling edge (KRMD = 0) is selected and a key interrupt signal is detected (KRM0n = 1), pull up the relevant input pins to Vod by an external resistor. The internal pull-up resistor can be used by setting the relevant bits to 1 in the key interrupt input pins PU125 and PU00 to PU03 (pull-up resistor registers 12 and 0 (the bit 5 of PU12 and bits 0 to 3 of PU0)).

- 2. An interrupt is generated if the target bits of the KRM0 and KRM1 registers are set while a low level (when KREG = 0) or high level (when KREG = 1) is input to the key interrupt input pin. To ignore this interrupt, set the KRM0 and KRM1 registers after disabling interrupt servicing by using the interrupt mask flag. After waiting for the key interrupt input high-level width or low-level width (see 28.4 AC characteristics or 29.4 AC characteristics), clear the interrupt request flag and enable interrupt servicing.

- **3.** The bits not used in the key interrupt mode can be used as normal ports.

# 16.4 Key Interrupt Operation

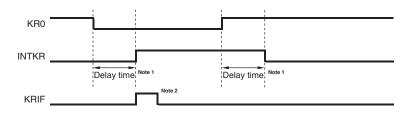

## 16.4.1 When not using the key interrupt flag (KRMD = 0)

A key interrupt (INTKR) is generated when the valid edge specified by the setting of the KREG bit is input to a key interrupt pin (KR0 to KR9). The channel to which the valid edge was input can be identified by reading the port register and checking the port level after the key interrupt (INTKR) is generated.

The INTKR signal changes according to the input level of the key interrupt input pin (KR0 to KR5).

# Figure 16-6. Operation of INTKR Signal When a Key Interrupt is Input to a Single Channel (When KRMD = 0 and KREG = 0)

- Notes 1. The maximum delay time is the maximum value of the high-level width and low-level width of the key interrupt input (see 28.4 AC Characteristics or 29.4 AC Characteristics).

- 2. Cleared by acknowledgment of vectored interrupt request or software.

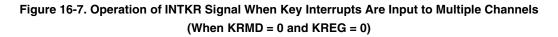

The operation when a valid edge is input to multiple key interrupt input pins is shown in Figure 16-7. The INTKR signal is set while a low level is being input to one pin (when KREG is set to 0). Therefore, even if a falling edge is input to another pin in this period, a key interrupt (INTKR) will not be generated again (<1> in the figure).

- Notes 1. The maximum delay time is the maximum value of the high-level width and low-level width of the key interrupt input (see 28.4 AC Characteristics or 29.4 AC Characteristics).

- 2. Cleared by acknowledgment of vectored interrupt request or bit cleared by software.

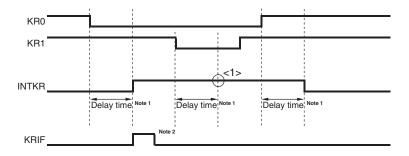

# Figure 19-2. Timing of Generation of Internal Reset Signal by Power-on-reset Circuit and Voltage Detector (3/3)

# Notes

- **1.** The internal reset processing time includes the oscillation accuracy stabilization time of the high-speed on-chip oscillator clock.

- 2. The high-speed on-chip oscillator clock can be switched to the high-speed system clock as the CPU clock. To use the X1 clock, use the oscillation stabilization time counter status register (OSTC) to confirm the lapse of the oscillation stabilization time.

- The time until normal operation starts includes the following LVD reset processing time after the LVD detection level (VLVD) is reached as well as the voltage stabilization wait + POR reset processing time after the VPOR (1.51 V, typ.) is reached.

- LVD reset processing time: 0 ms to 0.0701 ms (max.)

- 4. When the power supply voltage is below the lower limit for operation and the power supply voltage is then restored after an internal reset is generated only by the voltage detector (LVD), the following LVD reset processing time is required after the LVD detection level (V<sub>LVD</sub>) is reached. LVD reset processing time: 0.0629 ms (typ.), 0.0701 ms (max.)

- **Remarks** 1. VLVDH, VLVDL: LVD detection voltage

- VPOR: POR power supply rise detection voltage

- VPDR: POR power supply fall detection voltage

- When the LVD interrupt mode is selected (option byte 000C1H: LVIMD1 = 0, LVIMD0 = 1), the time until normal operation starts after power is turned on is the same as the time specified in Note 3 of Figure 19-2 (3).

# Figure 23-2. Format of User Option Byte (000C1H) (2/2)

Address: 000C1H

| <br>7 | 6     | 5     | 4        | 3     | 2     | 1       | 0       |

|-------|-------|-------|----------|-------|-------|---------|---------|

| VPOC2 | VPOC1 | VPOC0 | PORTSELB | LVIS1 | LVIS0 | LVIMDS1 | LVIMDS0 |

#### • LVD setting (interrupt mode)

| Detection   | Detection voltage |                | Option byte setting value |                |        |       |         |         |  |  |

|-------------|-------------------|----------------|---------------------------|----------------|--------|-------|---------|---------|--|--|

| Vı          | VD                | VPOC2          | VPOC1                     | VPOC0          | LVIS1  | LVIS0 | Mode    | setting |  |  |

| Rising edge | Falling edge      |                |                           |                |        |       | LVIMDS1 | LVIMDS0 |  |  |

| 1.88 V      | 1.84 V            | 0              | 0                         | 1              | 1      | 1     | 0       | 1       |  |  |

| 1.98 V      | 1.94 V            |                | 0                         | 1              | 1      | 0     |         |         |  |  |

| 2.09 V      | 2.04 V            |                | 0                         | 1              | 0      | 1     |         |         |  |  |

| 2.50 V      | 2.45 V            |                | 1                         | 0              | 1      | 1     |         |         |  |  |

| 2.61 V      | 2.55 V            |                | 1                         | 0              | 1      | 0     |         |         |  |  |

| 2.71 V      | 2.65 V            |                | 1                         | 0              | 0      | 1     |         |         |  |  |

| 2.81 V      | 2.75 V            |                | 1                         | 1              | 1      | 1     |         |         |  |  |

| 2.92 V      | 2.86 V            |                | 1                         | 1              | 1      | 0     |         |         |  |  |

| 3.02 V      | 2.96 V            |                | 1                         | 1              | 0      | 1     |         |         |  |  |

| 3.13 V      | 3.06 V            |                | 0                         | 1              | 0      | 0     |         |         |  |  |

| 3.75 V      | 3.67 V            |                | 1                         | 0              | 0      | 0     |         |         |  |  |

| 4.06 V      | 3.98 V            |                | 1                         | 1              | 0      | 0     |         |         |  |  |

|             | _                 | Setting of val | ues other than            | above is prohi | oited. |       |         |         |  |  |

# • LVD off (by controlling the externally input reset signal on the RESET pin)

| Detection voltage |              |                |                | Option          | n byte setting v | value |         |         |

|-------------------|--------------|----------------|----------------|-----------------|------------------|-------|---------|---------|

| VLVD              |              | VPOC2          | VPOC1          | VPOC0           | LVIS1            | LVIS0 | Mode    | setting |

| Rising edge       | Falling edge |                |                |                 |                  |       | LVIMDS1 | LVIMDS0 |

| _                 | -            | 1              | ×              | ×               | ×                | ×     | ×       | 1       |

| _                 |              | Setting of val | ues other than | above is prohil | bited.           |       |         |         |

# • Setting of the P125/KR1/SI01/RESET Pin (20-, 24-pin products)

| PORTSELB | P125/RESET pin control                                         |  |  |  |  |

|----------|----------------------------------------------------------------|--|--|--|--|

| 0        | ort function (P125/KR1/SI01)                                   |  |  |  |  |

| 1        | RESET input (The internal pull-up resistor is always enabled.) |  |  |  |  |

Note 20- and 24-pin products only

Cautions 1. In the 30-pin products, be sure to set bit 4 (PORTSELB) to 1.

2. After power is supplied, the reset state must be retained until the operating voltage becomes in the range defined in 28.4 or 29.4 AC Characteristics. This is done by utilizing the voltage detection circuit or controlling the externally input reset signal. After the power supply is turned off, this LSI should be placed in the STOP mode, or placed in the reset state by utilizing the voltage detection circuit or controlling the externally input reset signal, before the voltage falls below the operating range. The range of operating voltage varies with the setting of the user option byte (000C2H).

#### Remarks 1. ×: don't care

- 2. For details on the LVD circuit, see CHAPTER 20 VOLTAGE DETECTOR.

- 3. The detection voltage is a typical value. For details, see 28.6.4 or 29.6.4 LVD circuit characteristics.

RENESAS