Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 14                                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 512 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | 20-LSSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10267dsp-x0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Special Function Register (SFR) Name               | Symbol |       | R/W | Manip        | ulable Bit | After Reset  |           |

|---------|----------------------------------------------------|--------|-------|-----|--------------|------------|--------------|-----------|

|         |                                                    |        |       |     | 1-bit        | 8-bit      | 16-bit       |           |

| F00F0H  | Peripheral enable register 0                       | PER0   |       | R/W | $\checkmark$ |            | -            | 00H       |

| F00F3H  | Operation speed mode control register              | OSMC   |       | R/W | _            |            | -            | 00H       |

| F00F5H  | RAM parity error control register                  | RPECTL |       | R/W |              |            | _            | 00H       |

| F00FEH  | BCD adjust result register                         | BCDADJ |       | R   | -            |            | _            | Undefined |

| F0100H  | Serial status register 00                          | SSR00L | SSR00 | R   | -            |            | $\checkmark$ | 0000H     |

| F0101H  |                                                    | -      |       |     | -            | _          |              |           |

| F0102H  | Serial status register 01                          | SSR01L | SSR01 | R   | -            |            | $\checkmark$ | 0000H     |

| F0103H  |                                                    | -      |       | -   | -            | _          |              |           |

| F0104H  | Serial status register 02                          | SSR02L | SSR02 | R   | -            |            | $\checkmark$ | 0000H     |

| F0105H  |                                                    | -      |       | -   | -            | _          |              | 0000H     |

| F0106H  | Serial status register 03                          | SSR03L | SSR03 | R   | _            |            | $\checkmark$ | 0000H     |

| F0107H  |                                                    | _      |       |     | _            | -          | 1 [          | 0000H     |

| F0108H  | Serial flag clear trigger register 00              | SIR00L | SIR00 | R/W | -            |            | $\checkmark$ | 0000H     |

| F0109H  |                                                    | -      |       |     | -            | -          |              |           |

| F010AH  | Serial flag clear trigger register 01              | SIR01L | SIR01 | R/W | —            |            | $\checkmark$ | 0000H     |

| F010BH  |                                                    | -      |       |     | -            | -          |              |           |

| F010CH  | Serial flag clear trigger register 02              | SIR02L | SIR02 | R/W | -            |            | $\checkmark$ | 0000H     |

| F010DH  |                                                    | -      |       |     | -            | -          |              |           |

| F010EH  | Serial flag clear trigger register 03              | SIR03L | SIR03 | R/W | -            |            | $\checkmark$ | 0000H     |

| F010FH  |                                                    | -      |       |     | -            | _          |              |           |

| F0110H  | Serial mode register 00                            | SMR00  |       | R/W | -            | -          | $\checkmark$ | 0020H     |

| F0111H  |                                                    |        |       |     |              |            |              |           |

| F0112H  | Serial mode register 01                            | SMR01  |       | R/W | -            | -          | $\checkmark$ | 0020H     |

| F0113H  |                                                    |        |       |     |              |            |              |           |

| F0114H  | Serial mode register 02                            | SMR02  |       | R/W | -            | -          | $\checkmark$ | 0020H     |

| F0115H  |                                                    |        |       |     |              |            |              |           |

| F0116H  | Serial mode register 03                            | SMR03  |       | R/W | —            | -          | $\checkmark$ | 0020H     |

| F0117H  |                                                    |        |       |     |              |            | ,            |           |

| F0118H  | Serial communication operation setting register 00 | SCR00  |       | R/W | —            | —          | $\checkmark$ | 0087H     |

| F0119H  | °                                                  |        |       |     |              |            |              |           |

| F011AH  | Serial communication operation setting register 01 | SCR01  |       | R/W | -            | -          | $\checkmark$ | 0087H     |

| F011BH  | 5                                                  | 00500  |       | DAM |              |            | .1           | 000711    |

| F011CH  | Serial communication operation setting register 02 | SCR02  |       | R/W | -            | -          | $\checkmark$ | 0087H     |

| F011DH  | °                                                  | 00000  |       | DAA |              |            | .1           | 000711    |

| F011EH  | Serial communication operation setting register 03 | SCR03  |       | R/W | _            | -          |              | 0087H     |

| F011FH  |                                                    |        |       |     |              |            |              |           |

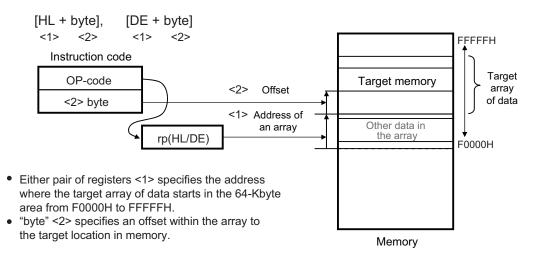

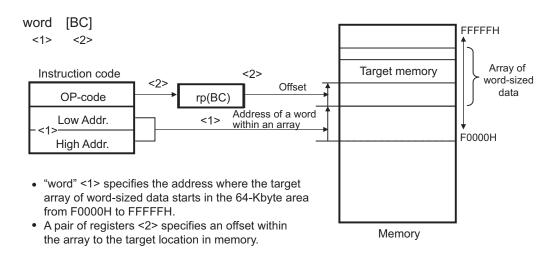

Figure 3-29. Example of [HL + byte], [DE + byte]

#### 5.4.2 High-speed on-chip oscillator

The high-speed on-chip oscillator is incorporated in the RL78/G12. The frequency can be selected from among 24, 16, 12, 8, 6, 4, 3, 2, or 1 MHz by using the option byte (000C2H). Oscillation can be controlled by bit 0 (HIOSTOP) of the clock operation status control register (CSC). The high-speed on-chip oscillator automatically starts oscillating after reset release.

#### 5.4.3 Low-speed on-chip oscillator

The low-speed on-chip oscillator is incorporated in the RL78/G12.

The low-speed on-chip oscillator clock is used only as the watchdog timer, and 12-bit interval timer clock. The low-speed on-chip oscillator clock cannot be used as the CPU clock.

This clock operates when bit 4 (WDTON) of the option byte (000C0H), bit 4 (WUTMMCK0) of the operation speed mode control register (OSMC), or both are set to 1.

Unless the watchdog timer is stopped and WUTMMCK0 is a value other than zero, oscillation of the low-speed on-chip oscillator continues. Note that only when the watchdog timer is operating and the WUTMMCK0 bit is 0, oscillation of the low-speed on-chip oscillator will stop while the WDSTBYON bit is 0 and operation is in the HALT, STOP, or SNOOZE mode. While the watchdog timer operates, the low-speed on-chip oscillator clock does not stop even if the program freezes.

# 5.5 Clock Generator Operation

The clock generator generates the following clocks and controls the operation modes of the CPU, such as standby mode (see **Figure 5-1**).

- Main system clock fMAIN

- High-speed system clock f<sub>MX</sub> X1 clock fx

- External main system clock fex

- High-speed on-chip oscillator clock fin

- Low-speed on-chip oscillator clock fill

- CPU/peripheral hardware clock fclk

The CPU starts operation when the high-speed on-chip oscillator starts outputting after a reset release in the RL78/G12. When the power supply voltage is turned on, the clock generator operation is shown in Figure 5-13.

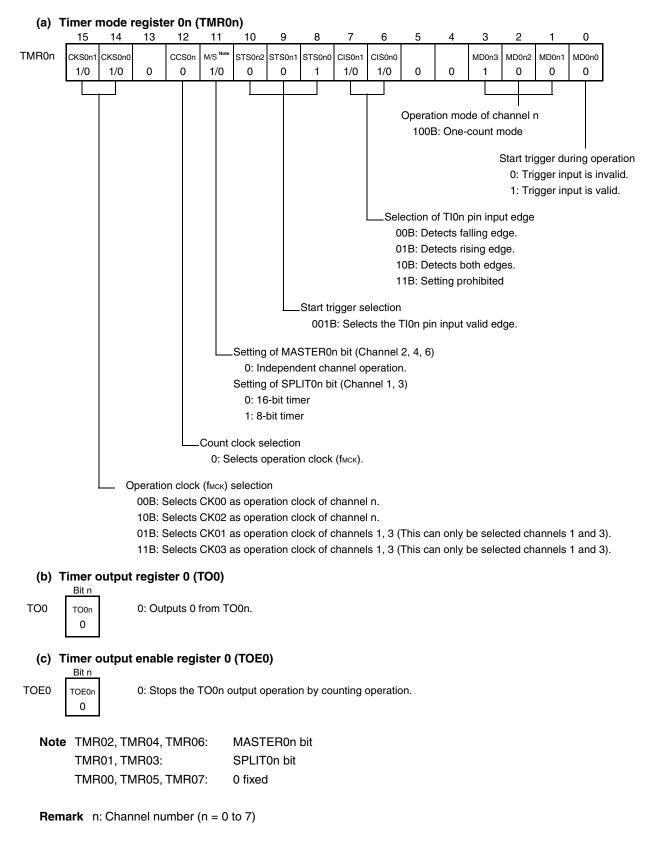

| Address: : F0190H, F0191H (TMR00) to F019EH, F019FH (TMR07) After reset: 0000H R/W |     |     |    |     |                   |     |     |     |     |     |   |   |     |     |     |     |

|------------------------------------------------------------------------------------|-----|-----|----|-----|-------------------|-----|-----|-----|-----|-----|---|---|-----|-----|-----|-----|

| Symbol                                                                             | 15  | 14  | 13 | 12  | 11                | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3   | 2   | 1   | 0   |

| TMR0n                                                                              | CKS | CKS | 0  | CCS | MAST              | STS | STS | STS | CIS | CIS | 0 | 0 | MD  | MD  | MD  | MD  |

| (n =2, 4, 6)                                                                       | 0n1 | 0n0 |    | 0n  | ER0n              | 0n2 | 0n1 | 0n0 | 0n1 | 0n0 |   |   | 0n3 | 0n2 | 0n1 | 0n0 |

|                                                                                    |     |     |    |     |                   |     |     |     |     |     |   |   |     |     |     |     |

| Symbol                                                                             | 15  | 14  | 13 | 12  | 11                | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3   | 2   | 1   | 0   |

| TMR0n                                                                              | CKS | CKS | 0  | CCS | SPLIT             | STS | STS | STS | CIS | CIS | 0 | 0 | MD  | MD  | MD  | MD  |

| (n = 1, 3)                                                                         | 0n1 | 0n0 |    | 0n  | 0n                | 0n2 | 0n1 | 0n0 | 0n1 | 0n0 |   |   | 0n3 | 0n2 | 0n1 | 0n0 |

|                                                                                    |     |     |    |     |                   |     |     |     |     |     |   |   |     |     |     |     |

| Symbol                                                                             | 15  | 14  | 13 | 12  | 11                | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3   | 2   | 1   | 0   |

| TMR0n                                                                              | CKS | CKS | 0  | CCS | 0 <sup>Note</sup> | STS | STS | STS | CIS | CIS | 0 | 0 | MD  | MD  | MD  | MD  |

| (n = 0, 5, 7)                                                                      | 0n1 | 0n0 |    | 0n  |                   | 0n2 | 0n1 | 0n0 | 0n1 | 0n0 |   |   | 0n3 | 0n2 | 0n1 | 0n0 |

#### Figure 6-9. Format of Timer Mode Register 0n (TMR0n) (2/4)

(Bit 11 of TMR0n (n = 2, 4, 6))

| MASTER0n                                                                                                                                                                                                                      | Selection between using channel n independently or simultaneously with another channel (as a slave or master)      |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0                                                                                                                                                                                                                             | Operates in independent channel operation function or as slave channel in simultaneous channel operation function. |  |  |  |  |

| 1                                                                                                                                                                                                                             | Operates as master channel in simultaneous channel operation function.                                             |  |  |  |  |

| Only the 2, 4, 6 channel can be set as a master channel (MASTER0n = 1).<br>Be sure to use channel 0, 5, 7 are fixed to 0 (Regardless of the bit setting, channel 0 operates as master, because it<br>is the highest channel). |                                                                                                                    |  |  |  |  |

Clear the MASTER0n bit to 0 for a channel that is used with the independent channel operation function.

| (Bit 11 | of TMR0n | (n = 1.            | 3))      |

|---------|----------|--------------------|----------|

| (010111 |          | $(\cdots - \cdot)$ | $\sim n$ |

| \       |                                                                                                                      |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SPLIT0n | Selection of 8 or 16-bit timer operation for channels 1 and 3                                                        |  |  |  |  |

| 0       | Operates as 16-bit timer.                                                                                            |  |  |  |  |

|         | (Operates in independent channel operation function or as slave channel in simultaneous channel operation function.) |  |  |  |  |

| 1       | Operates as 8-bit timer.                                                                                             |  |  |  |  |

| STS0n2           | STS0n1 | STS0n0 | Setting of start trigger or capture trigger of channel n                                                                                       |

|------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | 0      | 0      | Only software trigger start is valid (other trigger sources are unselected).                                                                   |

| 0                | 0      | 1      | Valid edge of the TI0n pin input is used as both the start trigger and capture trigger.                                                        |

| 0                | 1      | 0      | Both the edges of the TI0n pin input are used as a start trigger and a capture trigger.                                                        |

| 1                | 1 0 0  |        | Interrupt signal of the master channel is used (when the channel is used as a slave channel with the simultaneous channel operation function). |

| Other than above |        | ove    | Setting prohibited                                                                                                                             |

**Note** Bit 11 is a read-only bit and fixed to 0. Writing to this bit is ignored.

**Remark** n: Channel number (n = 0 to 7)

# 6.7 Timer Input (TI0n) Control

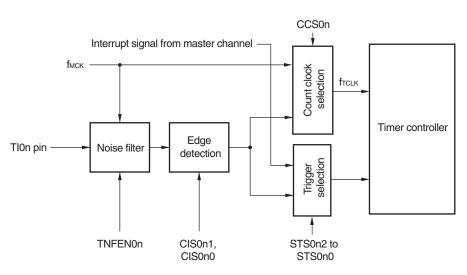

#### 6.7.1 TIOn input circuit configuration

A signal is input from a timer input pin, goes through a noise filter and an edge detector, and is sent to a timer controller. Enable the noise filter for the pin in need of noise removal. The following shows the configuration of the input circuit.

#### Figure 6-36. Input Circuit Configuration

#### 6.7.2 Noise filter

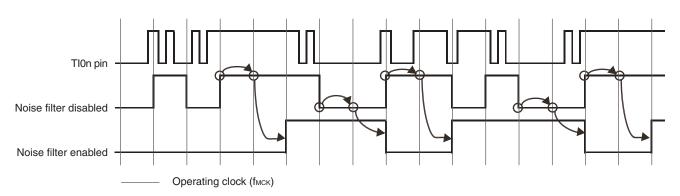

When the noise filter is disabled, the input signal is only synchronized with the operating clock (fMCK) for channel n. When the noise filter is enabled, after synchronization with the operating clock (fMCK) for channel n, whether the signal keeps the same value for two clock cycles is detected. The following shows differences in waveforms output from the noise filter between when the noise filter is enabled and disabled.

S ≺S <br/> <br/>

|                               | Software Operation                                                                                                                                                                                                                                                                            | Hardware Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                                                                                               | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                                                                                                                                                                                                                           |

|                               | Sets the TAU0EN bit of peripheral enable register 0<br>(PER0) to 1.                                                                                                                                                                                                                           | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                                                                                                                                                                                                                                                                                                                                                              |

|                               | Sets timer clock select register 0 (TPS0).<br>Determines clock frequencies of CK00 to CK03.                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Channel<br>default<br>setting | Sets the corresponding bit of the noise filter enable<br>registers 1 (NFEN1) to 0 (off) or 1 (on).<br>Sets timer mode register 0n (TMR0n) (determines<br>operation mode of channel).<br>Sets noise filter enable register 1 (NFEN1)<br>Clears the TOE0n bit to 0 and stops operation of TO0n. | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                                                                                                                                                                                                                          |

| • Operation<br>start          | Sets the TS0n bit to 1.<br>The TS0n bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                                                                                            | TE0n = 1, and the TI0n pin start edge detection wait status is set.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | Detects the TI0n pin input count start valid edge.                                                                                                                                                                                                                                            | Clears timer count register 0n (TCR0n) to 0000H and starts counting up.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| During<br>operation           | Set value of the TDR0n register can always be read.<br>The TCR0n register can always be read.<br>The TSR0n register can always be read.<br>Set values of the TMR0n register, TOM0n, TOL0n, TO0n,<br>and TOE0n bits cannot be changed.                                                         | When the TI0n pin start edge is detected, the counter<br>(TCR0n) counts up from 0000H. If a capture edge of the<br>TI0n pin is detected, the count value is transferred to time<br>data register 0n (TDR0n) and INTTM0n is generated.<br>If an overflow occurs at this time, the OVF bit of timer<br>status register 0n (TSR0n) is set; if an overflow does not<br>occur, the OVF bit is cleared. The TCR0n register stops<br>the count operation until the next TI0n pin start edge is<br>detected. |

| Operation<br>stop             | The TT0n bit is set to 1.<br>The TT0n bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                                                                                          | TE0n = 0, and count operation stops.<br>The TCR0n register holds count value and stops.<br>The OVF bit of the TSR0n register is also held.                                                                                                                                                                                                                                                                                                                                                           |

| TAU<br>stop                   | The TAU0EN bit of the PER0 register is cleared to 0.                                                                                                                                                                                                                                          | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.                                                                                                                                                                                                                                                                                                                                                                                                     |

# Figure 6-57. Operation Procedure When Input Signal High-/Low-Level Width Measurement Function Is Used

**Remark** n: Channel number (n = 0 to 7)

## Figure 6-60. Example of Set Contents of Registers to Delay Counter (2/2)

TOM0n 0 0: Sets master channel output mode.

**Remark** n: Channel number (n = 0 to 7)

| e oourmoud | Scannode (ADMD = 1)  |      |      |      |        |                      |        |        |

|------------|----------------------|------|------|------|--------|----------------------|--------|--------|

| ADS4       | ADS3                 | ADS2 | ADS1 | ADS0 |        | Analog input channel |        |        |

|            |                      |      |      |      | Scan 0 | Scan 1               | Scan 2 | Scan 3 |

| 0          | 0                    | 0    | 0    | 0    | ANI0   | ANI1                 | ANI2   | ANI3   |

| 0          | 0                    | 0    | 0    | 1    | ANI1   | ANI2                 | ANI3   | -      |

| 0          | 0                    | 0    | 1    | 0    | ANI2   | ANI3                 | -      | -      |

| 0          | 0                    | 0    | 1    | 1    | ANI3   | -                    | -      | -      |

|            | Other than the above |      |      |      |        |                      |        |        |

$\bigcirc$  Scan mode (ADMD = 1)

Remark -: Ignore the conversion result because it is undefined.

Cautions 1. Be sure to clear bits 5 and 6 to 0.

- 2. Set a channel to be set the analog input by ADPC and PMCx registers in the input mode by using port mode registers 0, 1, 2, 4, 12, or 14 (PM0, PM1, PM2, PM4 PM12, PM14).

- **3.** Do not set the pin that is set by the A/D port configuration register (ADPC) as digital I/O by the ADS register.

- **4.** Do not set the pin that is set by port mode control registers 0, 1, 4, 12, 14 (PMC0, PMC1, PMC4, PMC12, PMC14) as digital I/O by the ADS register.

- Only rewrite the value of the ADISS bit while A/D conversion comparator operation is stopped(ADCS = 0, ADCE = 0)

- **6.** If using AVREFP as the + side reference voltage of the A/D converter, do not select ANIO as an A/D conversion channel.

- **7.** If using AVREFM as the side reference voltage of the A/D converter, do not select ANI1 as an A/D conversion channel.

- If the ADISS bit is set to 1, the internal reference voltage (1.45 V) cannot be used for the + side reference voltage. After the ADISS bit is set to 1, the initial conversion result cannot be used. For details about the setting flow, see 10.7.4 Setup when temperature sensor output voltage/internal reference voltage is selected.

- 9. Do not set the ADISS bit to 1 when shifting to the STOP mode or HALT mode. If the ADISS bit is set to 1, the A/D converter reference voltage current (IADREF) indicated in 28.3.2 or 29.3.2 Supply current characteristics will be added.

# 11.5 Operation of 3-Wire Serial I/O (CSI00, CSI01, CSI11, CSI20) Communication

This is a clocked communication function that uses three lines: serial clock (SCK) and serial data (SI and SO) lines. [Data transmission/reception]

- Data length of 7 or 8 bits

- Phase control of transmit/receive data

- MSB/LSB first selectable

[Clock control]

- Master/slave selection

- Phase control of I/O clock

- Setting of transfer period by prescaler and internal counter of each channel

- Maximum transfer rate<sup>Note</sup>

- During master communication: Max. fcLk/2 (CSI00 only)

- Max. fclk/4

During slave communication: Max. fmck/6

[Interrupt function]

Transfer end interrupt/buffer empty interrupt

[Error detection flag]

• Overrun error

In addition, CSI00 (channel 0 of unit 0) supports the SNOOZE mode. When SCK00 pin input is detected while in the STOP mode, the SNOOZE mode makes data reception that does not require the CPU possible.

Note Use the clocks within a range satisfying the SCK cycle time (tκcr) characteristics. For details, see CHAPTER 28 ELECTRICAL SPECIFICATIONS (A, D: T<sub>A</sub> = -40 to +85°C) or CHAPTER 29 ELECTRICAL SPECIFICATIONS (G: T<sub>A</sub> = -40 to +105°C).

The channels supporting 3-wire serial I/O (CSI00, CSI01, CSI11, CSI20) are channels 0, 1, 3 of SAU0 and channel 0 of SAU1.

20- or 24-pin products

| Unit | Channel | Used as CSI           | Used as UART | Used as Simplified I <sup>2</sup> C |

|------|---------|-----------------------|--------------|-------------------------------------|

| 0    | 0       | CSI00                 | UART0        | IIC00 <sup>Note</sup>               |

| 0    | 1       | CSI01 <sup>Note</sup> |              | IIC01 <sup>Note</sup>               |

30-pin products

| ľ | Unit | Channel | Used as CSI           | Used as UART          | Used as Simplified I <sup>2</sup> C |

|---|------|---------|-----------------------|-----------------------|-------------------------------------|

|   | 0    | 0       | CSI00                 | UART0                 | IIC00                               |

|   |      | 1       | -                     |                       | -                                   |

|   |      | 2       | -                     | UART1 <sup>Note</sup> | _                                   |

|   |      | 3       | CSI11 <sup>Note</sup> | UARTI                 | IIC11 <sup>Note</sup>               |

|   | 1    | 0       | CSI20 <sup>Note</sup> | UART2 <sup>Note</sup> | IIC20 <sup>Note</sup>               |

|   |      | 1       |                       | UART2                 | -                                   |

Note Provided in the R5F102 products only.

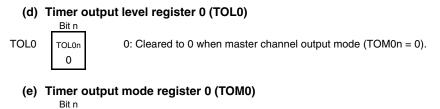

#### Figure 12-30. Slave Operation Flowchart (1)

**Remark** Conform to the specifications of the product that is in communication, regarding the transmission and reception formats.

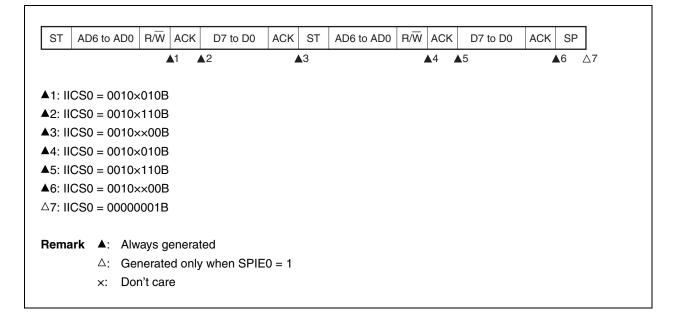

#### (c) Start ~ Code ~ Data ~ Start ~ Code ~ Data ~ Stop

#### (i) When WTIM0 = 0 (after restart, extension code reception)

(ii) When WTIM0 = 1 (after restart, extension code reception)

### CHAPTER 14 DMA CONTROLLER

The R5F102 products of the RL78/G12 have an internal DMA (Direct Memory Access) controller.

Data can be automatically transferred between the peripheral hardware supporting DMA, SFRs, and internal RAM without via CPU.

As a result, the normal internal operation of the CPU and data transfer can be executed in parallel with transfer between the SFR and internal RAM, and therefore, a large capacity of data can be processed. In addition, real-time control using communication, timer, and A/D can also be realized.

#### 14.1 Functions of DMA Controller

- O Number of DMA channels: 2 channels (R5F102 products)

- O Transfer unit: 8 or 16 bits

- O Maximum transfer unit: 1024 times

- O Transfer type: 2-cycle transfer (One transfer is processed in 2 clocks and the CPU stops during that processing.)

- O Transfer mode: Single-transfer mode

- O Transfer request: Selectable from the following peripheral hardware interrupts

- A/D converter

- Serial interface (CSI00, CSI01, CSI11, CSI20, UART0 to UART2)

- Timer (channel 0, 1, 2, 3)

- O Transfer target: Between SFR and internal RAM

Here are examples of functions using DMA.

- Successive transfer of serial interface

- Consecutive capturing of A/D conversion results

- Capturing A/D conversion result at fixed interval

- Capturing port value at fixed interval

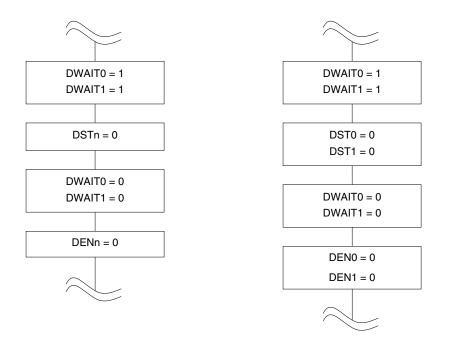

## Figure 14-11. Forced Termination of DMA Transfer (2/2)

# Example 3

- Procedure for forcibly terminating the DMA transfer for one channel if both channels are used

- Procedure for forcibly terminating the DMA transfer for both channels if both channels are used

- **Caution** In example 3, the system is not required to wait two clock cycles after the DWAITn bit is set to 1. In addition, the system does not have to wait two clock cycles after clearing the DSTn bit to 0, because more than two clock cycles elapse from when the DSTn bit is cleared to 0 to when the DENn bit is cleared to 0.

- **Remarks 1.** n: DMA channel number (n = 0, 1)

- 2. 1 clock: 1/fclk (fclk: CPU clock)

# 15.3.3 Priority specification flag registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, PR12H)

The priority specification flag registers are used to set the priority level of the corresponding maskable interrupt.

A priority level is set by using the PR0xy and PR1xy registers in combination (xy = 0L, 0H, 1L, 1H, 2L, or 2H).

The PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, and PR12H L registers can be set by a 1-bit or 8-bit memory manipulation instruction. If the PR00L and PR00H registers, the PR01L and PR01H registers, the PR02L and PR02H registers, the PR10L and PR10H registers, the PR11L and PR11H registers, and the PR12L and PR12H registers are combined to form 16-bit registers PR00 and PR10, they can be set by a 16-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

**Remark** If an instruction that writes data to this register is executed, the number of instruction execution clocks increases by 2 clocks.

# Figure 23-2. Format of User Option Byte (000C1H) (1/2)

Address: 000C1H

| 7     | 6     | 5     | 4 3              |       | 2     | 1       | 0       |  |

|-------|-------|-------|------------------|-------|-------|---------|---------|--|

| VPOC2 | VPOC1 | VPOC0 | PORTSELB<br>Note | LVIS1 | LVIS0 | LVIMDS1 | LVIMDS0 |  |

• LVD setting (interrupt mode & reset mode)

| Detection voltage |                 |                 | Option byte setting value                         |       |       |       |       |         |         |  |

|-------------------|-----------------|-----------------|---------------------------------------------------|-------|-------|-------|-------|---------|---------|--|

| Vlvdh Vlvdl       |                 | VLVDL           | VPOC2                                             | VPOC1 | VPOC0 | LVIS1 | LVIS0 | Mode    | setting |  |

| Rising<br>edge    | Falling<br>edge | Falling<br>edge |                                                   |       |       |       |       | LVIMDS1 | LVIMDS0 |  |

| 1.98 V            | 1.94 V          | 1.84 V          | 0                                                 | 0     | 1     | 1     | 0     | 1       | 0       |  |

| 2.09 V            | 2.04 V          |                 |                                                   |       |       | 0     | 1     |         |         |  |

| 3.13 V            | 3.06 V          |                 |                                                   |       |       | 0     | 0     |         |         |  |

| 2.61 V            | 2.55 V          | 2.45 V          |                                                   | 1     | 0     | 1     | 0     |         |         |  |

| 2.71 V            | 2.65 V          |                 |                                                   |       |       | 0     | 1     |         |         |  |

| 3.75 V            | 3.67 V          |                 |                                                   |       |       | 0     | 0     |         |         |  |

| 2.92 V            | 2.86 V          | 2.75 V          |                                                   | 1     | 1     | 1     | 0     |         |         |  |

| 3.02 V            | 2.96 V          |                 |                                                   |       |       | 0     | 1     |         |         |  |

| 4.06 V            | 3.98 V          |                 |                                                   |       |       | 0     | 0     |         |         |  |

|                   | —               |                 | Setting of values other than above is prohibited. |       |       |       |       |         |         |  |

### • LVD setting (reset mode)

| Detection voltage |              | Option byte setting value |                |                |        |       |              |         |  |

|-------------------|--------------|---------------------------|----------------|----------------|--------|-------|--------------|---------|--|

| Vlvd              |              | VPOC2                     | VPOC1          | VPOC0 LVIS1    |        | LVIS0 | Mode setting |         |  |

| Rising edge       | Falling edge |                           |                |                |        |       | LVIMDS1      | LVIMDS0 |  |

| 1.88 V            | 1.84 V       | 0                         | 0              | 1              | 1      | 1     | 1            | 1       |  |

| 1.98 V            | 1.94 V       |                           | 0              | 1              | 1      | 0     |              |         |  |

| 2.09 V            | 2.04 V       |                           | 0              | 1              | 0      | 1     |              |         |  |

| 2.50 V            | 2.45 V       |                           | 1              | 0              | 1      | 1     |              |         |  |

| 2.61 V            | 2.55 V       |                           | 1              | 0              | 1      | 0     |              |         |  |

| 2.71 V            | 2.65 V       |                           | 1              | 0              | 0      | 1     |              |         |  |

| 2.81 V            | 2.75 V       |                           | 1              | 1              | 1      | 1     |              |         |  |

| 2.92 V            | 2.86 V       |                           | 1              | 1              | 1      | 0     |              |         |  |

| 3.02 V            | 2.96 V       |                           | 1              | 1              | 0      | 1     |              |         |  |

| 3.13 V            | 3.06 V       |                           | 0              | 1              | 0      | 0     |              |         |  |

| 3.75 V            | 3.67 V       |                           | 1              | 0              | 0      | 0     | ]            |         |  |

| 4.06 V            | 3.98 V       |                           | 1              | 1              | 0      | 0     |              |         |  |

|                   | _            |                           | ues other than | above is prohi | bited. |       |              |         |  |

Note 20- and 24-pin products only

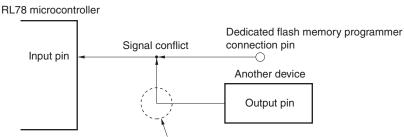

### 24.3 Connection of Pins on Board

To write the flash memory on-board by using the flash memory programmer, connectors that connect the dedicated flash memory programmer must be provided on the target system. First provide a function that selects the normal operation mode or flash memory programming mode on the board.

When the flash memory programming mode is set, all the pins not used for programming the flash memory are in the same status as immediately after reset. Therefore, if the external device does not recognize the state immediately after reset, the pins must be handled as described below.

Remark For the flash memory programming mode, see 24.4.2 Flash memory programming mode.

#### 24.3.1 P40/TOOL0 pin

In the flash memory programming mode, pull up externally with a 1 k $\Omega$  resister, and connect it to the dedicated flash memory programmer.

When using it as a port pin, use it as described below.

| When used as an input pin:  | Do not input a low level for t <sub>HD</sub> period after the external reset release. However, when this pin is used via pull-down resistors, use the 500 k $\Omega$ or more resistors. |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| When used as an output pin: | When this pin is used via pull-down resistors, use the 500 k $\Omega$ or more resistors.                                                                                                |

- Remarks 1. tHD: How long to keep the TOOL0 pin at the low level from when the external reset ends for setting of the flash memory programming mode (see 28.10 or 29.10 Timing of Entry to Flash Memory Programming Modes)

- 2. The SAU and IICA pins are not used for communication between the RL78 microcontroller and dedicated flash memory programmer, because single-line UART (TOOL0 pin) is used.

#### 24.3.2 RESET pin

Signal conflict will occur if the reset signal of the dedicated flash memory programmer and external device are connected to the  $\overrightarrow{\text{RESET}}$  pin that is connected to the reset signal generator on the board. To prevent this conflict, isolate the connection with the reset signal generator.

The flash memory will not be correctly programmed if the reset signal is input from the user system while the flash memory programming mode is set. Do not input any signal other than the reset signal of the dedicated flash memory programmer and external device.

#### Figure 24-5. Signal Conflict (RESET Pin)

In the flash memory programming mode, a signal output by another device will conflict with the signal output by the dedicated flash memory programmer. Therefore, isolate the signal of another device.

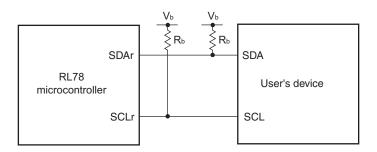

# Simplified I<sup>2</sup>C mode connection diagram (during communication at different potential)

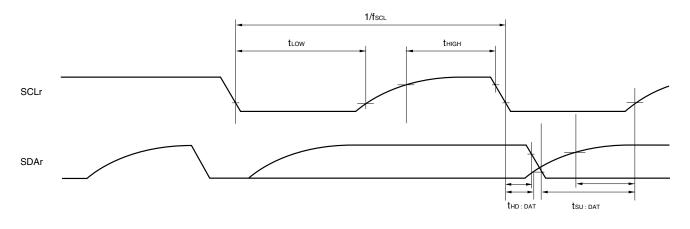

#### Simplified I<sup>2</sup>C mode serial transfer timing (during communication at different potential)

- **Remarks 1.** R<sub>b</sub> [Ω]: Communication line (SDAr, SCLr) pull-up resistance, C<sub>b</sub> [F]: Communication line (SDAr, SCLr) load capacitance, V<sub>b</sub> [V]: Communication line voltage

- **2.** r: IIC Number (r = 00, 20)

- **3.** fMCK: Serial array unit operation clock frequency (Operation clock to be set by the serial clock select register m (SPSm) and the CKSmn bit of serial mode register mn (SMRmn).

m: Unit number (m = 0,1), n: Channel number (n = 0))

- Simplified I<sup>2</sup>C mode is supported only by the R5F102 products.

| Parameter              | Symbol |              | Conditions                                                                                                                |                | HS (high-speed main)<br>Mode |                   | Unit |

|------------------------|--------|--------------|---------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|-------------------|------|

|                        |        |              |                                                                                                                           |                | MIN.                         | MAX.              |      |

| Transfer<br>rate Note4 |        | Reception    | $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$<br>$2.7 \text{ V} \le \text{V}_{\text{b}} \le 4.0 \text{ V}$  |                |                              | fмск/12<br>Note 1 | bps  |

|                        |        |              | Theoretical value o<br>transfer rate<br>f <sub>MCK</sub> = fcLK <sup>Note 2</sup>                                         | of the maximum |                              | 2.0               | Mbps |

|                        |        |              | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V},$<br>$2.3 \text{ V} \leq \text{V}_{\text{b}} \leq 2.7 \text{ V}$ |                |                              | fмск/12<br>Note 1 | bps  |

|                        |        |              | Theoretical value of<br>transfer rate<br>fмск = fclк <sup>Note 2</sup>                                                    | of the maximum |                              | 2.0               | Mbps |

|                        |        |              | $1MCK = 1CLK$ $2.4 V \le V_{DD} < 3.3 V,$ $1.6 V \le V_b \le 2.0 V$                                                       |                |                              | fмск/12<br>Note 1 | bps  |

|                        |        |              | Theoretical value of<br>transfer rate<br>fмск = fclк <sup>Note 2</sup>                                                    | of the maximum |                              | 2.0               | Mbps |

|                        |        | Transmission | $\begin{array}{l} 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \\ 2.7 \ V \leq V_b \leq 4.0 \ V \end{array}$                         |                |                              | Note 3            | bps  |

|                        |        |              | Theoretical value of transfer rate $C_b = 50 \text{ pF}, R_b = 1.4$                                                       |                |                              | 2.0<br>Note 4     | Mbps |

|                        |        |              | $\begin{array}{l} 2.7 \ V \leq V_{DD} < 4.0 \ V, \\ 2.3 \ V \leq V_b \leq 2.7 \ V, \end{array}$                           |                |                              | Note 5            | bps  |

|                        |        |              | Theoretical value of transfer rate $C_b = 50 \text{ pF}, R_b = 2.7$                                                       |                |                              | 1.2<br>Note 6     | Mbps |

|                        |        |              | $\begin{array}{l} 2.4 \ V \leq V_{DD} < 3.3 \ V, \\ 1.6 \ V \leq V_b \leq 2.0 \ V \end{array}$                            |                |                              | Notes<br>2, 7     | bps  |

|                        |        |              | Theoretical value of transfer rate $C_b = 50 \text{ pF}, R_b = 5.5$                                                       |                |                              | 0.43<br>Note 8    | Mbps |

# (5) Communication at different potential (1.8 V, 2.5 V, 3 V) (UART mode)

Notes 1. Transfer rate in the SNOOZE mode is 4800 bps only.

2. The maximum operating frequencies of the CPU/peripheral hardware clock (fcLK) are:

HS (high-speed main) mode: 24 MHz (2.7 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V) 16 MHz (2.4 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V)

**3.** The smaller maximum transfer rate derived by using fMCK/12 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 4.0 V  $\leq$  V\_DD  $\leq$  5.5 V and 2.7 V  $\leq$  V\_b  $\leq$  4.0 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{2.2}{V_b})\} \times 3}$$

[bps]

# RL78/G12