Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 14                                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 512 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | 20-LSSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10267gsp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

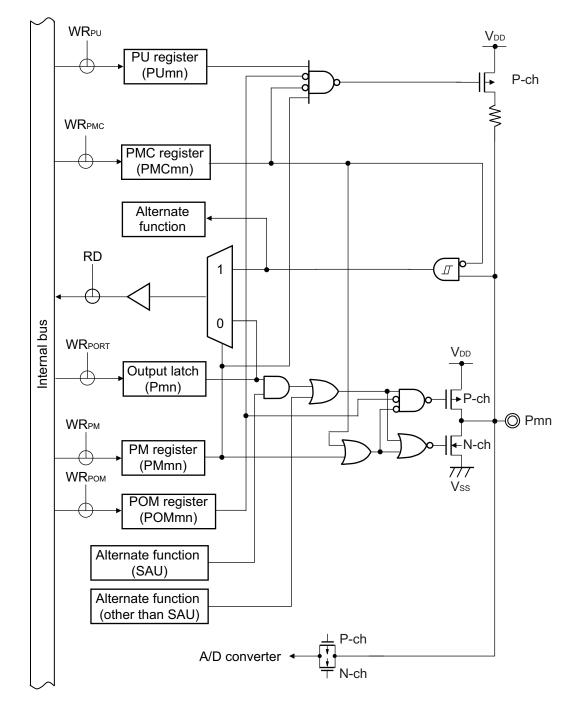

Figure 2-9. Pin Block Diagram for Pin Type 7-3-2

2. SAU: Serial array unit

<R> Caution A through current may flow through if the pin is in the intermediate potential, because the input buffer is also turned on when the pin is in N-ch open-drain output mode by port output mode register (POMx).

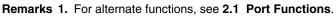

Figure 3-4. Memory Map for the R5F10x69, R5F10x79, and R5F10xA9 (x = 2 or 3)

- <R> Notes 1. Do not allocate the stack area, data buffers for use by the flash library, arguments of library functions, branch destinations in the processing of vectored interrupts, or destinations or sources for DMA transfer to the area from FFE20H to FFEDFH when performing self-programming or rewriting of the data flash memory. For R5F10x69 and R5F10x79, the RAM area used by the flash library starts at FFB00H. For the RAM areas used by the flash library starts at FFB00H. For the RAM areas used by the flash library, see Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944).

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- 3. Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- 4. The areas are reserved in the R5F10369, R5F10379, and R5F103A9.

- **Caution** While RAM parity error resets are enabled (RPERDIS = 0), be sure to initialize RAM areas where data access is to proceed and the RAM area +10 bytes when instructions are fetched from RAM areas, respectively. Reset signal generation sets RAM parity error resets to enabled (RPERDIS = 0). For details, see 21.3.2 RAM parity error detection.

### 6.9.2 Operation as PWM function

Two channels can be used as a set to generate a pulse of any period and duty factor. The period and duty factor of the output pulse can be calculated by the following expressions.

Pulse period = {Set value of TDR0n (master) + 1} × Count clock periodDuty factor [%] = {Set value of TDR0p (slave)}/{Set value of TDR0n (master) + 1} × 1000% output:Set value of TDR0p (slave) = 0000H100% output:Set value of TDR0p (slave)  $\geq$  {Set value of TDR0n (master) + 1}

**Remark** Although the duty factor exceeds 100% if the set value of TDR0p (slave) > (set value of TDR0n (master) + 1), it summarizes to 100% output.

The master channel operates in the interval timer mode. If the channel start trigger bit (TS0n) of timer channel start register 0 (TS0) is set to 1, an interrupt (INTTM0n) is output, the value set to timer data register 0n (TDR0n) is loaded to timer count register 0n (TCR0n), and the counter counts down in synchronization with the count clock. When the counter reaches 0000H, INTTM0n is output, the value of the TDR0n register is loaded again to the TCR0n register, and the counter counts down. This operation is repeated until the channel stop trigger bit (TT0n) of timer channel stop register 0 (TT0) is set to 1.

If two channels are used to output a PWM waveform, the period until the master channel counts down to 0000H is the PWM output (TO0p) cycle.

The slave channel operates in one-count mode. By using INTTMOn from the master channel as a start trigger, the TCR0p register loads the value of the TDR0p register and the counter counts down to 0000H. When the counter reaches 0000H, it outputs INTTM0p and waits until the next start trigger (INTTM0n from the master channel) is generated.

If two channels are used to output a PWM waveform, the period until the slave channel counts down to 0000H is the PWM output (TO0p) duty.

PWM output (TO0p) goes to the active level one clock after the master channel generates INTTM0n and goes to the inactive level when the TCR0p register of the slave channel becomes 0000H.

- **Caution** To rewrite both timer data register 0n (TDR0n) of the master channel and the TDR0p register of the slave channel, a write access is necessary two times. The timing at which the values of the TDR0n and TDR0p registers are loaded to the TCR0n and TCR0p registers is upon occurrence of INTTM0n of the master channel. Thus, when rewriting is performed split before and after occurrence of INTTM0n of the master channel, the TO0p pin cannot output the expected waveform. To rewrite both the TDR0n register of the master and the TDR0p register of the slave, therefore, be sure to rewrite both the registers immediately after INTTM0n is generated from the master channel.

- $\begin{array}{ll} \textbf{Remark} & n: Channel number \ (n=0,\,2,\,4,\,6) \\ & p: Slave \ channel \ number \ (n$

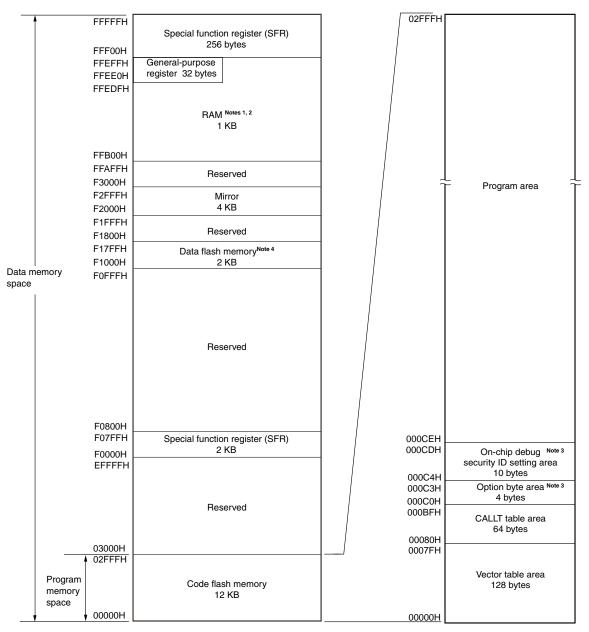

### 10.7.2 Setting up hardware trigger no-wait mode

#### Figure 10-30. Setting up Hardware Trigger No-Wait Mode

**Note** Depending on the settings of the ADRCK bit and ADUL/ADLL register, there is a possibility of no interrupt signal being generated. In this case, the results are not stored in the ADCR and ADCRH registers.

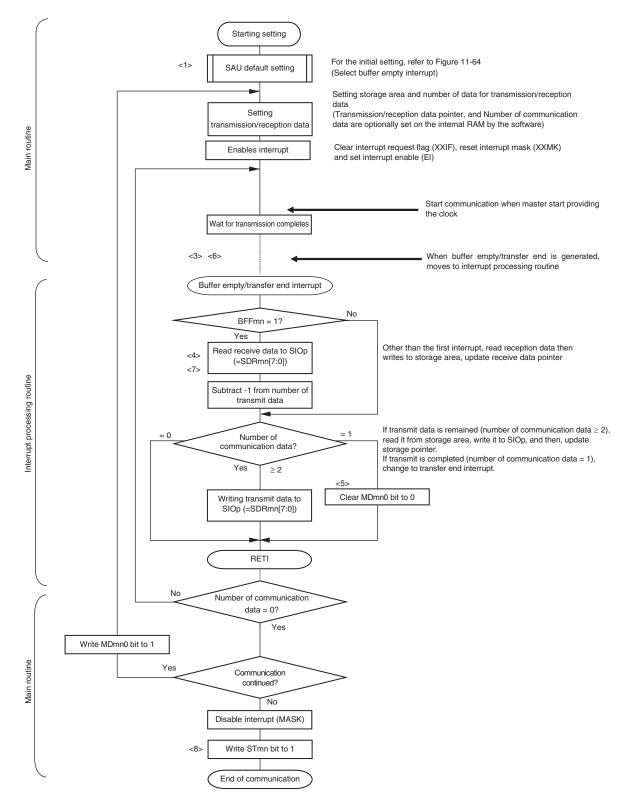

# CHAPTER 11 SERIAL ARRAY UNIT

Serial array unit 0 has two serial channels in 20- and 24-pinproducts and four serial channels in 30-pin products, and serial array unit 1 mounted 30-pin products, has two serial channels.

Each channel can achieve 3-wire serial (CSI), UART, and simplified I<sup>2</sup>C communication.

Function assignment of each channel supported by the RL78/G12 is as shown below.

| 20- | or | 24-pii | n proo | ducts |

|-----|----|--------|--------|-------|

|-----|----|--------|--------|-------|

| Unit | Channel | Used as CSI           | Used as UART | Used as Simplified I <sup>2</sup> C |  |  |

|------|---------|-----------------------|--------------|-------------------------------------|--|--|

| 0    | 0       | CS100                 | UART0        | IIC00 <sup>Note</sup>               |  |  |

|      | 1       | CSI01 <sup>Note</sup> |              | IIC01 <sup>Note</sup>               |  |  |

30-pin products

| Unit | Channel | Used as CSI           | Used as UART          | Used as Simplified I <sup>2</sup> C |

|------|---------|-----------------------|-----------------------|-------------------------------------|

| 0    | 0       | CS100                 | UART0                 | IIC00 <sup>Note</sup>               |

|      | 1       | _                     |                       | _                                   |

|      | 2       | =                     | UART1 <sup>Note</sup> | =                                   |

|      | 3       | CSI11 <sup>Note</sup> |                       | IIC11 <sup>Note</sup>               |

| 1    | 0       | CSI20 <sup>Note</sup> | UART2 <sup>Note</sup> | IIC20 <sup>Note</sup>               |

|      | 1       | _                     |                       | _                                   |

Note Provided in the R5F102 products only.

A single channel cannot be used under multiple communication methods. When a different communication method is to be configured, use another channel.

When using CSI00, CSI20, IIC00, IIC20, UART0, UART1, or UART2, communication between devices with different voltages (1.8, 2.5, or 3 V) is possible, except when the serial I/O for UART0 of a 20- or 24-pin product is assigned to P6 by the setting of the I/O redirection register (PIOR1 = 1). For details about the settings, see **4.4.4 Handling different potentials (1.8 V, 2.5 V, and 3 V) by using I/O buffers.**

#### 11.3.10 Serial channel enable status register m (SEm)

The SEm register indicates whether the data transmission/reception operation of each channel is enabled or disabled. When 1 is written to a bit of serial channel start register m (SSm), the corresponding bit of this register is set to 1.

When 1 is written to a bit of serial channel stop register m (STm), the corresponding bit of this register is cleared to 0. If the operation of channel n is enabled, the value of the CKOmn bit (serial clock output of channel n) of serial output register m (SOm) cannot be rewritten by software, and a value is output from the serial clock pin according to the communication operation.

If the operation of channel n is disabled, the value of the CKOmn bit of the SOm register can be set by software and its value is output from the serial clock pin. In this way, any waveform, such as that of a start condition/stop condition, can be created by software.

The SEm register can be read by a 16-bit memory manipulation instruction.

The lower 8 bits of the SEm register can be set with a 1-bit or 8-bit memory manipulation instruction as SEmL. Reset signal generation clears the SEm register to 0000H.

#### Figure 11-15. Format of Serial Channel Enable Status Register m (SEm)

| Address: F012         | 20H, F0                                            | 121H ( | SE0) | After re | eset: 00 | 00H | R |   |   |   |   |   |              |              |      |      |

|-----------------------|----------------------------------------------------|--------|------|----------|----------|-----|---|---|---|---|---|---|--------------|--------------|------|------|

| Symbol                | 15                                                 | 14     | 13   | 12       | 11       | 10  | 9 | 8 | 7 | 6 | 5 | 4 | 3            | 2            | 1    | 0    |

| SE0                   | 0                                                  | 0      | 0    | 0        | 0        | 0   | 0 | 0 | 0 | 0 | 0 | 0 | SE03<br>Note | SE02<br>Note | SE01 | SE00 |

| Address: F016         | Address: F0160H, F0161H (SE1) After reset: 0000H R |        |      |          |          |     |   |   |   |   |   |   |              |              |      |      |

| Symbol                | 15                                                 | 14     | 13   | 12       | 11       | 10  | 9 | 8 | 7 | 6 | 5 | 4 | З            | 2            | 1    | 0    |

| SE1 <sup>Note 1</sup> | 0                                                  | 0      | 0    | 0        | 0        | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0            | 0            | SE11 | SE11 |

| SEmn | Indication of operation enable/disable status of channel n |

|------|------------------------------------------------------------|

| 0    | Operation is disabled (stopped)                            |

| 1    | Operation is enabled.                                      |

**Note** 30-pin product only.

**Caution** Be sure to clear bits 15 to 2 of the SE0 register for 20- or 24-pin products, bits 15 to 4 of the SE0 register for 30-pin products, and bits 15 to 2 of the SE1 register to "0".

**Remark** m: Unit number (m = 0, 1) n: Channel number (n = 0 to 3)

# (1) Register setting

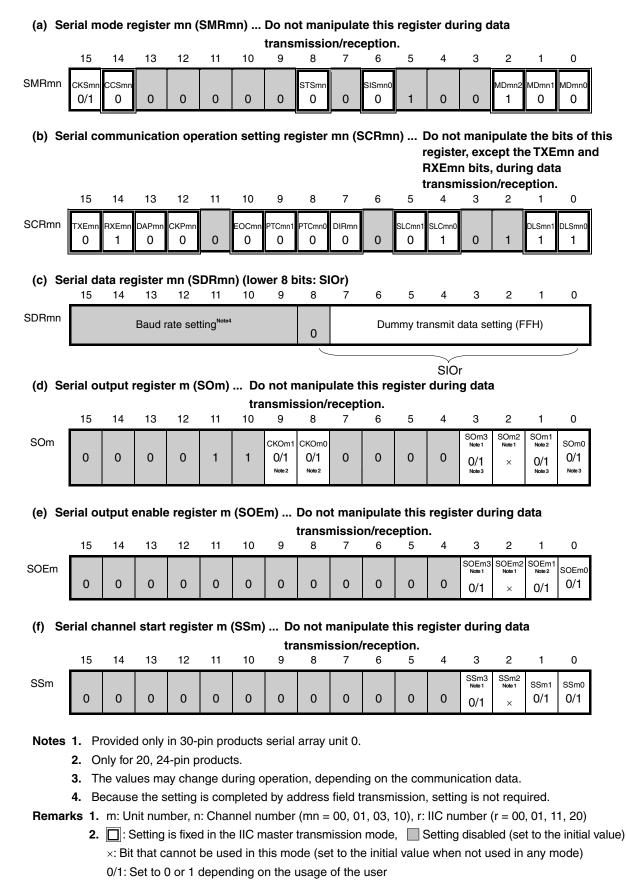

# Figure 11-41. Example of Contents of Registers for Master Transmission/Reception of 3-Wire Serial I/O (CSI00, CSI01, CSI11, CSI20) (1/2)

| (a)                                                                                                                                                                                                                                                                                                                                                                    | Seri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>ial m</b><br>15   | ode ro             | egiste<br>13         | <b>r mn (</b><br>12       | SMRr<br>11       | <b>nn)</b><br>10     | 9                   | 8            | 7                 | 6           | 5                   | 4           | 3                          | 2                             | 1                      | 0                              |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|----------------------|---------------------------|------------------|----------------------|---------------------|--------------|-------------------|-------------|---------------------|-------------|----------------------------|-------------------------------|------------------------|--------------------------------|-------|

| SMRm                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                    | CCSmn<br>0         | 0                    | 0                         | 0                | 0                    | 0                   | STSmn<br>0   | 0                 | SISmn0      | 1                   | 0           | 0                          |                               | MDmn1<br>0             | MDmn0<br>0/1                   |       |

|                                                                                                                                                                                                                                                                                                                                                                        | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Oper<br>0: Pre       | ation c<br>escaler | lock (f⊮<br>r output | іск) of c<br>t clock (    | hannel<br>CK00 s | l n<br>set by th     | ne SPS<br>ne SPS    | 0 regis      | ter               |             |                     | -           | terrupt<br>0: Ti           | source<br>ransfer<br>uffer er | of cha<br>end int      | nnel n<br>errupt               |       |

| (b)                                                                                                                                                                                                                                                                                                                                                                    | Seri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | i <b>al co</b><br>15 | <b>ommu</b><br>14  | nicati<br>13         | <b>on op</b><br>12        | eratio           | <b>n sett</b><br>10  | ing re<br>9         | gister<br>8  | <b>mn (S</b><br>7 | 6           | <b>n)</b><br>5      | 4           | 3                          | 2                             | 1                      | 0                              |       |

| SCRm                                                                                                                                                                                                                                                                                                                                                                   | nт                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XEmn I<br>1          | RXEmn<br>1         | DAPmn<br>0/1         | CKPmn<br>0/1              | 0                | EOCmn<br>0           | PTCmn1<br>0         | PTCmn0<br>0  | DIRmn<br>0/1      | 0           | SLCmn1<br>0         | SLCmn0<br>0 | 0                          | 1                             | DLSmn1<br><b>1</b>     | DLSmn0<br>0/1                  |       |

| Selection of data transfer sequence       Setting of data length         Selection of the data and clock       0: Inputs/outputs data with MSB first       0: 7-bit data length         phase (For details about the       1: Inputs/outputs data with LSB first.       1: 8-bit data length         setting, see 11.3 Registers       Controlling Serial Array Unit.) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |                    |                      |                           |                  |                      |                     |              |                   |             |                     |             |                            |                               |                        |                                |       |

| (c)                                                                                                                                                                                                                                                                                                                                                                    | Seri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | i <b>al da</b><br>15 | ata reg<br>14      | <b>gister</b><br>13  | <b>mn (S</b><br>12        | <b>DRm</b><br>11 | <b>n) (lov</b><br>10 | <b>ver 8 b</b><br>9 | oits: S<br>8 | <b>IOp)</b><br>7  | 6           | 5                   | 4           | 3                          | 2                             | 1                      | 0                              |       |

| SDRm                                                                                                                                                                                                                                                                                                                                                                   | In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | (Ope               |                      | ud rate se<br>ck (fмск) ( |                  | etting)              |                     | 0            |                   | Tra         | ansmit da           | ta setting  | /receive o                 | lata regis                    | ter                    |                                |       |

| (d)                                                                                                                                                                                                                                                                                                                                                                    | SlOp           (d) Serial output register m (SOm) Sets only the bits of the target channel.           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1         0                                                                                                                                                                                                                                                   |                      |                    |                      |                           |                  |                      |                     |              |                   |             |                     |             |                            |                               |                        |                                |       |

| Om                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                    | 0                  | 0                    | 0                         | 1                | 1                    | CKOm1<br><b>0/1</b> | скот0<br>0/1 | 0                 | 0           | 0                   | 0           | SO03<br>Note 1<br>0/1      | SO02<br>Note 1<br>×           | SO01<br>Note 2<br>0/1  | SOm0<br>0/1                    |       |

|                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                    |                      | <u>.</u>                  |                  |                      | ·                   |              | phas<br>If the    | e is nor    | n-invers<br>bhase i | sion (the   | e CKPı<br>ed (CK           | mn bit o                      | of the S               | the clock<br>CRmn =<br>mmunica | = 0). |

| (e)                                                                                                                                                                                                                                                                                                                                                                    | Seri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | i <b>al οι</b><br>15 | utput<br>14        | enable<br>13         | e regis                   | ster m           | <b>(SOE</b><br>10    | i <b>m)</b> 9       | Sets o<br>8  | only th<br>7      | e bits<br>6 | of the              | e targe     | et cha<br>3                | nnel te<br>2                  | <b>o 1.</b><br>1       | 0                              |       |

| SOEn                                                                                                                                                                                                                                                                                                                                                                   | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                    | 0                  | 0                    | 0                         | 0                | 0                    | 0                   | 0            | 0                 | 0           | 0                   | 0           | SOE03<br>Note 1<br>0/1     | SOE02<br>Note 1<br>X          | SOE01<br>Note 2<br>0/1 | SOEm0<br>0/1                   |       |

| (f)                                                                                                                                                                                                                                                                                                                                                                    | Seri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |                    |                      | -                         |                  | •                    | ) Se                |              | -                 |             |                     | -           |                            |                               |                        |                                |       |

| SSm                                                                                                                                                                                                                                                                                                                                                                    | Γ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15<br>0              | 14<br>0            | 13<br>0              | 12<br>0                   | 11<br>0          | 10<br>0              | 9                   | 8            | 7                 | 6           | 5                   | 4           | 3<br>SS03<br>Note 1<br>0/1 | 2<br>SS02<br>Note 1<br>×      | 1<br>SSm1<br>0/1       | 0<br>SSm0<br>0/1               |       |

|                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Notes 1. Provided in the serial array unit 0 of 30-pin products.</li> <li>20-, 24-pin products only.</li> <li>Remarks 1. m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), p: CSI number (p = 00, 01, 11, 20), mn = 00, 01, 03, 10</li> <li>2. : Setting is fixed in the CSI master transmission/reception mode <ul> <li>: Setting disabled (set to the initial value)</li> <li>×: Bit that cannot be used in this mode (set to the initial value when not used in any mode)</li> </ul> </li> </ul> |                      |                    |                      |                           |                  |                      |                     |              |                   |             |                     |             |                            |                               |                        |                                |       |

|                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | 0/1:8              | Set to               | 0 or 1                    | depen            | iding c              | on the u            | usage        | of the            | user        |                     |             |                            |                               |                        |                                |       |

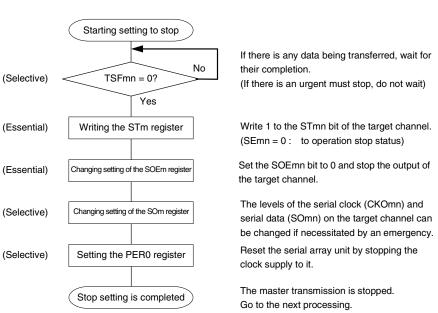

#### Figure 11-51. Procedure for Stopping Slave Transmission

Caution Be sure to set transmit data to the SIOp register before the clock from the master is started.

**Remark** <1> to <8> in the figure correspond to <1> to <8> in **Figure 11-69 Timing Chart of Slave Transmission/Reception (in Continuous Transmission/Reception Mode)**.

#### 11.5.8 Calculating transfer clock frequency

The transfer clock frequency for 3-wire serial I/O (CSI00, CSI01, CSI11, CSI20) communication can be calculated by the following expressions.

#### (1) Master

(Transfer clock frequency) = {Operation clock ( $f_{MCK}$ ) frequency of target channel} ÷ (SDRmn[15:9] + 1) ÷ 2 [Hz]

(2) Slave

| (Transfer clock frequency) = {Frequency of serial clock (SCK) supplied by master} <sup>Note</sup> | [Hz] |

|---------------------------------------------------------------------------------------------------|------|

|---------------------------------------------------------------------------------------------------|------|

- Note The permissible maximum transfer clock frequency is fmck/6.

- **Remark** The value of SDRmn[15:9] is the value of bits 15 to 9 of serial data register mn (SDRmn) (0000000B to 1111111B) and therefore is 0 to 127.

The operation clock (fMCK) is determined by serial clock select register m (SPSm) and bit 15 (CKSmn) of serial mode register mn (SMRmn).

RL78/G12

The channels supporting simplified I<sup>2</sup>C (IIC00, IIC01, IIC11, IIC20) are channels 0, 1, 3 of SAU0 and channel 0 of SAU1.

20- or 24-pin products

| Unit | Channel | Used as CSI           | Used as Simplified I <sup>2</sup> C |                       |  |  |

|------|---------|-----------------------|-------------------------------------|-----------------------|--|--|

| 0    | 0       | CSI00                 | UART0                               | IIC00 <sup>Note</sup> |  |  |

|      | 1       | CSI01 <sup>Note</sup> |                                     | IIC01 <sup>Note</sup> |  |  |

30-pin products

| Unit | Channel | Used as CSI           | Used as UART          | Used as Simplified I <sup>2</sup> C |  |  |

|------|---------|-----------------------|-----------------------|-------------------------------------|--|--|

| 0    | 0       | CSI00                 | UART0                 | IIC00 <sup>Note</sup>               |  |  |

|      | 1       | _                     |                       | _                                   |  |  |

|      | 2       | _                     | UART1 <sup>Note</sup> | _                                   |  |  |

|      | 3       | CSI11 <sup>Note</sup> |                       | IIC11 <sup>Note</sup>               |  |  |

| 1    | 0       | CSI20 <sup>Note</sup> | UART 2Note            | IIC20 <sup>Note</sup>               |  |  |

|      | 1       | _                     |                       | _                                   |  |  |

Note Provided in the R5F102 products only.

Simplified I<sup>2</sup>C (IIC00, IIC01, IIC11, IIC20) performs the following four types of communication operations.

- Address field transmission (See 11.7.1.)

- Data transmission (See 11.7.2.)

- Data reception (See 11.7.3.)

- Stop condition generation (See **11.7.4**.)

### (1) Register setting

Figure 11-105. Example of Contents of Registers for Data Reception of Simplified I<sup>2</sup>C (IIC00, IIC01, IIC11, IIC20)

# 12.6 Timing Charts

When using the I<sup>2</sup>C bus mode, the master device outputs an address via the serial bus to select one of several slave devices as its communication partner.

After outputting the slave address, the master device transmits the TRC0 bit (bit 3 of the IICA status register 0 (IICS0)), which specifies the data transfer direction, and then starts serial communication with the slave device.

Figures 12-32 and 12-33 show timing charts of the data communication.

The IICA shift register 0 (IICA0)'s shift operation is synchronized with the falling edge of the serial clock (SCLA0). The transmit data is transferred to the SO latch and is output (MSB first) via the SDAA0 pin.

Data input via the SDAA0 pin is captured into IICA0 at the rising edge of SCLA0.

#### 13.2.1 Multiplication/division data register A (MDAH, MDAL)

The MDAH and MDAL registers set the values that are used for a multiplication or division operation and store the operation result. They set the multiplier and multiplicand data in the multiplication mode or multiply-accumulator mode, and set the dividend data in the division mode. Furthermore, the operation result (quotient) is stored in the MDAH and MDAL registers in the division mode.

The MDAH and MDAL registers can be set by a 16-bit manipulation instruction.

Reset signal generation clears these registers to 0000H.

#### Figure 13-2. Format of Multiplication/Division Data Register A (MDAH, MDAL)

| Address: I | -FFF0F | I, FFFF | 1H, FF | FF2H, I | FFFF3F | - Afte | r reset: | 0000H | I, 0000H | H R/W |      |      |      |      |      |      |

|------------|--------|---------|--------|---------|--------|--------|----------|-------|----------|-------|------|------|------|------|------|------|

| Symbol     |        |         |        | FFF     | F3H    |        |          |       | FFFF2H   |       |      |      |      |      |      |      |

|            |        |         |        |         |        |        |          |       | _        |       |      |      |      |      |      |      |

|            | (      |         |        |         |        |        |          | J     |          |       |      |      |      |      |      | )    |

| MDAH       | MDAH   | MDAH    | MDAH   | MDAH    | MDAH   | MDAH   | MDAH     | MDAH  | MDAH     | MDAH  | MDAH | MDAH | MDAH | MDAH | MDAH | MDAH |

|            | 15     | 14      | 13     | 12      | 11     | 10     | 9        | 8     | 7        | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|            |        |         |        |         |        |        |          |       |          |       |      |      |      |      |      |      |

| Symbol     | FFFF1H |         |        |         |        |        |          |       | FFFF0H   |       |      |      |      |      |      |      |

|            |        |         |        |         |        |        |          |       |          |       |      |      |      |      |      |      |

|            | /      |         |        |         |        |        |          | 1     | /        |       |      |      |      |      |      | )    |

| MDAL       | MDAL   | MDAL    | MDAL   | MDAL    | MDAL   | MDAL   | MDAL     | MDAL  | MDAL     | MDAL  | MDAL | MDAL | MDAL | MDAL | MDAL | MDAL |

|            | 15     | 14      | 13     | 12      | 11     | 10     | 9        | 8     | 7        | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

- **Cautions 1.** Do not rewrite the MDAH and MDAL registers values during division operation processing (when the multiplication/division control register (MDUC) value is 81H or C1H). The operation will be executed in this case, but the operation result will be an undefined value.

- 2. The MDAH and MDAL registers values read during division operation processing (when the MDUC register value is 81H or C1H) will not be guaranteed.

- **3.** The data is in the two's complement format in either the multiplication mode (signed) or multiplyaccumulator mode (signed).

The following table shows the functions of the MDAH and MDAL registers during operation execution.

| Table 12-2  | Functions of MDAH and MI  | <b>DAL Bogistore Duri</b> | a Operation Execution  |

|-------------|---------------------------|---------------------------|------------------------|

| Table 13-2. | FUNCTIONS OF MDATI and MI | JAL REGISTERS DUIT        | ig Operation Execution |

| Operation Mode                       | Setting                       | Operation Result                            |

|--------------------------------------|-------------------------------|---------------------------------------------|

| Multiplication mode (unsigned)       | MDAH: Multiplier (unsigned)   | _                                           |

| Multiply-accumulator mode (unsigned) | MDAL: Multiplicand (unsigned) |                                             |

| Multiplication mode (signed)         | MDAH: Multiplier (signed)     | -                                           |

| Multiply-accumulator mode (signed)   | MDAL: Multiplicand (signed)   |                                             |

| Division mode (unsigned)             | MDAH: Dividend (unsigned)     | MDAH: Division result (quotient) (unsigned) |

|                                      | (higher 16 bits)              | Higher 16 bits                              |

|                                      | MDAL: Dividend (unsigned)     | MDAL: Division result (quotient) (unsigned) |

|                                      | (lower 16 bits)               | Lower 16 bits                               |

#### Address: F00E8H After reset: 00H R/WNote 1 Symbol <6> 5 <2> <7> 4 <3> <1> <0> MDUC DIVMODE MACMODE 0 0 MDSM MACOF MACSF DIVST

Figure 13-5. Format of Multiplication/Division Control Register (MDUC)

| DIVMODE | MACMODE        | MDSM | Operation mode selection                                                            |

|---------|----------------|------|-------------------------------------------------------------------------------------|

| 0       | 0              | 0    | Multiplication mode (unsigned) (default)                                            |

| 0       | 0              | 1    | Multiplication mode (signed)                                                        |

| 0       | 1              | 0    | Multiply-accumulator mode (unsigned)                                                |

| 0       | 1              | 1    | Multiply-accumulator mode (signed)                                                  |

| 1       | 0              | 0    | Division mode (unsigned), generation of a division completion interrupt (INTMD)     |

| 1       | 1              | 0    | Division mode (unsigned), not generation of a division completion interrupt (INTMD) |

| 0       | ther than abov | /e   | Setting prohibited                                                                  |

| MACOF | Overflow flag of multiply-accumulation result (accumulated value) |

|-------|-------------------------------------------------------------------|

| 0     | No overflow                                                       |

| 1     | With over flow                                                    |

<Set condition>

• For the multiply-accumulator mode (unsigned)

The bit is set when the accumulated value goes outside the range from 00000000h to FFFFFFFh.

• For the multiply-accumulator mode (signed)

The bit is set when the result of adding a positive product to a positive accumulated value exceeds 7FFFFFFh and is negative, or when the result of adding a negative product to a negative accumulated value exceeds 80000000h and is positive.

| MACSF                                 | Sign flag of multiply-accumulation result (accumulated value) |                                                          |  |  |

|---------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|--|--|

| 0                                     | The accumulated value is positive.                            |                                                          |  |  |

| 1                                     | The accumulated value is                                      | negative.                                                |  |  |

| Multiply-accumulator mode (unsigned): |                                                               | The bit is always 0.                                     |  |  |

| Multiply-accumulator mode (signed):   |                                                               | The bit indicates the sign bit of the accumulated value. |  |  |

| DIVST <sup>Note 2</sup> Division operation start/stop                 |                                        |

|-----------------------------------------------------------------------|----------------------------------------|

| 0                                                                     | Division operation processing complete |

| 1 Starts division operation/division operation processing in progress |                                        |

Notes 1. Bits 1 and 2 are read-only bits.

- 2. The DIVST bit can only be set (1) in the division mode. In the division mode, division operation is started by setting (1) the DIVST bit. The DIVST bit is automatically cleared (0) when the operation ends. In the multiplication mode, operation is automatically started by setting the multiplier and multiplicand to multiplication/division data register A (MDAH, MDAL), respectively.

- **Cautions 1.** Do not rewrite the DIVMODE, MDSM bits during operation processing (while the DIVST bit is 1). If it is rewritten, the operation result will be an undefined value.

- **2.** The DIVST bit cannot be cleared (0) by using software during division operation processing (while the DIVST bit is 1).

#### 13.4.4 Multiply-accumulation (signed) operation

- · Initial setting

- <1> Set the multiplication/division control register (MDUC) to 48H.

- <2> Set the initial accumulated value of higher 16 bits to multiplication/division data register C (H) (MDCH). (<3> If the accumulated value in the MDCH register is negative, the MACSF bit is set to 1.)

- <4> Set the initial accumulated value of lower 16 bits to multiplication/division data register C (L) (MDCL).

- <5> Set the multiplicand to multiplication/division data register A (L) (MDAL).

- <6> Set the multiplier to multiplication/division data register A (H) (MDAH). (There is no preference in the order of executing steps <2>, <4>, and <5>. Multiplication operation is automatically started when the multiplier is set to the MDAH register of <6>, respectively.)

- During operation processing

- <7> The multiplication operation finishes in one clock cycle.

(The multiplication result is stored in multiplication/division data register B (L) (MDBL) and multiplication/division data register B (H) (MDBH).)

- <8> After <7>, the multiply-accumulation operation finishes in one additional clock cycle. (There is a wait of at least two clock cycles after specifying the initial settings is finished (<6>).)

- Operation end

- <9> If the accumulated value stored in the MDCL and MDCH registers is positive, the MACSF bit is cleared to 0.

- <10> Read the accumulated value (lower 16 bits) from the MDCL register.

- <11> Read the accumulated value (higher 16 bits) from the MDCH register.

- (There is no preference in the order of executing steps <10> and <11>.)

- (<12> If the result of the multiply-accumulation operation causes an overflow, the MACOF bit is set to 1, INTMD signal is occurred.)

- Next operation

- <13> Start with the initial settings of each step to change the operation mode. When the same operation mode is used sequentially, settings <1> and <5> can be omitted.

- Caution The data is in the two's complement format in multiply-accumulation (signed) operation.

Remark Steps <1> to <12> correspond to <1> to <12> in Figure 13-9.

| Instruction | Mnemonic | Operands        | Bytes | Clocks |        | Clocks                                       |   | Flag | lag |  |

|-------------|----------|-----------------|-------|--------|--------|----------------------------------------------|---|------|-----|--|

| Group       |          |                 |       | Note 1 | Note 2 |                                              | z | AC   | CY  |  |

| 8-bit       | SUBC     | A, #byte        | 2     | 1      | -      | A, CY $\leftarrow$ A – byte – CY             | × | ×    | ×   |  |

| operation   |          | saddr, #byte    | 3     | 2      | -      | (saddr), CY $\leftarrow$ (saddr) – byte – CY | × | ×    | ×   |  |

|             |          | A, r            | 2     | 1      | -      | A, CY $\leftarrow$ A – r – CY                | × | ×    | ×   |  |

|             |          | r, A            | 2     | 1      | -      | $r, CY \leftarrow r - A - CY$                | × | ×    | ×   |  |

|             |          | A, !addr16      | 3     | 1      | 4      | A, CY $\leftarrow$ A – (addr16) – CY         | × | ×    | ×   |  |

|             |          | A, ES:!addr16   | 4     | 2      | 5      | A, CY $\leftarrow$ A – (ES, addr16) – CY     | × | ×    | ×   |  |

|             |          | A, saddr        | 2     | 1      | _      | A, CY $\leftarrow$ A – (saddr) – CY          | × | ×    | ×   |  |

|             |          | A, [HL]         | 1     | 1      | 4      | A, CY $\leftarrow$ A – (HL) – CY             | × | ×    | ×   |  |

|             |          | A, ES:[HL]      | 2     | 2      | 5      | A,CY ← A − (ES, HL) − CY                     | × | ×    | ×   |  |

|             |          | A, [HL+byte]    | 2     | 1      | 4      | A, CY $\leftarrow$ A – (HL+byte) – CY        | × | ×    | ×   |  |

|             |          | A, ES:[HL+byte] | 3     | 2      | 5      | $A,CY \leftarrow A - ((ES, HL)+byte) - CY$   | × | ×    | ×   |  |

|             |          | A, [HL+B]       | 2     | 1      | 4      | A, CY $\leftarrow$ A – (HL+B) – CY           | × | ×    | ×   |  |

|             |          | A, ES:[HL+B]    | 3     | 2      | 5      | $A,CY \leftarrow A - ((ES, HL)+B) - CY$      | × | ×    | ×   |  |

|             |          | A, [HL+C]       | 2     | 1      | 4      | A, CY $\leftarrow$ A – (HL+C) – CY           | × | ×    | ×   |  |

|             |          | A, ES:[HL+C]    | 3     | 2      | 5      | A, CY $\leftarrow$ A – ((ES:HL)+C) – CY      | × | ×    | ×   |  |

|             | AND      | A, #byte        | 2     | 1      | -      | $A \leftarrow A \land byte$                  | × |      |     |  |

|             |          | saddr, #byte    | 3     | 2      | -      | $(saddr) \leftarrow (saddr) \land byte$      | × |      |     |  |

|             |          | A, r            | 2     | 1      | -      | $A \leftarrow A \wedge r$                    | × |      |     |  |

|             |          | r, A            | 2     | 1      | -      | R ← r ∧ A                                    | × |      |     |  |

|             |          | A, !addr16      | 3     | 1      | 4      | $A \leftarrow A \land (addr16)$              | × |      |     |  |

|             |          | A, ES:!addr16   | 4     | 2      | 5      | $A \leftarrow A \land (ES:addr16)$           | × |      |     |  |

|             |          | A, saddr        | 2     | 1      | _      | $A \leftarrow A \land (saddr)$               | × |      |     |  |

|             |          | A, [HL]         | 1     | 1      | 4      | $A \leftarrow A \land (HL)$                  | × |      |     |  |

|             |          | A, ES:[HL]      | 2     | 2      | 5      | $A \leftarrow A \land (ES:HL)$               | × |      |     |  |

|             |          | A, [HL+byte]    | 2     | 1      | 4      | $A \leftarrow A \land (HL+byte)$             | × |      |     |  |

|             |          | A, ES:[HL+byte] | 3     | 2      | 5      | $A \leftarrow A \land ((ES:HL)+byte)$        | × |      |     |  |

|             |          | A, [HL+B]       | 2     | 1      | 4      | $A \leftarrow A \land (HL{+}B)$              | × |      |     |  |

|             |          | A, ES:[HL+B]    | 3     | 2      | 5      | $A \leftarrow A \land ((ES:HL){+}B)$         | × |      |     |  |

|             |          | A, [HL+C]       | 2     | 1      | 4      | $A \leftarrow A \land (HL{+}C)$              | × |      |     |  |

|             |          | A, ES:[HL+C]    | 3     | 2      | 5      | $A \leftarrow A \land ((ES:HL)+C)$           | × |      |     |  |

Table 27-5. Operation List (8/17)

**Notes 1.** Number of CPU clocks (fcLK) when the internal RAM area, SFR area, or extended SFR area is accessed, or when no data is accessed.

2. Number of CPU clocks (fcLK) when the code flash memory is accessed, or when the data flash memory is accessed by an 8-bit instruction.

<sup>3.</sup> Except r = A

**Remark** Number of clock is when program exists in the internal ROM (flash memory) area. If fetching the instruction from the internal RAM area, the number becomes double number plus 3 clocks at a maximum.

# (3) When reference voltage (+) = V<sub>DD</sub> (ADREFP1 = 0, ADREFP0 = 0), reference voltage (−) = V<sub>ss</sub> (ADREFM = 0), target pin: ANI0 to ANI3, ANI16 to ANI22, internal reference voltage, and temperature sensor output voltage

| Parameter                                  | Symbol                                           | Condition                                                                        | ns                                  | MIN.   | TYP.                      | MAX.  | Unit |

|--------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------|--------|---------------------------|-------|------|

| Resolution                                 | Res                                              |                                                                                  |                                     | 8      |                           | 10    | bit  |

| Overall error <sup>Note 1</sup>            | AINL                                             | 10-bit resolution                                                                |                                     |        | 1.2                       | ±7.0  | LSB  |

| Conversion time                            | <b>t</b> CONV                                    | 10-bit resolution                                                                | $3.6~V \leq V \text{DD} \leq 5.5~V$ | 2.125  |                           | 39    | μS   |

|                                            |                                                  | Target pin: ANI0 to ANI3,                                                        | $2.7~V \leq V\text{DD} \leq 5.5~V$  | 3.1875 |                           | 39    | μS   |

|                                            |                                                  | ANI16 to ANI22                                                                   | $2.4~V \leq V \text{DD} \leq 5.5~V$ | 17     |                           | 39    | μs   |

| Conversion time                            | tconv                                            | 10-bit resolution                                                                | $3.6~V \leq V \text{DD} \leq 5.5~V$ | 2.375  |                           | 39    | μs   |

|                                            |                                                  | Target pin: internal reference                                                   | $2.7~V \leq V \text{DD} \leq 5.5~V$ | 3.5625 |                           | 39    | μs   |

|                                            | sensor output vo                                 | voltage, and temperature<br>sensor output voltage (HS<br>(high-speed main) mode) | $2.4~V \le V_{DD} \le 5.5~V$        | 17     |                           | 39    | μs   |

| Zero-scale error <sup>Notes 1, 2</sup>     | EZS                                              | 10-bit resolution                                                                | I                                   |        |                           | ±0.60 | %FSR |

| Full-scale error <sup>Notes 1, 2</sup>     | EFS                                              | 10-bit resolution                                                                |                                     |        |                           | ±0.60 | %FSR |

| Integral linearity error <sup>Note 1</sup> | ILE                                              | 10-bit resolution                                                                |                                     |        |                           | ±4.0  | LSB  |

| Differential linearity error Note 1        | DLE                                              | 10-bit resolution                                                                |                                     |        |                           | ±2.0  | LSB  |

| Analog input voltage                       | Analog input voltage VAIN ANIO to ANI3, ANI16 to |                                                                                  | 2                                   | 0      |                           | VDD   | V    |

|                                            |                                                  | Internal reference voltage<br>(HS (high-speed main) mode)                        |                                     |        | VBGR Note 3               |       | V    |

|                                            |                                                  | Temperature sensor output voltage<br>(HS (high-speed main) mode)                 |                                     |        | VTMPS25 <sup>Note 3</sup> | •     | V    |

|                                          |               | Defense of the set (1) 1/            | Defense and the set ( ) V )  |  |

|------------------------------------------|---------------|--------------------------------------|------------------------------|--|

| (TA = −40 to +105°C, 2.4 V ≤ VDD ≤ 5.5 V | ', vss = u v, | , Reference voltage $(+) = v_{DD}$ , | Reference voltage (–) = vss) |  |

**Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

2. This value is indicated as a ratio (%FSR) to the full-scale value.

3. Refer to 29.6.2 Temperature sensor/internal reference voltage characteristics.

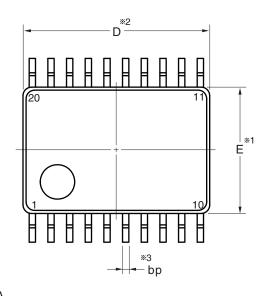

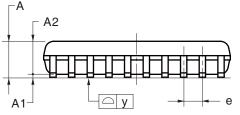

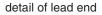

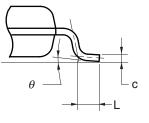

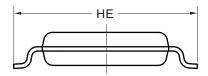

# CHAPTER 30 PACKAGE DRAWINGS

### 30.1 20-pin products

RL78/G12

R5F1026AASP, R5F10269ASP, R5F10268ASP, R5F10267ASP, R5F10266ASP R5F1036AASP, R5F10369ASP, R5F10368ASP, R5F10367ASP, R5F10366ASP R5F1026ADSP, R5F10269DSP, R5F10268DSP, R5F10267DSP, R5F10266DSP R5F1036ADSP, R5F10369DSP, R5F10368DSP, R5F10367DSP, R5F10366DSP R5F1026AGSP, R5F10269GSP, R5F10268GSP, R5F10267GSP, R5F10266GSP

| JEITA Package Code     | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|------------------------|--------------|----------------|-----------------|

| P-LSSOP20-4.4x6.5-0.65 | PLSP0020JB-A | P20MA-65-NAA-1 | 0.1             |

1.Dimensions "%1" and "%2" do not include mold flash.

2.Dimension "3" does not include trim offset.

|      | (UNIT:mm)              |

|------|------------------------|

| ITEM | DIMENSIONS             |

| D    | 6.50±0.10              |

| Е    | 4.40±0.10              |

| HE   | 6.40±0.20              |

| Α    | 1.45 MAX.              |

| A1   | 0.10±0.10              |

| A2   | 1.15                   |

| е    | 0.65±0.12              |

| bp   | 0.22 + 0.10 - 0.05     |

| С    | $0.15 \pm 0.05 - 0.02$ |

| L    | 0.50±0.20              |

| У    | 0.10                   |

| θ    | 0° to 10°              |

|      |                        |

© 2012 Renesas Electronics Corporation. All rights reserved.

NOTE

RL78/G12 User's Manual: Hardware

Publication Date: Rev.2.10 Mar 25, 2016

Published by: Renesas Electronics Corporation