Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 14                                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 768 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | 20-LSSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10268dsp-x0 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2.2 Description of Functions

| Function Name                | I/O    | Functions                                                                                                                                 |

|------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| ANI0 to ANI3, ANI16 to ANI22 | input  | Analog input pins of A/D converter                                                                                                        |

|                              |        | (see Figure 10-44 Analog Input Pin Connection)                                                                                            |

| AVREFP                       | input  | Inputs the A/D converter reference potential (+ side)                                                                                     |

| AVREFM                       | input  | Inputs the A/D converter reference potential (- side)                                                                                     |

| INTP0 to INTP5               | input  | External interrupt request input                                                                                                          |

|                              |        | Specified available edge : rising edge, falling edge, or both rising and falling edges                                                    |

| KR0 to KR9                   | input  | Key interrupt input                                                                                                                       |

| PCLBUZ0, PCLBUZ1             | output | Clock/buzzer output                                                                                                                       |

| REGC                         | _      | Connecting regulator output stabilization capacitance for internal operation. Connect this pin to Vss via a capacitor (0.47 to 1 $\mu$ F) |

| RESET                        | input  | External reset input for low level active                                                                                                 |

|                              |        | When the external reset pin is not used, connect this pin directly or via a resistor to $V_{\text{DD}}$ .                                 |

| RxD0 to RxD2                 | input  | Serial data input for serial interfaces UART0, UART1, and UART2                                                                           |

| TxD0 to TxD2                 | output | Serial data output for serial interfaces UART0, UART1, and UART2                                                                          |

| SCK00, SCK01, SCK11, SCK20   | I/O    | Serial clock I/O for serial interfaces CSI00, CSI01, CSI11, and CSI20                                                                     |

| SI00, SI01, SI11, SI20       | input  | Serial data input for serial interfaces CSI00, CSI01, CSI11, and CSI20                                                                    |

| SO00, SO01, SO11, SO20       | output | Serial data output for serial interfaces CSI00, CSI01, CSI11, and CSI20                                                                   |

| SCLA0                        | I/O    | Serial clock I/O for serial interface IICA                                                                                                |

| SDAA0                        | I/O    | Serial data I/O for serial interface IICA                                                                                                 |

| SCL00, SCL01, SCL11, SCL20   | output | Clock output for simplified I <sup>2</sup> C serial interfaces IIC00, IIC01, IIC11, IIC20                                                 |

| SDA00, SDA01, SDA11, SDA20   | I/O    | Serial data I/O for simplified I <sup>2</sup> C serial interfaces IIC00, IIC01, IIC11, IIC20                                              |

| TI00 to TI07                 | input  | Inputting an external count clock/capture trigger to 16-bit timers 00 to 07                                                               |

| TO00 to TO07                 | output | Timer output pins of 16-bit timers 00 to 07                                                                                               |

| X1, X2                       | -      | Connecting a resonator for main system clock                                                                                              |

| EXCLK                        | input  | External clock input pin for main system clock                                                                                            |

| Vdd                          | -      | Positive power supply                                                                                                                     |

| Vss                          | -      | Ground potential                                                                                                                          |

| TOOLRxD                      | input  | This UART serial data input pin for an external device connection is used during flash<br>memory programming                              |

| TOOLTxD                      | output | This UART serial data output pin for an external device connection is used during flash memory programming                                |

| TOOL0                        | I/O    | Data I/O pin for a flash memory programmer/debugger                                                                                       |

Caution The following shows the relationship between P40/TOOL0 and the operation mode when reset is released.

# Table 2-1. Relationship between P40/TOOL0 and the Operation Mode When Reset Is Released

| P40/TOOL0 | Operation mode                |

|-----------|-------------------------------|

| Vdd       | Normal operation mode         |

| 0 V       | Flash memory programming mode |

For details, see 24.4 Serial Programming Method.

**Remark** Use bypass capacitors (about 0.1  $\mu$ F) as noise and latch up countermeasures with relatively thick wires at the shortest distance to V<sub>DD</sub> to V<sub>SS</sub> lines.

#### 5.3.3 Clock operation status control register (CSC)

This register is used to control the operations of the high-speed system clock and high-speed on-chip oscillator clock, (except the low-speed on-chip oscillator clock).

The CSC register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to C0H.

#### Figure 5-4. Format of Clock Operation Status Control Register (CSC)

Address: FFFA1H After reset: C0H R/W

<R>

| Symbol | <7>   | 6 | 5 | 4 | 3 | 2 | 1 | <0>     |

|--------|-------|---|---|---|---|---|---|---------|

| CSC    | MSTOP | 1 | 0 | 0 | 0 | 0 | 0 | HIOSTOP |

| MSTOP | High-speed system clock operation control |                                          |                 |  |  |  |  |

|-------|-------------------------------------------|------------------------------------------|-----------------|--|--|--|--|

|       | X1 oscillation mode                       | External clock input mode                | Input port mode |  |  |  |  |

| 0     | X1 oscillator operating                   | External clock from EXCLK pin is valid   | Input port      |  |  |  |  |

| 1     | X1 oscillator stopped                     | External clock from EXCLK pin is invalid |                 |  |  |  |  |

| HIOSTOP | High-speed on-chip oscillator clock operation control |

|---------|-------------------------------------------------------|

| 0       | High-speed on-chip oscillator operating               |

| 1       | High-speed on-chip oscillator stopped                 |

Cautions 1. After reset release, set the clock operation mode control register (CMC) before setting the CSC register.

- 2. Set the oscillation stabilization time select register (OSTS) before setting the MSTOP bit to 0 after releasing reset. Note that if the OSTS register is being used with its default settings, the OSTS register is not required to be set here.

- 3. To start X1 oscillation as set by the MSTOP bit, check the oscillation stabilization time of the X1 clock by using the oscillation stabilization time counter status register (OSTC).

- 4. Do not stop the clock selected for the CPU peripheral hardware clock (fcLK) with the CSC register.

- 5. The setting of the flags of the register to stop clock oscillation (invalidate the external clock input) and the condition before clock oscillation is to be stopped are as Table 5-2. Before stopping the clock oscillation, check the conditions before the clock oscillation is stopped.

| Clock                                     | Condition Before Stopping Clock<br>(Invalidating External Clock Input)                               | Setting of CSC<br>Register Flags |

|-------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------|

| X1 clock<br>External main system<br>clock | CPU and peripheral hardware clocks operate with a high-<br>speed on-chip oscillator clock. (MCS = 0) | MSTOP = 1                        |

| High-speed on-chip<br>oscillator clock    | CPU and peripheral hardware clocks operate with a high-<br>speed system clock.(MCS = 1)              | HIOSTOP = 1                      |

# Example

### Figure 6-40. Example of Set Contents of Registers During Operation as Interval Timer/Square Wave Output (2/2)

#### (d) Timer output level register 0 (TOL0) Bit n

0

TOM0n

0

0: Cleared to 0 when master channel output mode (TOMOn = 0)

#### (e) Timer output mode register 0 (TOM0) Bit n

TOM0

0: Sets master channel output mode.

**Remark** n: Channel number (n = 0 to 7)

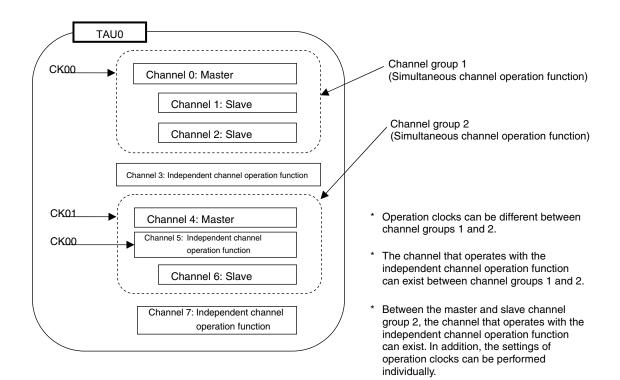

# Figure 6-51. Example of Basic Timing of Operation as Input Pulse Interval Measurement (MD0n0 = 0)

**Remarks 1.** n: Channel number (n = 0 to 7)

**2.** TS0n: Bit n of timer channel start register 0 (TS0)

- TE0n: Bit n of timer channel enable status register 0 (TE0)

- TIOn: TIOn pin input signal

TCR0n: Timer count register 0n (TCR0n)

TDR0n: Timer data register 0n (TDR0n)

OVF: Bit 0 of timer status register 0n (TSR0n)

| _   |        |        |       |      |             |                 |                         |                    |                       |                       |                    |                       |                   |                    |

|-----|--------|--------|-------|------|-------------|-----------------|-------------------------|--------------------|-----------------------|-----------------------|--------------------|-----------------------|-------------------|--------------------|

|     |        |        |       |      | Mode        | Conversion      | Number of<br>Conversion | Conversion<br>Time |                       | Conv                  |                    | e at 10-Bit F         |                   |                    |

|     | Regist | 0 (1   |       | )    |             | Clock (fad)     |                         | Time               |                       |                       | 2.7 V <u>s</u>     | ≤ Vdd ≤ 5.5 \         | /                 |                    |

| FR2 | FR1    | FR0    | LV1   | LV0  |             |                 | Clock Note              |                    | fclк=<br>1 MHz        | fclк=<br>2 MHz        | fclк=<br>4 MHz     | fc∟k =<br>8 MHz       | fc∟к =<br>16 MHz  | fclk=<br>24 MHz    |

| 0   | 0      | 0      | 0     | 0    | Normal<br>1 | fclк/ <b>64</b> | 19 fad<br>(number of    | 1216/fclк          | Setting prohibited    | Setting<br>prohibited | Setting prohibited | Setting<br>prohibited | 76 <i>μ</i> s     | 50.67 <i>µ</i> s   |

| 0   | 0      | 1      |       |      |             | fclк/32         | sampling                | 608/fclк           |                       |                       |                    | 76 <i>μ</i> s         | 38 <i>µ</i> s     | 25.33 <i>µ</i> s   |

| 0   | 1      | 0      |       |      |             | fclк/16         | clock: 7 fad)           | <b>304/f</b> ськ   |                       |                       | 76 <i>μ</i> s      | 38 <i>µ</i> s         | 19 <i>µ</i> s     | 12.67 <i>μ</i> s   |

| 0   | 1      | 1      |       |      |             | fclk/8          |                         | 152/fclк           |                       | 76 <i>μ</i> s         | 38 <i>µ</i> s      | 19 <i>μ</i> s         | 9.5 <i>μ</i> s    | 6.33 <i>μ</i> s    |

| 1   | 0      | 0      |       |      |             | fclк/6          |                         | 114/fclк           |                       | 57 <i>μ</i> s         | 28.5 <i>μ</i> s    | 14.25 <i>μ</i> s      | 7.125 <i>μ</i> s  | 4.75 <i>μ</i> s    |

| 1   | 0      | 1      |       |      |             | fclк/5          |                         | 95/fclк            | 95 <i>μ</i> s         | 47.5 μs               | 23.75 <i>µ</i> s   | 11.875 <i>µ</i> s     | 5.938 <i>μ</i> s  | 3.96 <i>µ</i> s    |

| 1   | 1      | 0      |       |      |             | fс∟к/4          |                         | <b>76/f</b> ськ    | 76 <i>μ</i> s         | 38 <i>µ</i> s         | 19 <i>μ</i> s      | 9.5 <i>μ</i> s        | 4.75 <i>μ</i> s   | 3.17 <i>μ</i> s    |

| 1   | 1      | 1      |       |      |             | fclк/2          |                         | <b>38/f</b> ськ    | 38 <i>µ</i> s         | 19 <i>μ</i> s         | 9.5 <i>µ</i> s     | 4.75 <i>μ</i> s       | 2.375 <i>µ</i> s  | Setting prohibited |

| 0   | 0      | 0      | 0     | 1    | Normal<br>2 | fclк/ <b>64</b> | 17 fad<br>(number of    | 1088/fclк          | Setting<br>prohibited | Setting prohibited    | Setting prohibited | Setting<br>prohibited | 68 <i>µ</i> s     | 45.33 <i>µ</i> s   |

| 0   | 0      | 1      |       |      |             | fclк/ <b>32</b> | sampling                | 544/fclк           |                       |                       |                    | 68 <i>µ</i> s         | 34 <i>µ</i> s     | 22.67 <i>μ</i> s   |

| 0   | 1      | 0      |       |      |             | fclк/16         | clock: 5 fad)           | 272/fclк           |                       |                       | 68 <i>µ</i> s      | 34 <i>µ</i> s         | 17 <i>μ</i> s     | 11.33 <i>μ</i> s   |

| 0   | 1      | 1      |       |      |             | fclk/8          |                         | 136/fclк           |                       | 68 <i>μ</i> s         | 34 <i>µ</i> s      | 17 <i>μ</i> s         | 8.5 <i>μ</i> s    | 5.67 <i>μ</i> s    |

| 1   | 0      | 0      |       |      |             | fclк/6          |                         | 102/fclк           |                       | 51 <i>μ</i> s         | 25.5 <i>μ</i> s    | 12.75 <i>μ</i> s      | 6.375 <i>μ</i> s  | 4.25 <i>μ</i> s    |

| 1   | 0      | 1      |       |      |             | fclк/5          |                         | <b>85/f</b> ськ    | 85 <i>μ</i> s         | 42.5 <i>μ</i> s       | 21.25 <i>µ</i> s   | 10.625 <i>μ</i> s     | 5.3125 <i>μ</i> s | 3.54 <i>μ</i> s    |

| 1   | 1      | 0      |       |      |             | fс∟к/4          |                         | <b>68/f</b> ськ    | 68 <i>µ</i> s         | 34 <i>µ</i> s         | 17 <i>μ</i> s      | 8.5 <i>μ</i> s        | 4.25 <i>μ</i> s   | 2.83 <i>µ</i> s    |

| 1   | 1      | 1      |       |      |             | fс∟к/2          |                         | <b>34/f</b> с∟к    | 34 <i>μ</i> s         | 17 <i>μ</i> s         | 8.5 <i>µ</i> s     | 4.25 <i>μ</i> s       | 2.125 <i>µ</i> s  | Setting prohibited |

|     | Oth    | er tha | n the | abov | 'e          | -               | -                       | -                  | Setting p             | orohibited            |                    |                       |                   |                    |

# Table 10-3. A/D Conversion Time Selection (1/4)

(1) When there is no A/D power supply stabilization wait time Normal mode 1 or 2 (software trigger mode/hardware trigger no-wait mode)

**Note** These are the numbers of clock cycles when conversion is with 10-bit resolution. When eight-bit resolution is selected, the values are shorter by two cycles of the conversion clock (f<sub>AD</sub>).

- **Cautions 1.** The A/D conversion time must be within the range of conversion times (tconv) described in 28.6.1 A/D converter characteristics or 29.6.1 A/D converter characteristics.

- When rewriting the FR2 to FR0, LV1, and LV0 bits to other than the current data, stop A/D conversion once (ADCS = 0, ADCE = 0) beforehand.

- **3.** The above conversion time does not include conversion state time. Conversion state time add in the first conversion. Select conversion time, taking clock frequency errors into consideration.

Remark fclk: CPU/peripheral hardware clock frequency

# 10.3.3 A/D converter mode register 1 (ADM1)

This register is used to specify the A/D conversion trigger, conversion mode, and hardware trigger signal. The ADM1 register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

# Figure 10-6. Format of A/D Converter Mode Register 1 (ADM1)

| Address: FFF32H After reset: 00H |        | R/W    |       |   |   |   |        |        |

|----------------------------------|--------|--------|-------|---|---|---|--------|--------|

| Symbol                           | 7      | 6      | 5     | 4 | 3 | 2 | 1      | 0      |

| ADM1                             | ADTMD1 | ADTMD0 | ADCSM | 0 | 0 | 0 | ADTRS1 | ADTRS0 |

| ADTMD1 | ADTMD0 | Selection of the A/D conversion trigger mode |

|--------|--------|----------------------------------------------|

| 0      | ×      | Software trigger mode                        |

| 1      | 0      | Hardware trigger no- wait mode               |

| 1      | 1      | Hardware trigger wait mode                   |

| ADSCM | Specification of the A/D conversion mode |

|-------|------------------------------------------|

| 0     | Sequential conversion mode               |

| 1     | One-shot conversion mode                 |

| ADTRS1    | ADTRS0   | Selection of the hardware trigger signal                                              |

|-----------|----------|---------------------------------------------------------------------------------------|

| 0         | 0        | Count completion of timer channel 01 or capture completion interrupt signal (INTTM01) |

| 1         | 1        | 12-bit interval timer interrupt signal (INTIT)                                        |

| Other the | an above | Setting prohibited                                                                    |

**Cautions 1.** Only rewrite the value of the ADM1 register while conversion is stopped (ADCS = 0, ADCE = 0).

2. To complete A/D conversion, specify at least the following values as the hardware trigger interval:

Hardware trigger no-wait mode: 2 fcL $\kappa$  clock + conversion start time + A/D conversion time Hardware trigger wait mode: 2 fcL $\kappa$  clock + conversion start time + A/D power supply stabilization wait time + A/D conversion time

3. In modes other than SNOOZE mode, input of the next INTIT will not be recognized as a valid hardware trigger for up to four fclk cycles after the first INTIT is input.

Remarks 1. ×: don't care

2. fclk: CPU/peripheral hardware clock frequency

# Figure 11-6. Format of Peripheral Enable Register 0 (PER0)

| Address: F00 | -0H After re | eset: 00H R/V                                | V     |                                   |                                |              |   |        |

|--------------|--------------|----------------------------------------------|-------|-----------------------------------|--------------------------------|--------------|---|--------|

| Symbol       | <7>          | 6                                            | <5>   | <4>                               | <3>                            | <2>          | 1 | <0>    |

| PER0         | TMKAEN       | 0                                            | ADCEN | IICA0EN                           | SAU1EN <sup>Note</sup>         | SAU0EN       | 0 | TAU0EN |

|              |              |                                              |       |                                   |                                |              |   |        |

|              | SAU1EN       |                                              |       | Control of se                     | erial array unit 1             | clock supply |   |        |

|              | 0            | SFR used b                                   |       | unit 1 cannot b                   | 4-pin products).<br>e written. |              |   |        |

|              | 1            | Enables clock <ul> <li>SFR used b</li> </ul> |       | unit 1 can be re                  | ead/written.                   |              |   |        |

|              | 0.4110511    |                                              |       | O a start of a                    | vial annu 110                  |              |   |        |

|              | SAU0EN       |                                              |       | Control of se                     | erial array unit 0             | CIOCK SUPPIY |   |        |

|              | 0            |                                              |       | unit 0 cannot be<br>reset status. | e written.                     |              |   |        |

|              | 1            | Enables clock <ul> <li>SFR used b</li> </ul> |       | unit 0 can be re                  | ad/written.                    |              |   |        |

Note 30-pin products only.

- Cautions 1. When setting serial array unit m, be sure to first set the following registers with the SAUMEN bit set to 1. If SAUMEN = 0, control registers of serial array unit m become default values and writing to them is ignored (except for the noise filter enable register 0 (NFEN0), port input mode registers 0, 1 (PIM0, PIM1), port output mode registers 0, 1, 4, 5 (POM0, POM1, POM4, POM5), port mode control registers 0, 1, 4 (PMC0, PMC1, PMC4), port mode registers 0, 1, 3 to 6 (PM0, PM1, PM3 to PM6), and port registers 0, 1, 3 to 6 (P0, P1, P3 to P6)).

- Serial clock select register m (SPSm)

- Serial mode register mn (SMRmn)

- Serial communication operation setting register mn (SCRmn)

- Serial data register mn (SDRmn)

- Serial flag clear trigger register mn (SIRmn)

- Serial status register mn (SSRmn)

- Serial channel start register m (SSm)

- Serial channel stop register m (STm)

- Serial channel enable status register m (SEm)

- Serial output enable register m (SOEm)

- Serial output level register m (SOLm)

- Serial output register m (SOm)

- Serial standby control register m (SSCm)

- **2.** Be sure to clear the following bits to 0.

- 20, 24-pin products: bits 1, 3, 6 30-pin products: bits 1, 6

|             | •                                         | <b>c</b>                                                                                                                                   |

|-------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|             | Starting setting for resumption           |                                                                                                                                            |

| (Essential) | Completing slave No preparations?         | Wait until stop the communication target<br>(slave) or communication operation<br>completed                                                |

| (Essential) | Yes<br>Port manipulation                  | Disable clock output of the target channel by setting a port register and a port mode register.                                            |

| (Selective) | Changing setting of the<br>SPSm register  | Re-set the register to change the operation clock setting.                                                                                 |

| (Selective) | Changing setting of the<br>SDRmn register | Re-set the register to change the transfer<br>baud rate setting (setting the transfer<br>clock by dividing the operation clock<br>(fMCK)). |

| (Selective) | Changing setting of the<br>SMRmn register | Re-set the register to change serial mode register mn (SMRmn) setting.                                                                     |

| (Selective) | Changing setting of the<br>SCRmn register | Re-set the register to change serial communication operation setting register mn (SCRmn) setting.                                          |

| (Selective) | Changing setting of the<br>SOm register   | Set the initial output level of the serial clock (CKOmn).                                                                                  |

| (Selective) | Clearing error flag                       | If the OVF flag remain set, clear this using serial flag clear trigger register mn (SIRmn).                                                |

| (Essential) | Port manipulation                         | Enable clock output of the target channel by setting a port register and a port mode register.                                             |

| (Essential) | Writing to the SSm register               | Set the SSmn bit of the target channel to 1 (SEmn bit = 1: to enable operation).                                                           |

|             | Completing resumption setting             | Setting is completed<br>Sets dummy data to the SIOp register (bits 7<br>to 0 of the SDRmn register) and start<br>communication.            |

#### Figure 11-36. Procedure for Resuming Master Reception

**Remark** If PER0 is rewritten while stopping the master transmission and the clock supply is stopped, wait until the transmission target (slave) stops or transmission finishes, and then perform initialization instead of restarting the transmission.

# Figure 11-84. Example of Contents of Registers for UART Reception (UART0 to UART2) (2/2)

| (e) Se | erial ou | utput i | registe | er m (S | SOm)  | The   | e regis | ter that | at not | used    | in this | s mod | e.           |              |       |       |

|--------|----------|---------|---------|---------|-------|-------|---------|----------|--------|---------|---------|-------|--------------|--------------|-------|-------|

|        | 15       | 14      | 13      | 12      | 11    | 10    | 9       | 8        | 7      | 6       | 5       | 4     | 3            | 2            | 1     | 0     |

| SOm    |          |         |         |         |       |       | CKOm1   | CKOm0    |        |         |         |       | SO03<br>Note | SO02<br>Note | SO01  | SOm0  |

|        | 0        | 0       | 0       | 0       | 1     | 1     | ×       | ×        | 0      | 0       | 0       | 0     | ×            | ×            | ×     | ×     |

|        |          |         |         |         |       |       |         |          |        |         |         |       |              |              |       |       |

| (f) Se | rial ou  | utput   | enable  | e regis | ter m | (SOE  | m) ī    | The re   | gister | that r  | not us  | ed in | this m       | ode.         |       |       |

|        | 15       | 14      | 13      | 12      | 11    | 10    | 9       | 8        | 7      | 6       | 5       | 4     | 3            | 2            | 1     | 0     |

| SOEm   |          |         |         |         |       |       |         |          |        |         |         |       | SOE03        | SOE02        | SOE01 | SOEm0 |

|        | 0        | 0       | 0       | 0       | 0     | 0     | 0       | 0        | 0      | 0       | 0       | 0     | ×            | ×            | ×     | ×     |

|        |          |         |         |         |       |       |         |          |        |         |         |       |              |              |       |       |

| (g) Se | erial ch | nanne   | l start | regist  | er m  | (SSm) | ) Se    | ts only  | the l  | bits of | the ta  | arget | chann        | el is 1      |       |       |

|        | 15       | 14      | 13      | 12      | 11    | 10    | 9       | 8        | 7      | 6       | 5       | 4     | 3            | 2            | 1     | 0     |

| SSm    |          |         |         |         |       |       |         |          |        |         |         |       | SS03         | SS02         | SSm1  | SSm0  |

|        | 0        | 0       | 0       | 0       | 0     | 0     | 0       | 0        | 0      | 0       | 0       | 0     | 0/1          | ×            | 0/1   | ×     |

|        |          |         |         |         |       |       |         |          |        |         |         |       |              |              |       |       |

Note Provided only in 30-pin product serial array unit 0.

#### **Remarks 1.** m: Unit number (m = 0, 1)

2. Setting disabled (set to the initial value)

$\times$ : Bit that cannot be used in this mode (set to the initial value when not used in any mode) 0/1: Set to 0 or 1 depending on the usage of the user

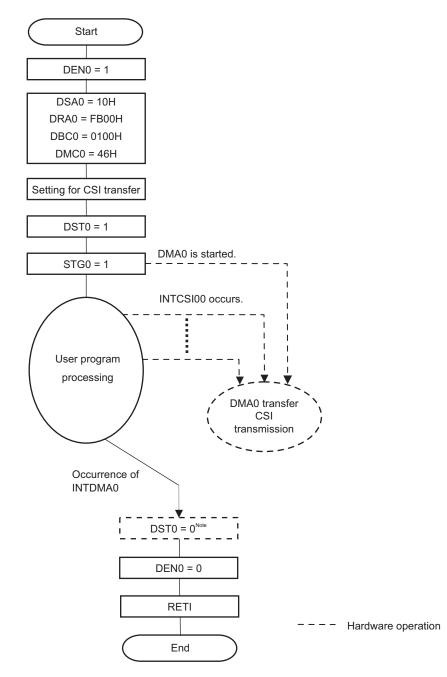

#### Figure 14-7. Example of Setting for CSI Consecutive Transmission

Note The DST0 flag is automatically cleared to 0 when a DMA transfer is completed. Writing the DEN0 flag is enabled only when DST0 = 0. To terminate a DMA transfer without waiting for occurrence of the interrupt of DMA0 (INTDMA0), set the DST0 bit to 0 and then the DEN0 bit to 0 (for details, refer to 14.5.5 Forced termination by software).

The first trigger for consecutive transmission is not started by the interrupt of CSI. In this example, it start by a software trigger.

CSI transmission of the second time and onward is automatically executed.

A DMA interrupt (INTDMA0) occurs when the last transmit data has been written to the data register.

# RL78/G12

# Figure 15-6. Format of Priority Specification Flag Registers (PR00L, PR00H, PR01L, PR10L, PR10H, PR11L) (20-, 24-pin product)

| Address: FFF | E8H After               | reset: FFH              | R/W           |                 |              |              |                                                      |                                      |

|--------------|-------------------------|-------------------------|---------------|-----------------|--------------|--------------|------------------------------------------------------|--------------------------------------|

| Symbol       | <7>                     | <6>                     | <5>           | <4>             | <3>          | <2>          | <1>                                                  | <0>                                  |

| PR00L        | DMAPR01 <sup>Note</sup> | DMAPR00 <sup>Note</sup> | PPR03         | PPR02           | PPR01        | PPR00        | LVIPR0                                               | WDTIPR0                              |

| •            |                         |                         |               |                 |              | •            |                                                      |                                      |

| Address: FFF | ECH After               | reset: FFH              | R/W           |                 |              |              |                                                      |                                      |

| Symbol       | <7>                     | <6>                     | <5>           | <4>             | <3>          | <2>          | <1>                                                  | <0>                                  |

| PR10L        | DMAPR11                 | DMAPR10                 | PPR13         | PPR12           | PPR11        | PPR10        | LVIPR1                                               | WDTIPR1                              |

|              |                         |                         |               |                 |              |              |                                                      |                                      |

| Address: FFF | E9H After               | reset: FFH              | R/W           |                 |              |              |                                                      |                                      |

| Symbol       | <7>                     | <6>                     | <5>           | <4>             | <3>          | <2>          | <1>                                                  | <0>                                  |

| PR00H        | TMPR001                 | TMPR000                 | IICAPR00      | TMPR003H        | TMPR001H     | SREPR00      | SRPR00                                               | STPR00                               |

|              |                         |                         |               |                 |              |              | CSIPR001 <sup>Note</sup><br>IICPR001 <sup>Note</sup> | CSIPR000<br>IICPR000 <sup>Note</sup> |

| l            |                         |                         |               |                 |              |              | IICPRUUT                                             | IICPR000                             |

| Address: FFF | EDH After               | reset: FFH              | R/W           |                 |              |              |                                                      |                                      |

| Symbol       | <7>                     | <6>                     | <5>           | <4>             | <3>          | <2>          | <1>                                                  | <0>                                  |

| PR10H        | TMPR101                 | TMPR100                 | IICAPR10      | TMPR103H        | TMPR101H     | SREPR10      | SRPR10                                               | STPR10                               |

| THINH        |                         |                         |               |                 |              | ONEITHO      | CSIPR101                                             | CSIPR100                             |

|              |                         |                         |               |                 |              |              | IICPR101                                             | IICPR100                             |

|              |                         |                         |               |                 |              |              |                                                      |                                      |

| Address: FF  | FEAH After              | reset: FFH              | R/W           |                 |              |              |                                                      |                                      |

| Symbol       | 7                       | <6>                     | <5>           | <4>             | <3>          | <2>          | <1>                                                  | <0>                                  |

| PR01L        | 1                       | FLPR0                   | MDPR0         | KRPR0           | TMKAPR0      | ADPR0        | TMPR003                                              | TMPR002                              |

|              |                         |                         |               |                 |              |              |                                                      |                                      |

| Address: FF  | FEEH After              | reset: FFH              | R/W           |                 |              |              |                                                      |                                      |

| Symbol       | 7                       | <6>                     | <5>           | <4>             | <3>          | <2>          | <1>                                                  | <0>                                  |

| PR11L        | 1                       | FLPR1                   | MDPR1         | KRPR1           | TMKAPR1      | ADPR1        | TMPR001                                              | TMPR102                              |

|              |                         | ,                       |               |                 |              |              |                                                      | 1                                    |

|              | XXPR1X                  | XXPR0X                  |               |                 | Priority Lev | el Selection |                                                      |                                      |

|              | 0                       | 0                       | Specifying le | vel 0 (high pri | ority)       |              |                                                      |                                      |

|              | 0                       | 1                       | Specifying le | vel 1           |              |              |                                                      |                                      |

|              | 1                       | 0                       | Specifying le | vel 2           |              |              |                                                      |                                      |

|              | 1                       | 1                       | Specifying le | vel 3 (low pric | ority)       |              |                                                      |                                      |

Note Provided in the R5F102 products only.

**Caution** Be sure to set bits that are not available to the initial value.

# 15.3.4 External interrupt rising edge enable register (EGP0), external interrupt falling edge enable register (EGN0)

These registers specify the valid edge for INTP0 to INTP5.

The EGP0 and EGN0 registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

# Figure 15-8. Format of External Interrupt Rising Edge Enable Register (EGP0) and External Interrupt Falling Edge Enable Register (EGN0)

# 20-, 24-pin products

| Address: FFF | -38H After | reset: 00H | R/W           |                |                |                |         |      |

|--------------|------------|------------|---------------|----------------|----------------|----------------|---------|------|

| Symbol       | 7          | 6          | 5             | 4              | 3              | 2              | 1       | 0    |

| EGP0         | 0          | 0          | 0             | 0              | EGP3           | EGP2           | EGP1    | EGP0 |

|              |            |            |               |                |                |                |         |      |

| Address: FFF | 39H After  | reset: 00H | R/W           |                |                |                |         |      |

| Symbol       | 7          | 6          | 5             | 4              | 3              | 2              | 1       | 0    |

| EGN0         | 0          | 0          | 0             | 0              | EGN3           | EGN2           | EGN1    | EGN0 |

|              |            |            |               |                |                |                |         |      |

| 30-pin pro   | ducts      |            |               |                |                |                |         |      |

| Address: FFF | -38H After | reset: 00H | R/W           |                |                |                |         |      |

| Symbol       | 7          | 6          | 5             | 4              | 3              | 2              | 1       | 0    |

| EGP0         | 0          | 0          | EGP5          | EGP4           | EGP3           | EGP2           | EGP1    | EGP0 |

|              |            |            |               |                |                |                |         |      |

| Address: FFF | -39H After | reset: 00H | R/W           |                |                |                |         |      |

| Symbol       | 7          | 6          | 5             | 4              | 3              | 2              | 1       | 0    |

| EGN0         | 0          | 0          | EGN5          | EGN4           | EGN3           | EGN2           | EGN1    | EGN0 |

|              |            |            |               |                |                |                |         |      |

|              | EGPn       | EGNn       |               | INTPn j        | oin valid edge | selection (n = | 0 to 5) |      |

|              | 0          | 0          | Edge detecti  | on disabled    |                |                |         |      |

|              | 0          | 1          | Falling edge  |                |                |                |         |      |

|              | 1          | 0          | Rising edge   |                |                |                |         |      |

|              | 1          | 1          | Both rising a | nd falling edg | es             |                |         |      |

**Caution** When the input port pins used for the external interrupt functions are switched to the output mode, the INTPn interrupt might be generated upon detection of a valid edge. When switching the input port pins to the output mode, set the port mode register (PMxx) to 0 after disabling the edge detection (by setting EGPn and EGNn to 0).

**Remark** n = 0 to 5

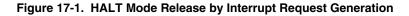

## (2) HALT mode release

The HALT mode can be released by the following two sources.

#### (a) Release by unmasked interrupt request

When an unmasked interrupt request is generated, the HALT mode is released. If interrupt acknowledgment is enabled, vectored interrupt servicing is carried out. If interrupt acknowledgment is disabled, the next address instruction is executed.

High-speed on-chip oscillator clock

- Notes 1. For details of the standby release signal, see Figure 15-1 Basic Configuration of Interrupt Function.

- 2. Wait time for HALT mode release

- When vectored interrupt servicing is carried out: 15 to 16 clocks

- When vectored interrupt servicing is not carried out: 9 to 10 clocks

- **Remark** The broken lines indicate the case when the interrupt request which has released the standby mode is acknowledged.

| STOP M                                    | ode Setting | When STOP Instruction Is                                                                    | s Executed While CPU Is Operat                                   | ing on Main System Clock                                                     |

|-------------------------------------------|-------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|

| Item                                      |             | When CPU Is Operating on<br>High-speed On-chip Oscillator<br>Clock (f⊮)                     | When CPU Is Operating on<br>X1 Clock (fx)                        | When CPU Is Operating on<br>External Main System Clock<br>(f <sub>Ex</sub> ) |

| System clock                              |             | Clock supply to the CPU is stop                                                             | ped                                                              |                                                                              |

| Main system clo                           | ck f⊮       | Stopped                                                                                     |                                                                  |                                                                              |

|                                           | fx          |                                                                                             |                                                                  |                                                                              |

|                                           | fex         |                                                                                             |                                                                  |                                                                              |

| fı∟                                       |             | operation speed mode control re<br>• WUTMMCK = 1: Oscillates<br>• WUTMMCK = 0 and WDTON     | = 0: Stops<br>and WDSTBYON = 1: Oscillate                        |                                                                              |

| CPU                                       |             | Operation stopped                                                                           |                                                                  |                                                                              |

| Code flash memory                         |             | 1                                                                                           |                                                                  |                                                                              |

| Data flash memory                         |             | Operation stopped                                                                           |                                                                  |                                                                              |

| RAM                                       |             | Operation stopped                                                                           |                                                                  |                                                                              |

| Port (latch)                              |             | Status before STOP mode was                                                                 | set is retained                                                  |                                                                              |

| Timer array unit                          |             | Operation disabled                                                                          |                                                                  |                                                                              |

| 12-bit interval timer                     |             | Operable                                                                                    |                                                                  |                                                                              |

| Watchdog timer                            |             | Set by bit 0 (WDSTBYON) of op<br>• WDSTBYON = 0: Operation s<br>• WDSTBYON = 1: Operation c | topped                                                           |                                                                              |

| Clock output/buzzer                       | output      | Operation disabled                                                                          |                                                                  |                                                                              |

| A/D converter                             |             | Wakeup operation is enabled (s                                                              | witching to the SNOOZE mode)                                     |                                                                              |

| Serial array unit (SA                     | U)          |                                                                                             | nly for CSI00 and UART0 (switch<br>ng other than CSI00 and UART0 |                                                                              |

| Serial interface (IICA                    | A)          | Wakeup by address match oper                                                                | rable                                                            |                                                                              |

| Multiplier and divider accumulator        | r/multiply- | Operation disabled                                                                          |                                                                  |                                                                              |

| DMA controller                            |             |                                                                                             |                                                                  |                                                                              |

| Power-on-reset func                       | tion        | Operable                                                                                    |                                                                  |                                                                              |

| Voltage detection fur                     | nction      | ]                                                                                           |                                                                  |                                                                              |

| External interrupt                        |             | ]                                                                                           |                                                                  |                                                                              |

| Key interrupt function                    | n           | ]                                                                                           |                                                                  |                                                                              |

| CRC operation funct                       | lion        | Operation stopped                                                                           |                                                                  |                                                                              |

| RAM parity error                          |             | ]                                                                                           |                                                                  |                                                                              |

| detection function                        |             |                                                                                             |                                                                  |                                                                              |

| RAM guard function                        |             | ļ                                                                                           |                                                                  |                                                                              |

| SFR guard function                        |             | ļ                                                                                           |                                                                  |                                                                              |

| Illegal-memory acce<br>detection function | SS          |                                                                                             |                                                                  |                                                                              |

#### Table 17-2. Operating Statuses in STOP Mode

**Remark** Operation stopped: Operation is automatically stopped before switching to the STOP mode.

Operation disabled: Operation is stopped before switching to the STOP mode.

- fін: High-speed on-chip oscillator clock

- fil: Low-speed on-chip oscillator clock

- fx: X1 clock

- fex: External main system clock

RENESAS

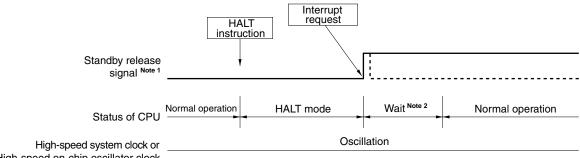

Figure 18-5. Procedure for Checking Reset Source

<R> The flow described above is an example of the procedure for checking.

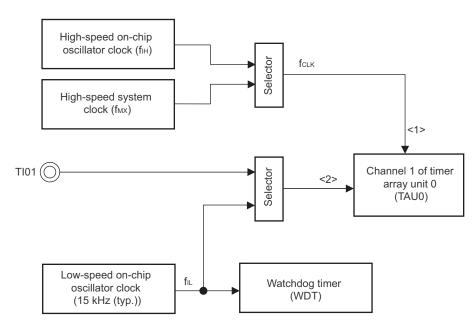

Figure 21-10. Configuration of Frequency Detection Function

If input pulse interval measurement results in an abnormal value, it can be concluded that the clock frequency is abnormal.

For how to execute input pulse interval measurement, see 6.8.4 Operation as input pulse interval measurement.

#### 21.3.6.1 Timer input select register 0 (TIS0)

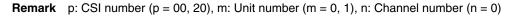

This register is used to select the timer input of channel 1 of the timer array unit 0 (TAU0) in 20- and 24-pin products. The TISO register can be set by an 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

Address: F0074H After reset: 00H R/W

S

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0     |

|--------|---|---|---|---|---|---|-------|-------|

| TIS0   | 0 | 0 | 0 | 0 | 0 | 0 | TIS01 | TIS00 |

| TIS01 | TIS00 | Selection of timer input used with channel 1 |

|-------|-------|----------------------------------------------|

| ×     | 0     | Input signal of timer input pin (TI01)       |

| 0     | 1     | Low-speed on-chip oscillator clock (fiL)     |

| 1     | 1     | Setting prohibited                           |

Remark ×: don't care

# 27.1.2 Description of operation column

The operation when the instruction is executed is shown in the "Operation" column using the following symbols.

| Symbol     | Function                                                                                 |

|------------|------------------------------------------------------------------------------------------|

| А          | A register; 8-bit accumulator                                                            |

| х          | X register                                                                               |

| В          | B register                                                                               |

| С          | C register                                                                               |

| D          | D register                                                                               |

| E          | E register                                                                               |

| н          | H register                                                                               |

| L          | L register                                                                               |

| ES         | ES register                                                                              |

| CS         | CS register                                                                              |

| AX         | AX register pair; 16-bit accumulator                                                     |

| BC         | BC register pair                                                                         |

| DE         | DE register pair                                                                         |

| HL         | HL register pair                                                                         |

| PC         | Program counter                                                                          |

| SP         | Stack pointer                                                                            |

| PSW        | Program status word                                                                      |

| CY         | Carry flag                                                                               |

| AC         | Auxiliary carry flag                                                                     |

| Z          | Zero flag                                                                                |

| RBS        | Register bank select flag                                                                |

| Ē          | Interrupt request enable flag                                                            |

| 0          | Memory contents indicated by address or register contents in parentheses                 |

| XH, XL     | 16-bit registers: $X_{H}$ = higher 8 bits, $X_{L}$ = lower 8 bits                        |

| Xs, Xн, XL | 20-bit registers: $X_S =$ (bits 19 to 16), $X_H =$ (bits 15 to 8), $X_L =$ (bits 7 to 0) |

| ^          | Logical product (AND)                                                                    |

| V          | Logical sum (OR)                                                                         |

| ¥          | Exclusive logical sum (exclusive OR)                                                     |

| _          | Inverted data                                                                            |

| addr5      | 16-bit immediate data (even addresses only in 0080H to 00BFH)                            |

| addr16     | 16-bit immediate data                                                                    |

| addr20     | 20-bit immediate data                                                                    |

| jdisp8     | Signed 8-bit data (displacement value)                                                   |

| jdisp16    | Signed 16-bit data (displacement value)                                                  |

| Table 27-2. Symbols in "Operation" Colun |

|------------------------------------------|

|------------------------------------------|

| Instruction<br>Group       | Mnemonic | Operands        | Bytes | Clocks |        | Clocks                                  | Flag |    |    |

|----------------------------|----------|-----------------|-------|--------|--------|-----------------------------------------|------|----|----|

|                            |          |                 |       | Note 1 | Note 2 |                                         | z    | AC | CY |

| 8-bit data<br>transfer     | ХСН      | A, [HL+B]       | 2     | 2      | _      | $A \longleftrightarrow (HL+B)$          |      |    |    |

|                            |          | A, ES:[HL+B]    | 3     | 3      | _      | $A \longleftrightarrow ((ES, HL){+}B)$  |      |    |    |

|                            |          | A, [HL+C]       | 2     | 2      | _      | $A \longleftrightarrow (HL+C)$          |      |    |    |

|                            |          | A, ES:[HL+C]    | 3     | 3      | _      | $A \leftarrow \rightarrow ((ES, HL)+C)$ |      |    |    |

|                            | ONEB     | A               | 1     | 1      | _      | A ← 01H                                 |      |    |    |

|                            |          | х               | 1     | 1      | _      | X ← 01H                                 |      |    |    |

|                            |          | В               | 1     | 1      | -      | B ← 01H                                 |      |    |    |

|                            |          | С               | 1     | 1      | _      | C ← 01H                                 |      |    |    |

|                            |          | !addr16         | 3     | 1      | _      | (addr16) ← 01H                          |      |    |    |

|                            |          | ES:laddr16      | 4     | 2      | _      | (ES, addr16) ← 01H                      |      |    |    |

|                            |          | saddr           | 2     | 1      | _      | (saddr) ← 01H                           |      |    |    |

|                            | CLRB     | A               | 1     | 1      | _      | A ~ 00H                                 |      |    |    |

|                            |          | х               | 1     | 1      | -      | X ← 00H                                 |      |    |    |

|                            |          | В               | 1     | 1      | _      | B ← 00H                                 |      |    |    |

|                            |          | С               | 1     | 1      | -      | C ← 00H                                 |      |    |    |

|                            |          | !addr16         | 3     | 1      | -      | (addr16) ← 00H                          |      |    |    |

|                            |          | ES:laddr16      | 4     | 2      | _      | (ES,addr16) ← 00H                       |      |    |    |

|                            |          | saddr           | 2     | 1      | _      | (saddr) ← 00H                           |      |    |    |

|                            | MOVS     | [HL+byte], X    | 3     | 1      | _      | (HL+byte) ← X                           | ×    |    | ×  |

|                            |          | ES:[HL+byte], X | 4     | 2      | _      | (ES, HL+byte) ← X                       | ×    |    | ×  |

| 16-bit<br>data<br>transfer | MOVW     | rp, #word       | 3     | 1      | -      | $rp \leftarrow word$                    |      |    |    |

|                            |          | saddrp, #word   | 4     | 1      | _      | $(saddrp) \leftarrow word$              |      |    |    |

|                            |          | sfrp, #word     | 4     | 1      | -      | $sfrp \leftarrow word$                  |      |    |    |

|                            |          | AX, rp Note 3   | 1     | 1      | -      | AX ← rp                                 |      |    |    |

|                            |          | rp, AX Note 3   | 1     | 1      | -      | $rp \leftarrow AX$                      |      |    |    |

|                            |          | AX, !addr16     | 3     | 1      | 4      | $AX \leftarrow (addr16)$                |      |    |    |

|                            |          | !addr16, AX     | 3     | 1      | _      | (addr16) $\leftarrow$ AX                |      |    |    |

|                            |          | AX, ES:!addr16  | 4     | 2      | 5      | $AX \leftarrow (ES, addr16)$            |      |    |    |

|                            |          | ES:laddr16, AX  | 4     | 2      | -      | (ES, addr16) $\leftarrow$ AX            |      |    |    |

|                            |          | AX, saddrp      | 2     | 1      | _      | $AX \leftarrow (saddrp)$                |      |    |    |

|                            |          | saddrp, AX      | 2     | 1      | _      | $(saddrp) \leftarrow AX$                |      |    |    |

|                            |          | AX, sfrp        | 2     | 1      | _      | AX ← sfrp                               |      |    |    |

|                            |          | sfrp, AX        | 2     | 1      | -      | $sfrp \leftarrow AX$                    |      |    |    |

Table 27-5.

Operation List (4/17)

**Notes 1.** Number of CPU clocks (fcLk) when the internal RAM area, SFR area, or extended SFR area is accessed, or when no data is accessed.

- 2. Number of CPU clocks (fcLK) when the code flash memory is accessed, or when the data flash memory is accessed by an 8-bit instruction.

- **3.** Except rp = AX

- **Remark** Number of clock is when program exists in the internal ROM (flash memory) area. If fetching the instruction from the internal RAM area, the number becomes double number plus 3 clocks at a maximum.

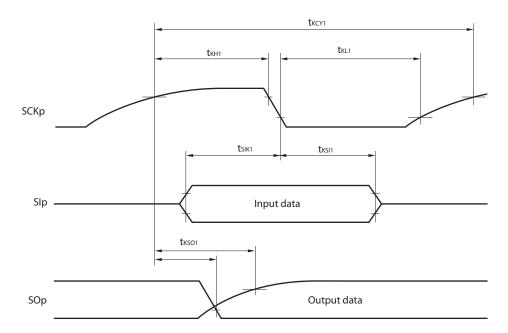

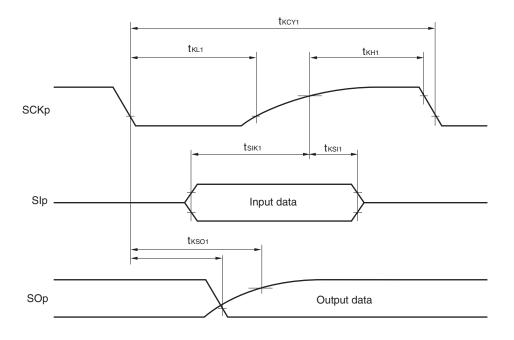

CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1)

CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)